# Role of HLT in PXD readout

R.Itoh, KEK

### **PXD** integration

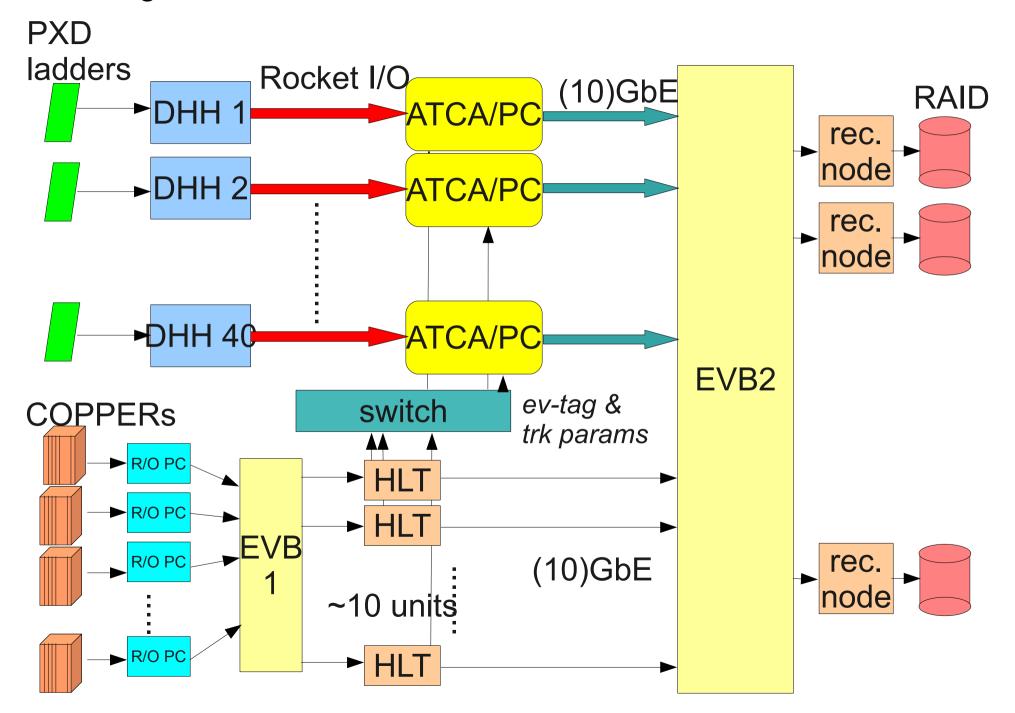

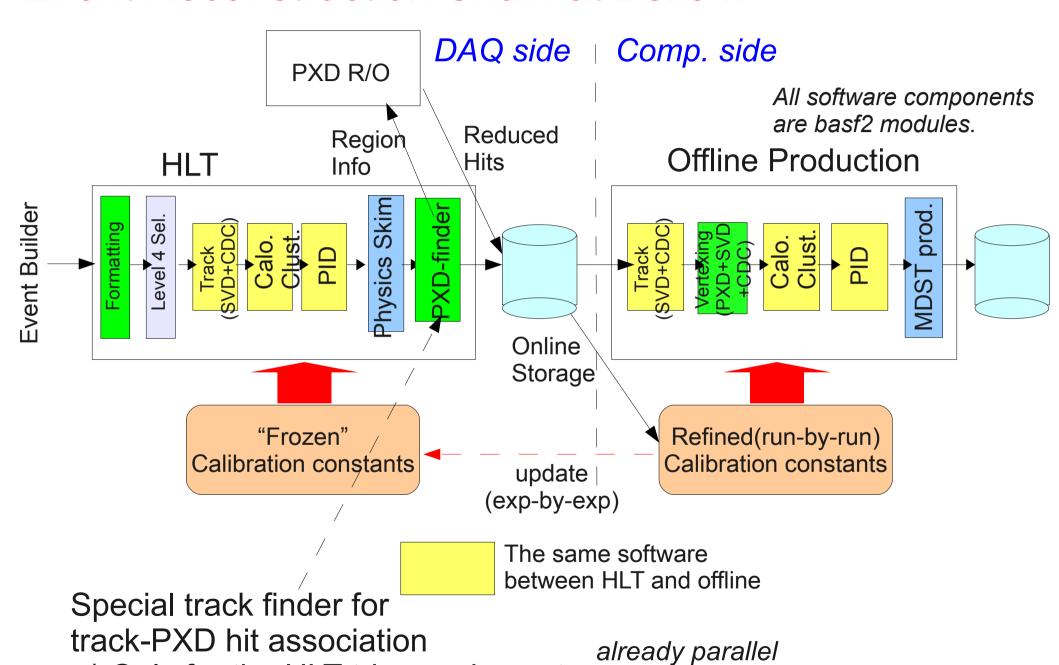

# **Event Reconstruction Chain at Belle II**

- \* Only for the HLT-triggered events in 200 \* 10 cores

- \* Can make use of SVD+CDC raw data + full tracking results also

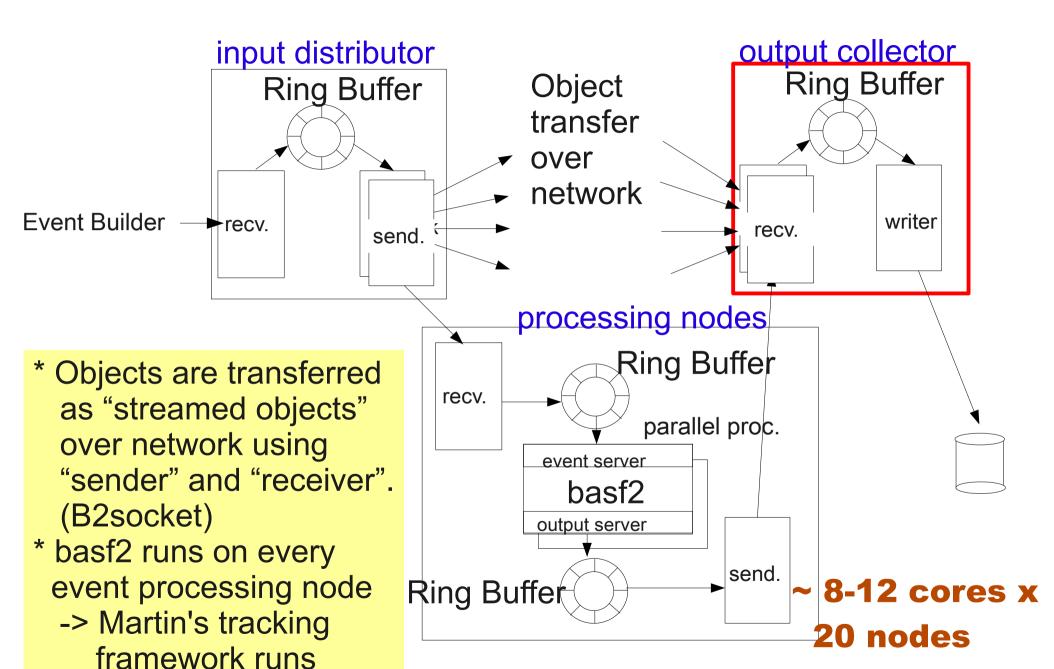

# Software framework of HLT (1 unit) = pbasf2 for PC cluster

"as is".

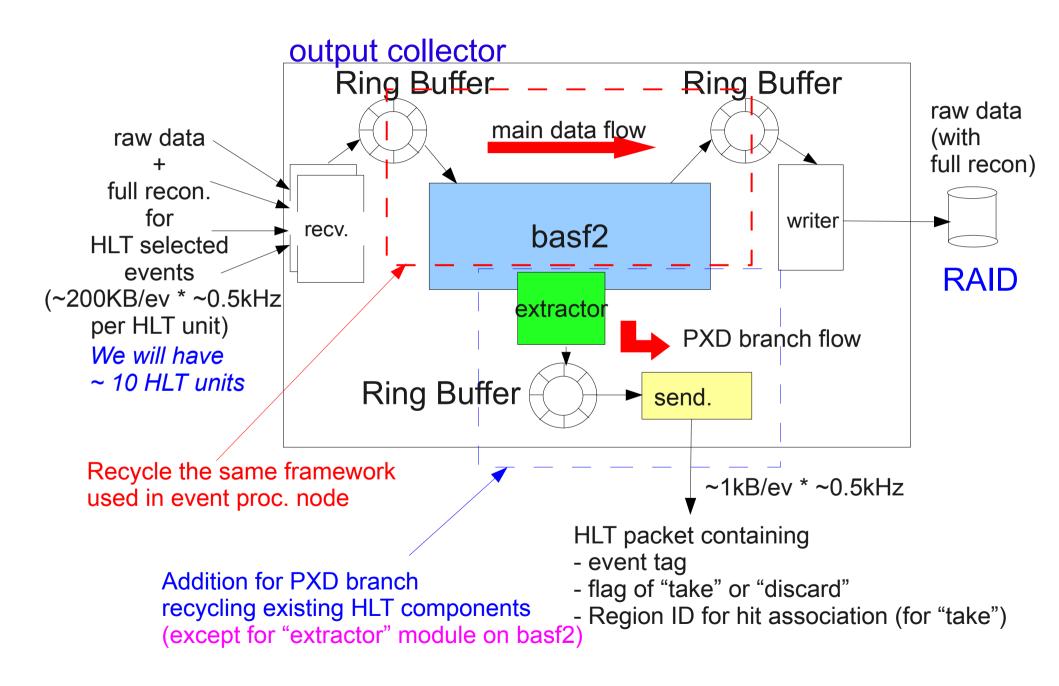

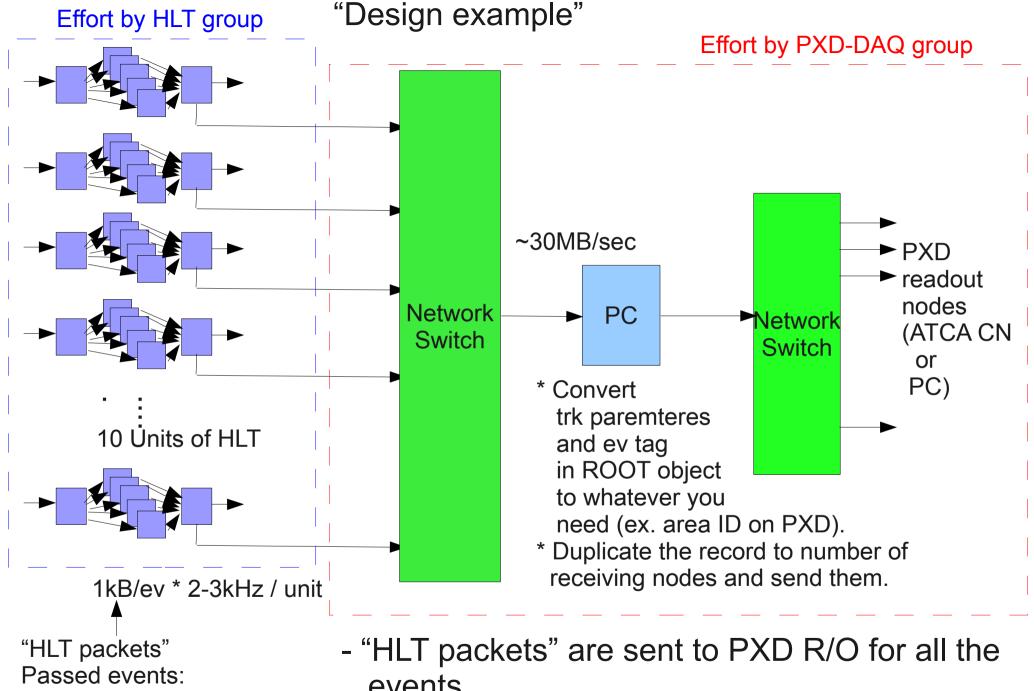

#### Modification for PXD data stream

- evtag + track parameters Discarded events: evtag + "discarded" flag

- events.

- HLT packets are disordered because of parallel processing

Processing framework in PXD R/O box for "baseline" and "backup" options DHH Hit buffer \* Event sequence is the **Event list** same as that of HLT packet evt tag ptr to hit buffer **Event Builder 2** PXD hits 1 PXD hits 2 evt 1 assoc, hits n PXD hits 3 evt 3 discard packet ~50k events evt 4 discard packet (30kHz \* a few sec) evt 2 assoc, hits PXD hits n ATCA on board memory Reduced hits or PC memory **HLT** packet Output buffer region ID take/discard evt tag take: \* hit-track association 1, 3, 4, 2, .... \* copy assoc hits to output buffer disorderd \* release hit buffer/event list discard: \* put discard packet in output buffer HI T \* release hit buffer/event list

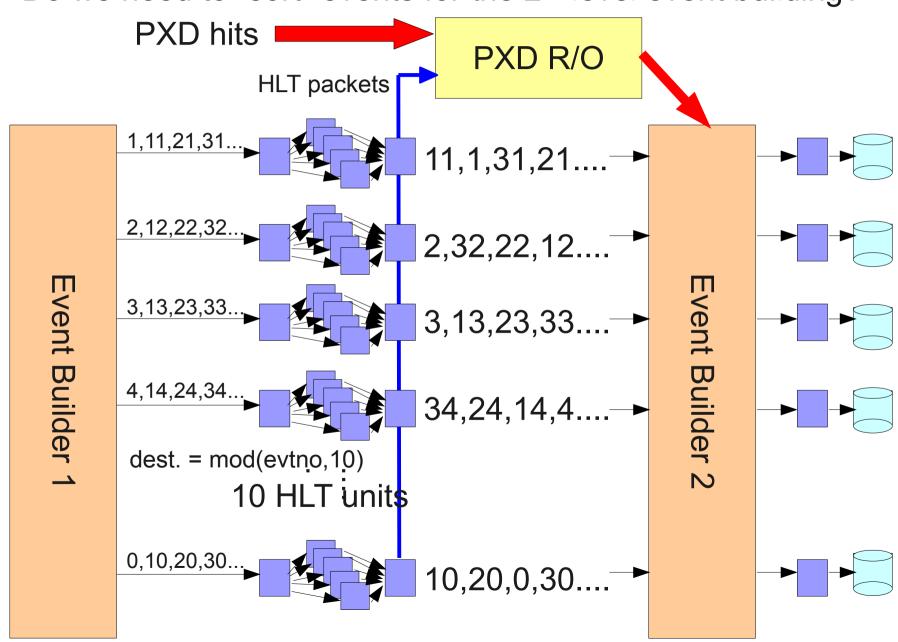

## Idea on 2<sup>nd</sup> level event building (EVB2)

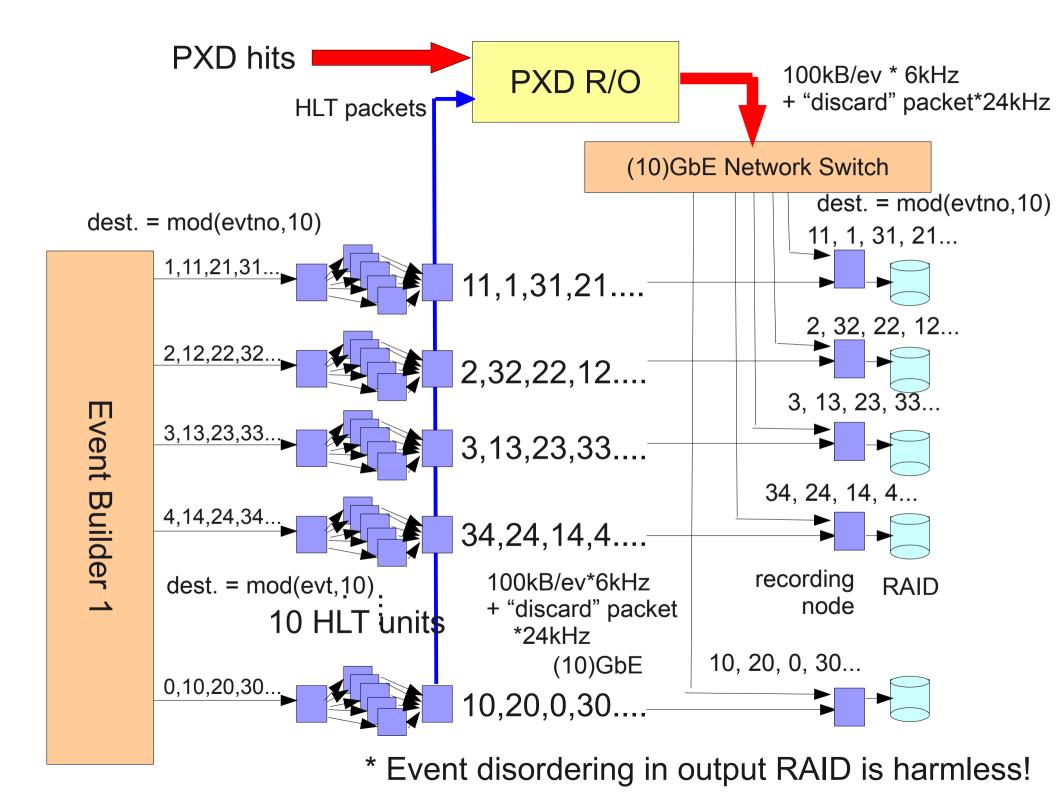

- Event sequence from HLT is disordered.

- Do we need to "sort" events for the 2<sup>nd</sup> level event building?

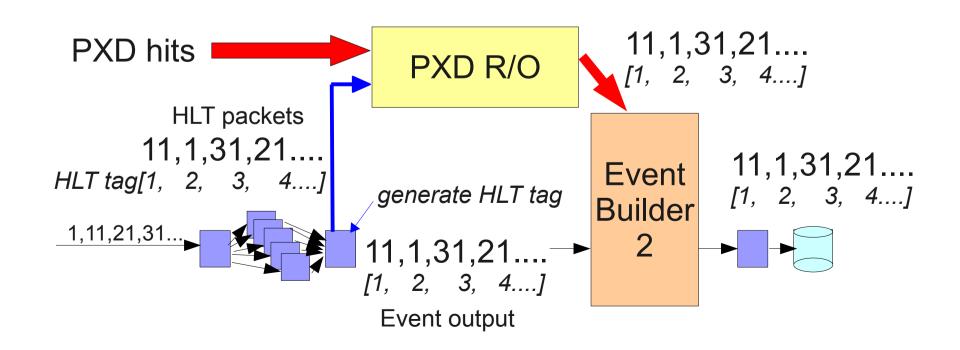

- HLT sends the event output to EVB2 and HLT packets to PXD R/O in the same order, although event tag is disordered.

- -> Idea: place new "HLT tag" both in "event output" and "HLT packet" and build event using the tag at EVB2.

- Processing on PXD R/O does not break the ordering of HLT packets.

- No sorting is required although the event tag is disordered in recording RAID.

# Summary

- HLT is supposed to provide track information to PXD readout box for the track-hit association (baseline and PC options).

- The "event disordering problem" can be solved for "baseline" and "PC" options in some cases.

- However, in case of "challenge" option where another parallel processing in ATCA card is expected, the event ordering may be broken in ATCA card differently from HLT's.

- -> Needs more consideration on event disordering......

- Waiting for the decision on PXD readout box.

# Backup Slides

# Do we really need 4GB/DHH for data buffering?

- Average HLT latency for an event is expected to be less than 1 sec as shown in previous meeting.

- Thanks to parallel processing, the HLT packets for events with shorter processing latency come faster. Not necessary to wait for the 5 sec latency for one particular problematic event.

- The PXD hit buffer is supposed to be released immediately after the hit-track association (if the algorithm shown in previous slide is used).

# We don't have to buffer every event for 5sec.

- \* It seems the required buffer size is much smaller than 30kHz\*5sec\*600MB/sec.

- <- This size is necessary only when 5 sec latency is consumed by all of ~2000 cores in HLT at one time. ==> very rare!

- \* We need a simple MC study to estimate the actual size.

- \* Sophisticated memory management scheme is required on FPGA in case of Option 12, anyway.