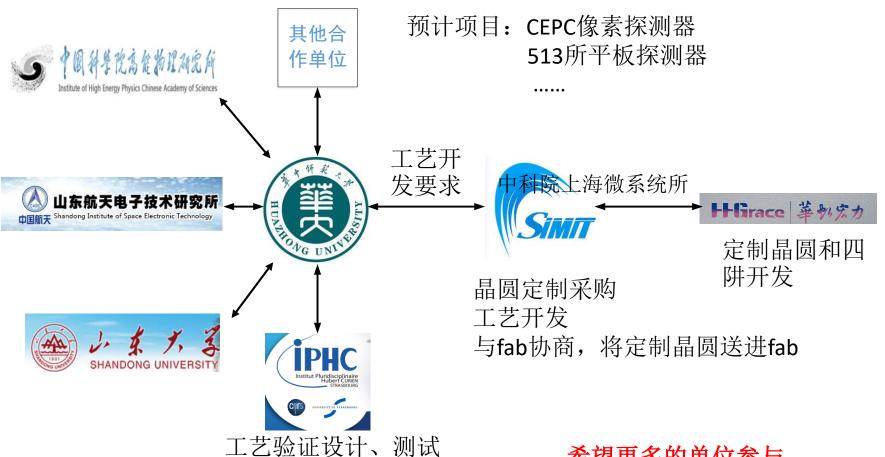

# 小线宽MAPS工艺开发和采样 x射线像素芯片研究

**肖乐** 华中师范大学

- 基于GSMC 115nm开发 -----上海华虹宏力半导体制造有限公司

- GSMC115nm工艺已经具备如下特征:

- 1P7M(1层Poly,7层金属)

- 1.2V NMOS/PMOS管 ————— 满足电路低功耗设计要求

- 3.3V NMOS/PMOS管用于设计I0电路

- 特征尺寸117nm, 从130nm工艺缩小10% ———— 可实现小面积电路

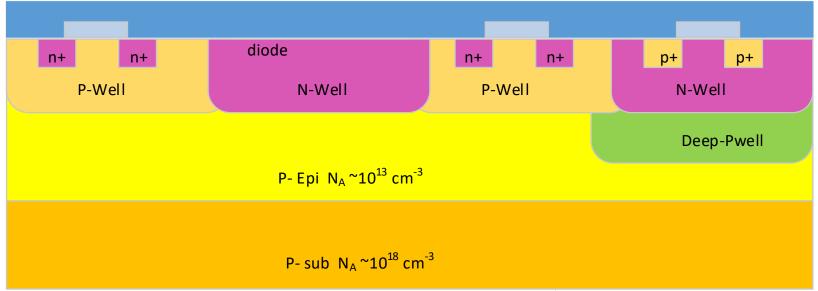

- 具有NW/PW/Deep-NW三阱

- Poly 电阻: 270 Ω/sqr N型poly,340 Ω/sqr P型poly,1 k Ω/sqr HR型poly

- MIM电容: 1fF/μm²

- SRAM IP

- 开发目标:

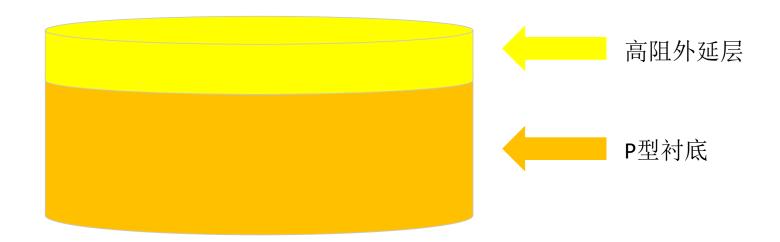

- 在晶圆上生长高阻外延层

- 开发四阱工艺: NW/PW/Deep-NW/Deep-PW , 即增加Deep-PW

- 实现上述目标需要非标准的工艺流程支持

- 基于115nm体硅工艺开发

- 在晶圆上生长高阻外延层

- 厚度可调: 18um~30um

- 电阻率: >1kΩ•cm

」参数参考了APLIDE芯片在TowerJazz 180nm

☐ CMOS图像传感器工艺的设计参数

- P型衬底注入浓度大约10<sup>18</sup>cm<sup>-3</sup>

- 高阻外延层注入浓度约为10<sup>13</sup>cm<sup>-3</sup>

- 像素内部使用Deep-Pwell屏蔽PMOS衬底N-well,阻止了与电极N-well竞争 收集电荷,从而提高电荷收集效率

开发后像素内部电路横截面示意图

希望更多的单位参与

### 指标要求:

- 能量范围: 3 keV~42 keV

- 空间分辨率: 100um

- 击中率: 5MHz

- 动态范围: 60dB

- 可连续采集

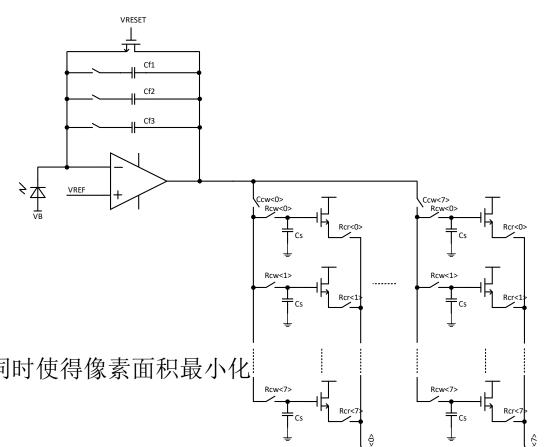

### 将采用开发的GSMC115nm工艺设计

目前使用TowerJazz180nm工艺进行前期仿真验证

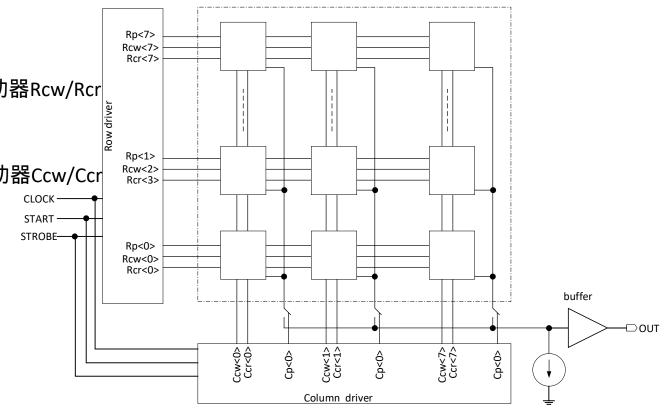

#### 整体结构:

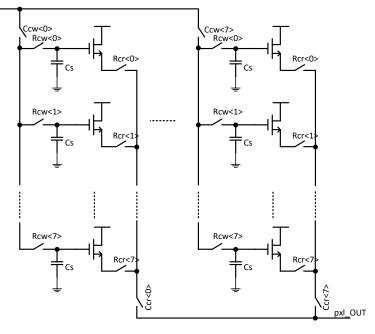

- 8x8像素阵列

- Row driver

- 像素级行驱动器Rp

- 像素内部读写行驱动器Rcw/Rcr

- Column driver

- 像素级列驱动器Cp

- 像素内部读写列驱动器Ccw/Ccr

- 一个输出buffer

#### 读出方式:

• 逐个像素读出

#### 像素内部结构:

- 收集电荷的p-n结

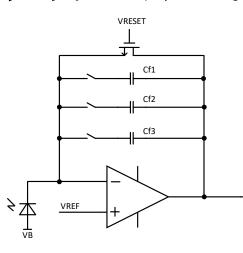

- 增益可调的前放

- 8x8开关电容阵列

- NMOS源跟随阵列

采样频率5MHz,且受STROBE信号控制

- STROBE高电平 ---> 逐个电容采样, 且所有像素同时进行采样。

- STROBE低电平 ---> 采样结束, 进入读出**阶段,逐个像素以** 312.5 kHz **速率读出,像素内部** 逐个采样电容以20 MHz**速率**读出。

Cs >>源跟随输入NMOS管栅极 电容

- 从而保证采样电容值 恒定,不受相关MOS 管寄生电容影响

- 目前Cs定在了10fF, 其他MOS管取最小尺

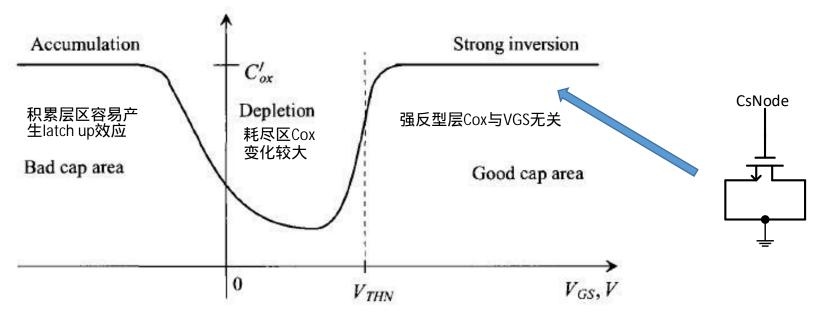

为了在保证性能的同时使得像素面积最小化

10fF采样电容Cs采用NMOS管来实现,工作于强反型层区域

**该**电容容值与其面积成正比,不受栅极电压变化影响

MOS管单位面积栅氧化层电容Cox与MOS管栅源电压VGS的关系

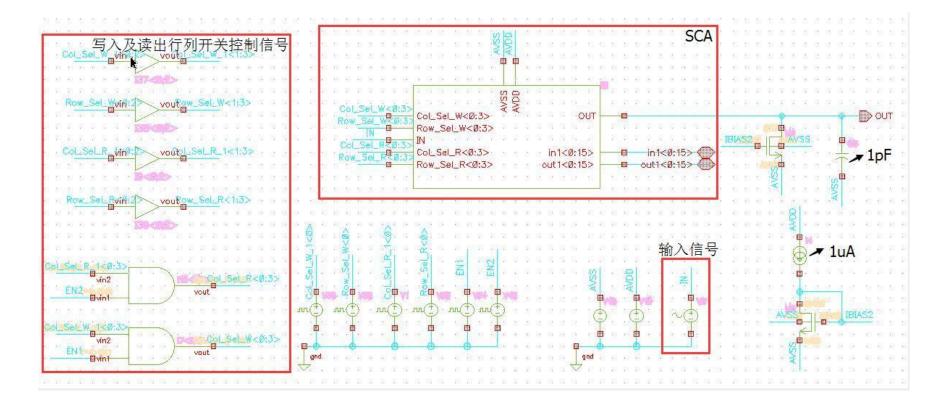

对4x4开关电容阵列(SCA)进行仿真 testbench包括:行列开关控制器、SCA、电流镜和sin信号源,负载为1pF电容,1uA电流。

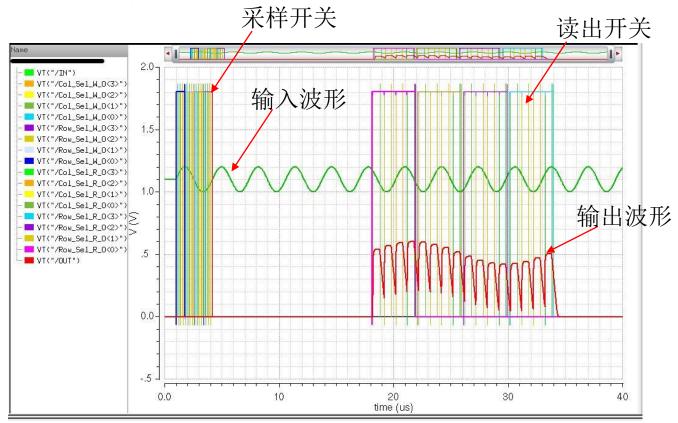

4x4开关电容阵列(SCA)仿真结果波形:输入为5MHz,幅**度是100mVpp的**正弦波,采样频率5MHz,读出频率1MHz。

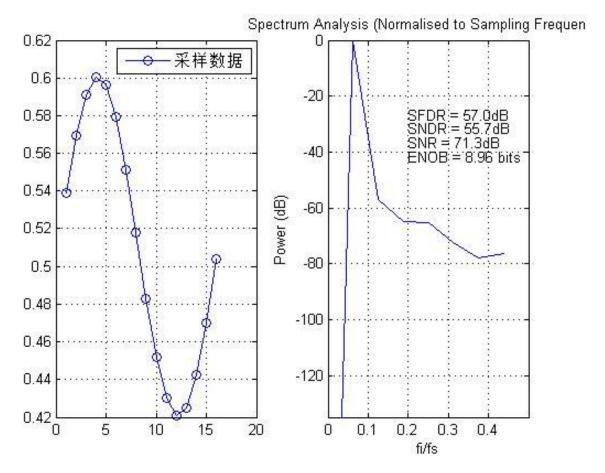

4x4开关电容阵列(SCA)仿真结果进行ENOB分析:可达到8.96 bit

### 总结

- GSMC115nm工艺的开发

- 开发比130nm更小尺寸且适合于MAPS设计的工艺

- 开发四阱工艺,像素内可以使用CMOS电路

- 开发有epi生长的晶圆

- · 基于GSMC115nm工艺的采样x射线像素芯片设计

- 采用像素内开关电容阵列结构(pixel-level SCA)

- 初步的仿真验证表明,可获得8.96bit的ENOB