# Pixel sensor prototypes design for CEPC vertex detector

## Ying ZHANG (张颖)

#### On behalf of the CEPC VTX study group

12-13 October 2017, NME'2017, IHEP, Beijing

### Outline

Introduction on CEPC vertex detector

#### R&D activities

- CMOS pixel sensor

- > SOI pixel sensor

- Summary and outlook

## Introduction

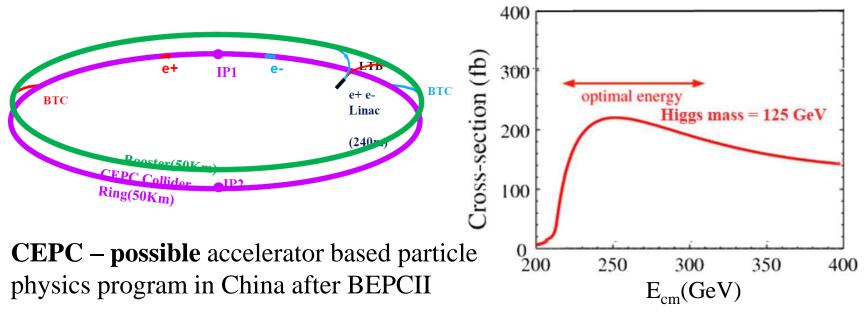

## CEPC – SppC

- Phase 1: e<sup>+</sup> e<sup>-</sup> Higgs [Z] factory two detectors, 1M H events in ~10yrs Circular Electron Positron Collider (CEPC)

- >  $E_{cm}$  ≈ 240 GeV, luminosity ~2×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, can also run at the Z-pole

- > Precise measurement of the Higgs boson and the Z boson

- Phase 2: a discovery machine for new physics; pp collision with E<sub>cm</sub> ≈ 50-100 TeV Supper proton-proton Collider (SppC)

Ref: CEPC-SppC workshop, X. LOU, Sep. 2, 2016, Beijing, China.

## **CEPC** accelerator layout option comparison

|        | Option                                    | Pretzel | Sawtooth<br>effect | Beam<br>loading | Dynamic<br>Aperture | Orbit<br>Correction | H<br>luminosity | Z-pole<br>luminosity | AC<br>power | SRF syetem<br>compatible<br>for H and Z |

|--------|-------------------------------------------|---------|--------------------|-----------------|---------------------|---------------------|-----------------|----------------------|-------------|-----------------------------------------|

| Pre-CD | R Baseline                                |         | Very<br>high       | Low             | Very<br>small       | Very<br>hard        | Low             | Very low             | High        | Difficult                               |

|        | Single Ring<br>(SR)                       | *       | *                  | ****            | *                   | *                   | ***             | *                    |             | ~~~                                     |

|        | CEPC Partial Double Ring Layout           | No      | High               | Very<br>High    | Medium              | Hard                | Medium          | Medium               | Low         | Difficult                               |

|        | Partial Double<br>Ring (PDR)              | ****    | **                 | *               | ***                 | **                  | ***             | ***                  | ****        | ***                                     |

|        | CEPC Measor Participants Ring Layor       | No      | High               | High            | Medium              | Medium              | Medium          | High                 | Low         | Difficult                               |

|        | Advanced<br>Partial Double<br>Ring (APDR) | ****    | ***                | ***             | ***                 | ***                 | ***             | ****                 | ****        | ***                                     |

| CDR B  | aseline                                   | No      | Vey<br>Low         | Low             | Large               | Easy                | High            | Very<br>High         | Low         | Very good                               |

|        | Full Parrtial<br>Double Ring<br>(FPDR)    | *****   | *****              | ****            | ****                | ****                | ****            | *****                | ****        | ****                                    |

Ref: J.Gao, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

### **Physics driven requirements**

Table 2.1 Required performance of the CEPC sub-detectors for critical benchmark Higgs processes.

| Physics Process                 | Measured Quantity                          | Critical Detector | Required Performance                                                    |

|---------------------------------|--------------------------------------------|-------------------|-------------------------------------------------------------------------|

| $ZH \to \ell^+ \ell^- X$        | Higgs mass, cross section                  | Tracker           | $\Delta(1/p_{\rm T})\sim 2	imes 10^{-5}$                                |

| $H \rightarrow \mu^+ \mu^-$     | $BR(H \to \mu^+ \mu^-)$                    | IIdekei           | $\oplus 1 \times 10^{-3}/(p_{\rm T}\sin\theta)$                         |

| $H\to b\bar{b},\;c\bar{c},\;gg$ | $BR(H \rightarrow b\bar{b}, c\bar{c}, gg)$ | Vertex            | $\sigma_{r\phi} \sim 5 \oplus 10/(p \sin^{3/2} \theta)  \mu \mathrm{m}$ |

| $H \to q\bar{q}, VV$            | $BR(H \to q\bar{q}, VV)$                   | ECAL, HCAL        | $\sigma_E^{ m jet}/E\sim 3$ – 4%                                        |

| $H \to \gamma \gamma$           | $BR(H \to \gamma \gamma)$                  | ECAL              | $\sigma_E \sim 16\%/\sqrt{E} \oplus 1\%$ (GeV)                          |

• Efficient tagging of heavy quarks (b/c) and  $\tau$  leptons

→ Impact parameter resolution,  $\sigma_{r\emptyset} = a \oplus \frac{b}{(p \cdot sin^{3/2}\theta)} \mu m$

Design constrains on vertex (to achieve a=5 and b=10, B=3.5T)

- > spatial resolution near the interaction point  $\sigma_{sp} \leq 3 \ \mu m$

- > material budget  $\leq 0.15\% X_0$ /layer

- > first layer located at a radius: ~1.6 cm

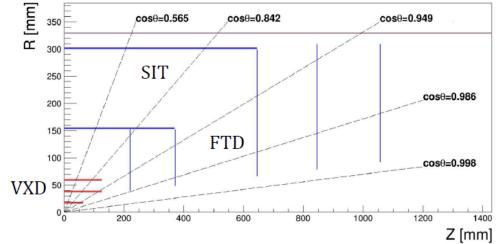

## **CEPC** vertex detector concept

## **Baseline design for the pre-CDR:** ILD-like but different forward region design

- > 3 layers of double-sided pixels

- >  $\sigma_{SP} = 2.8 \ \mu m$ , inner most layer

- readout time < 20 µs</p>

#### **VXD Geometry**

|         | R (mm) | <b>z</b>   (mm) | $ \cos \theta $ | $\sigma_{ m SP}$ ( $\mu$ m) | Readout time ( $\mu$ s) |

|---------|--------|-----------------|-----------------|-----------------------------|-------------------------|

| Layer 1 | 16     | 62.5            | 0.97            | 2.8                         | 20                      |

| Layer 2 | 18     | 62.5            | 0.96            | 2.8                         | 20                      |

| Layer 3 | 37     | 125.0           | 0.96            | 4                           | 20                      |

| Layer 4 | 39     | 125.0           | 0.95            | 4                           | 20                      |

| Layer 5 | 58     | 125.0           | 0.91            | 4                           | 20                      |

| Layer 6 | 60     | 125.0           | 0.90            | 4                           | 20                      |

## **Beam induced backgrounds**

## **Results of the Single Ring Scheme**

| Background<br>Type | Generators        | Sub-type               | Particle Flux at<br>VTX<br>[ $cm^{-2}BX^{-1}$ ] | Particle<br>Energy [GeV] | Priority |  |

|--------------------|-------------------|------------------------|-------------------------------------------------|--------------------------|----------|--|

| Synchrotron        | Geant4;           | Dipole                 | ~ 10 <sup>10</sup>                              | ~ 0.001                  | ***      |  |

| Radiation          | BDSIM             | Quadrupole             | ~ 10 <sup>6</sup>                               | ~ 0.007                  |          |  |

| Beam               | BBBrem;           | Radiative<br>Bhabha    | ~ 10                                            | ~ 120                    | **       |  |

| Lost Particles     | SAD               | Beam Gas<br>Scattering | t                                               | t                        |          |  |

| Peametrablung      | Guinea-           | Pairs                  | ~ 10 <sup>-2</sup>                              | ~ 0.05                   | _        |  |

| Beamstrahlung      | Pig++;<br>PYTHIA6 | Hadrons                | ~ 10 <sup>-5</sup>                              | ~ 2                      | *        |  |

- The synchrotron radiation is the most important beam induced backgrounds in the single ring scheme

- Require to reduce the critical energy and radiation power in the double ring scheme

2017-4-20

CEPC-SPPC Workshop, CCNU, Wuhan

3

Ref: Q. Xiu, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

## **Pixel sensor challenges**

- To achieve S.P. resolution

- Digital pixel ~ 16um

- Analog pixel ~ 20um (power pulsing mode in ILC)

- To lower the material budget

- Sensor thickness ~ 50um

- Heat load < 50 mW/cm<sup>2</sup> constrained by air cooling

- To tackle beam-related background

- 20us/frame?

- 300krad/year & 3×10<sup>12</sup>neq/ (cm<sup>2</sup>·year)?

| Physics driven requirements                                          | Running constraints       | Sensor specifications                          |

|----------------------------------------------------------------------|---------------------------|------------------------------------------------|

| $\sigma_{s.p.}$ 2.8um<br>Material budget 0.15% X <sub>0</sub> /layer |                           | > Small pixel 16um                             |

| Material budget 0.15% X <sub>0</sub> /layer                          |                           | > Thinning <mark>50</mark> um                  |

|                                                                      | > Air cooling             | > low power 50mW/cm <sup>2</sup>               |

| r of Inner most layer 16mm                                           | > beam-related background | > fast readout 20us?                           |

| L                                                                    | > radiation damage        |                                                |

|                                                                      |                           | ≤1 Mrad/ year ?                                |

|                                                                      |                           | $\leq 1 \times 10^{12} n_{eq} / (cm^2 year)$ ? |

Ref: Y. Lu, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

## **R&D** activities

## **Pixel sensor R&D activities**

#### **Unprecedented specifications**

- Severer low power constraint than ILD

- ILD duty cycle 1ms/199ms

- CEPC needs a reduction by a factor of 4

- > Higher s.p. resolution than ALICE-ITS upgrade

- 1/3 pixel size of ALICE pixel sensor

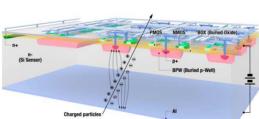

#### HR-CMOS pixel sensor

- > Towards compete CMOS & thick, fully depleted substrate

- More in-pixel functional circuitry → faster read-out & less power, radiation tolerance

- > TowerJazz CIS 0.18 µm process

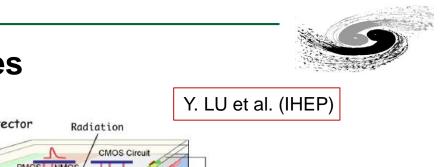

#### SOI pixel sensor

- > Fully depleted substrate: 50 µm thick, larger signal charge

- > Develop in-pixel circuit for minimum layout area

- LAPIS 0.2 µm process

11

C Rev.Hori

## **R&D** activities

- > CMOS pixel sensor

- > SOI pixel sensor

13

#### 12 October 2017, NME'2017, IHEP, Beijing

## **CMOS pixel sensor R&D activities**

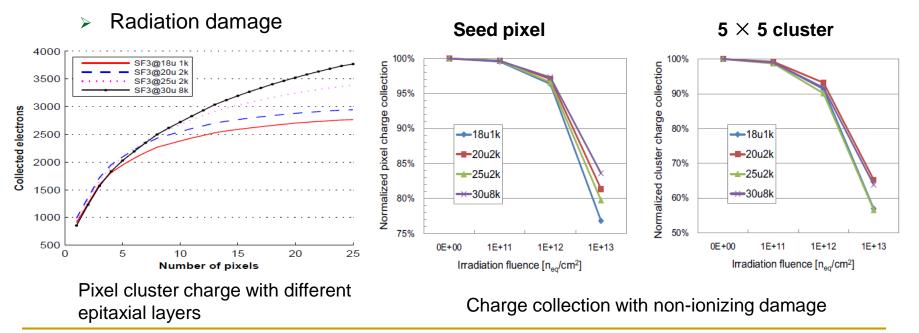

TCAD simulation on charge collection

#### First submission in Nov. 2015

- Exploratory prototype, analog pixel

- Sensor optimization and radiation tolerance study

#### Second submission in May 2017

- > Tow prototypes with digital pixels (in-pixel discriminator)

- > Tow different readout schemes: rolling shutter & asynchronous

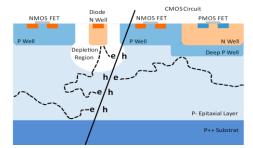

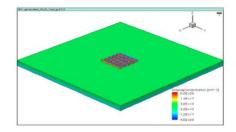

## **CPS – Charge collection simulation**

#### **Motivation:**

Y. ZHANG et al., NIMA 831 (2016) 99-104

Guide the diode geometry optimization and study radiation damage with different types of epitaxial layer

#### Simulated with different parameters

- Hit position

- Diode geometry

- > Thickness and resistivity of the epitaxial layer

12 October 2017, NME'2017, IHEP, Beijing

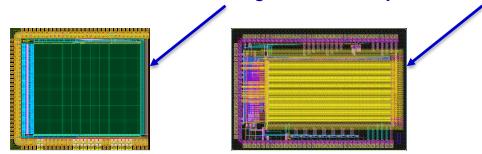

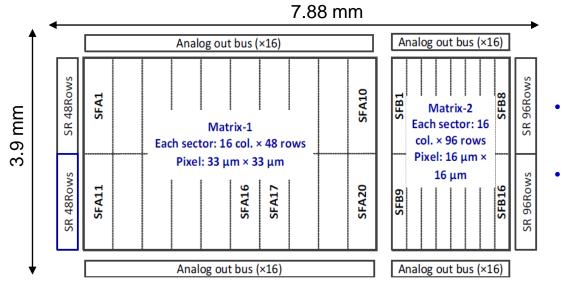

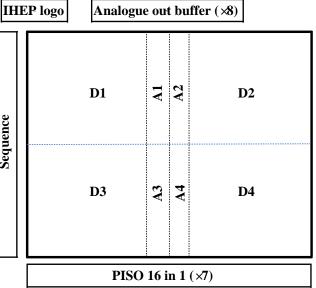

## First CPS prototype design

- Goals: sensing optimization and in-pixel pre-amplifier study

- Floorplan overview

- > Two independent matrices: Matrix-1 with  $33 \times 33 \ \mu\text{m}^2$  pixels (except one sector SFA20 with 16×16  $\mu\text{m}^2$  pixels), Matrix-2 with 16×16  $\mu\text{m}^2$  pixels.

- Matrix-1 includes 3 sectors with in-pixel pre-amplifier

- > SFA20 in Matrix-1 contains pixel with AC-coupled pixels

- TowerJazz 0.18 µm CIS process November 2015 submission

- Chip received in 2016 June, test in progress

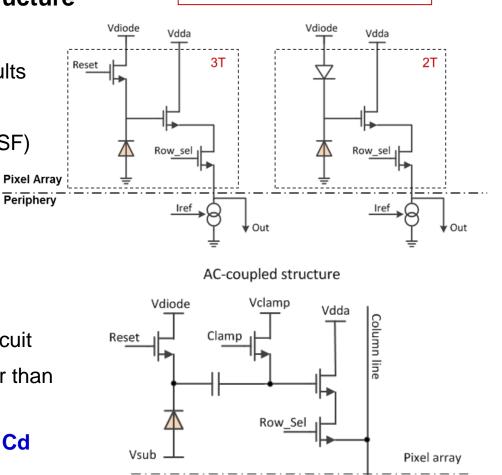

## First CPS prototype design — pixel structures

#### DC-coupled SF pixels: 2T/3T structure

- different diode geometries

- → to verify the TCAD simulation results

- > two biasing modes (2T/3T)

- > two transistor types (nmos/pmos SF)

Y. ZHANG, Y. ZHOU (IHEP)

#### AC-coupled pixel

- sensing node AC-coupled with circuit

- diode bias voltage could be higher than power supply, i.e. up to 10 V

- → larger depletion region & lower Cd

- → higher SNR

Pheriphery

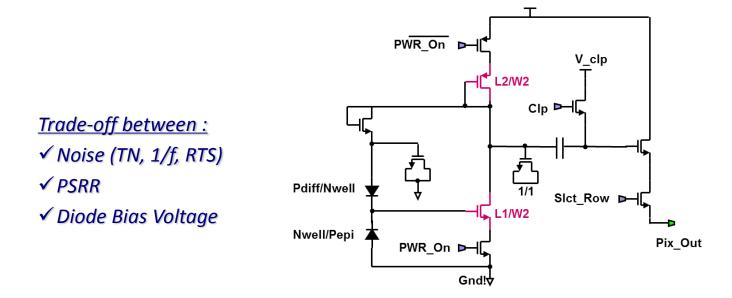

## First CPS prototype design — pixel structures

#### In-pixel pre-amplifier

- > Common source amplifier with AC feedback, CDS in pixel

- > Only active when the row is selected to be read  $\rightarrow$  power saving

- Using a twin-well process only NMOS can be used, while both types of transistors are used in our prototype

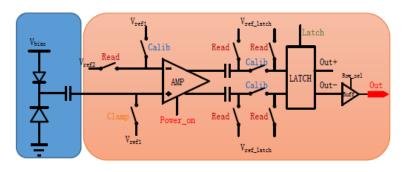

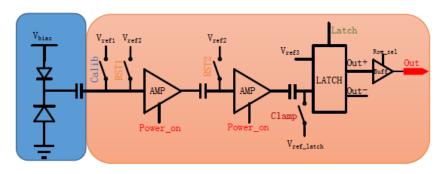

## 2<sup>nd</sup> submission – rolling shutter prototype

#### Digital pixels in rolling-shutter readout mode: 2 different versions

Version 1: differential amplifier + latch

- Same amount of transistors;

- Offset cancellation technique;

- Version 2 has higher signal gain, but suffers "more" from "Latch" input voltage distortion.

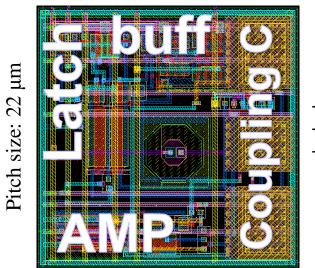

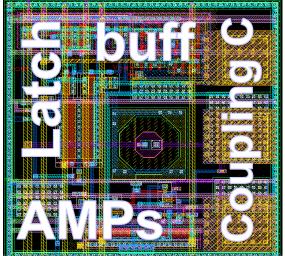

#### Version 2: two stage CS amplifiers + latch

Pitch size: 22 µm

Y. ZHOU (IHEP)

## 2<sup>nd</sup> submission – rolling shutter prototype

#### Version 1:

#### Y. ZHOU (IHEP)

Differential Amplifier Noise simulation: Input DC level: 600 mV Biasing current: 3.7  $\mu$ A Gain: 8.3 RMS noise: 1.962 mV ENC:  $\approx$  7 e<sup>-</sup> (for best case; highly relaied on the equivalent C<sub>sensing point</sub>) Readout speed: 100 ns/row

#### Version 2:

Single-end CS Amplifier Noise simulation: Input DC level: 520 mV Gain: 8 RMS noise: 1.566 mV ENC: 6.3 e- (for best case) Readout speed: 80 ns/row

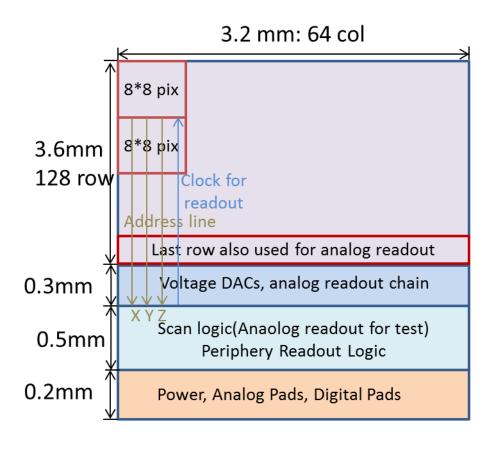

## 2<sup>nd</sup> Submission: rolling-shutter mode prototype

Y. ZHOU (IHEP)

- $-3 \times 3.3 \text{ mm}^2$ ;

- 96  $\times$  112 pixels with 8 sub-matrix

- Processing speed: 11.2 μs/frame for 100 ns/row;

- Output data speed: 160 MHz;

- Power:3.7  $\mu$ A/pixel;

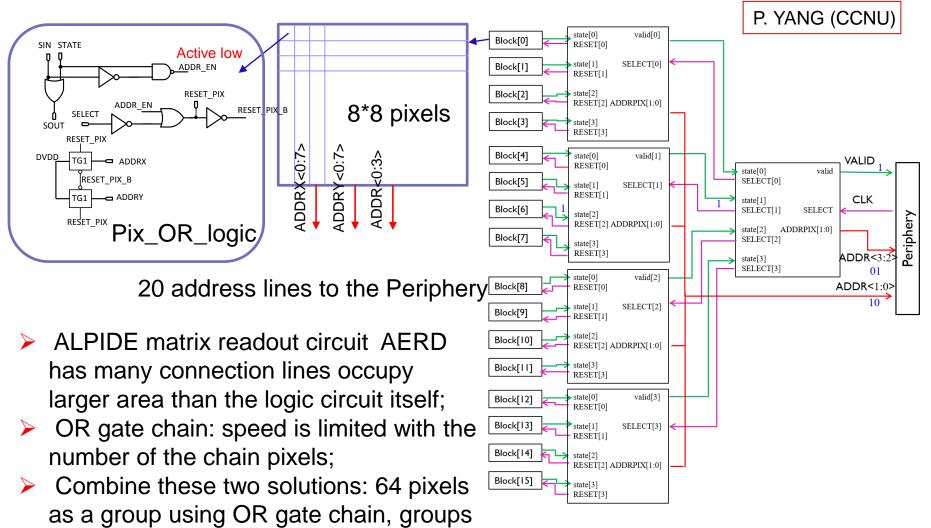

## 2<sup>nd</sup> Submission: asynchronous mode prototype

using AERD structure to readout

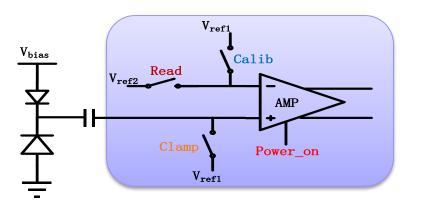

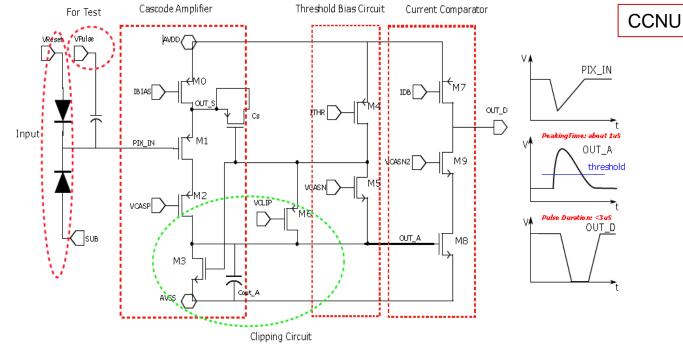

## Asynchronous mode prototype – front-end I

- Signal charge creates negative voltage step  $\Delta V_{PIX_{-IN}}$ at input node(PIX\_IN).

- From OUT\_A baseline voltage to point where discriminated output OUT\_D flips when  $I_{M8} > I_{DB}$ .

$$\Delta V_{OUT\_A} \approx \frac{C_s \bullet \Delta V_{PIX\_IN}}{C_{OUT\_A}} = \frac{C_s}{C_{OUT\_A}} \bullet \frac{Q_{in}}{C_{PIX\_IN}}$$

Simulation results

- ENC: 8 e<sup>-</sup>

- Power cons.: 61 nA/pixel

- Threshold: 140 e<sup>-</sup>

- Peaking time < 1 us

- Pulse duration  $< 3 \ \mu s$

## > Pixel size: $25 \times 25 \ \mu m^2$

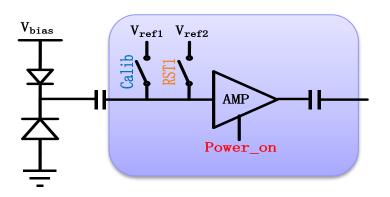

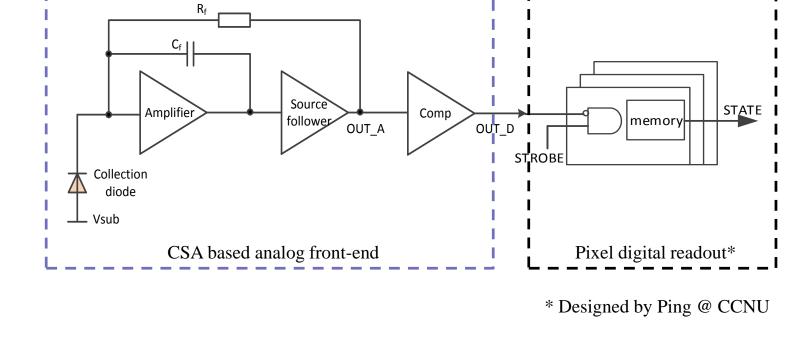

CSA based front-end circuit

Signal process chain

## Asynchronous mode prototype – front-end II

Y. ZHANG (IHEP)

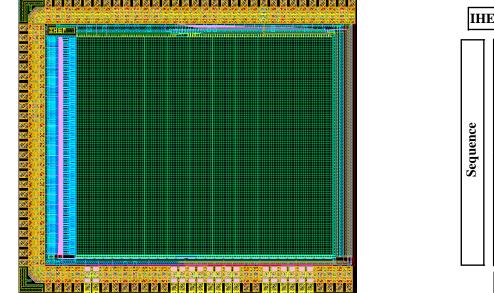

## Asynchronous mode prototype overview

MIC4 chip:

P. YANG et al. (CCNU)

- $\succ$  3.2  $\times$  3.7 mm<sup>2</sup>

- $\succ$  128  $\times$  64 pixels

- Integration time: < 5 µs</p>

- Power consumption: < 80 mW/cm<sup>2</sup>

- Chip periphery

- Band gap

- Voltage DAC

- Current DAC

- LVDS

- Custom designed PADs

## **R&D** activities

- > CMOS pixel sensor

- SOI pixel sensor

## SOI pixel sensor R&D activities

#### INTPIX2P5 prototype for the sensor depletion study, 2015

- Fully depleted around 190 V

- Seed/cluster ration decrease with V<sub>bias</sub>

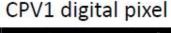

#### CPV prototypes for CEPC

- > CPV1/2, 2015/2016

- > Small pixel size, 16 μm pitch

- Focus on Sensing diode + Front end

- Digital pixel (in-pixel hit discrimination)

## SOI pixel sensor R&D activities

Y. LU et al. (IHEP)

#### A comparison of digital pixels

|                      | ASTRAL                             | ALPIDE                                                                 | CPV                                     |

|----------------------|------------------------------------|------------------------------------------------------------------------|-----------------------------------------|

| Process technology   | 0.18 µn                            | 0.2 <i>µm</i> SOI                                                      |                                         |

| Readout strategy     | Rolling shutter                    | asynchronous                                                           | Rolling shutter                         |

| Readout time         | 20 µs                              | <2 µs                                                                  |                                         |

| Power                | 85 mW/cm <sup>2</sup>              | 39 mW/cm <sup>2</sup>                                                  | Analog power<br>< 10 mW/cm <sup>2</sup> |

| Pixel size           | $22 \times 33 \ \mu m^2$           | $28 \times 28 \ \mu m^2$                                               | $16 \times 16 \mu m^2$                  |

| Spatial resolution   | atial resolution $\approx 5 \mu m$ |                                                                        |                                         |

| Total signal for MIP | ≈ <i>1200 e⁻ (20µm</i> epi-l       | <pre>≈4000 e<sup>-</sup> (back thinning to 50µm, fully depleted)</pre> |                                         |

- Unique opportunity to explore very compact pixel circuit

- 3 times larger MIP signal

- Possibly smaller cluster size

Ref: Y. Lu, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

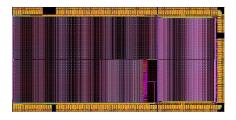

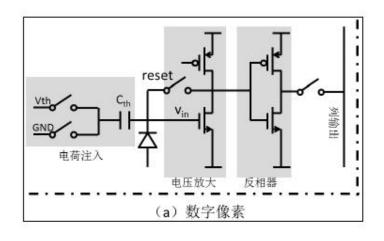

## **First SOI pixel prototype**

- First digital pixel of 16um pitch

- CS voltage amplifier, gain ~ 10

- Inverter as discriminator

- Threshold charge injected to sensing node

- Pixel array: 64\*32 (digital) + 64\*32 (analog)

- Double-SOI process for shielding and radiation enhancement

- Submitted June, 2015

Ref: Y. Lu, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

## Y. LU et al. (IHEP)

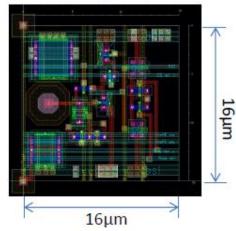

## First SOI pixel prototype

## Single pixel test

- Chip circuit function verified on single pixel

- Voltage gain of amplifier ~ 10  $\,$

- Threshold scan

- Temporal noise ~ 50e<sup>-</sup> (< 20 e<sup>-</sup> expected)

- Bias voltage not applicable due to a design fault

- Diode capacitance 3 times larger

Ref: Y. Lu, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

#### Y. LU et al. (IHEP)

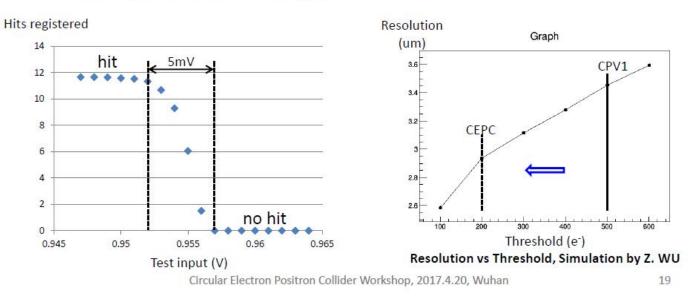

## Second SOI pixel prototype design

- Protection diode added

- Enable full depletion on sensor

- In-pixel CDS stage inserted

- improve RTC and FPN noise

- replace the charge injection threshold

- Submitted June, 2016

Ref: Y. Lu, Circular Electron Positron Collider workshop, Wuhan, April 19-21, 2017.

## Summary and outlook

- Pixel sensor is the core component for VTX

- R&D started along the physics driven requirement

- > Running constraints not settle yet

#### CMOS pixel sensors prototypes

- Exploratory prototype under test

- 2<sup>nd</sup> CPS submission under fabrication, targeting on highly compact digital pixels and fast readout development

#### Two compact SOI pixel sensor prototypes

- Fully depletion of SOI verified

- Circuit function verified on single pixel

- Evaluation of digital pixel array underway

- Optimization study of vertex system needed

#### Possible change of sensor design

- > Beam related background level

- > Impact of partial-double ring scheme, with time-stamp of microsecond

## Thanks for your attention !