Digital Design and Verification of the Front-end readout chip of ITk Strip for ATLAS Phase II upgrade

> Weiguo Lu On behalf of ITk Strip ASIC community Dec. 8, 2017

## Outline

- Star chips for ITk strip upgrade

- New design features of ABCStar

- Functional Verification

- Other blocks and current status

#### Star chips for ITk strip upgrade

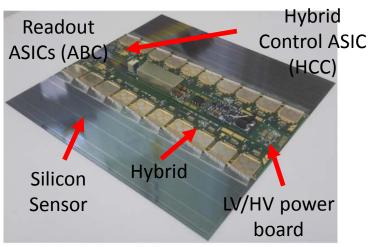

## Star chips for ITk Strip

- Challenge for ITk Strip upgrade

- Higher luminosity , finer granularity, larger scale, harsher radiation...

- Chip set on module

- ABC--ATLAS Binary Chip

- HCC--Hybrid Control Chip

- Interface for higher trigger rate

- Increased trigger rate->1MHz L0

- shorter latency

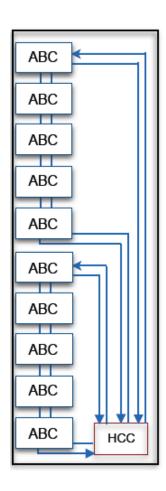

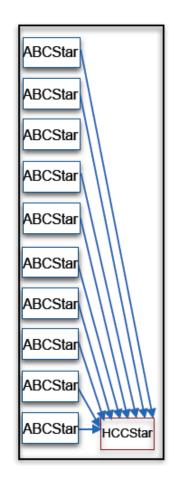

- From serial transfer to star connection

#### New design features of ABCStar

#### **ABCStar ASIC**

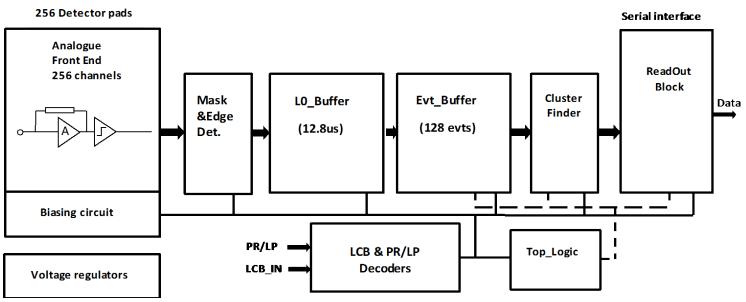

- It uses the standard binary readout architecture

- Data path: amplifier, discriminator, input register block, pipeline, event buffer and a cluster algorithm to compress data for output

- It is being designed to support various trigger modes

- It will be built in GF130nm technology

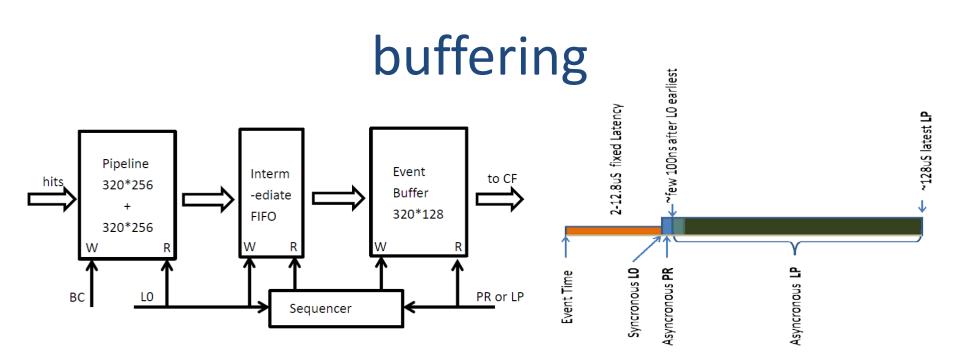

- The two stage buffers: Pipeline(LOBuffer) and EvtBuffer

- Transfer **1** event per LO from Pipeline to EvtBuffer(instead of 3)

- Less RAM

- Simpler logic

- Modification of buffer size

- Pipeline(LOBuffer)extended to 512bit length

- EvtBuffer reduced to 128bit length(128 events)

- Basic memory IP: single port RAM+ in case of consecutive LOs

- -->Intermediate FIFO to give the priority to EvtBuffer read operation

#### Data compression

ABC130

ABCStar

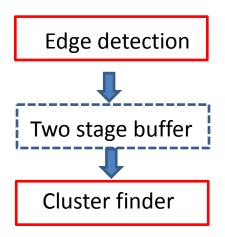

- Edge detection circuit before pipeline

- Extract only the leading edge information

- To compress the data in terms of time by factor of 2

- Cluster finder after eventbuffer

- Data reduction in terms of space, creating a cluster byte for channels found with hits

- takes in 256 bits of strip data and reports out 12 bit clusters at 40MHz

## Priority readout

| • | Physics data                                                                                                                                                                                                                                                        |      |                              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|

|   | <ul> <li>PR trigger has higher priority over LP trigger</li> </ul>                                                                                                                                                                                                  | high | HPR                          |

| • | Register readback                                                                                                                                                                                                                                                   |      |                              |

|   | <ul> <li>32 positions Register Data FIFO</li> </ul>                                                                                                                                                                                                                 |      | PR                           |

|   | <ul> <li>Two cases of conditions independent of read<br/>register command</li> </ul>                                                                                                                                                                                |      |                              |

| ٠ | HPR                                                                                                                                                                                                                                                                 |      | LP                           |

|   | <ul> <li>The content of the 32 bits register called "HPR"</li> </ul>                                                                                                                                                                                                |      | L)                           |

|   | (for High Priority Register) is transmitted<br>periodically after powerup, a HardReset, or a<br>RegisterReset fast command, or in case of the<br>lcb_lock bit being false, indicating the LCB circuit<br>has lost its synchronization with the LCB signal<br>frame. | low  | Regular register<br>readback |

| • | Tonlogic                                                                                                                                                                                                                                                            |      |                              |

- TopLogic

- Sequencer for the control of EvtBuffer, ClusterFinder and ReadOut

## interface

- LCB

- The LOA/CMD/BCR signal transfers triggers (LOA), fastcommands, register read-writes (CMD) and bunch-counter-reset (BCR) to the HCCStar and then onto the ABCSTAR

- The signal is 6b8b encoded and sent at 160Mbps over an LVDS bus

- 16 bits frame extending over 4BC

- Data packets

- 68 bits fixed length readout packet format

- 160Mb/s readout rate was rather chosen to reduce the transmission latency for L1-track

| Start<br>Bits | Header | Payload | Trailer |

|---------------|--------|---------|---------|

| 3             | 16     | 48      | 1       |

## Robust design

- LOtag insertion in LCB

- Improve reliability by remove sensitive LOID counter

- Deglitcher for external asynchronous resets

- Radiation hard design

- TMR for key logic and registers

- Hamming coded state machine

### **Functional Verification**

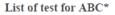

### UVM setup

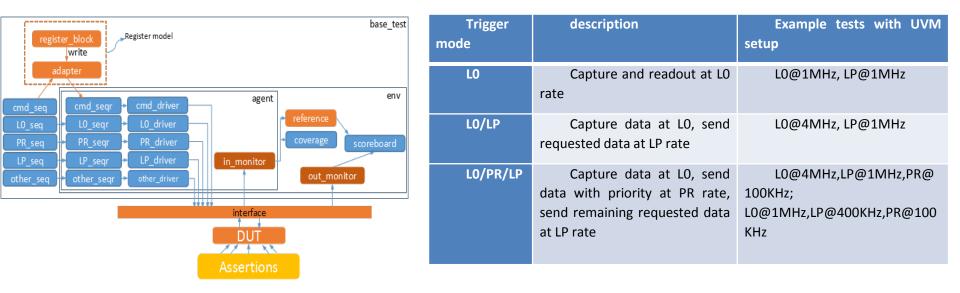

- A top verification setup based on (UVM)Universal Verification Methodology was built for ABCStar.

- Functional coverage with customized random stimulus

- Result comparison with reference model through scoreboard

- SystemVerilog assertions for validating key design features

- to verify the current design under several possible trigger conditions

- different rate, latency and distribution model of triggers

### SystemVerilog setup

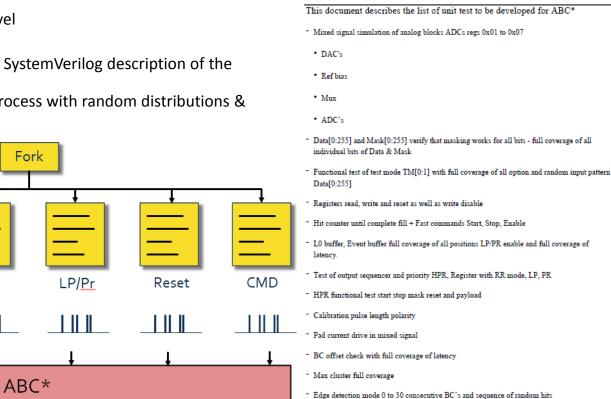

- Unit tests .

- **RTI** level tests

- Done at the module level

- Directed random tests

256 ch

- ABCStar golden model, SystemVerilog description of the \_ **ABCStar specs**

- Independent parallel process with random distributions & \_ payloads.

Lo

BCR

#### Other blocks and current status

## Analog frontend

# Supporting blocks

- Power options for TID current bump mitigation

- extend the range of digital voltage regulator, lower voltage down to 1 volt for the digital part

- eFuse for chip identification

- an individual chip identifier programmed with eFuses

- Analogue monitor of voltage and temperature

- an analogue monitor circuit like in the HCC to measure regulated VDDs, and temperature

### Pads and layout

### Summary

- In order to meet new challenges, many new features are adopted for ABCStar design, especially in the digital part

- rtl designs are close to the end, a lot of verification work ahead

- Analog blocks almost fixed, the layout has started

## Thanks for your attention !