## **Status of digital pixel**

Tianya Wu **CEPC MOST2** Chips Meeting twu@ifae.es 17-09-2019

CENTRAL CHINA NORMAL UNIVERSITY

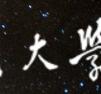

## Verification of solution of FE-I3 high-z

This is the schematic level simulation of FE-I3, the top one connected the pull-up cell without controlling signal, address encoder will be a refresh to the high level before next hit.

The bottom one connect the pullup cell with the FASTOR as the controlling signal. The final hit will be last for 21ns more after FASTOR shut down.

The static current of digital pixel is 18.6nA. And it is 1.447uA for address encoder. Total static power dissipation is 3.4mW/cm2

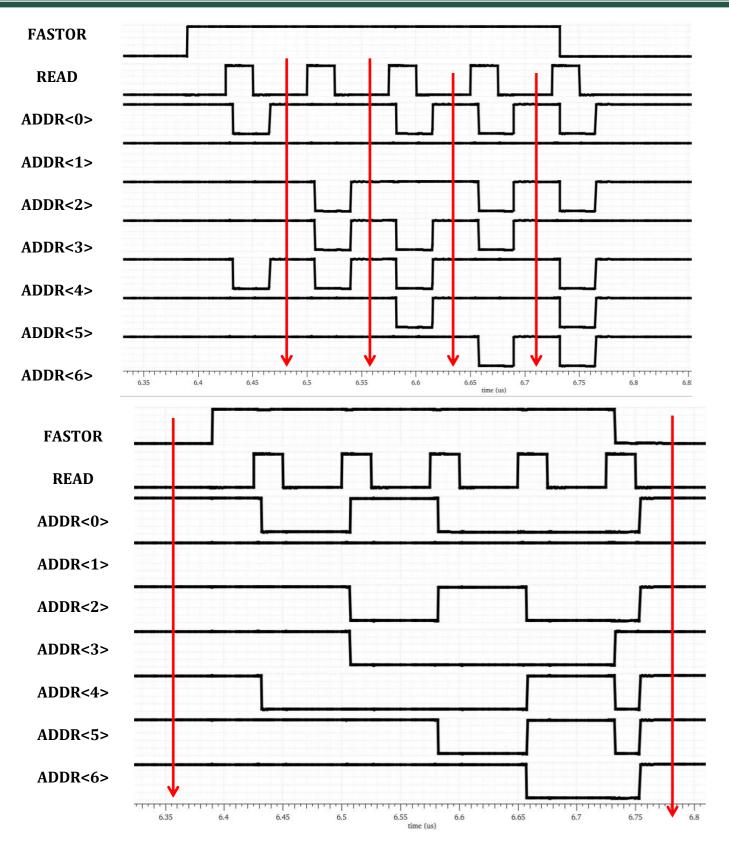

## Verification of solution of ALPIDE high-z

| 1.37V  | ADDR=1 | 1.39   |

|--------|--------|--------|

| 1.37V  | ADDR=0 | 1.39V  |

| 4.99uA |        | 1.71uA |

|        |        |        |

This is the schematic level simulation of ALPIDE, the top one connected the pull-up cell only before the buffer. The voltage level of ADDR not stable, but the current is under control.(within 3uA)

The bottom one add the extra pull up cell after the buffer. And the voltage level of ADDR keeps at 1.4V.

The static current of digital pixel is around 1.7uA. Total static power dissipation is 3.96mW/cm2

## Thanks for your attention.

4