# **Sci-W ECAL Status for CEPC**

#### Yunlong Zhang

#### State Key Laboratory of Particle Detection and Electronics, China

University of Science and Technology of China

On behalf of CEPC Calorimeter working group

# Outline

# Motivation

# CEPC ECAL Status

- Absorber optimization

- ➤Two layers prototype assembly and test

- ➤ECAL prototype

- > Summary

# **PFA Calorimeter**

- ➤ Challenges

- ➢ High granularity ₅

➤ ECAL ~10 million channels

- Compact design

- ≻ High power

- ► ECAL about 100 kW

- EBU: 80 kW (without power pulsing)

- ≻ DIF: 20 kW

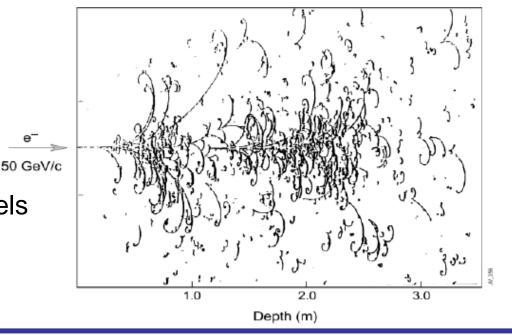

Big European Bubble Chamber filled with Ne:H $_2$  = 70%:30%, 3T Field, L=3.5 m, X $_0$  $\approx$ 34 cm, 50 GeV incident electron

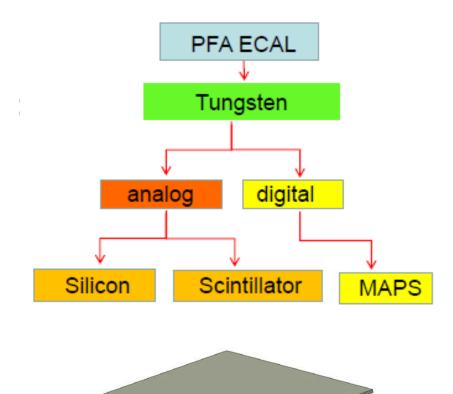

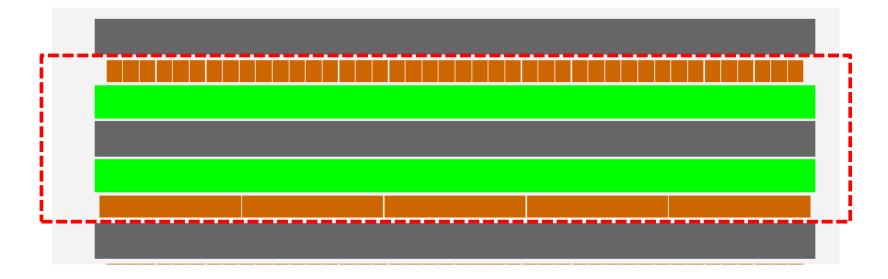

# Sci-W PFA ECAL of CEPC

- Sampling Calorimeter

- Sandwich structure

- Absorber+SD+Electronics

- Absorber

- Tungsten

- Sensitive Detector

- Scintillator+SiPM

- Electronics

- ASIC Chip

4

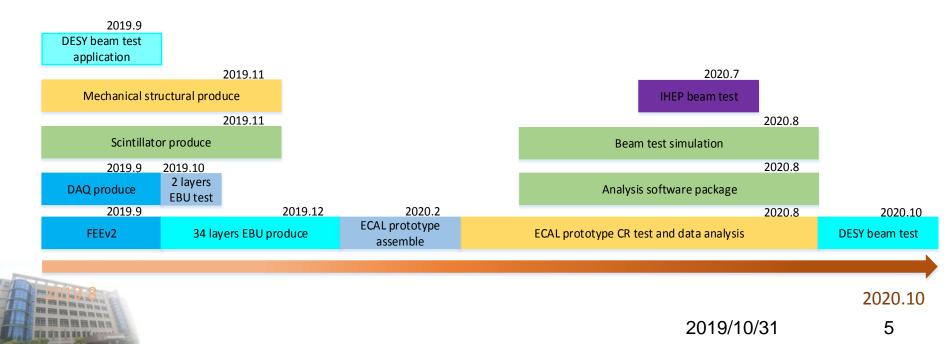

- According to the MOST funding task, a prototype should be assembled in the beginning of next year (2020.2)

- Then the cosmic ray test in laboratory and Beam test in IHEP and DESY respectively.

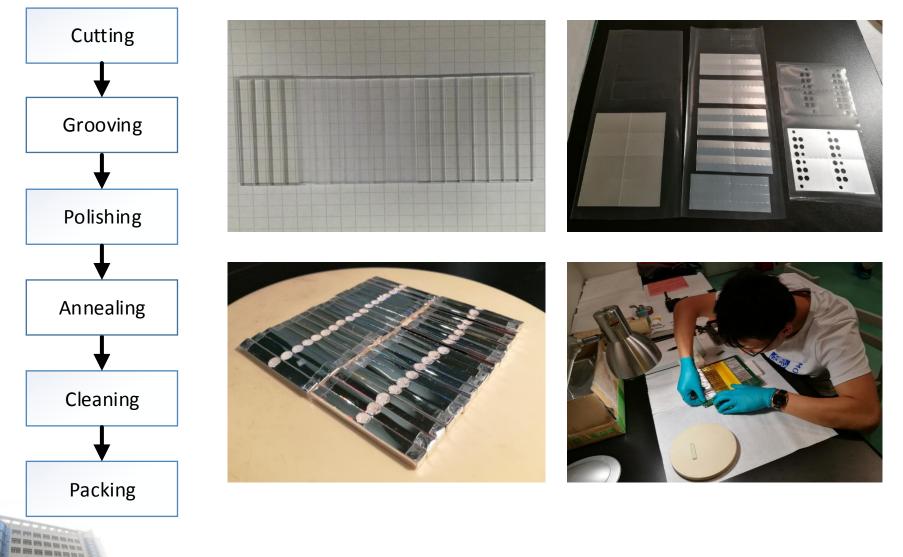

#### **Elements of ECAL**

Scintillator (5mm\*45mm\*2mm)

SiPM (1mm \* 1mm, 10k pixels)

- Dynamic range: ~100fC~200pC

- channels: 36

- Dead time: 2ms

- Polar: positive

- power: 8mW/channel

> All of the elements and materials of the ECAL were arrival

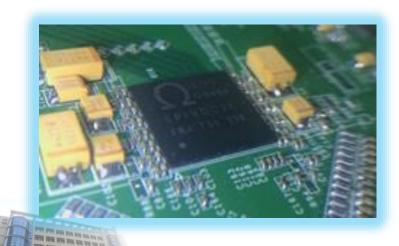

- Plastic scintillator, SiPM, SPIROC chips and others...

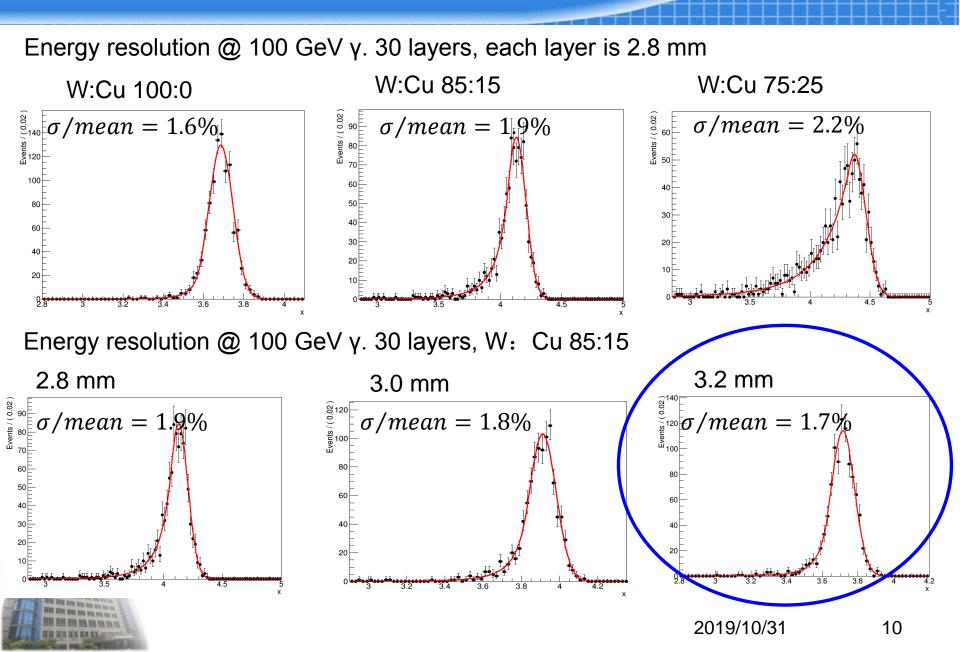

- Plastic scintillator strips production

- About 1,000 plastic scintillator strips were produced now

- $\succ$  7, 000 strips will be produced in the end of Nov.

- 35 Electronics boards were produced last week. 32 layers will be welded in the end of Nov.

- The supporting mechanical design was discussed several times and one layer was prepared for trial assembly

# Outline

# > Motivation

# CEPC ECAL Status

#### Absorber optimization

➤Two layers prototype assembly and test

➢ECAL prototype

> Summary

2019 Joint Workshop on Future ct Factory, Moscow

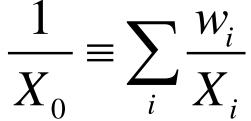

#### **Absorber parameter**

- In the previous design, the thickness of tungsten is 2.8 mm (0.8  $X_0$ ) each layer

- Considering the tungsten is very hard, not easy to punch

- Use the W-Cu alloy instead

| W:Cu                | 100:0 | 85:15 | 75:25 |

|---------------------|-------|-------|-------|

| X <sub>0</sub> (mm) | 3.5   | 4.4   | 5.1   |

#### **Absorber parameter**

# Outline

# > Motivation

# CEPC ECAL Status

>Absorber optimization

Two layers prototype assembly and test

ECAL Prototype

> Summary

2019 Joint Workshop on Future ct Factory, Moscow

### **Prototype assembly**

### **Prototype assembly**

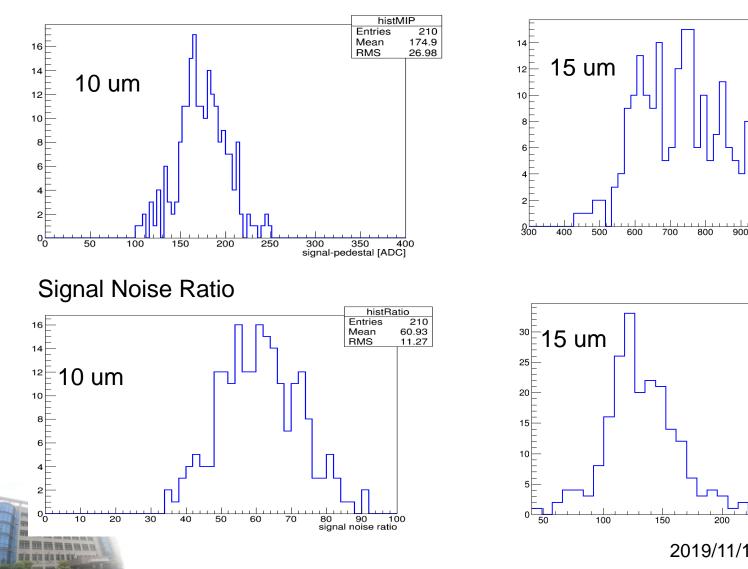

• EBU V2.1

- Two layers were assembled with 2 different type SiPM.

- S12571-010P, 10000 pixels, 10 um, PDE: 10%

- S12571-015P, 4880 pixels, 15 um, PDE: 25%

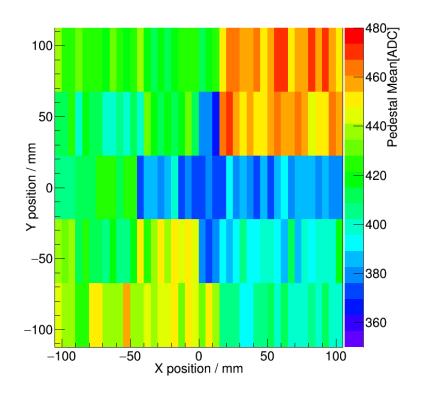

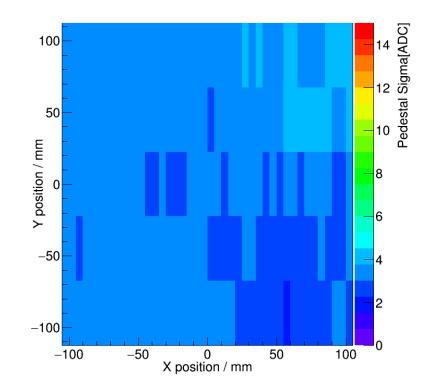

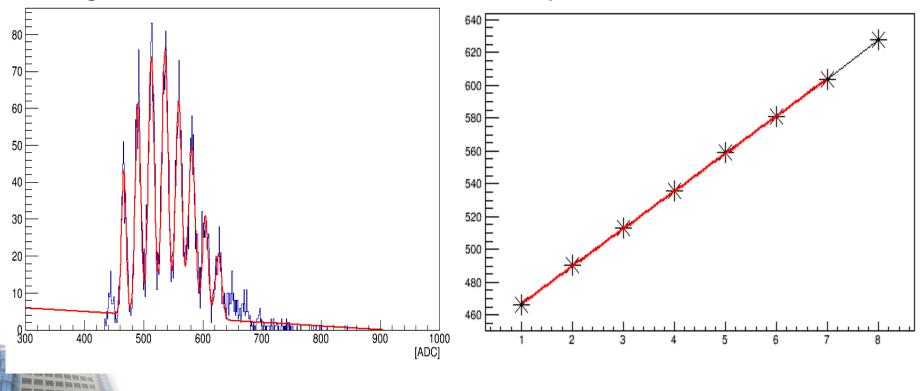

#### pedestal

**Pedestal Position**

Pedestal width

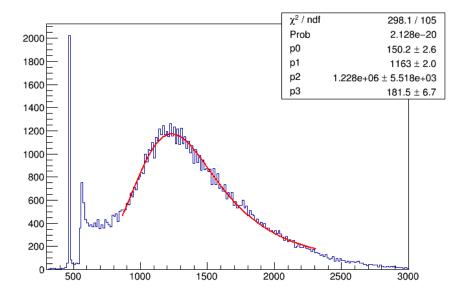

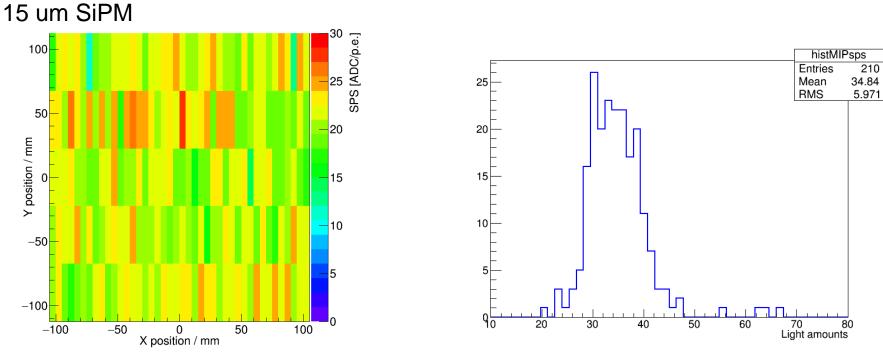

#### **MIPs response**

10 um SiPM

15 um SiPM

#### **MIPs response**

#### MIPs amplitude of each layer

300

histMIP

1200

histRatio Entries

210

135.1

34.03

210

737.5

126.3

Entries

Mean

RMS

800

200

900

1000 1100

signal-pedestal [ADC]

Mean

RMS

LED calibration system in electronics board could be used to calibrate the SPE of SiPM. If the gain of SiPM is good enough, the SPE could be seen clearly.

# **LED** calibration

SPE amplitude of each channel

Light yield of MIPs

The scintillator coupled with 15 um SiPM, light yield is about 35 p.e. /MIP

# Outline

# > Motivation

# CEPC ECAL Status

≻Absorber optimization

>Two layers prototype assembly and test

#### ➤ECAL prototype

# > Summary

2019 Joint Workshop on Future ct Factory, Moscow

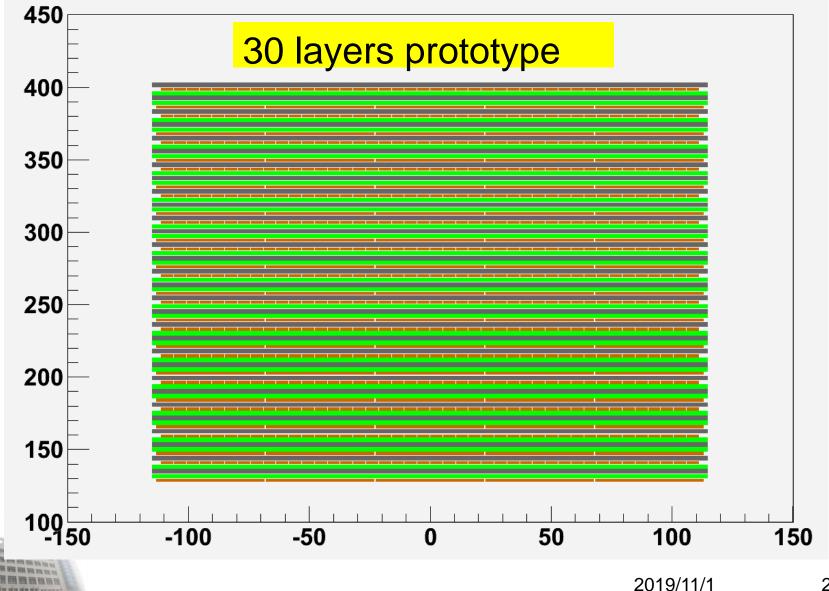

# **ECAL** prototype

PCB

### **ECAL prototype**

21

# **ECAL prototype**

hh1

15 Layers

2019/11/1

500

22

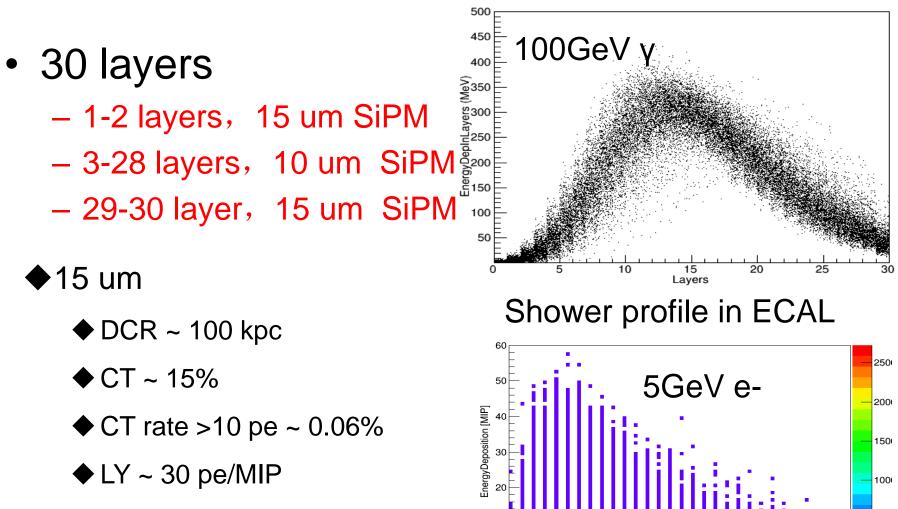

Thr > 10 pe or more

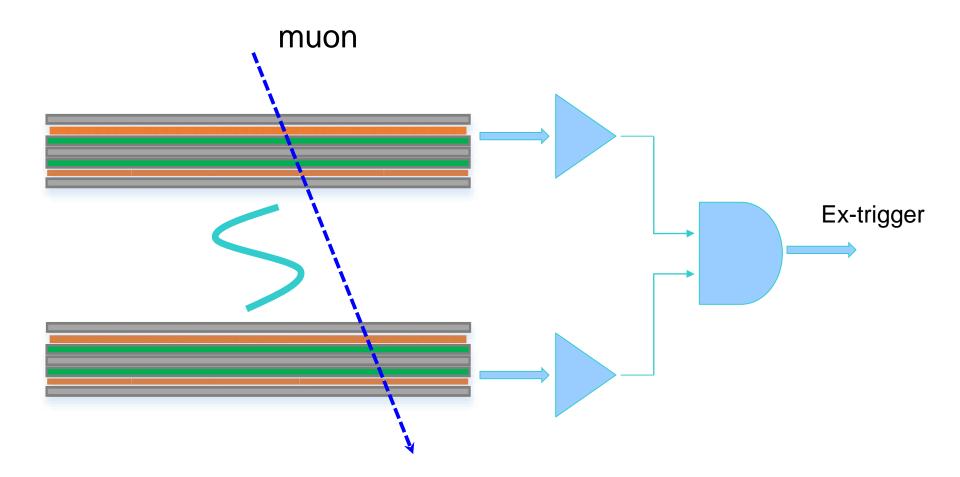

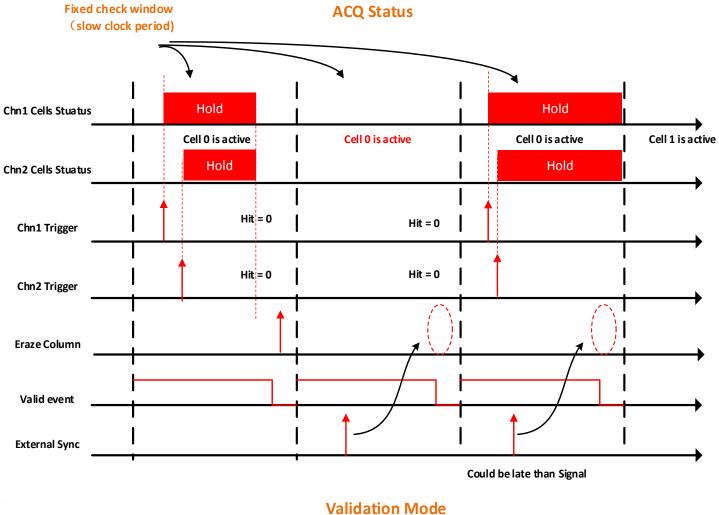

# ECAL test trigger

# **ECAL trigger**

24

- All the elements and materials are prepared

- Electronics boards are ready

- Two layers were assembled and tested. The operation are well.

- 30 layers will be started to assemble in Nov.