中國科學院為能物服為完備 Institute of High Energy Physics Chinese Academy of Sciences

# Development of TaichuPix prototypes for the CEPC vertex detector

**Zhang Ying**

# On behalf of the CEPC MOST2 Vertex detector design team 2021-8-17

# Outline

- Project motivation and TaichuPix chip overview

- Small scale prototypes design and test results

- Full size chip design

- Summary

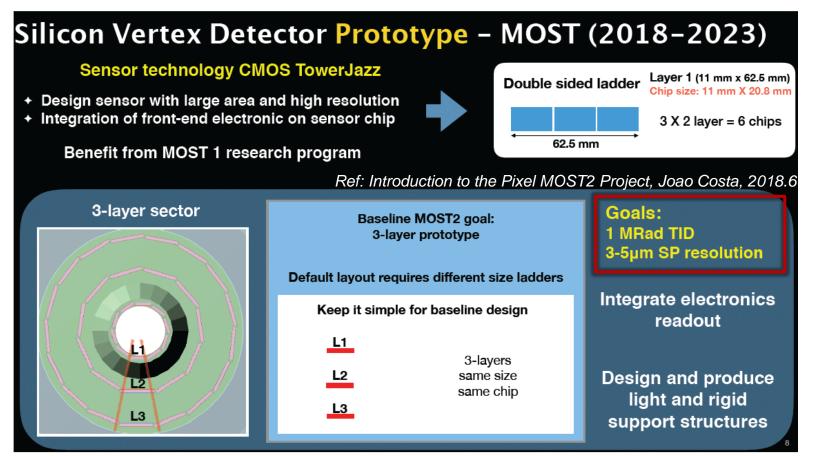

# **MOST2** project requirements on pixel chip

## Motivation for TaichuPix chip design

- > Large-scale & full functionality pixel chip

- Fit to be assembled on ladders with backend Elec. & DAQ

## Main specs of the full size chip for high rate vertex detector

## Bunch spacing

- Higgs: 680 ns; W: 210 ns; Z: 25 ns

- Meaning 40M/s bunches (same as the ATLAS Vertex)

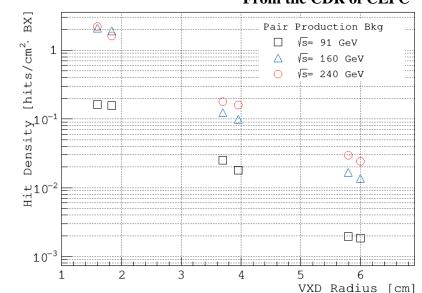

## Hit density

2.5 hits/bunch/cm<sup>2</sup> for Higgs/W; 0.2 hits/bunch/cm<sup>2</sup> for Z

## Cluster size: 3pixels/hit

- > Epi-layer thickness: ~18 μm

- > Pixel size:  $25 \ \mu m \times 25 \ \mu m$

#### From the CDR of CEPC

CP

| For Vertex  | Specs    | For High rate<br>Vertex | Specs                                            | For Ladder<br>Prototype | Specs                                     |

|-------------|----------|-------------------------|--------------------------------------------------|-------------------------|-------------------------------------------|

| Pixel pitch | <= 25 µm | Hit rate                | 120 MHz/chip                                     | Pixel array             | 512 row × 1024 col                        |

| TID         | >1 Mrad  | Date rate               | 3.84 Gbps<br>triggerless<br>~110 Mbps<br>trigger | Power<br>Density        | < 200 mW/cm <sup>2</sup><br>(air cooling) |

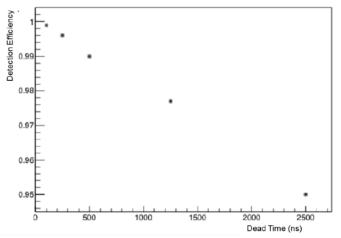

|             |          | Dead time               | < 500 ns<br>for 98% efficiency                   | Chip size               | ~1.4 cm×2.56 cm                           |

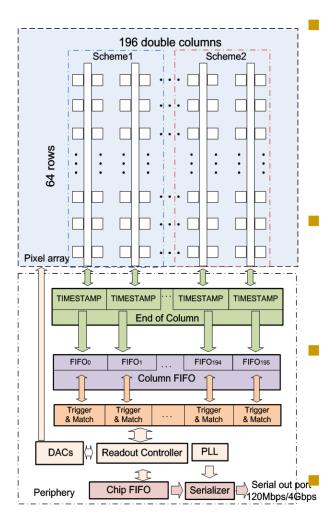

# **TaichuPix architecture**

## Similar to the ATLAS ITK readout architecture: "column-drain" readout

- > Priority based data driven readout, zero-suppression intrinsically

- Modification: time stamp is added at EOC whenever a new fast-or busy signal is received

- > Dead time: 2 clk for each pixel (50 ns @40MHz clk)

## Two parallel pixel digital schemes

- > ALPIDE-like: Readout speed was enhanced for 40MHz BX

- FE-I3-like: Fully customized layout of digital cells and address decoder for smaller area

## 2-level FIFO architecture

- > L1 FIFO: In column level, to de-randomize the injecting charge

- L2 FIFO: Chip level, to match the in/out data rate between the core and interface

## Trigger readout

- > Make the data rate in a reasonable range

- > Data coincidence by time stamp, only matched event will be readout

# Outline

- Project motivation and TaichuPix chip overview

- Small scale prototypes design and test results

- Full size chip design

- Summary

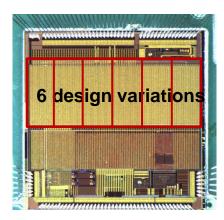

# TaichuPix small prototypes overview

TaichuPix-1 Chip size: 5 mm  $\times$  5 mm Pixel size: 25  $\mu$ m  $\times$  25  $\mu$ m

$\begin{array}{l} \mbox{TaichuPix-2} \\ \mbox{Chip size: 5 mm} \times 5 \mbox{mm} \\ \mbox{Pixel size: 25 } \mbox{\mu m} \times 25 \mbox{\mu m} \end{array}$

## Two MPW chips were fabricated and verified

- > TaichuPix-1: 2019.06~2019.11

- TaichuPix-2: 2020.02~2020.06

## Chip size 5 mm×5 mm with standalone features

- In-pixel circuitry:

- Continuously active front-end

- Two digital schemes, with masking & testing config. logics

- > A full functional pixel array (64×192 pixels)

- Periphery logics

- Fully integrated logics for the data-driven readout

- Fully digital control of the chip configuration

- > Auxiliary blocks for standalone operation

- High speed data interface up to 4 Gbps

- On-chip bias generation

- Power management with LDOs

- IO placement in the final ladder manner

- Multiple chip interconnection features included

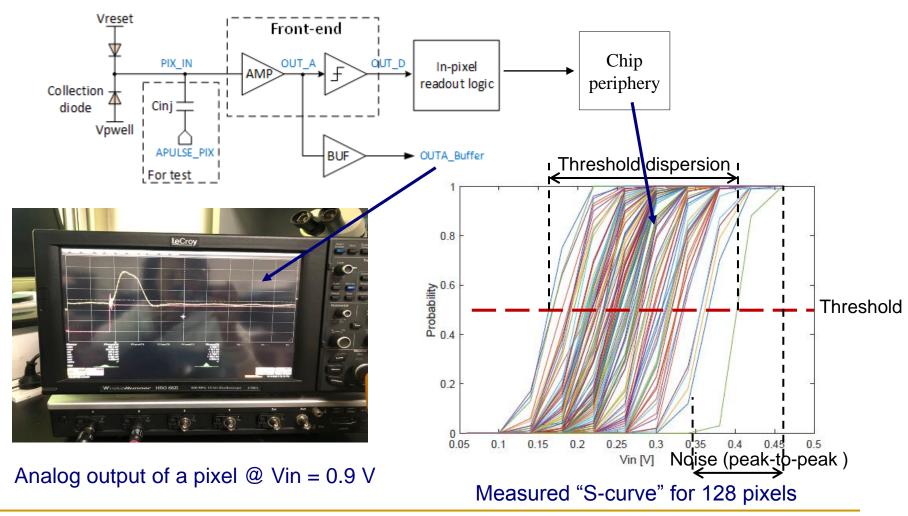

# **Electrical test**

Electrical performance verified by injecting external voltage pulses into pixel front-end

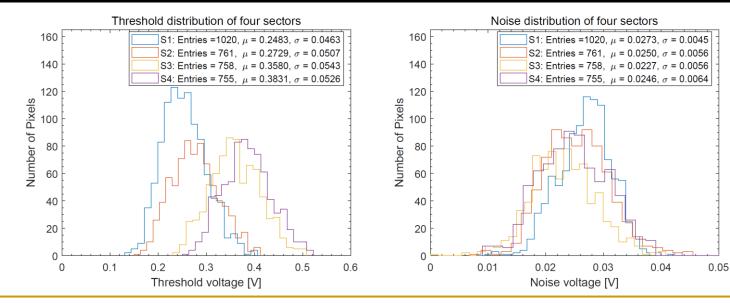

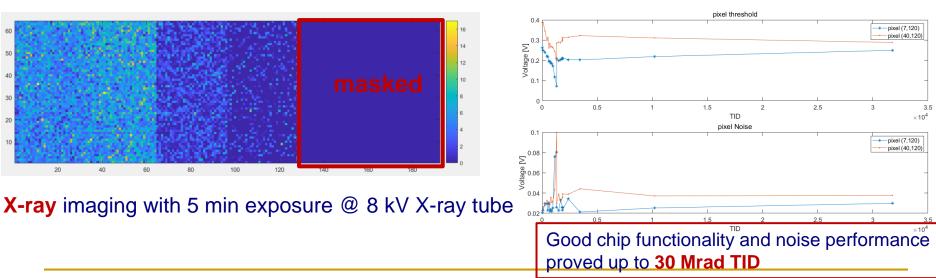

# Performance of threshold and noise of TaichuPix2

## Bias setting: ITHR = 6.2 nA, VSUB = 0 V

> Threshold can be tuned by changing ITHR (a global current bias)

| Chip4 | Threshold Mean<br>(e-) | Threshold<br>rms (e-) | Temporal<br>noise (e-) | Total equivalent<br>noise (e-) |

|-------|------------------------|-----------------------|------------------------|--------------------------------|

| S1    | 272.9                  | 50.9                  | 30.0                   | 59.1                           |

| S2    | 299.9                  | 55.7                  | 27.5                   | 62.1                           |

| S3    | 393.4                  | 59.7                  | 24.9                   | 64.7                           |

| S4    | 421.0                  | 57.8                  | 27.0                   | 63.8                           |

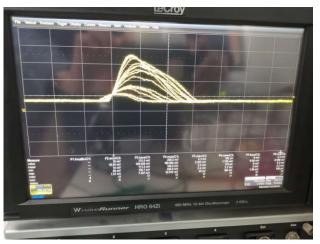

# **TaichuPix response to radioactive**

Functionality of TaichuPix1&2 proved by various tests

Analog output of a pixel response to X-ray tube

第十三届全国粒子物理学术会议, 2021-8-17

#### OUTA under Sr-90 injected 1.6r 1.5 1.4 1.3 OUTA(V) 1.2 1.1 0.9 0.8 -0.2 -0.1 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0 Time [s]

### Analog output with <sup>90</sup>Sr exposure

# Outline

- Project motivation and TaichuPix chip overview

- Small scale prototypes design and test results

- Full size chip design

- Summary

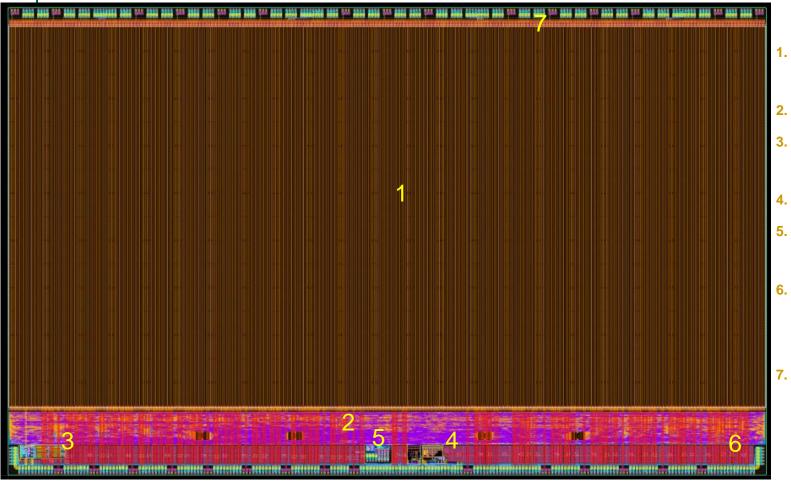

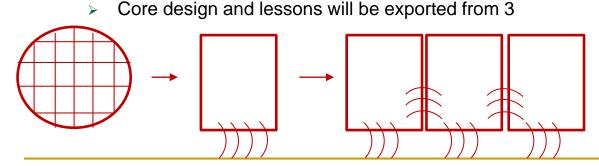

# Overview of the full size engineering run

- Pixel array 1024\*512

- 2. Periphery

- DAC & Bias generation

- Data interface

- 5. LDO (test blocks)

- Chip interconnection features

- Scribe-able top power connection features

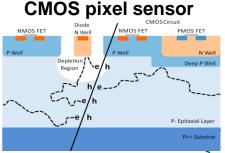

- Process: 180 nm CMOS Imaging Sensor process (7 metal layers)

- Pixel cell copied exactly from MPW + scaled logic with new layout

Periphery + debugged/improved blocks + enhanced power network

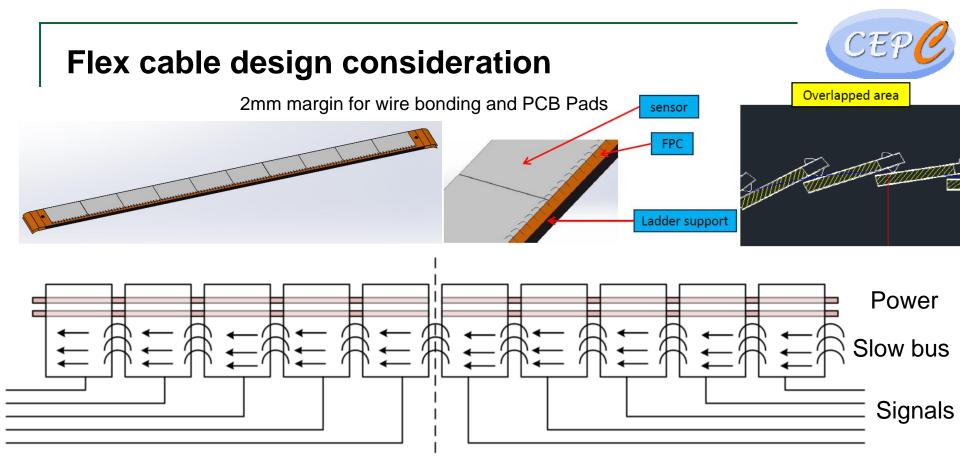

### Design goals & considerations for the Flex PCB

- Minimum material budget

- Minimum dead zone extension, limited height of PCB

- Minimum set of signals on Flex

- Slow buses to go on chip area by chip interconnection buses

- Robust power supply

- Manufacturability

# CEPC

# Testability design & test plan consideration

- All test features reserved, while the connected IOs will decrease at diff stages depending on chip test & study results

- > Analog probe signals at the top part, accessible from the top pads

- > When mounted on ladder, only minimum self test possibilities can be reserved

### 1. Probe Card design for the wafer test

For all the pads at both sides

### 2. Single chip test board design

> Designed with all the test features for the chip functional study

### 3. Multiple chip test board for the ladder debugging

- > Designed following the same manner as the ladder but on PCB

- > Signals and power supplies will be limited just with the ladder's dimension

- > Extra test signals can be connected to the extended area, to help debugging

## 4. The real flex cable design for the ladder

# Summary

- TaichuPix small prototypes were fully verified and preparing to submit the full size tape-out

- > Full signal chain & functionality verified with both electrical & radioactive test

- > TID performance satisfied with CEPC's requirement with a large headroom

- > Full size chip design finished

## Recent plan

- > Design will be submitted for the engineering run

- > Preparation for the chip test (probe card, test PCB, flex cable ...)

## Thank you for your attention!

# Backup

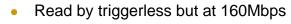

# **Chip Power consuming test**

- The EMMI (Emission Microscope) test showed the hot points were exactly as expected

- > quiet pixel array & periphery = no leakage point

- CEP

- Tcpx2 chip current consuming tested of 210mA (380mW@1.8V)

- Almost agreed with simulation

- > PLL@trigger speed: 306mW

- Read by triggerless but at 160Mbps

- Two PLLs in Tcpx2

- Analog biased at fastest: 15mW (192\*64 pixel array)

- With 16 probe buffers

- > Periphery@trigger speed: 90mW

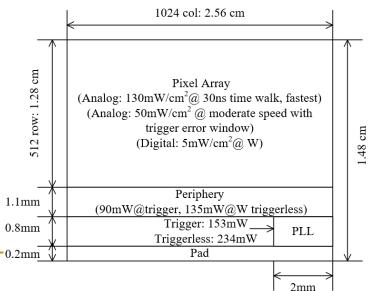

# **Full size chip dimension**

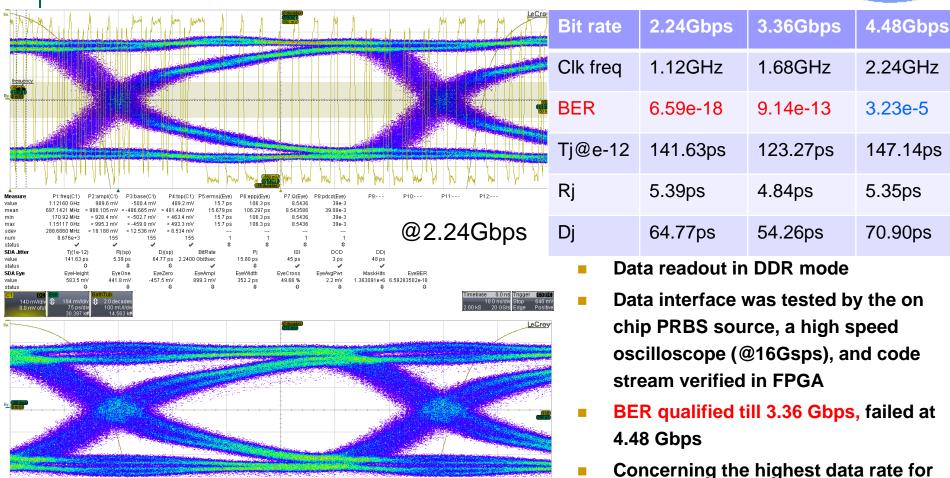

# Test of the data interface

Measure

value

mean

max

sdev

num

status SDA Jitte

value

status

value

SDA Eve

P1:freg(C1)

255.2 MHz

1 8142 GHz

14.389e+3

Tj(1e-12)

123.27 ps

EveHeight

479.8 mV

447.550 MHz

1 1076 GHz

1.036750 GHz

P2:ampl(C1)

> 889.8 mV

> 903.732 mV

> 850.4 mV

> 979.1 mV

> 26.016 mV

4.84 ps

EveOne

404.1 mV

P3thase(C1)

< -460.9 mV

< -541.6 mV

< -421.1 mV

< 20.392 mV

173

Dj(sp

54.26 ps

EveZero

-431.1 mV

< -466.151 mV

P4/ton(C1) P5/ermsi(Eve)

BitRate

EveAmpl

835.2 mV

162 ns

16.2 ps

16.2 ps

16.212 ps

428.9 mV

437.581 m\

> 349.8 mV

> 483.3 mV

> 14.592 mV

173

3.3600 Gbit/sec

P6:eppi(Eve)

115 0 ps

115.034 ps

115.0 ps

115.0 ps

7.15 ps

EveWidth

200.3 ps

P7:Q(Eve)

7 0496

7 0496

7 0498

51 ps

EveCross

50.01 %

7.049625

P8:ndcd(Eve)

18e-3

18e-3

DCD

1 ps

EveAvgPwr

-11.4 mV

18e-3

18.14e-3

P9:enni/Eve)

DD

51 ps

1.524591e+6 914.388622e-15

MaskHits

P10--

EveBER

P12--

@3.36Gbps

- Concerning the highest data rate for triggerless at 4Gbps, at least 2 SER interface ports needed

- Thus bit rate @2.24Gbps is safe and power optimized

# **Readout & Periphery**

## Designed for low power

- Only the hit (fastor) info & address are fannout from the pixel array

- $\forall$  Only the read (acquisition) signal is fanned in to the pixel array

- Clock & time stamp are localized only in the EOC, different from FE-I3

## Optimized @ CEPC hit rate

- Some common time stamp recorded for a full double column

- > For low power

- Column is hit every 8.3us / pixel is readout in 2 clocks (50ns) / cluster size 3 pixels

- ▶ Dead time 500ns 98% trigger efficiency

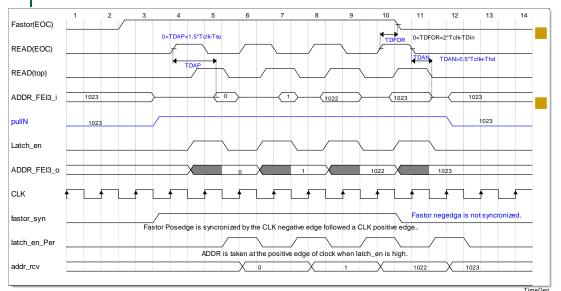

Time stamp recorded when Fastor is valid

# Each pixel readout by 2 clocks (50ns)

- ♦ Worst delay ~ 25ns

- Sim by 512 rows (full size)

- > TDA: read sent –addr come

- Address latch @ 37.5ns

- ▶ @1.5 clock

- > Enough headroom for all corners