5

# <sup>2</sup> Technical Design Report:

- <sup>3</sup> A High-Granularity Timing Detector for the

- ATLAS Phase-II Upgrade

Draft version: 1.5 Created: 1st January 2020 – 14:35 **Prepared by: The ATLAS Collaboration**

$_7$   $\,$  © 2020 CERN for the benefit of the ATLAS Collaboration.

<sup>8</sup> Reproduction of this article or parts of it is allowed as specified in the CC-BY-4.0 license.

#### 9 Abstract

The large increase of pile-up interactions is one of the main experimental 10 challenges for the HL-LHC physics program. A powerful new way to mitigate 11 the effects of pile-up is to use high-precision timing information to distinguish 12 between collisions occurring close in space but well-separated in time. A 13 High-Granularity Timing Detector, based on low gain avalanche detector 14 technology, is therefore proposed for the ATLAS Phase-II upgrade. Covering the 15 pseudorapidity region between 2.4 and 4.0, this device will significantly improve 16 the performance in the forward region. Taking into account the typical number 17 of hits per track in the detector, the target average time resolution per track for a 18 minimum-ionising particle is 30 ps at the start of lifetime, increasing to 50 ps at 19 the end of HL-LHC operation. The high-precision timing information greatly 20 improves the track-to-vertex association, leading to a performance similar to that 21 in the central region for both jet and lepton reconstruction, as well as the tagging 22 of heavy-flavour jets. These improvements in object reconstruction performance 23 translate into important sensitivity gains and enhance the reach of the HL-LHC 24 physics program. In addition, the HGTD offers unique capabilities for the online 25 and offline luminosity determination, an important requirement for precision 26 physics measurements. 27

# 28 Contents

| 29 | 1 | Intro | oductio  | n                                                                      | 1  |

|----|---|-------|----------|------------------------------------------------------------------------|----|

| 30 | 2 | Dete  | ector Re | equirements and Layout                                                 | 3  |

| 31 |   | 2.1   | Beam     | conditions at the HL-LHC                                               | 3  |

| 32 |   | 2.2   | Detect   | or overview and requirements                                           | 4  |

| 33 |   | 2.3   | Detect   | or layout and optimisation                                             | 6  |

| 34 |   | 2.4   | Radiat   | tion hardness                                                          | 14 |

| 35 | 3 | Perf  | ormano   | ce and Physics Benchmarks                                              | 17 |

| 36 |   | 3.1   | Simula   | ation                                                                  | 17 |

| 37 |   |       | 3.1.1    | Detector geometry                                                      | 17 |

| 38 |   |       | 3.1.2    | Sensor simulation                                                      | 19 |

| 39 |   |       | 3.1.3    | Simulation using silicon hits                                          | 25 |

| 40 |   | 3.2   | Detect   | or performance                                                         | 27 |

| 41 |   |       | 3.2.1    | Detector response characterisation                                     | 27 |

| 42 |   |       | 3.2.2    | Track-level performance                                                | 33 |

| 43 |   |       | 3.2.3    | Determination of the time of the primary vertex                        | 39 |

| 44 |   |       | 3.2.4    | Suppression of pile-up jets                                            | 42 |

| 45 |   |       | 3.2.5    | Missing transverse momentum                                            | 44 |

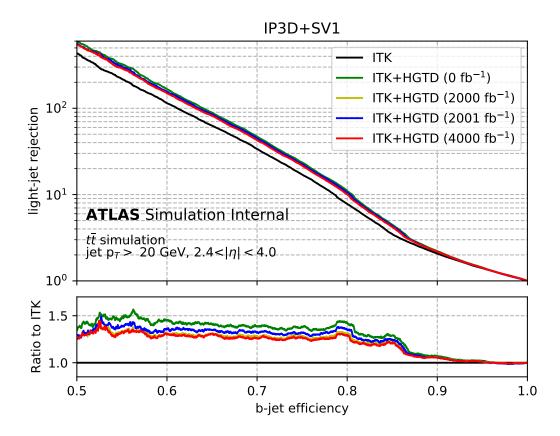

| 46 |   |       | 3.2.6    | Tagging of heavy flavour jets                                          | 45 |

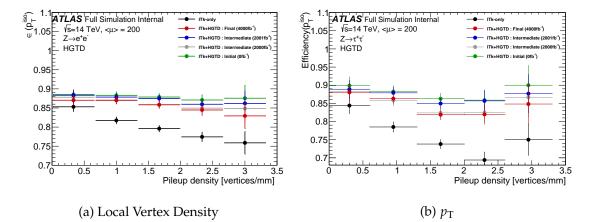

| 47 |   |       | 3.2.7    | Lepton isolation                                                       | 46 |

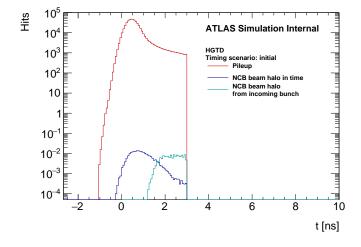

| 48 |   |       | 3.2.8    | Non-collision background                                               | 48 |

| 49 |   | 3.3   | Physic   | 28                                                                     | 50 |

| 50 |   |       | 3.3.1    | Strategy for the Application of Object Performance to Physics Analyses | 50 |

| 51 |   |       | 3.3.2    | Impact of the luminosity uncertainty                                   | 53 |

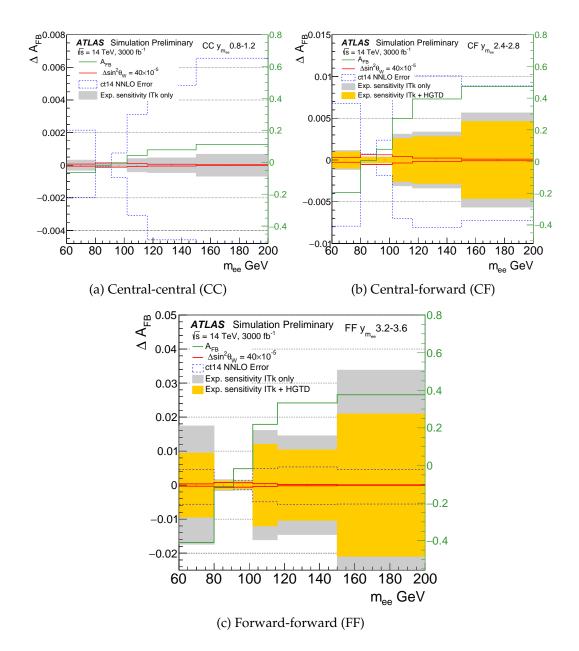

| 52 |   |       | 3.3.3    | Measurement of $\sin^2 \theta_{\text{eff}}$                            | 54 |

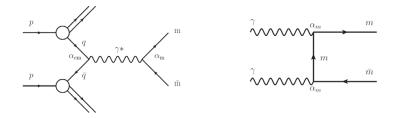

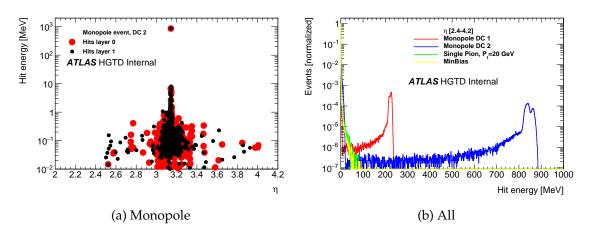

| 53 |   |       | 3.3.4    | Monopole searches                                                      | 55 |

| 54 | 4 | Tech  | nical C  | Dverview                                                               | 59 |

| 55 |   | 4.1   | Introd   | uction                                                                 | 59 |

| 56 |   | 4.2   | Detect   | or overview and key requirements                                       | 59 |

| 57 |   |       | 4.2.1    | Expected Radiation levels                                              | 60 |

| 58 |   |       | 4.2.2    | Key requirements                                                       | 61 |

| 59 |   |       | 4.2.3    | Read-out bandwidth and trigger                                         | 62 |

| 60 |   | 4.3  | Hybrid HGTD module63                                   |

|----|---|------|--------------------------------------------------------|

| 61 |   |      | 4.3.1 Sensors 64                                       |

| 62 |   |      | 4.3.2 Front End ASIC 66                                |

| 63 |   |      | 4.3.3 Module assembly 68                               |

| 64 |   | 4.4  | Module loading on support structure                    |

| 65 |   | 4.5  | Off detector electronics, calibration and luminosity   |

| 66 |   |      | 4.5.1 Peripheral Electronics Boards 71                 |

| 67 |   |      | 4.5.2 $t_0$ time calibration 73                        |

| 68 |   |      | 4.5.3 Luminosity 74                                    |

| 69 |   | 4.6  | Power distribution and detector control system         |

| 70 |   |      | 4.6.1 HV system 74                                     |

| 71 |   |      | 4.6.2 LV system 74                                     |

| 72 |   |      | 4.6.3 Monitoring and Controls 75                       |

| 73 |   | 4.7  | Mechanics, Services and Infrustructure                 |

| 74 |   | 4.8  | Assembly, Installation and Commissioning               |

| 75 |   | 4.9  | Next steps towards construction                        |

|    |   |      | 1                                                      |

| 76 | 5 | Sen  | sors 79                                                |

| 77 |   | 5.1  | Sensor parameters and requirements                     |

| 78 |   | 5.2  | Low Gain Avalanche Detectors79                         |

| 79 |   |      | 5.2.1 Overview 79                                      |

| 80 |   |      | 5.2.2 LGAD productions 82                              |

| 81 |   | 5.3  | Radiation damage and irradiations                      |

| 82 |   | 5.4  | Sensor tests: methodology and experimental techniques  |

| 83 |   | 5.5  | LGAD performance before and after irradiation          |

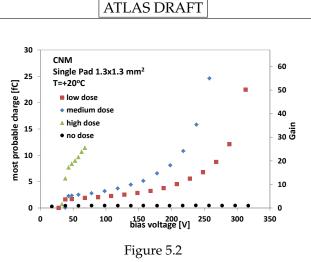

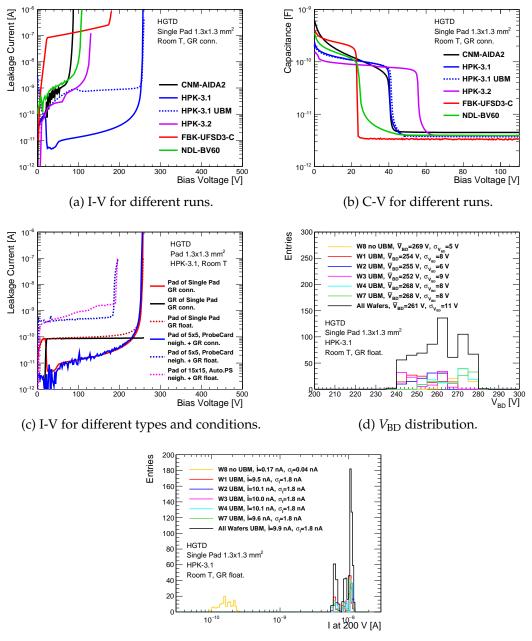

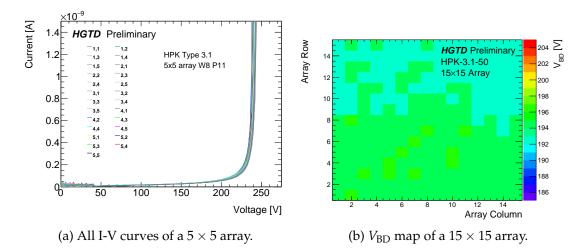

| 84 |   |      | 5.5.1 Electrical characterisation: I-V and C-V 87      |

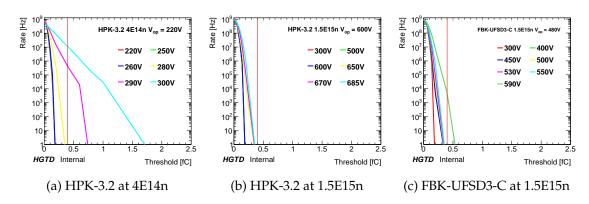

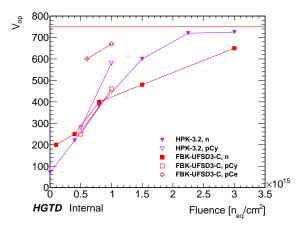

| 85 |   |      | 5.5.2 Operating bias Voltage and self-triggering 91    |

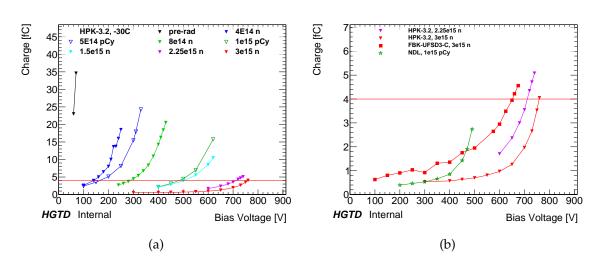

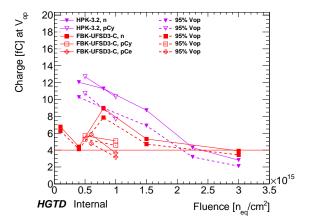

| 86 |   |      | 5.5.3 Collected charge and gain 93                     |

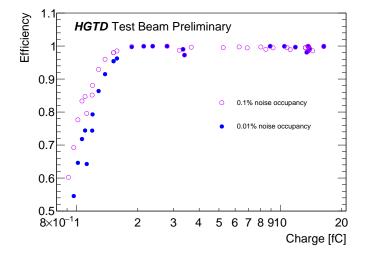

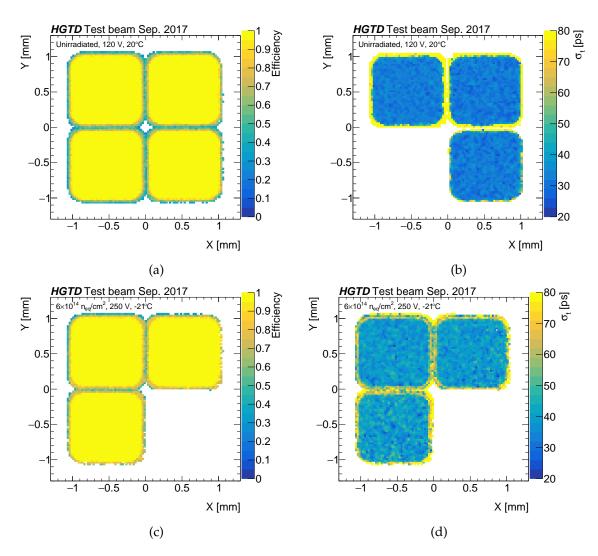

| 87 |   |      | 5.5.4 Efficiency 94                                    |

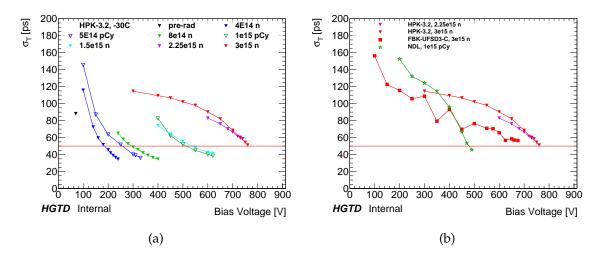

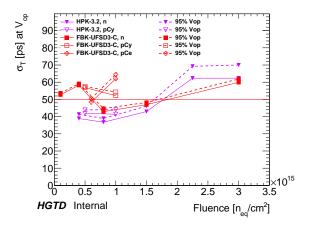

| 88 |   |      | 5.5.5 Time resolution 95                               |

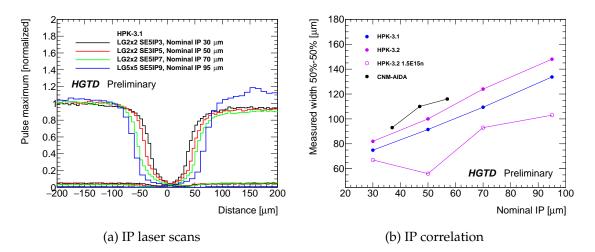

| 89 |   |      | 5.5.6 Uniformity, inter-pad gap and edge region 96     |

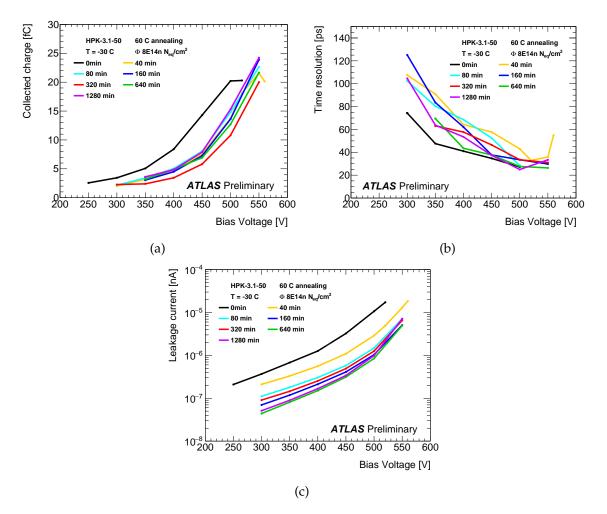

| 90 |   |      | 5.5.7 Long term and stability tests 99                 |

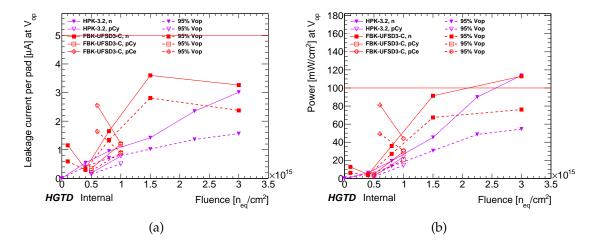

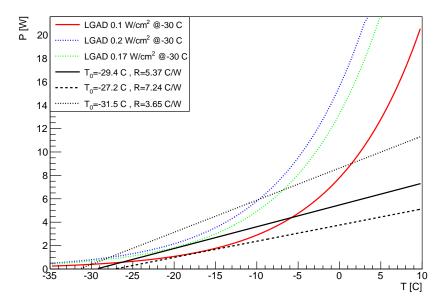

| 91 |   |      | 5.5.8 Leakage current and power after irradiation 102  |

| 92 |   | 5.6  | Operational aspects and bias voltage evolution in HGTD |

| 93 |   | 5.7  | Summary of status quo sensor design                    |

| 94 |   | 5.8  | Roadmap for future sensor productions and activities   |

|    |   |      |                                                        |

| 95 | 6 | Fror | nt-end Electronics 109                                 |

| 96 |   | 6.1  | General requirements                                   |

| 97 |   |      | 6.1.1Data transmission bandwidth requirements112       |

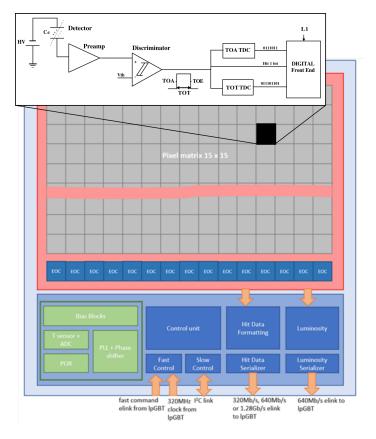

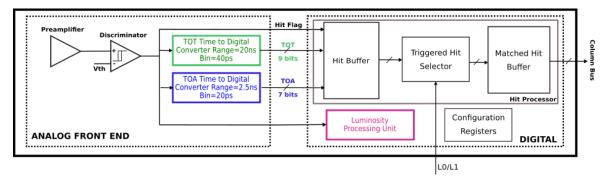

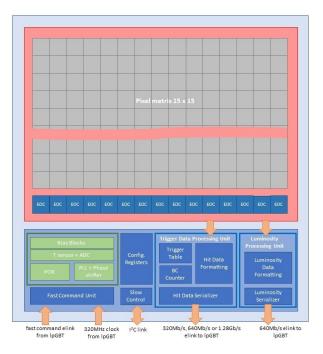

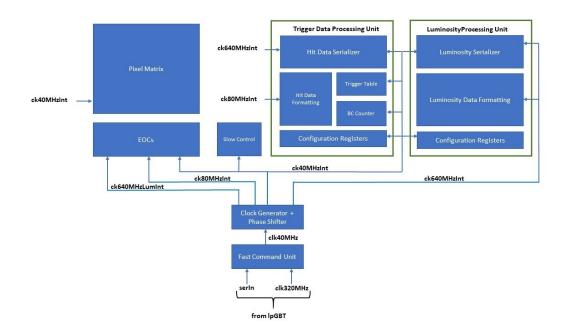

| 98 |   | 6.2  | ASIC architecture                                      |

| 99 |   |      | 6.2.1 Channel architecture 113                         |

| 100 |   |     | 6.2.2   | Readout architecture                                 | 115   |

|-----|---|-----|---------|------------------------------------------------------|-------|

| 101 |   | 6.3 | Single  | -channel readout electronics                         | . 117 |

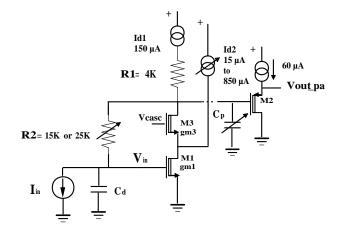

| 102 |   |     | 6.3.1   | Preamplifier                                         | 117   |

| 103 |   |     | 6.3.2   | Discriminator and time walk correction               | 119   |

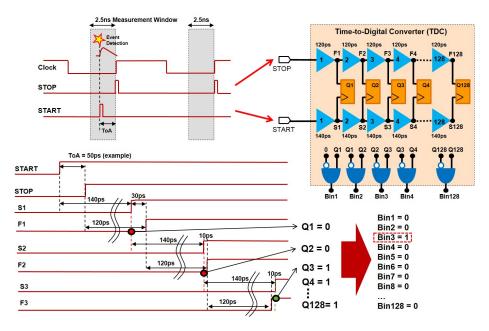

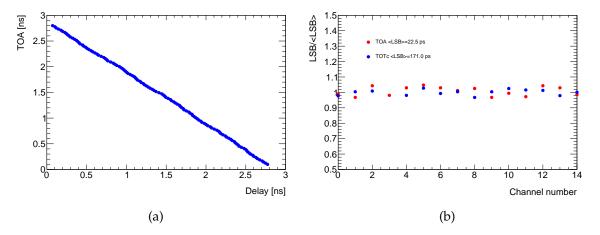

| 104 |   |     | 6.3.3   | TDC                                                  | 120   |

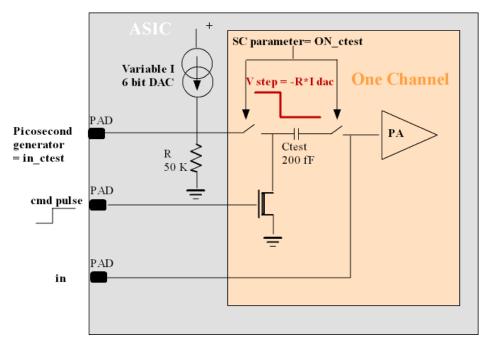

| 105 |   |     | 6.3.4   | Command pulser for calibration                       | 122   |

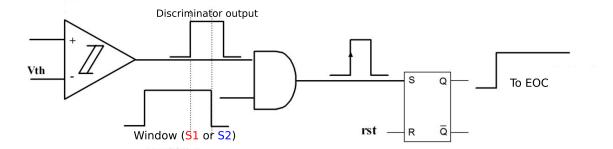

| 106 |   |     | 6.3.5   | Hit processor                                        | 122   |

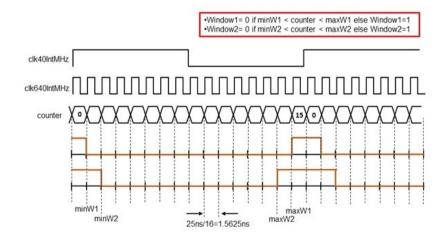

| 107 |   |     | 6.3.6   | Luminosity processing unit                           | 124   |

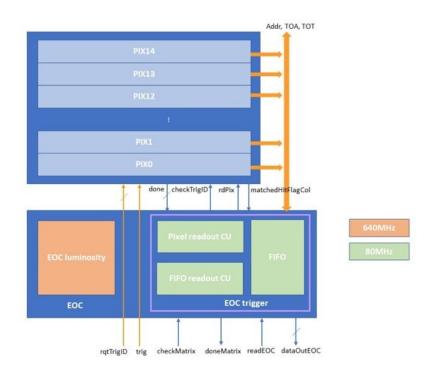

| 108 |   | 6.4 | ASIC    | End of Column logic and digital blocks               | . 125 |

| 109 |   |     | 6.4.1   | Matrix readout process                               | 125   |

| 110 |   |     | 6.4.2   | Slow control                                         | 127   |

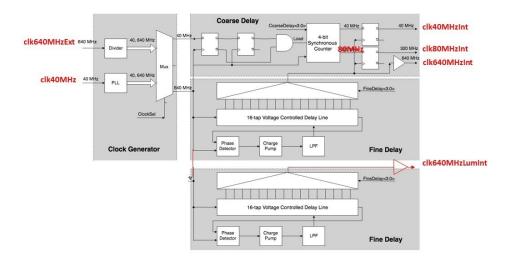

| 111 |   |     | 6.4.3   | Clock generator and phase shifter                    | 128   |

| 112 |   |     | 6.4.4   | Clock distribution                                   | 128   |

| 113 |   | 6.5 | Radia   | tion tolerance                                       | . 129 |

| 114 |   | 6.6 | ASIC    | Power distribution and grounding                     | . 130 |

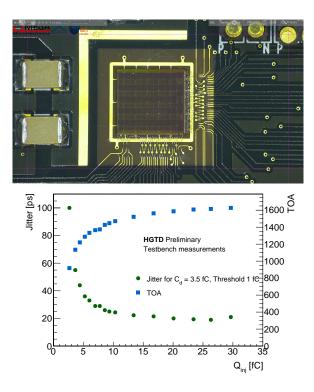

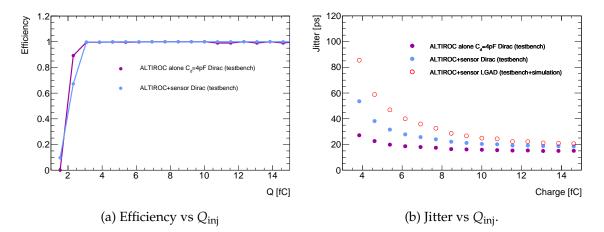

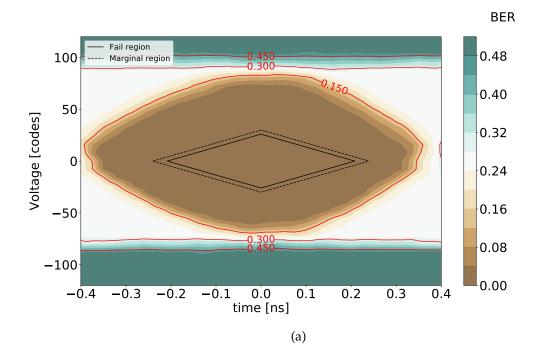

| 115 |   | 6.7 | ASIC ]  | prototype measurements                               | . 131 |

| 116 |   |     | 6.7.1   | Test bench performance                               | 132   |

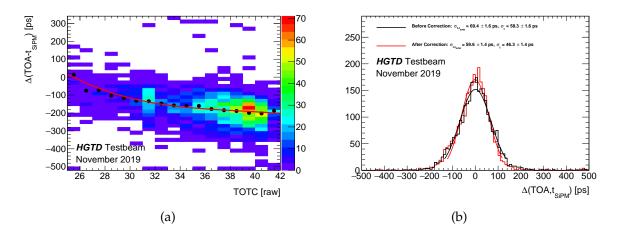

| 117 |   |     | 6.7.2   | Test beam performance                                | 134   |

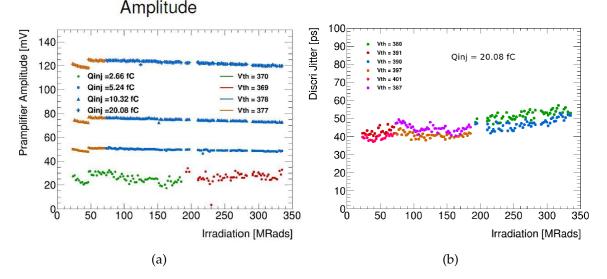

| 118 |   |     | 6.7.3   | Irradiation tests                                    | 135   |

| 119 |   | 6.8 | Monit   | oring                                                | . 135 |

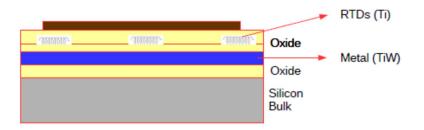

| 120 |   |     | 6.8.1   | Temperature monitoring                               | 135   |

| 121 |   |     | 6.8.2   | Supply voltages monitoring                           | 136   |

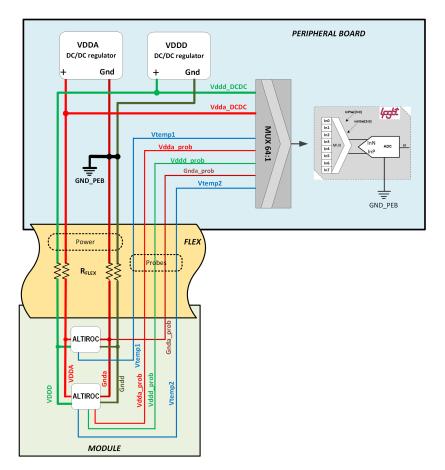

| 122 |   |     | 6.8.3   | Complete monitoring system                           | 137   |

| 123 |   | 6.9 | Roadn   | nap towards production                               | . 138 |

| 124 | 7 | Mod | lule As | sembly and Loading                                   | 141   |

| 125 |   | 7.1 | Introd  | uction                                               | . 141 |

| 126 |   | 7.2 | The ba  | are module                                           | . 141 |

| 127 |   |     | 7.2.1   | Bare module assembly                                 | 142   |

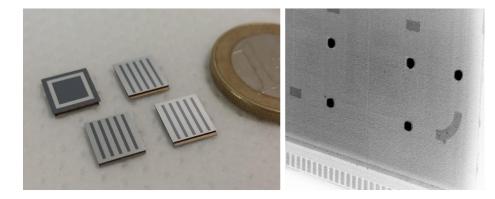

| 128 |   |     | 7.2.2   | First bare module prototypes: process and results    | 143   |

| 129 |   |     | 7.2.3   | Hybridization specifications                         | 146   |

| 130 |   |     | 7.2.4   | Quality assurance / quality control                  | 148   |

| 131 |   |     | 7.2.5   | Production hybridization strategy                    | 148   |

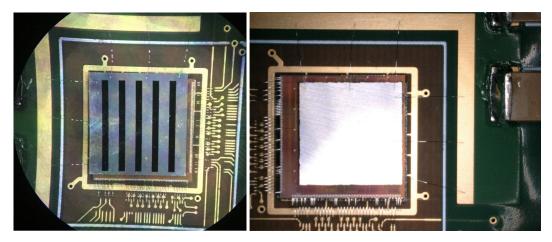

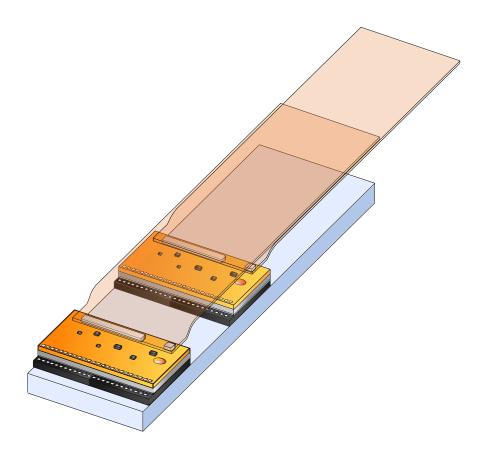

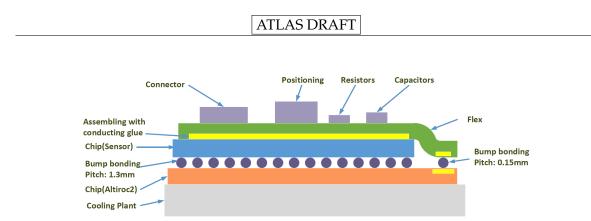

| 132 |   | 7.3 | Modu    | le design and assembly                               | . 149 |

| 133 |   |     | 7.3.1   | General description                                  | 149   |

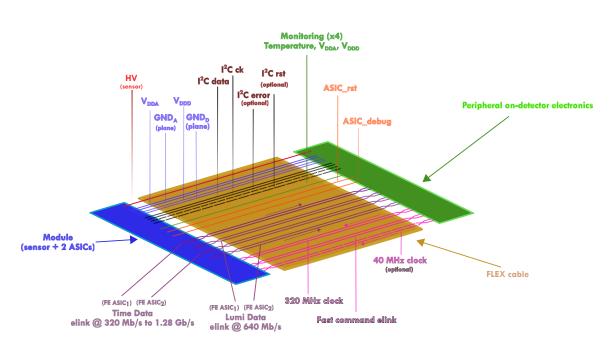

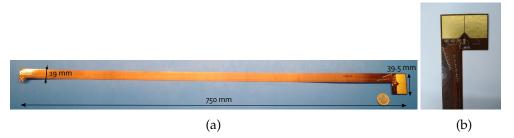

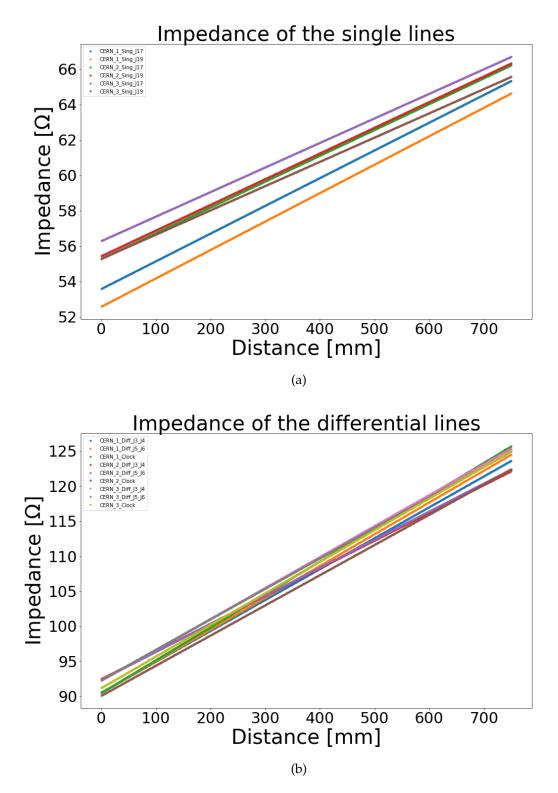

| 134 |   |     | 7.3.2   | Voltage distribution and signal readout: flex cables | 150   |

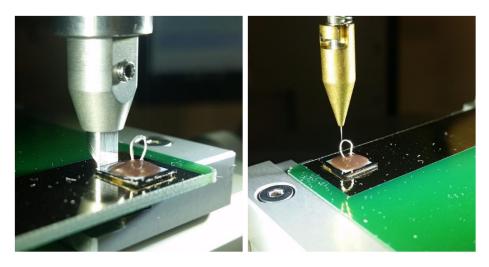

| 135 |   |     | 7.3.3   | Gluing and wire-bonding                              | 154   |

| 136 |   |     | 7.3.4   | Assembly specifications                              | 158   |

| 137 |   |     | 7.3.5   | Quality assurance / quality control                  | 159   |

| 138 |   |     | 7.3.6   | Production strategy for module assembly              | 159   |

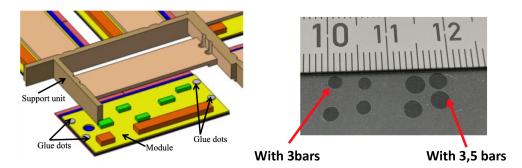

| 139 |   | 7.4 | Modu    | le loading                                           | . 160 |

| 140 |   |     | 7.4.1   | General description                                  | 160   |

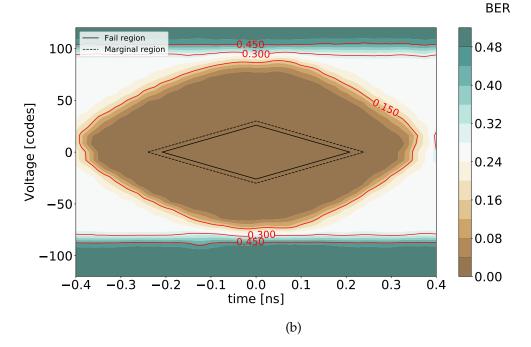

| 141<br>142<br>143 |    |      | <ul><li>7.4.2 Support units and detector units</li><li>7.4.3 Gluing studies</li></ul> | 160<br>162 |

|-------------------|----|------|---------------------------------------------------------------------------------------|------------|

|                   |    |      | 7.4.3 Gluing studies                                                                  | 162        |

| 143               |    |      | 0                                                                                     | 102        |

|                   |    |      | 7.4.4 Procedure for assembly and qualification                                        | 163        |

| 144               |    |      | 7.4.5 Detector unit assembly strategy                                                 | 164        |

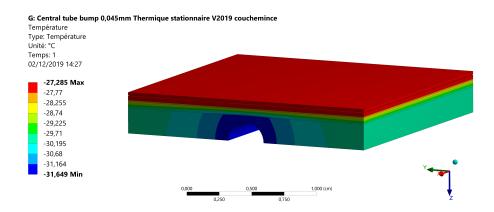

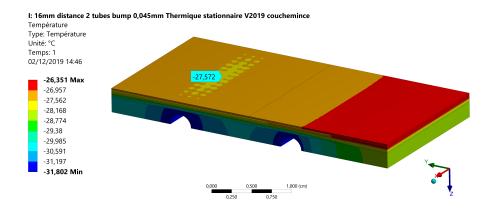

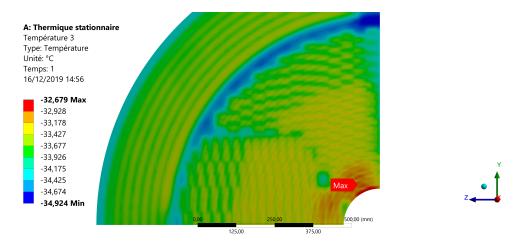

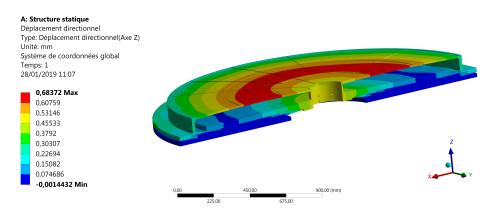

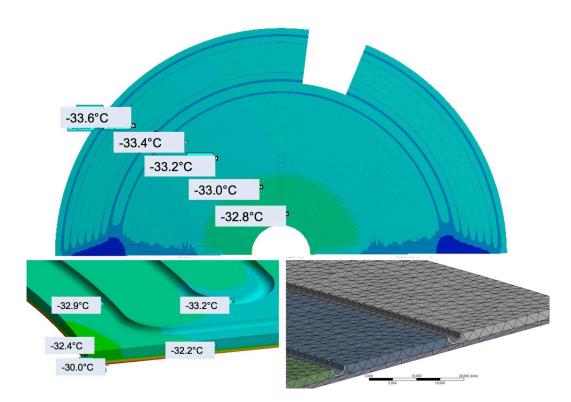

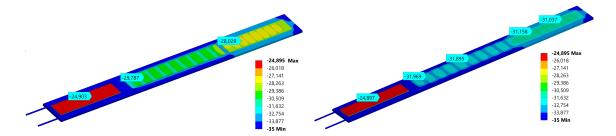

| 145               |    | 7.5  | Thermal calculation                                                                   | . 165      |

| 146               | 8  | Pow  | er Distribution, Control, and Safety Systems                                          | 171        |

| 147               |    | 8.1  | High voltage                                                                          | . 171      |

| 148               |    | 8.2  | Low voltage                                                                           | . 172      |

| 149               |    | 8.3  | Grounding/shielding                                                                   | . 173      |

| 150               | 9  | Peri | pheral Electronics                                                                    | 175        |

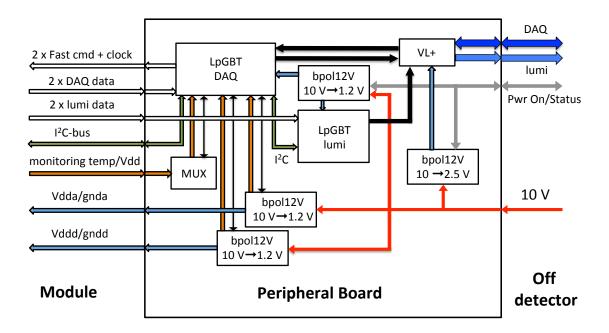

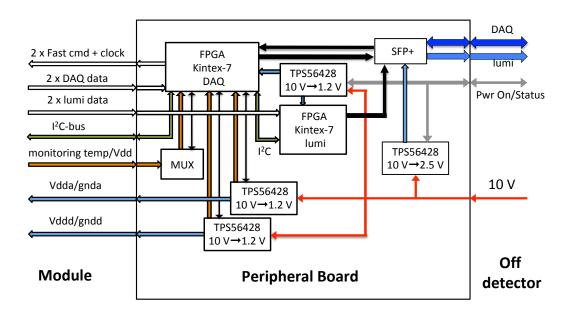

| 151               |    | 9.1  | Requirements                                                                          | . 177      |

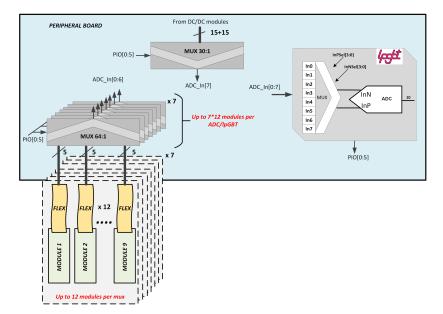

| 152               |    |      | 9.1.1 Data transfer                                                                   | 177        |

| 153               |    |      | 9.1.2 Physical limitations                                                            | 177        |

| 154               |    |      | 9.1.3 Radiation tolerance                                                             | 178        |

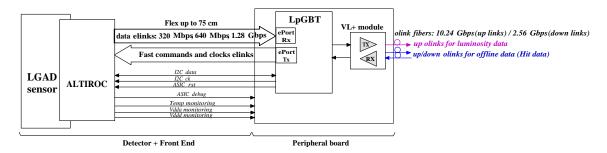

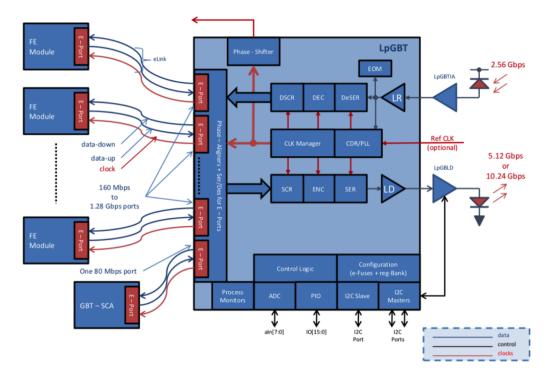

| 155               |    | 9.2  | Data transfer                                                                         | . 178      |

| 156               |    |      | 9.2.1 LpGBT                                                                           | 178        |

| 157               |    |      | 9.2.2 Optical links                                                                   | 181        |

| 158               |    | 9.3  | DC-DC converters                                                                      | . 181      |

| 159               |    | 9.4  | Control and monitoring                                                                |            |

| 160               |    | 9.5  | Connectors                                                                            |            |

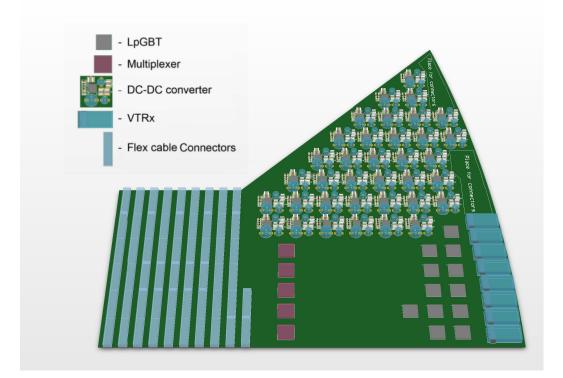

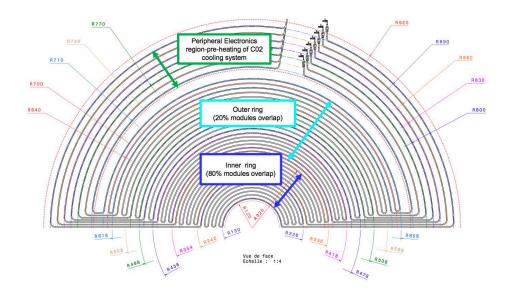

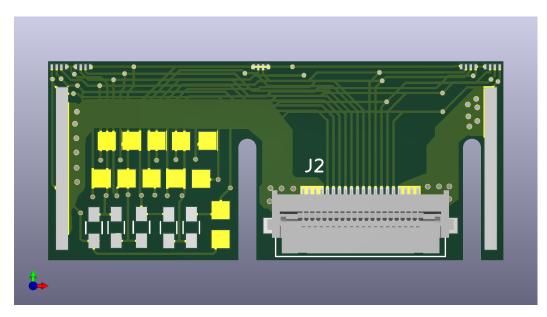

| 161               |    | 9.6  | Peripheral boards                                                                     | . 183      |

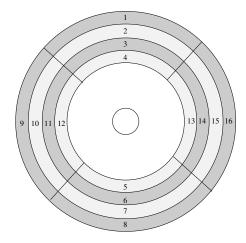

| 162               |    |      | 9.6.1 Layout considerations                                                           | 183        |

| 163               |    |      | 9.6.2 Layout                                                                          | 184        |

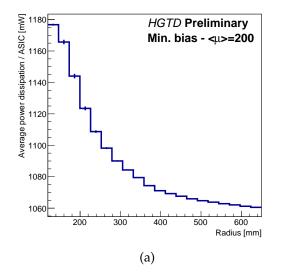

| 164               |    | 9.7  | Power dissipation                                                                     | . 185      |

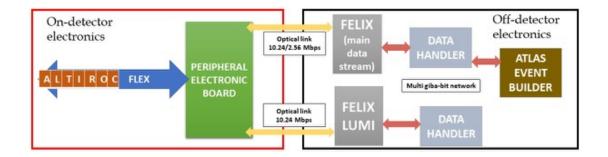

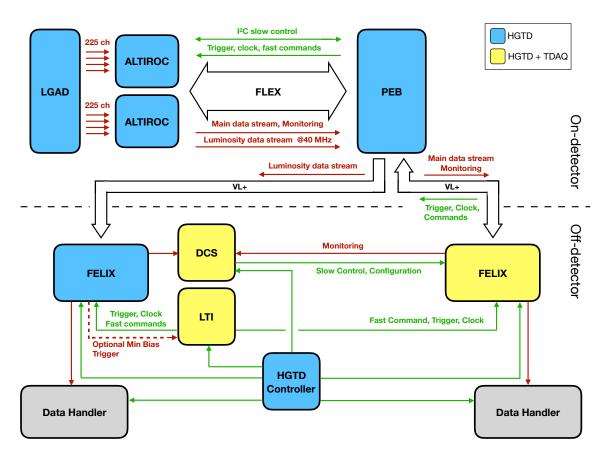

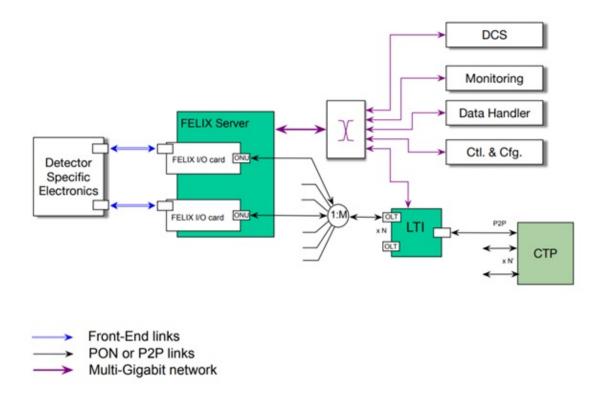

| 165               | 10 | DAG  | ) and Luminosity Measurement                                                          | 187        |

| 166               |    |      | DAQ interface                                                                         |            |

| 167               |    | 1011 | 10.1.1 Off-detector electronics                                                       | 187        |

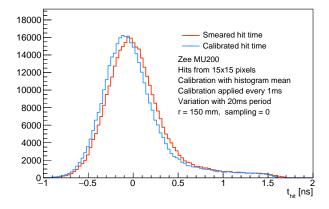

| 168               |    |      | 10.1.2 Calibration and timing                                                         | 189        |

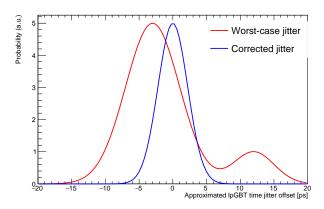

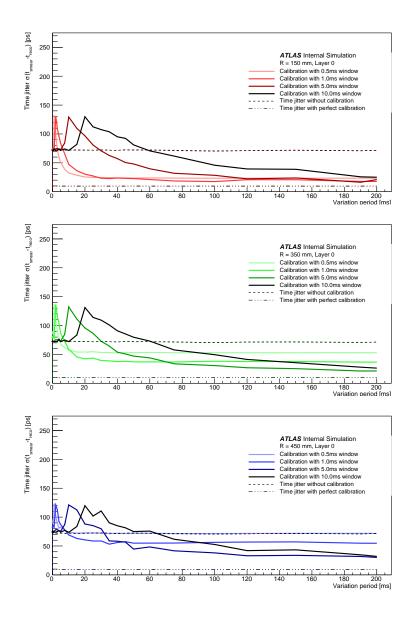

| 169               |    | 10.2 | Timing correction                                                                     |            |

| 170               |    |      | 10.2.1 Sources of clock jitter                                                        | 191        |

| 171               |    |      | 10.2.2 Timing correction procedure                                                    | 192        |

| 172               |    | 10.3 | Luminosity                                                                            | . 195      |

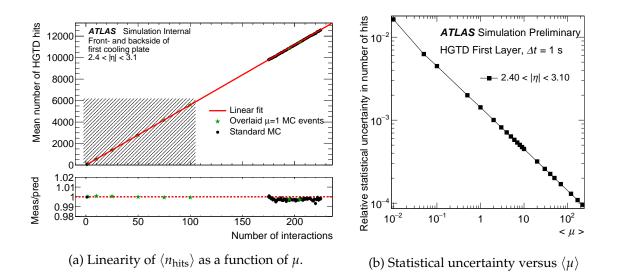

| 173               |    |      | 10.3.1 HGTD as a luminometer                                                          | 196        |

| 174               |    |      | 10.3.2 Linearity of the luminosity determination                                      | 197        |

| 175               |    |      | 10.3.3 Noise and afterglow subtraction                                                | 197        |

| 176               |    |      | 10.3.4 Statistical precision of the luminosity determination                          | 199        |

| 177               |    |      | 10.3.5 Systematic uncertainties affecting the luminosity determination                | 200        |

| 178               |    |      | 10.3.6 Occupancy readout at 40 MHz                                                    | 202        |

| 179               |    |      | 10.3.7 Luminosity back-end electronics                                                | 205        |

| 180 |    |      | 10.3.8    | Per-event luminosity information stored in the ATLAS raw data | 206 |

|-----|----|------|-----------|---------------------------------------------------------------|-----|

| 181 |    |      | 10.3.9    | Operation in non-Stable Beams conditions                      | 207 |

| 182 |    |      | 10.3.10   | ) Minimum-bias trigger at Level-0                             | 207 |

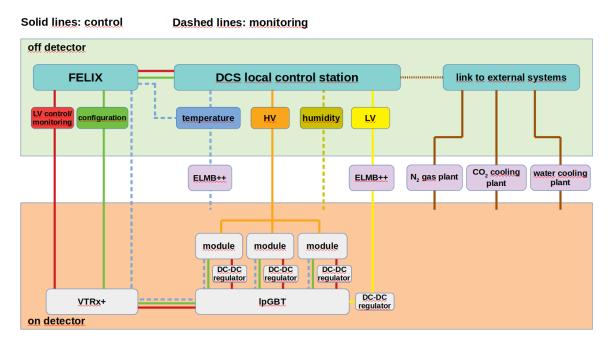

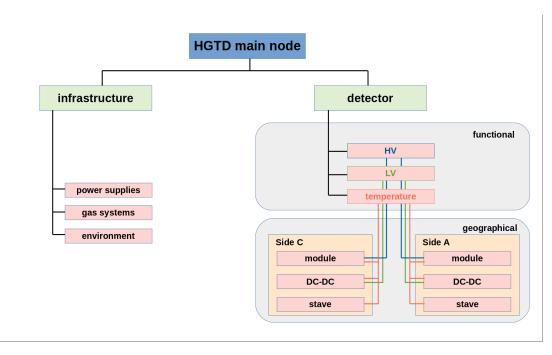

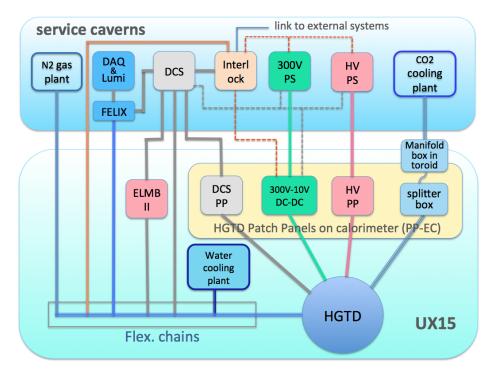

| 183 |    | 10.4 | Detect    | or Control System                                             | 208 |

| 184 |    |      | 10.4.1    | High Voltage                                                  | 208 |

| 185 |    |      | 10.4.2    | Low Voltage                                                   | 209 |

| 186 |    |      | 10.4.3    | Temperatures                                                  | 209 |

| 187 |    |      | 10.4.4    | Pressure and humidity                                         | 209 |

| 188 |    |      | 10.4.5    | Configuring                                                   | 210 |

| 189 |    |      | 10.4.6    | DCS software                                                  | 210 |

| 190 |    |      | 10.4.7    | Interlock system                                              | 211 |

| 191 |    |      | 10.4.8    | External systems                                              | 211 |

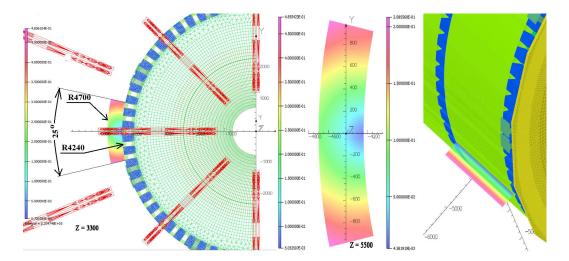

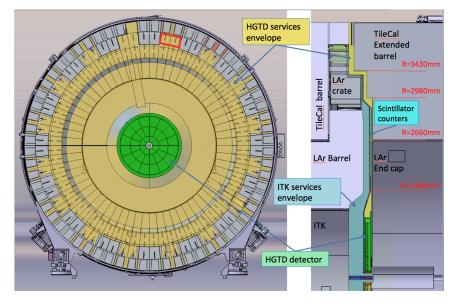

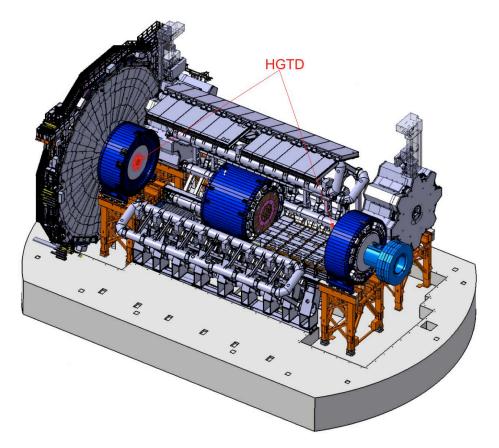

| 192 | 11 | Dete | ector M   | echanics                                                      | 213 |

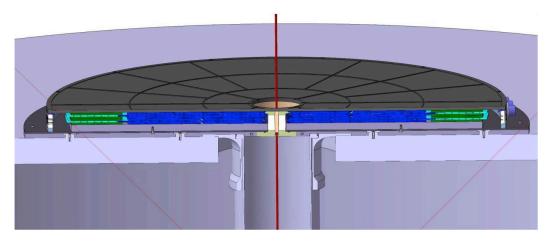

| 193 |    | 11.1 | Engine    | eering design overview                                        | 213 |

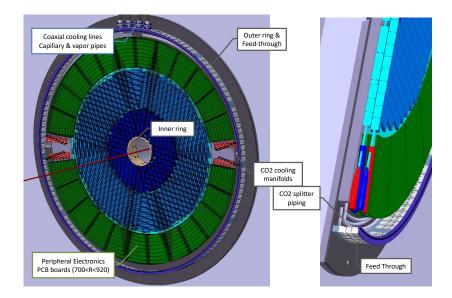

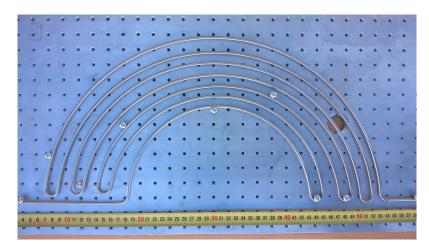

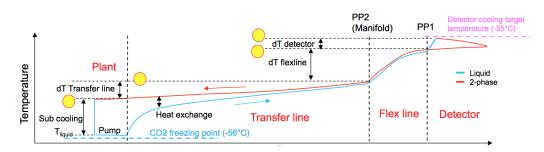

| 194 |    | 11.2 | $CO_2 co$ | ooling system                                                 | 215 |

| 195 |    |      | 11.2.1    | Requirements                                                  | 215 |

| 196 |    |      | 11.2.2    | Cooling design                                                | 217 |

| 197 |    |      | 11.2.3    | Cooling plant demonstrator                                    | 220 |

| 198 |    | 11.3 | Mode      | rator                                                         | 221 |

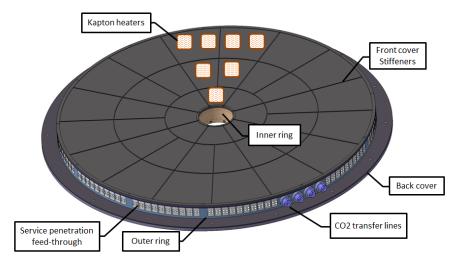

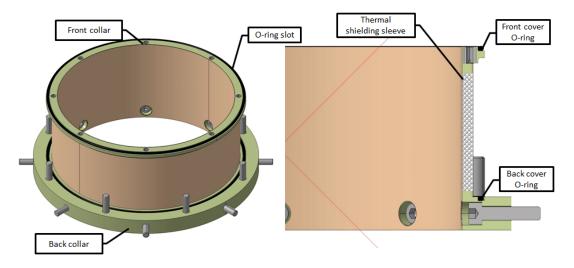

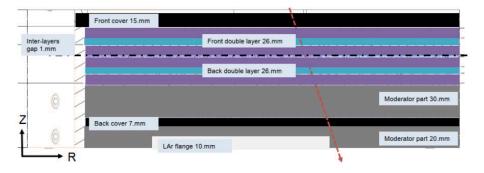

| 199 |    | 11.4 | Herme     | etic vessel                                                   | 222 |

| 200 |    |      | 11.4.1    | Requirements                                                  | 222 |

| 201 |    |      | 11.4.2    | Front cover and heaters                                       | 223 |

| 202 |    |      | 11.4.3    | Back cover and interface with LAr cryostat                    | 224 |

| 203 |    |      | 11.4.4    | Inner ring design                                             | 225 |

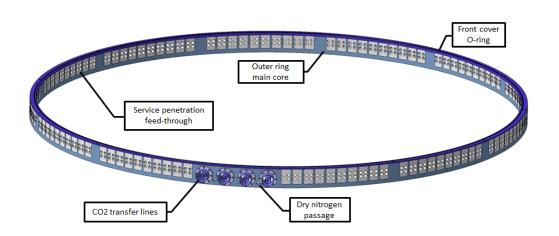

| 204 |    |      | 11.4.5    | Outer ring design                                             | 226 |

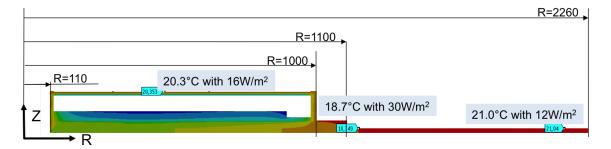

| 205 |    | 11.5 | Local s   | supports and cooling disks                                    | 228 |

| 206 |    |      | 11.5.1    | Geometry and design                                           | 228 |

| 207 |    |      | 11.5.2    | Thermal performance                                           | 229 |

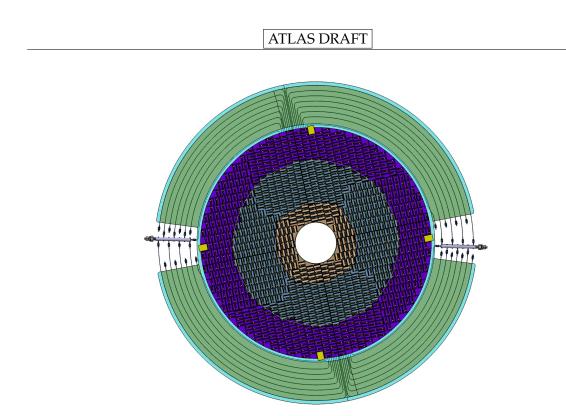

| 208 |    | 11.6 | Detect    | or overall layout                                             | 229 |

| 209 | 12 | Dete | ector In  | frastructure                                                  | 233 |

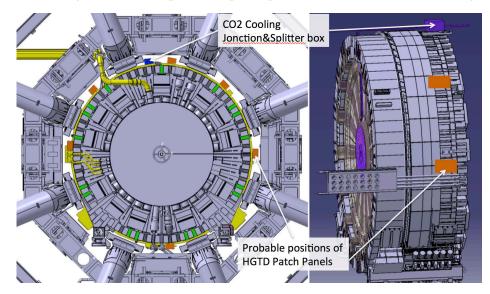

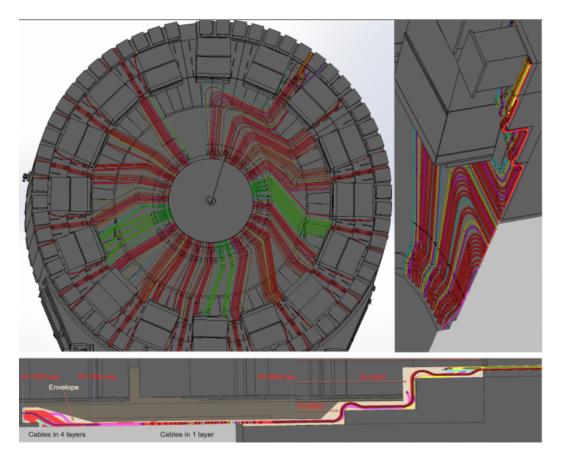

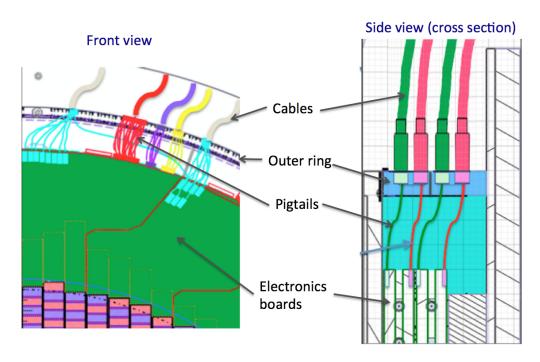

| 210 |    | 12.1 | Servic    | es                                                            | 233 |

| 211 |    |      | 12.1.1    | Specifications                                                | 233 |

| 212 |    |      | 12.1.2    | Services layout                                               | 235 |

| 213 |    |      | 12.1.3    | Patch panels in PP-EC area                                    | 237 |

| 214 |    |      | 12.1.4    | Services routing on the calorimeter front wall                | 238 |

| 215 |    |      | 12.1.5    | Services connection to outer ring and inside the vessel       | 240 |

| 216 |    |      | 12.1.6    | Services installation                                         | 241 |

| 217 | 13 | Detector Assembly, Installation, and Commissioning              | 243 |

|-----|----|-----------------------------------------------------------------|-----|

| 218 |    | 13.1 Assembly and commissioning on surface                      | 243 |

| 219 |    | 13.1.1 Half disks instrumentation                               | 243 |

| 220 |    | 13.1.2 Detector assembly on hermetic vessel                     | 244 |

| 221 |    | 13.1.3 Quality Assurance after assembly                         | 244 |

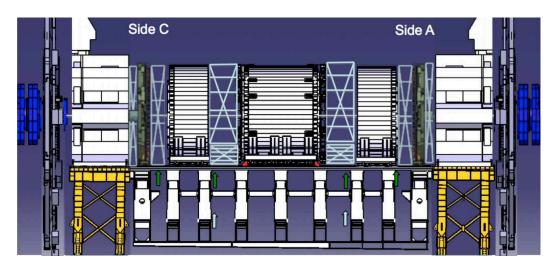

| 222 |    | 13.2 Installation in the cavern and commissioning               | 245 |

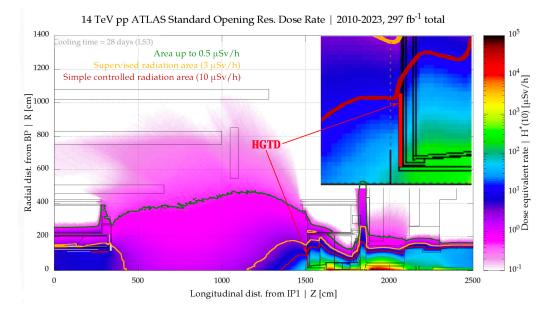

| 223 |    | 13.2.1 Access scenarios                                         | 245 |

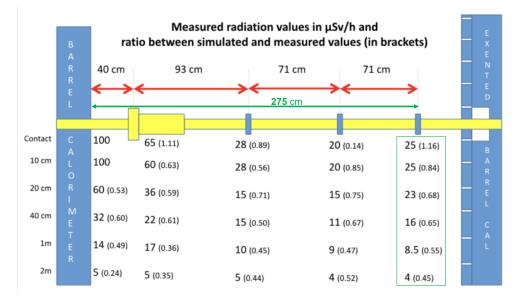

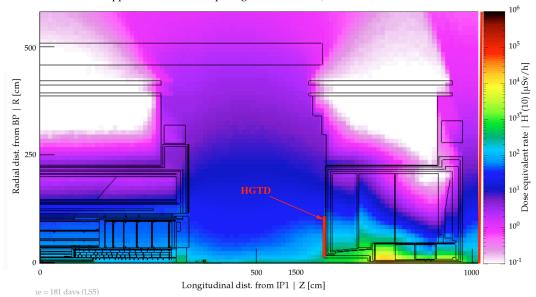

| 224 |    | 13.2.2 Maintenance, radiation environment, and radio protection | 246 |

| 225 |    | 13.2.3 Transport to the cavern and lowering                     | 251 |

| 226 |    | 13.2.4 Detector Installation and Commissioning                  | 252 |

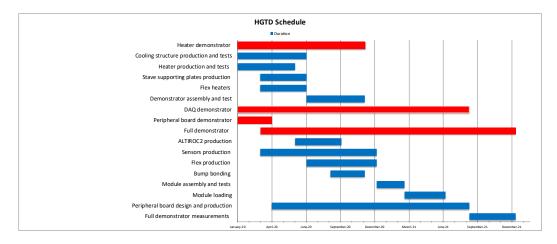

| 227 | 14 | Demonstrator                                                    | 253 |

| 228 |    | 14.1 Introduction                                               | 253 |

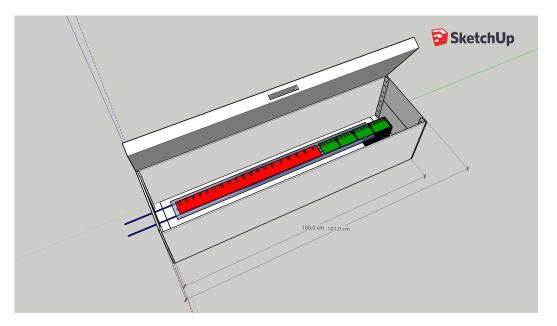

| 229 |    | 14.2 Heater demonstrator                                        | 253 |

| 230 |    | 14.2.1 Mechanical structure                                     | 256 |

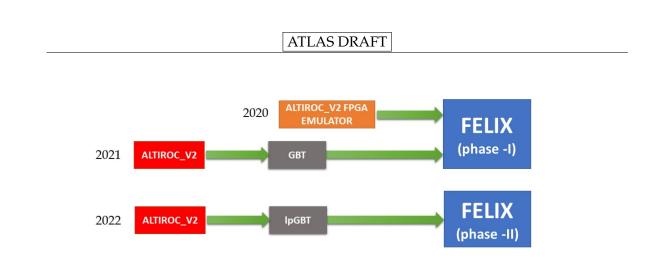

| 231 |    | 14.3 Peripheral and back-end electronics, data acquisition      | 257 |

| 232 |    | 14.3.1 Peripheral electronics demonstrator                      | 257 |

| 233 |    | 14.3.2 DAQ demonstrator                                         | 258 |

| 234 |    | 14.3.3 HGTD module                                              | 259 |

| 235 |    | 14.4 Full demonstrator                                          | 260 |

| 236 |    | 14.5 Demonstrator tests                                         | 260 |

| 237 |    | 14.6 Schedule and organisation                                  | 260 |

| 238 | 15 | Project Organization, Costs, and Schedule                       | 263 |

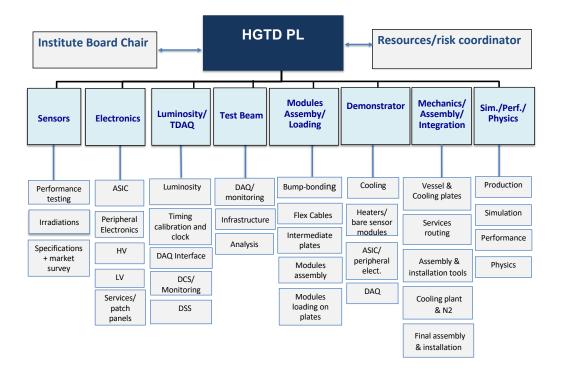

| 239 |    | 15.1 Organization and management                                | 263 |

| 240 |    | 15.1.1 Upgrade organisation in ATLAS                            | 263 |

| 241 |    | 15.1.2 HGTD organisation                                        | 264 |

| 242 |    | 15.1.3 Technical milestones                                     | 267 |

| 243 |    | 15.1.4 Deliverables and WBS                                     | 269 |

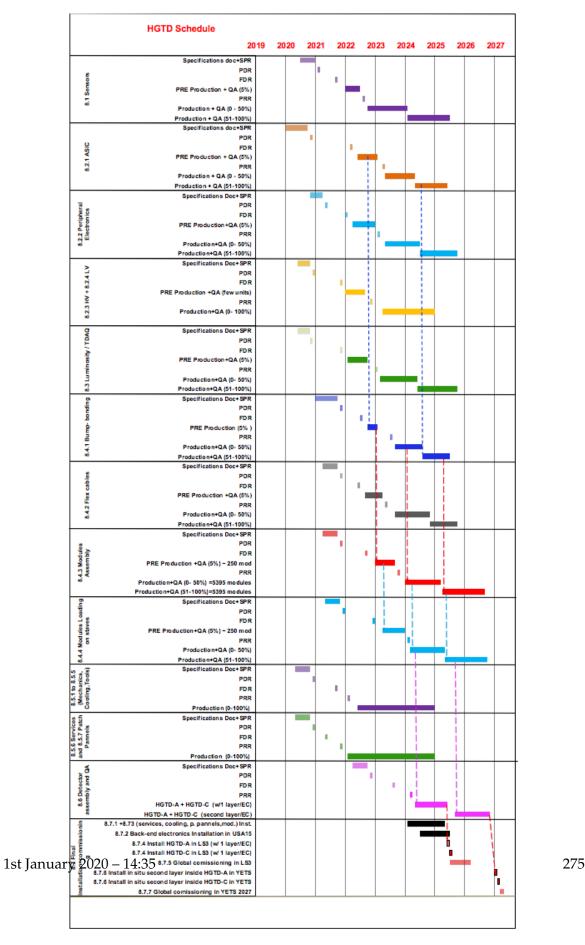

| 244 |    | 15.2 Schedule and production schedule milestones                | 269 |

| 245 |    | 15.3 Costs                                                      | 274 |

| 246 |    | 15.4 Risk management                                            | 277 |

| 247 | A  | Expected Energy Spectra                                         | 283 |

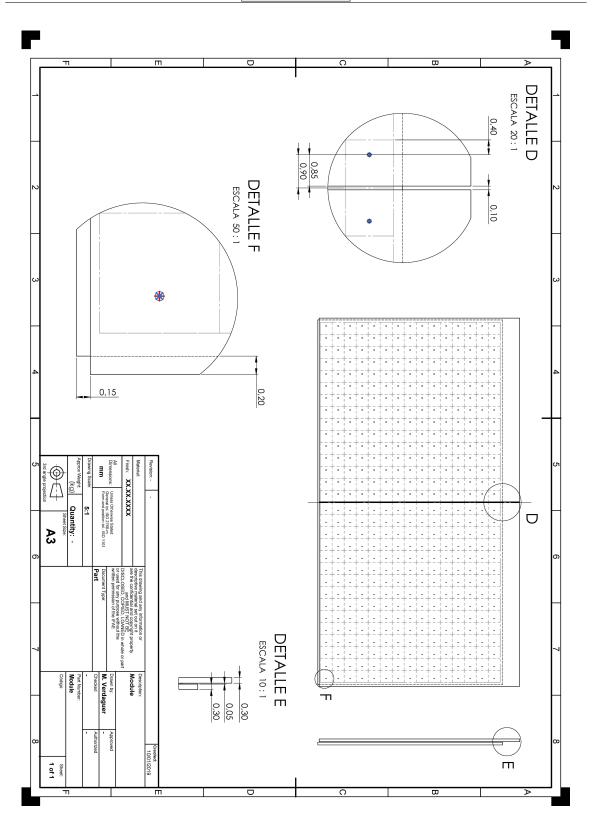

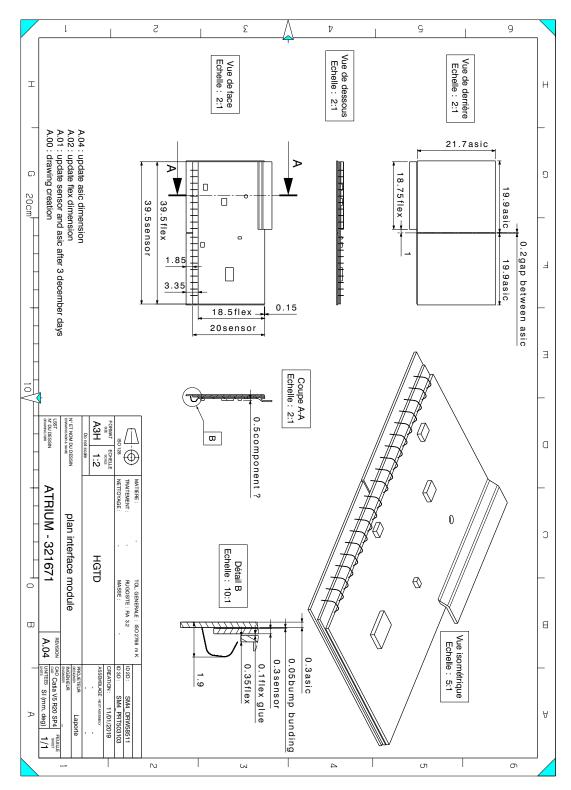

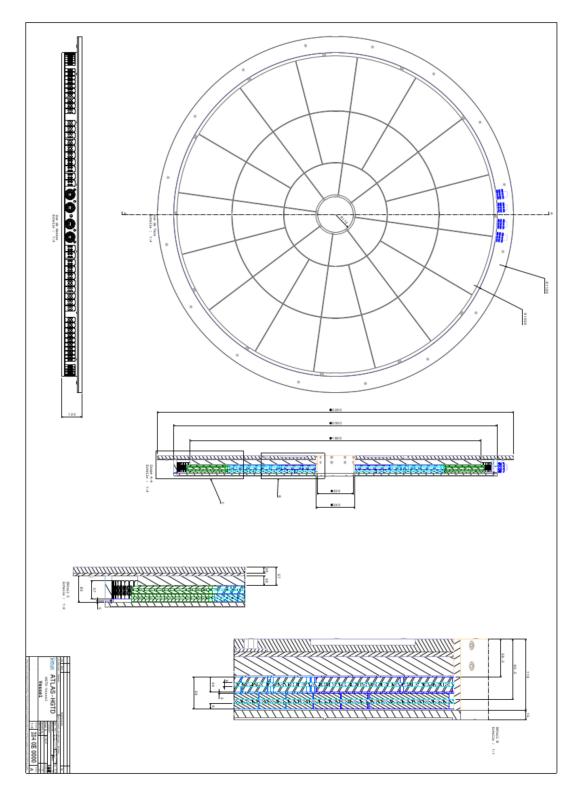

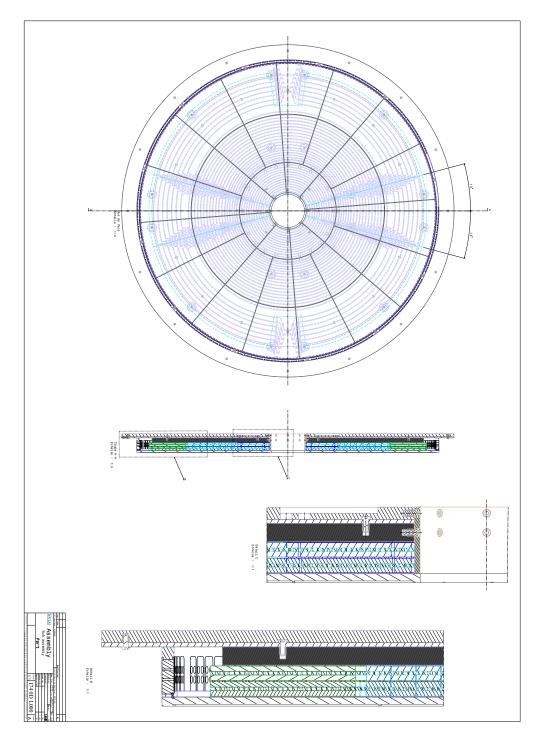

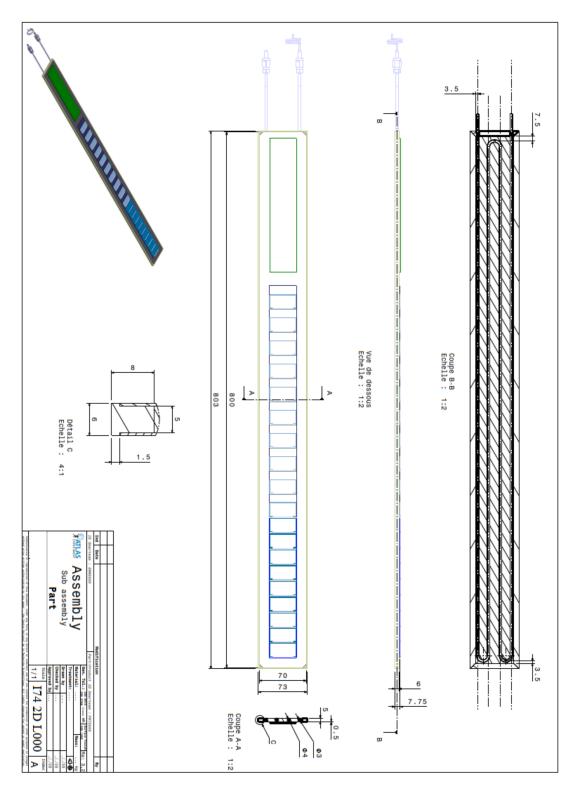

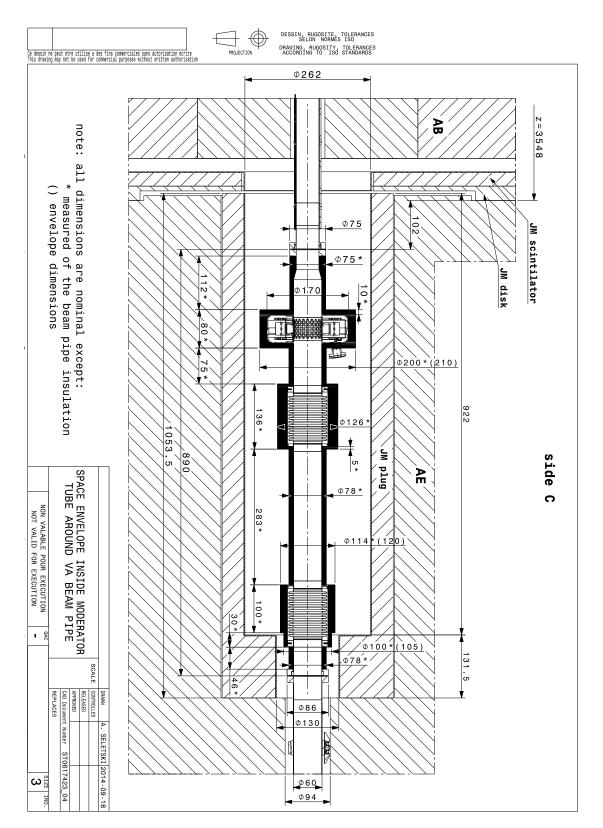

| 248 | B  | Technical Drawings                                              | 285 |

| 249 | Bi | bliography                                                      | 292 |

# <sup>250</sup> 1 Introduction

The high-luminosity (HL) Phase-II of the Large Hadron Collider (LHC) at CERN is scheduled 251 to start in 2026. This HL-LHC will deliver an integrated luminosity of up to  $4000 \text{ fb}^{-1}$  over 252 the subsequent decade. The instantaneous luminosity of the HL-LHC will reach up to 253  $7.5 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, a large increase from the  $2.1 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> obtained during LHC Run-2. 254 Two extended periods without physics operation are anticipated prior to Phase-II, Long 255 Shutdown 2 (LS2) in 2019–2020 and Long Shutdown 3 (LS3) from 2024 until mid 2026. 256 During LS3, extensive upgrades to the ATLAS Experiment will be installed to cope with the 257 higher luminosities and add new capabilities. 258

This report describes the technical design of a High Granularity Timing Detector (HGTD) 259 for the ATLAS Phase-II upgrade, an upgrade that will augment the Phase-II silicon-based 260 Inner Tracker, the ITk [1], in the forward region, with the capability to measure charged-261 particle trajectories in time as well as space. The target average time resolution per track 262 for a minimum-ionising particle is  $\approx 30$  ps at the beginning of the HL-LHC, increasing to 263 50 ps per track at the end of the HL-LHC. The HGTD will also provide a precise, real-time 264 luminosity measurement for ATLAS's Phase-II physics programme. The goals for the design 265 are detailed in Chap. 2, and Chap. 3 provides projections for how the detector will improve 266 ATLAS object reconstruction and physics. 267

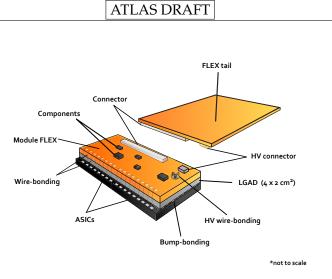

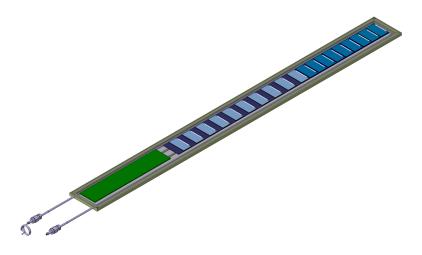

The technical design of the HGTD is summarized in Chap. 4. The HGTD will consist of 268 many silicon-based low-gain avalanche detectors (LGADs), placed in front of the end-cap 269 and forward calorimeters at  $2.4 < |\eta| < 4.0$  and arranged such that a track traverses two 270 or three sensors. Chap. 5 describes the LGAD sensors and their expected performance, 271 based on measurements of prototype devices that include irradiation at the levels expected 272 at the HL-LHC. Chap. 6 describes the front-end electronics, a low-noise, radiation-hard 273 custom ASIC called the ALTIROC, and the performance of the analog front end. Chap. 7 274 discusses the hybridization of the LGAD and ALTIROC into modules of a single LGAD 275 sensor bump-bonded to two ALTIROC chips, their assembly into disks and staves, and their 276 connection via a flex cable to peripheral electronics boards at the outer radii of the disk 277 geometry. Chap. 8 describes the powering and control of the detector. Chap. 9 describes 278 the function and layout of the peripheral electronics boards, and Chap. 10 summarizes the 279 connection of the detector to the ATLAS data acquistion system, the real-time intercalibration 280 of the arrival time within the readout path, and the 40 MHz readout of highly-granular hit 281 multiplicity data for real-time luminosity measurement. Chap. 11 provides the engineering 282 design for cooling the LGADs and front-end electronics, Chap. 12 the mechanical design 283

- <sup>284</sup> of the overall detector, the necessary services and routing, and Sec. 13.1 the assembly and

- commissioning of the detector. Chap. 14 describes a set of intermediate prototypes that will

- integrate elements of the full design during the remaining R&D period, in order to validate

- key aspects of the design. Finally, Chap. 15 documents the organisation of the project to

- <sup>288</sup> deliver and commission the detector for the start of the HL-LHC in 2026.

# **209** 2 Detector Requirements and Layout

#### 290 2.1 Beam conditions at the HL-LHC

Pile-up is one of the main challenges at the HL-LHC. The exact beam-spot characteristics of 291 the HL-LHC have not yet been determined. In the nominal operation scheme [2], an average 292 of 200 simultaneous pp interactions ( $\langle \mu \rangle = 200$ ) will occur within the same bunch crossing 293 interval. A major challenge for the ITk is to efficiently reconstruct charged particles created 294 in the primary interactions and assign them to the correct production vertices in this high 295 pile-up environment. The luminous region will have an estimated Gaussian spread of 30 to 296 60 mm along the beam axis (z direction<sup>1</sup>.) The width in time could range from 175 to 260 ps. 297 The case considered in this report is the *nominal* scenario, with Gaussian spreads of 45 mm 298 in along the beam axis and 175 ps in time. 299

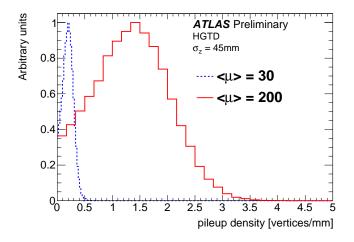

The spatial pile-up line density, i.e. the number of collisions per length unit along the beam 300 axis during one bunch crossing, is a key quantity for evaluating the performance of ATLAS 301 with and without the HGTD. For an average of 200 collisions per bunch crossing, denoted 302  $\langle \mu \rangle = 200$ , an average pile-up density of 1.8 collisions/mm is expected. This average masks 303 the effect of the local variations illustrated in Fig. 2.1. The local pile-up vertex density is 304 calculated by computing the average number of interactions per unit length in a window of 305  $\pm 3$  mm around the signal vertex for  $\langle \mu \rangle = 200$ . This is large enough to avoid quantisation 306 effects and small enough to probe the tails of the distribution. The curve for  $\langle \mu \rangle = 30$  is 307 obtained by scaling, which effectively increases the window size. 308

Fig. 2.1 shows the pile-up densities for  $\langle \mu \rangle = 30$  and  $\langle \mu \rangle = 200$  for the same beam spot size. The most probable local pile-up density for this scenario is around 1.44 collisions/mm.

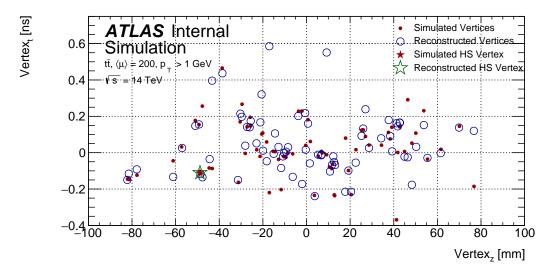

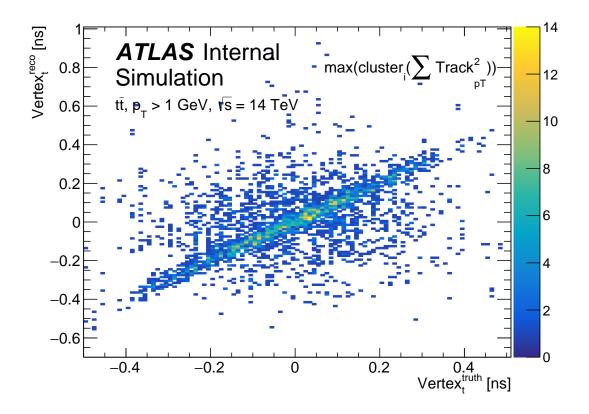

Timing information can supplement the tracker measurement of the longitudinal impact parameter,  $z_0$ , improving how often tracks are assigned to the correct vertices and mitigating the impact of a high vertex density. To illustrate this, an example is presented in Fig. 2.2, which shows a single  $t\bar{t}$  Hard Scatter (HS) vertex along pile-up vertices in the z-t plane at  $\langle \mu \rangle = 200$ . The simulated and reconstructed vertices are overlaid. The vertex and track

<sup>&</sup>lt;sup>1</sup> The ATLAS experiment uses a right-handed coordinate system with its origin at the nominal interaction point (IP) in the centre of the detector and the *z*-axis along the beam pipe. The *x*-axis points from the IP to the centre of the LHC ring, and the *y*-axis points upward. Cylindrical coordinates (r,  $\phi$ ) are used in the transverse plane,  $\phi$  being the azimuthal angle around the *z*-axis. The pseudo-rapidity is defined in terms of the polar angle  $\theta$  as  $\eta = -\ln \tan(\theta/2)$ .

Figure 2.1: Local pile-up vertex densities for different values of  $\langle \mu \rangle$ .

reconstruction used in this event are further described in Sec. 3.2.2. The impact parameter

resolution in the forward region is limited by multiple scattering. A minimal  $p_{\rm T}$  cut of 0.9

GeV is applied for tracks at all  $\eta$  to reject soft forward tracks. Each track is required to have

at least 3 pixel clusters. Tracks are required to have  $\sigma(d_0) < 0.3$  mm and  $\sigma(z_0) < 0.5$  mm in

$_{320}$  order to ensure good precision. This cut effectively removes low- $p_{\rm T}$  forward tracks because

<sup>321</sup> of their limited resolution.

The tracker sees the event as a one-dimensional projection on the z axis, where a large number 322 of tracks from vertices occurring at different times but close in space lead to ambiguities 323 in the track-to-vertex association. This happens when the distance between vertices is of 324 the same order or smaller than the resolution of the longitudinal impact parameter of the 325 track, which happens more often for tracks in the forward region. The timing information 326 reduces the density of vertices which are considered for a given track. The figure shows the 327 reconstructed vertices are also spread in time, due to the association of tracks with timing 328 information of the HGTD. The time of HS vertex may be reconstructed using tracks with hits 329 in the HGTD, as discussed Sec. 3.2.3, allows for more effective separation of the HS vertex 330 from pile-up vertices surrounding it in the *z* direction. 33

#### <sup>332</sup> 2.2 Detector overview and requirements

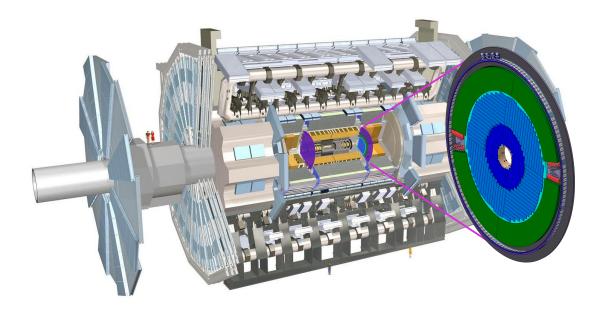

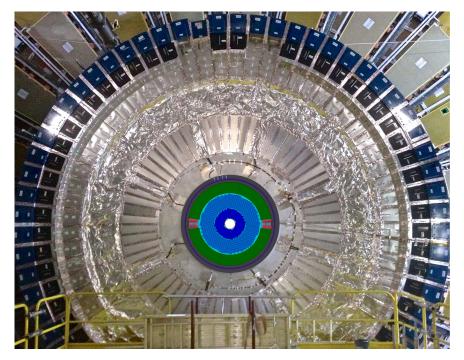

The HGTD has been designed for operation with  $\langle \mu \rangle = 200$  and a total integrated luminosity of 4000 fb<sup>-1</sup>. Taking into account the space constraints of the existing ATLAS Experiment, including the more advanced planning for the tracker upgrade when R&D on the HGTD began, the HGTD will be located in the gap region between the barrel and the end-cap calorimeters, at a distance in *z* of approximately  $\pm$  3.5 m from the nominal interaction point.

Figure 2.2: Visualisation of the primary vertices in an event in the *z*–*t* plane, showing the simulated Hard Scatter (HS) with pile-up interactions superimposed for  $\langle \mu \rangle = 200$ . The reconstructed vertices (blue circles) are overlaid along with the reconstructed HS vertex (green star).

<sup>338</sup> This region lies outside the ITk volume and in front of the end-cap and forward calorimeters

in the volume currently occupied by the Minimum-Bias Trigger Scintillators (MBTS), which

will be removed. The position of the two vessels for the HGTD within the ATLAS detector isshown in Fig. 2.3.

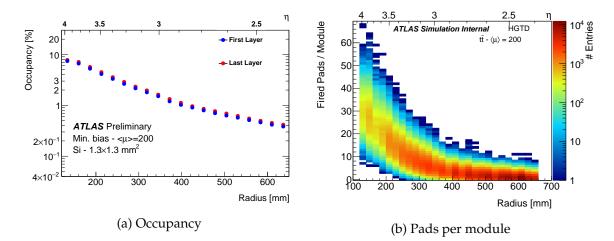

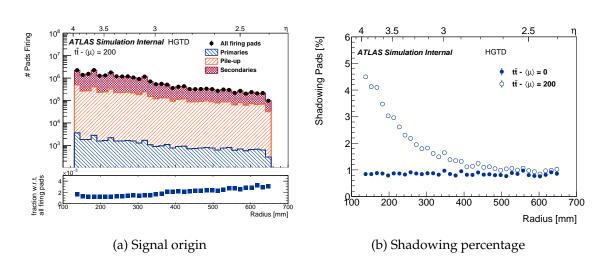

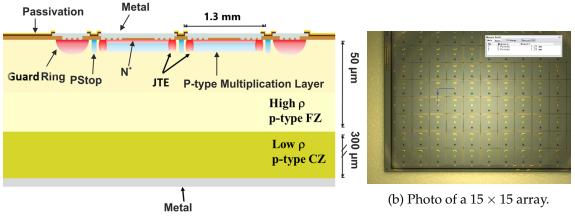

The envelope of the detector vessel has a radial extent of 110 to 1000 mm. The envelope in z, 342 including the moderator, supports, and front and rear vessel covers, is 125 mm. A 50 mm-343 thick moderator is placed behind the HGTD to reduce the back-scattered neutrons created by 344 the end-cap/forward calorimeters, protecting both the ITk and the HGTD. A silicon-based 345 timing detector technology is preferred due to the space limitations. The sensors must be 346 thin and configurable in arrays. In close collaboration with RD50 [3] and manufacturers, an 347 extensive R&D program is progressing quickly towards sensors that provide the required 348 timing resolution in harsh radiation environments. Low Gain Avalanche Detector (LGAD) [4] 349 pads of  $1.3 \,\mathrm{mm} \times 1.3 \,\mathrm{mm}$  with an active thickness of  $50 \,\mu\mathrm{m}$  fulfil these requirements. This 350 pad size ensures occupancies below 10% at the highest expected levels of pile-up, small 351 dead areas between pads, and low sensor capacitance, which is important for the time 352 resolution. 353

A custom ASIC (ALTIROC), which will be bump-bonded to the sensors, is being developed to meet the requirements on time resolution and radiation hardness. The ASIC will also provide functionality to count the number of hits registered in the sensor and transmit this at 40 MHz to allow unbiased, bunch-by-bunch measurements of the luminosity and the implementation of a minimum-bias trigger. After optimising the layout for timing performance and cost, the detector design described in this document will give an average of

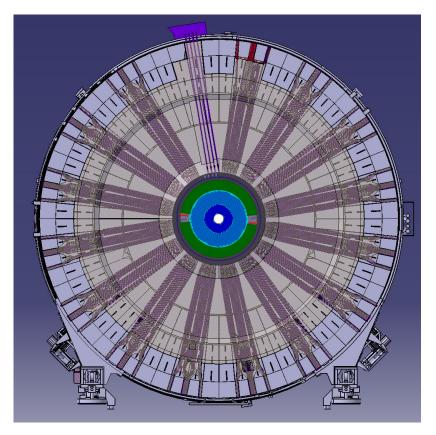

Figure 2.3: *TO BE UPDATED* Position of the HGTD within the ATLAS Detector. The HGTD acceptance is defined as the surface covered by the HGTD between a radius of 120 mm and 640 mm at a position of  $z = \pm 3.5$  m along the beamline, on both sides of the detector.

2.1, 2.5 and 2.7 hits per track for the regions 230 mm > r > 120 mm, 470 mm > r > 230 mmand 640 mm > r > 470 mm. A description of the detector layout optimisation is presented in Sec. 2.3. It covers the pseudo-rapidity range  $2.4 < |\eta| < 4.0$ .

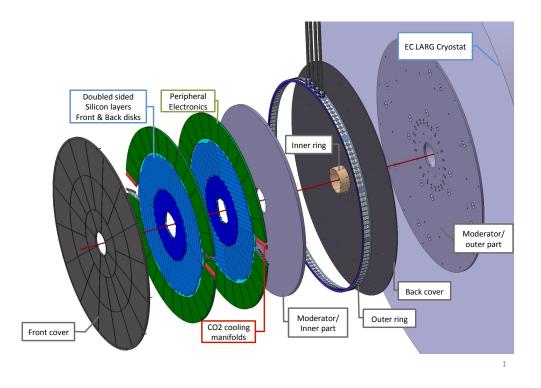

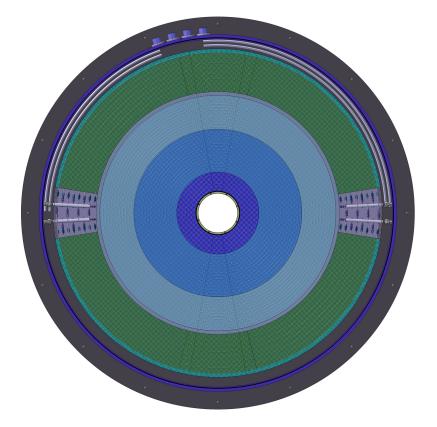

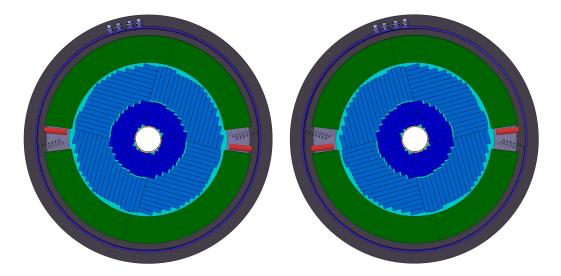

Each HGTD end-cap is the integration of one hermetic vessel, two instrumented doublesided layers (mounted in two cooling/support disks), and two moderator pieces placed inside and outside the hermetic vessel. Each cooling/support disk is physically separated in two half circular disks. Furthermore, the layers are rotated in opposite directions with respect to one another by 18° to 20° in order to maximize the hit efficiency.

A global view of the various components of the detector and its main parameters are shown in Fig. 2.4 and Tab. 2.1. The time resolution parameters have been optimised using information from the sensor Chap. 5 and front-end electronics Chap. 6 performance from lab and testbeam measurements.

## 372 2.3 Detector layout and optimisation

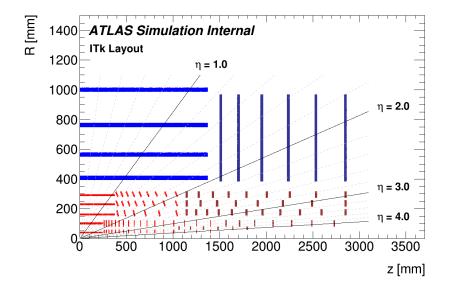

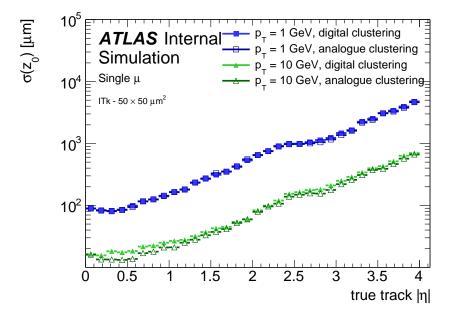

The goal of the detector design is to provide the best possible time resolution in order to effectively suppress the effects of pile-up in the forward region. The ability to associate tracks to primary vertices depends on the longitudinal impact parameter resolution of the ITk. The current ITk layout is shown in Fig. 2.5. Fig. 2.6 shows the resolution,  $\sigma_{z_0}$ , of the longitudinal

Figure 2.4: *TO BE UPDATED* Global view of the HGTD to be installed on each of two end-cap calorimeters. The various components are shown: hermetic vessel (front and rear covers, inner and outer rings), two instrumented double-sided layers (mounted in two cooling disks), two moderator pieces placed inside and outside the hermetic vessel.

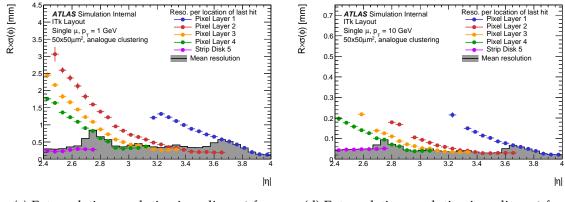

track impact parameter,  $z_0$ , from the ITk as a function of  $\eta$ , for  $p_T = 1$  GeV and  $p_T = 10$  GeV 377 muons. The resolution is shown for both digital and analogue clustering. Digital clustering 378 shows a similar performance to analogue clustering for  $p_{\rm T} = 1$  GeV muons and a 10–20 % 379 degradation in  $\sigma_{z_0}$  for  $p_T = 10$  GeV muons. Digital clustering takes the geometrical average 380 as the centroid of a given pixel cluster, while analogue clustering improves the ability to 381 determine the position by weighting the centroid by the charge deposited in each of the 382 pixels contributing to the cluster. In this report, performance studies have been performed 383 with an ITk layout and simulation [5] including a sensor pitch of  $50 \times 50 \,\mu\text{m}$  and digital 384 clustering, except where otherwise specified. 385

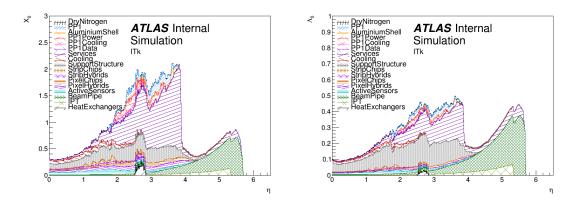

For good spatial separation of the HL-LHC collision vertices,  $\sigma_{z_0}$  should be significantly better than the inverse of the average pile-up density, 600 µm. Fig. 2.6 shows that, in the central region,  $\sigma_{z_0}$  is well below this limit. In the forward region, however, the resolution exceeds the limit by a large factor, reaching 3 mm for particles with low transverse momentum ( $p_T$ ) at  $|\eta| \approx 4$ , due to the combination of geometric projection and, as shown in Fig. 2.7, increased material. As a result, ITk by itself cannot associate such forward tracks to correct vertices in

1st January 2020 – 14:35

| Pseudo-rapidity coverage                                                  | $2.4 <  \eta  < 4.0$                                                            |  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|

| Thickness in z                                                            | 75 mm (+50 mm moderator)                                                        |  |

| Position of active layers in <i>z</i>                                     | $z=\pm 3.5\mathrm{m}$                                                           |  |

| Weight per endcap                                                         | 350 kg                                                                          |  |

| Radial extension:                                                         |                                                                                 |  |

| Total                                                                     | $110{ m mm} < r < 1000{ m mm}$                                                  |  |

| Active area                                                               | $120 \mathrm{mm} < r < 640 \mathrm{mm}$                                         |  |

| Pad size                                                                  | $1.3\mathrm{mm} 	imes 1.3\mathrm{mm}$                                           |  |

| Active sensor thickness                                                   | 50 µm                                                                           |  |

| Number of channels                                                        | 3.6 M                                                                           |  |

| Active area                                                               | $6.4 \mathrm{m}^2$                                                              |  |

| Module size                                                               | $30 	ext{ x 15 pads} (4 	ext{ cm} \times 2 	ext{ cm})$                          |  |

| Modules                                                                   | 8032                                                                            |  |

| Collected charge per hit                                                  | > 4.0 fC                                                                        |  |

| Average number of hits per track                                          |                                                                                 |  |

| $2.4 <  \eta  < 2.7$ (640 mm > r > 470 mm)                                | ≈2.1                                                                            |  |

| $2.7 <  \eta  < 3.5$ (470 mm > r > 230 mm)                                | ≈2.5                                                                            |  |

| $3.5 <  \eta  < 4.0$ (230 mm > r > 120 mm)                                | ≈2.7                                                                            |  |

| Average time resolution per hit (start and end of operational lifetime)   |                                                                                 |  |

| $2.4 <  \eta  < 4.0$                                                      | pprox 35 ps (start) $pprox$ 65 ps (end)                                         |  |

| Average time resolution per track (start and end of operational lifetime) | $\approx 30 \mathrm{ps} \mathrm{(start)} \approx 50 \mathrm{ps} \mathrm{(end)}$ |  |

Table 2.1: Main parameters of the HGTD.

#### <sup>392</sup> an unambiguous way.

In addition to the spatial distribution of collisions, pile-up collisions will also be distributed in time, with a Gaussian width in the range 175 to 260 ps. The current baseline working point is 175 ps, which is used in the simulation of the HGTD performance studies. HGTD is designed to provide a time-of-arrival measurement for incident tracks with a resolution of 30 ps at the beginning of the HL-LHC, degrading to 50 ps at the end of the HL-LHC. After determining the vertex position using the ITk, this complementary time measurement is significantly more precise than the spread of the beamspot in time.

With the combination of ITk and HGTD measurements, ATLAS can view a portion of the event in space and time, extending the pile-up rejection capabilities of the ITk to the extent of its acceptance. This is one of the main motivations for the HGTD.

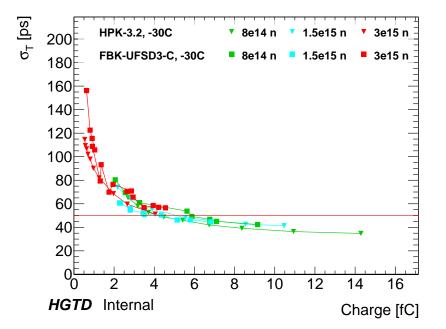

The main contributions to the time resolution of a detector element are:

$$\sigma_{\text{total}}^2 = \sigma_{\text{L}}^2 + \sigma_{\text{elec}}^2 + \sigma_{\text{clock}}^2$$

(2.1)

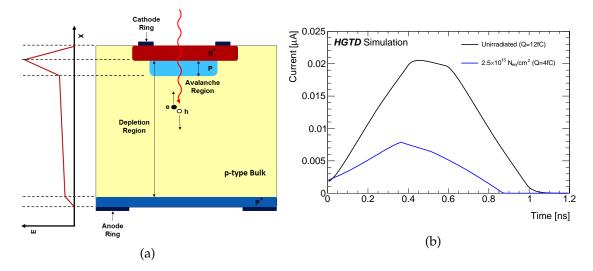

where  $\sigma_{\rm L}^2$  are Landau fluctuations in the deposited charge as the charged particle traverses the sensor,  $\sigma_{\rm elec}^2$  represents the contributions from the readout electronics, and  $\sigma_{\rm clock}^2$  is the clock contribution. Beam tests and sensor simulations show that thinner silicon sensors reduce the contribution from Landau fluctuations. With a 50 µm thick LGAD sensor, this contribution amounts to approximately 25 ps. This is further discussed in Chap. 5. With fast

Figure 2.5: Schematic layout of the ITk for the HL-LHC phase of ATLAS. The active elements of the barrel and end-cap ITk Strip detector are shown in blue, for the ITk Pixel detector the sensors are shown in red for the barrel layers and in dark red for the end-cap rings. Here only one quadrant and only active detector elements are shown.

detector signals and a high signal-to-noise ratio, the contribution from the electronics can be

kept to approximately 25 ps. This is achievable only if applying corrections for the time walk

induced by different signal amplitudes, using small bins in the time-to-digital conversion

and applying precise in-situ inter-calibration. The details of the design of the readout

electronics to achieve this are described in Chap. 6. The clock contribution is required to be

below 15 ps; its distribution is discussed in more detail in Chap. 10.

For simplicity, the same pad size,  $1.3 \text{ mm} \times 1.3 \text{ mm}$  is used for the entire HGTD. This pad size balances several characteristics. For smaller pad sizes, both electronic noise and physics occupancy are smaller, while the number of channels to be instrumented and the cumulative area of inter-pad dead zones are larger. The size was chosen to give a maximum occupancy at the lowest instrumented radius, 120 mm, of less than 10%. This also ensures a low double-hit probability.

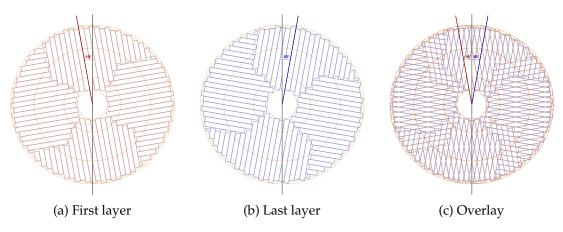

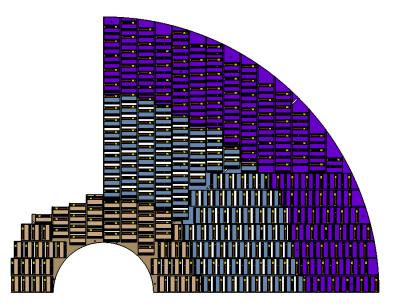

The layout of modules in each endcap was defined by maximising the coverage and minimising the effect of non-instrumented regions due to mechanical tolerances. In the second step the spacing between modules was defined.

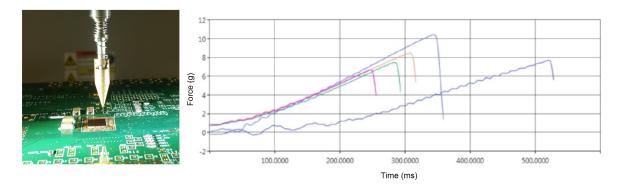

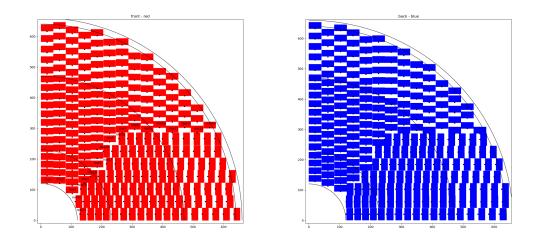

The readout rows are sets of modules whose flex cables are guided together towards larger radii to the peripheral on-detector electronics. Their disposition for the first and last layer is shown as rectangles in Fig. 2.8. The active width of a module is 39 mm which limits how well the area near the circular opening at 120 mm can be covered. For r > 150 mm, the coverage

Figure 2.6: Resolution of the longitudinal track impact parameter,  $z_0$ , as a function of  $\eta$  for muons of  $p_T = 1 \text{ GeV}$  and  $p_T = 10 \text{ GeV}$ . Additionally, the figure highlights the difference in resolution whether analogue or digital clustering is used. Studies for this report use digital clustering, which have roughly a 10 % degradation in  $z_0$  resolution for  $p_T = 10 \text{ GeV}$  muons.

Figure 2.7: Radiation length  $X_0$  (left) and nuclear interaction length  $\lambda_0$  (right) as a function of pseudorapidity  $\eta$ , broken down by type of material for the ITk Layout [5] and beam pipe. *Preliminary, to be updated in new release*

is complete. The maximum length of the readout rows is limited by the manufacturing

capabilities for the flexible circuits used for the data transmission. The non-instrumented

zone is 0.5 mm between two readout rows for each row to account for mechanical tolerances.

The effective width of a readout row is therefore 41 mm. These constraints lead to the helix

structure shown in Fig. 2.8. A particle transiting the detector should encounter multiple

layers of LGAD sensors as it enters (encountering a "first layer") and exits (after encountering 432 a "last layer"). Fig. 2.8(a) shows the geometry of the first layer and Fig. 2.8(b) shows the 433 geometry of the last layer. The first and last layer are arranged to mirror the geometry of 434 one another. Therefore the non-instrumented zones of the two disks will not overlap, except 435 in the case of four readout rows per quadrant. Additionally, each of the layers is rotated in 436 opposite directions by 18° to 20° as shown in Fig. 2.8(c) for 20°. Any angle of rotation beyond 437 10° results in similar performance in terms of the number of hits and dead regions. The 438 baseline angle is chosen largely due to detector services considerations, which are further 439 discussed in Chap. 12 and Chap. 13. Along with optimising the coverage, the rotation 440 frees sufficient room at 640 mm to install the cooling equipment between the peripheral 441 electronics. 442

Figure 2.8: The orientation of the readout rows for the first and last layer encountered by a particle, separately and with the overlay of both. Each layer is rotated in alternating directions by 20°.

The geometry of the detector has been optimised to approximate a flat timing resolution 443 as a function of  $\eta$ . Due to radiation damage, the timing resolution of the detector will 444 be degraded as the integrated luminosity delivered by the LHC increases. This radiation 445 depends strongly on r, with higher radiation closer to the beam axis. The radiation levels 446 expected for the full lifetime of the HL-LHC, including safety factors, are discussed in Sec. 2.4. 447 The geometry of the HGTD is designed such that at r < 230 mm on average about 2.7 hits 448 are obtained for a charged particle, for 230 mm < r < 470 mm on average about 2.5 hits are 449 obtained, whereas at r > 470 mm on average about 2.1 hits are expected to be associated to 450 a track. 451

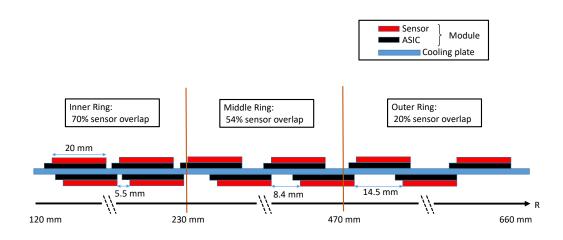

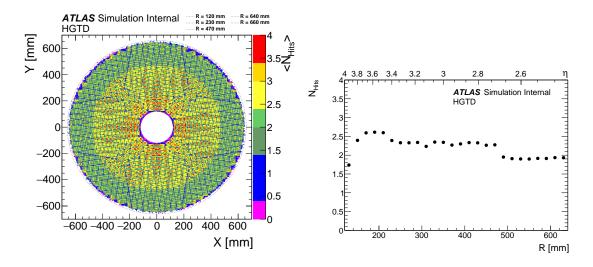

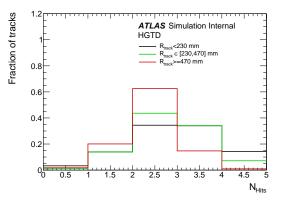

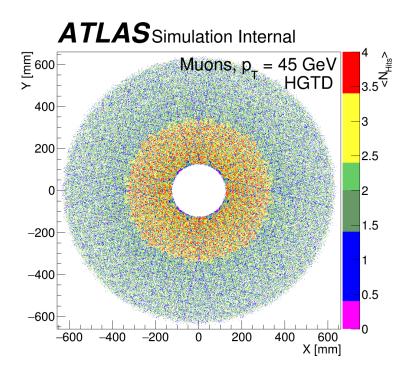

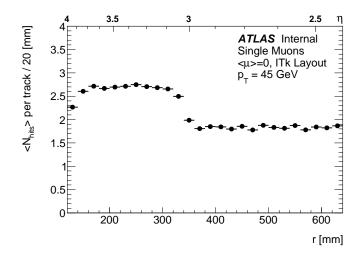

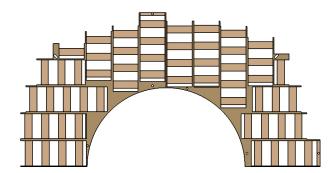

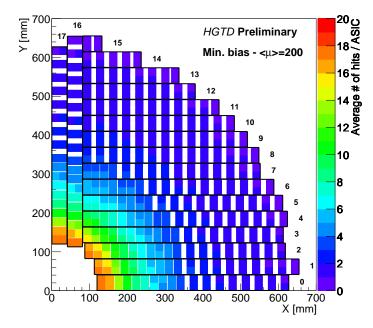

Each layer of the HGTD is double-sided, i.e., the modules with sensors and on-detector electronics are mounted on the front and back sides of a common cooling disk. As illustrated in Fig. 2.9, the modules on the two sides of a disk are arranged to overlap so that the number of hits exceeds the number of disks. A study using full simulation was performed to determine the optimal overlap between modules in r < 230 mm to achieve the required timing resolution via the average number of hits given the expected time resolution of the <sup>458</sup> pads. The maximal overlap is limited by the need for sufficient space between the modules to <sup>459</sup> allow the read out of the data. For r > 470 mm, an overlap of 20%, for 470 mm > r > 230 mm <sup>460</sup> an overlap of 54% and for r < 230 mm an overlap of 70% was the result of the optimisation. <sup>461</sup> The HGTD acceptance is defined as the surface covered by the HGTD between a radius <sup>462</sup> of 120 mm and 640 mm. The number of hits as a function of radius and trasvenrse plane <sup>463</sup> position is shown in Fig. 2.10. The relative fraction of tracks as a function of hits per track for

each ring can be found in Fig. 2.11.

Figure 2.9: The schematic drawing shows the overlap between the modules on the front and back of a cooling disk. There is a sensor overlap of 20% for r > 470 mm, 54% for 470 mm > r > 230 mm and 70 % for r < 230 mm.

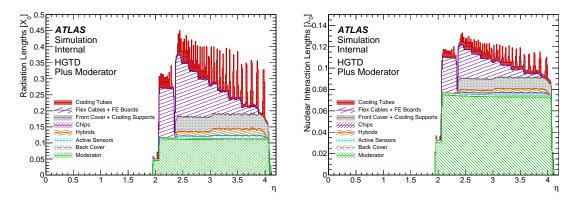

The material for the HGTD is highlighted in Fig. 2.12, which includes the material for the moderator located behind the active sensor area of the HGTD.

Beyond pile-up mitigation, HGTD can play a key role in the HL-LHC physics programme 467 as a luminometer. An accurate luminosity determination will be a critical input for corner-468 stone precision measurements. The luminosity uncertainty can be a limiting factor to many 469 precision cross-section measurements, including achieving  $\mathcal{O}(1\%)$  accuracy on certain meas-470 urements of Higgs boson production and couplings. It is therefore important to be able to 471 determine the luminosity as accurately as in Phase-I, which will be a challenge with the 472 harsh environment at the HL-LHC. For the technologies used traditionally for luminometers, 473 the increased pile-up leads to increased detector occupancies, posing serious problems. The 474 HGTD provides unique and pile-up-robust capabilities for measuring the luminosity at the 475 HL-LHC. 476

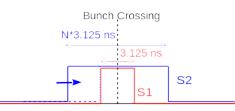

Taking advantage of the high granularity of the detector, the luminosity can be measured

Figure 2.10: Hit multiplicity as function of X,Y and R.

Figure 2.11: Fraction of tracks as a function of number of Hits in the track for tracks in the inner, middle and outer ring.

by counting the mean number of hits in the detector, a quantity linearly proportional to the

average number of interactions per bunch crossing. The counting will be done over two

time windows, one centred at the bunch crossing and with a width of 3.125 ns, the other

with both width and relative position tunable with a step of 3.125 ns. The application of

these capabilities and their implementation are further discussed in in Sec. 3.3.2, Chap. 6,

and Chap. 10.

1st January 2020 - 14:35

Figure 2.12: Radiation length  $X_0$  (left) and nuclear interaction length  $\lambda_0$  (right) as a function of pseudo-rapidity  $\eta$ , broken down by type of material for the HGTD. The moderator is included as it is within the hermetic vessel, although it is situated completed behind the active area of the HGTD. The baseline cooling pipes will be made with Titanium, which will reduce the peaks amplitude by almost a factor of 2.

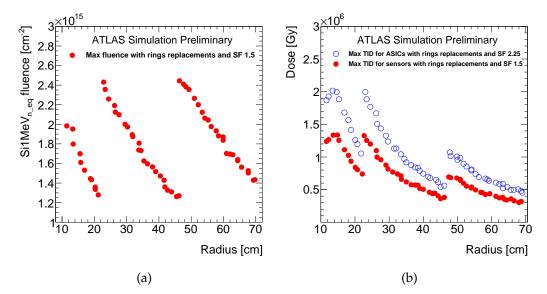

### 484 2.4 Radiation hardness

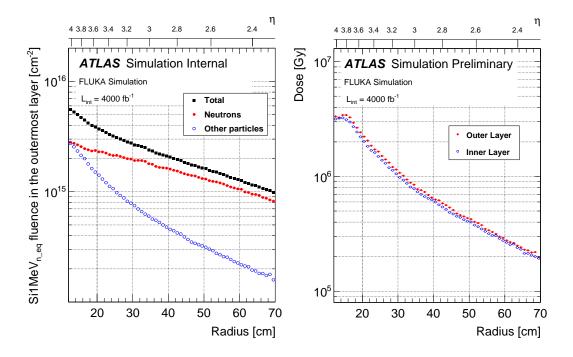

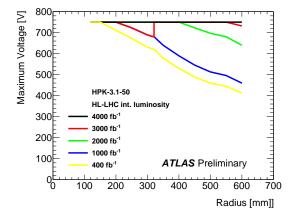

One of the most important parameters of the HGTD will be radiation hardness of the sensors 485 and electronics. Given that the HGTD will be installed with a pseudo-rapidity coverage 486 of 2.4  $< |\eta| <$  4.0, it is crucial that the detector can withstand the lifetime of the HL-LHC 48 running. At the end of the HL-LHC ( $4000 \text{ fb}^{-1}$ ), the maximum nominal neutron-equivalent 488 fluence at a radius of 120 mm, should reach  $5.6 \times 10^{15} \, n_{eq} \, cm^{-2}$  and the total ionising dose 489 (TID) will be about 3.3 MGy, as shown in Fig. 2.13. To account for uncertainties in the 490 simulation, a safety factor of 1.5 is applied to both numbers. An additional factor of 1.5 is 49<sup>.</sup> applied to the TID due to uncertainties in the behaviour of the electronics after irradiation. 492 This leads to a total safety factor of 1.5 for the sensors that are most sensitive to the particle 493 fluence, and 2.25 for the electronics which are more sensitive to the TID. After applying 494 these, the detector would need to withstand  $8.3 \times 10^{15} \,\mathrm{n_{eq}} \,\mathrm{cm}^{-2}$  and  $7.5 \,\mathrm{MGy}$ . 495

This amount of radiation damage to lowest-radius (r < 230 mm) sensors and electronics 496 suggests that this innermost part of the detector should be replaced after each 1000fb<sup>-1</sup>and 497 the sensors and electronics within 470 mm > r > 230 mm should be replaced at half lifetime 498  $(2000 \text{ fb}^{-1})$  of data-taking during the HL-LHC program. The plan is therefore to replace the 499 sensors and ASICs located at a radius up to about r > 230 mm three times and the sensors 500 and electronics located within 470 mm > r > 230 mm once. This corresponds to about 52% 501 of the sensors and ASICs. Consequently, in the proposed 3 rings layout the maximal TID 502 and fluence, using the Fluka estimations of September 2019, does not exceed 2 MGy and 503  $2.5 \times 10^{15}$  neq/cm<sup>2</sup>. In the inner ring the total Si 1MeV neq has a similar contribution from 504 neutrons and charged particles while in the middle and outer rings the dominant effect 505 comes from neutrons, as seen in Fig. 2.13. The exact radial transition between the three rings 506

(a) Nominal Si1MeV $_{n_{eq}}$  fluence for HL-LHC. (b) Nominal ionising dose for HL-LHC.

Figure 2.13: Expected nominal Si1MeV<sub>neq</sub> fluence and ionising dose as functions of the radius in the outermost sensor layer of the HGTD for  $4000 \text{ fb}^{-1}$ , i.e. before including safety factors. The contribution from charged hadrons is included in 'Others'. These estimations used Fluka simulations using ATLAS Fluka geometry 3.1Q7 (from December 2019).

will be tuned for the final detector layout, once the FLUKA simulations will be updated

with the final ITk layout, and the radiation hardness of the final sensors and ASICs are

re-evaluated.

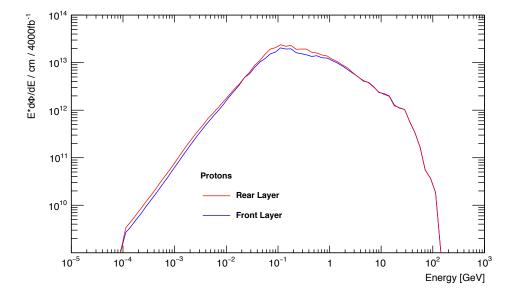

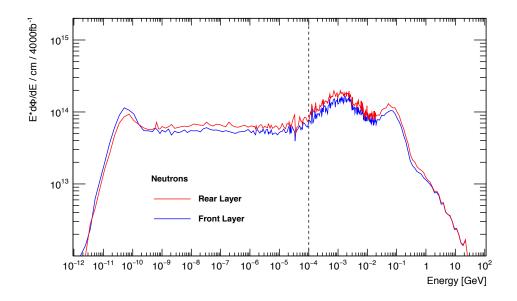

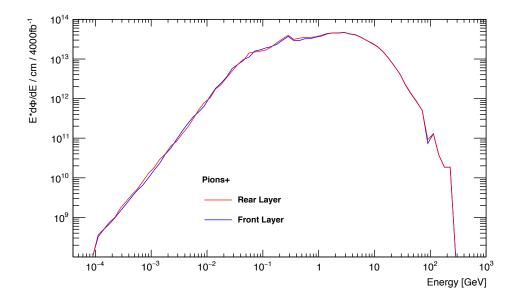

<sup>510</sup> More details can be found in Chap. 5 to Chap. 6. The maximum fluence and total ionising

dose as a function of the radial position including the replacement of the rings can be found

<sup>512</sup> in Fig. 4.2. The expected proton, neutron, and pion energy spectra in the HGTD front and

rear layer after  $4000 \text{ fb}^{-1}$  are shown in Fig. A.1, Fig. A.2, and Fig. A.3.

# **3 Performance and Physics Benchmarks**

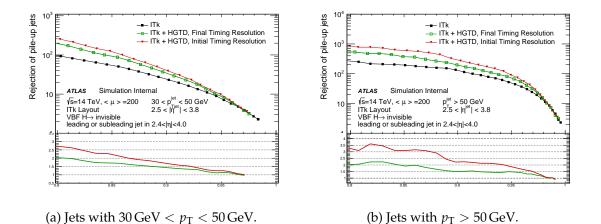

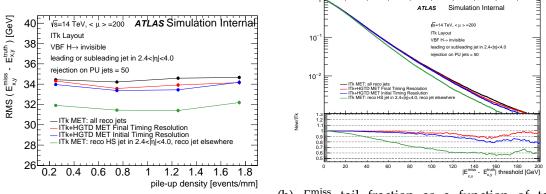

The precision time measurement capability of the HGTD enhances the performance for hard scatter jet tagging, missing transverse momentum  $E_{\rm T}^{\rm miss}$ , tagging *b*-jets, and lepton isolation in the forward region. Additionally the timing structure of non collision background (NCB) is analysed. The impact of these improvements on the sensitivity of a few selected physics analyses is presented. The HGTD timing capabilities will provide a luminosity measurement, a discussion on the impact of the precision of this measurement as well as the systematic errors are also included.

### 522 3.1 Simulation

The full simulation of the HGTD is performed using a software release dedicated to the ATLAS Upgrade program. The production of simulated samples follows the same steps as regular ATLAS simulation based on the Run 2 offline software chain: event generation, detector simulation, digitisation of simulated energy deposits into the actual detector readout data format, and event reconstruction starting from the digitised data.

The simulation of the HGTD was implemented as close as possible to the layout foreseen. In the direction of the beam axis the HGTD implementation starts at 3420 mm. Behind the HGTD before the cryostat wall two moderators with a total thickness of 50 mm are implemented.

#### 532 3.1.1 Detector geometry

The GEANT4 toolkit [6] is used to simulate the ATLAS detector. The simulation uses 533 dedicated GeoModel packages to implement the detector geometry which is converted, via 534 dedicated tools, to GEANT4 volumes. Particles are propagated through this geometry and 535 the various physics processes, caused by their interaction with the detector material, are 536 simulated. In sensitive detector elements, processes ranging from energies of a few eV, such 537 as the ionisation in gases, up to TeV energies are simulated to provide a detector-response 538 model as realistic as possible. The simulation step produces hits, i.e. small steps in the 539 material with a starting point, an end point and the amount of energy deposited by the 540 particle. 541

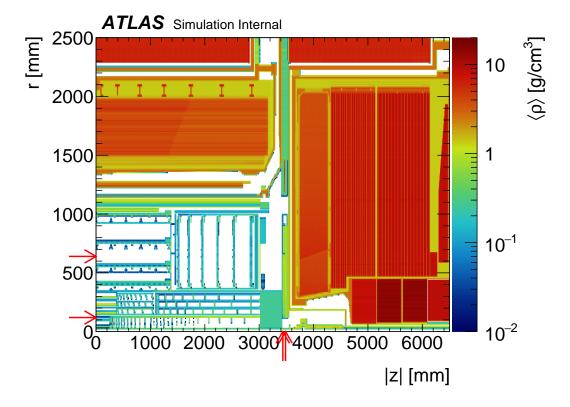

Figure 3.1: The material density is shown as function of z and radius. The extent of the active part of the HGTD in z and r direction, 500 mm and 520 mm respectively, is indicated by the arrows. TODO: This figure needs to be updated.

In Fig. 3.1, the material density of the upgraded ATLAS detector is shown as a function of the beam axis and the radius. The active part of the HGTD extends from 120 mm to 640 mm

544 in radius.

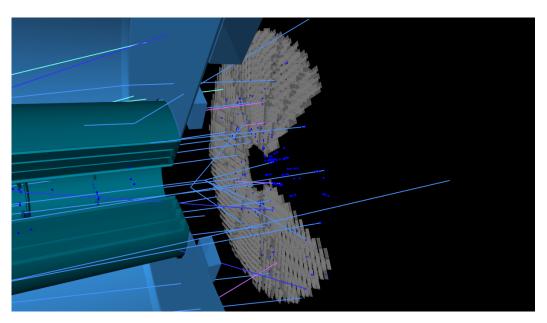

There are four individual layers per endcap, the silicon sensors are mounted on both sides of the two cooling ensembles. The simulation of the HGTD has been extended to implement the peripheral electronics at radii greater than 640 mm. As an illustration a simulated event is shown in Fig. 3.2.

The simulation of the HGTD includes front and back covers and heaters of the HGTD. The simulation of the cooling plates, the CO<sub>2</sub> cooling loops as well as the support plates for the modules is also implemented. Volumes mimicking the peripheral electronics have also been implemented in the simulation.

$_{553}$  The modules are the ASICs plus the sensors. These are simulated as boxes of size 22 mm imes

$_{554}$  40 mm with silicon sensors of size 20.5 mm imes 40 mm perpendicular to the direction of the

<sup>555</sup> beam axis. The modules are slightly larger than the sensors in one dimension to account for

Figure 3.2: The simulation of an event in the HGTD is shown.

the wirebonding of the ASIC to the silicon sensor. The total thickness of the silicon sensor is

$_{557}$  250  $\mu$ m with an active thickness of 50  $\mu$ m a passive thickness of 200  $\mu$ m, corresponding to

the LGAD sensor design. In total, 3992 modules are present in each end-cap. TODO: Check

these numbers - do we use two-ring or three-ring layout here?

<sup>560</sup> The Flex PCBs connecting the ASICs to the peripheral electronics beyond 640 mm have also

<sup>561</sup> been implemented in the simulation. This leads to an increase of the material distribution of

<sup>562</sup> the HGTD as the radius increases.

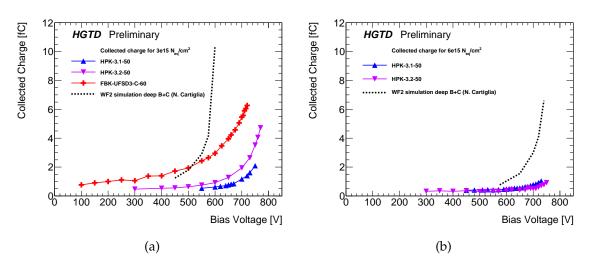

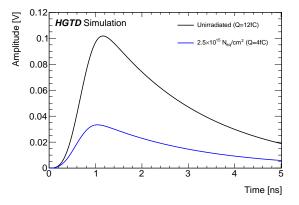

### 563 3.1.2 Sensor simulation

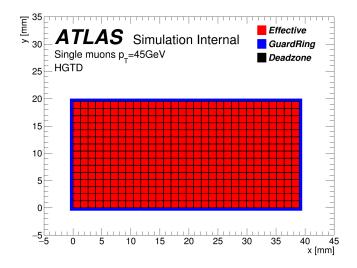

The baseline of  $1.3 \text{ mm} \times 1.3 \text{ mm}$  is used for the padsize. Two sources of inefficiency are taken into account at simulation time. The guard ring of 0.5 mm and the inter-pad dead zone of 50  $\mu$ m are implemented. The active area is 79% of the total silicon area. The different zones of the sensors are illustrated in Fig. 3.3.

The digitization and clustering steps are implemented using silicon pixel hits and contains functionality for associating truth information to the simulated hits. The digitization step generates a detector signal with a pulse shape extracted from beam tests of LGAD sensors, adds expected electronic noise and is capable of describing the timing performance expected at various points during the HL-LHC program. The expected timing resolution depends on the radiation the detector has been exposed to, and this is implemented through with increasing integrated luminosity.

1st January 2020 - 14:35

Figure 3.3: The simulation of the HGTD sensor is shown separated into the active area, the guard ring and the inter–pad deadzones using the simulation of single muons.

The active area of each pad is associated with a unique identifier. In the digitization step for  $\langle \mu \rangle = 200$ , the hits from the different interactions are summed in energy if they are in the same 5 ps time bin (TODO: Check to what extent this is true for SiHits). To allow for maximum flexibility at the analysis stage, the hits are then copied down to the format used for the analysis. The timing information is stored after subtracting a global offset of 11.6 ns, corresponding to the time of flight from the nominal interaction point to the center of the HGTD.

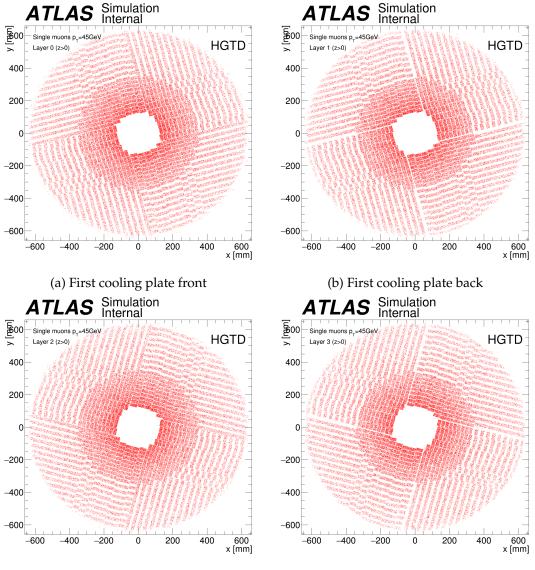

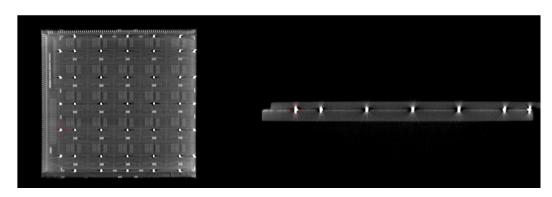

In Fig. 3.4 the hits in the HGTD are shown in the transverse plane for the two cooling plates with modules on the front and back for positive *z*. The position of the modules can be identified. The displacement of modules mounted on the back of a cooling plate with respect to those mounted on the front of each cooling plate is shown. The transition around 320 but outofdate from an overlap of 80% to 20% is visible as decreased density of sensors. The mirror symmetry between the first and second cooling disk as well as the rotation of 15° of each of the cooling disks is observed.

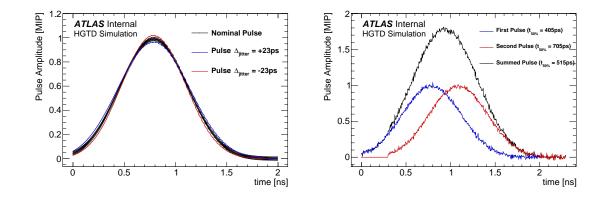

The simulation provides the energy deposit in the sensitive layer of the HGTD as single 589 energy deposit for each particle traversing it. The simulation of the non-uniform distribution 590 of the charges in the sensitive volume as well as the effect of the electronics chain (time walk, 59 jitter) are taken into account at analysis level. For each hit a pulse is simulated to compute 592 the time and energy in each pad. Data derived from the 2016 HGTD test beam were used to 593 derive the pulse shape. A convolution of a Gaussian with a Landau distribution was found 594 to give the best description of the pulse shape. The non-uniform energy deposit is modeled 595 via the width of the Gaussian. The signal time is defined on its leading edge, therefore the 596

(c) Second cooling plate front

(d) Second cooling plate back

Figure 3.4: The positions of simulated hits in the transverse plane for each of the four layers separately. Only hits in active parts of the detector elements are shown. The position of the modules, the mirror symmetry between the first and second cooling plate as well as the rotation are clearly visible. TODO: These plots need to be updated to be made with SiHits, or just replaced with the figures showing the placement of the modules.

Figure 3.5: The simulated shape in time of the signal in a pad of the HGTD is shown for (a) a normal hit and (b) a double hit, separated by 300 ps.

- variation models adequately the induced timing uncertainty. Fig. 3.5 shows the nominal

shape and the effect of two hits in the same pad, separated by 300 ps.

- <sup>599</sup> For each hit, a pulse is simulated with 200 points of a step size of 5 ps where the width of

Gaussian contribution is driven by the desired timing resolution of the sensor. The maximal

amplitude of the pulse is the deposited energy. The time corresponding to the first point of

the pulse is chosen to be the time of the hit. Additionally a Gaussian noise with of 1.5% of

the energy of a MIP (0.2 keV) is added to the amplitude in each time bin.

For each pad, the pulses are then summed together. A pseudo constant fraction discriminator (CFD) algorithm defines the time as the time of the first point with an energy above 50% of the maximum amplitude. Therefore the time of a pad is offset by 0.405 ns.

The contribution of electronic noise to the timing resolution is taken into account as a function of the position of the sensor and the accumulated integrated luminosity with a Gaussian smearing. The dose received by the sensor as a function of its radius was computed using FLUKA, then data from test bench measurements of sensors define the corresponding gain for the sensor. The gain is transformed into the timing resolution using measurements with ALTIROC0. This procedure results in a Gaussian smearing of minimum 10 ps and maximum 60 ps.

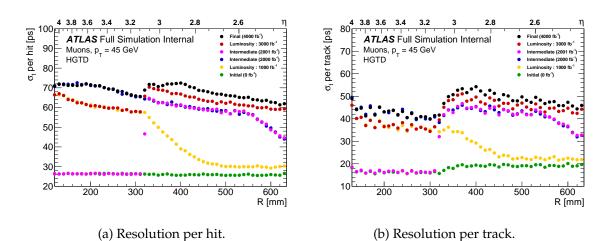

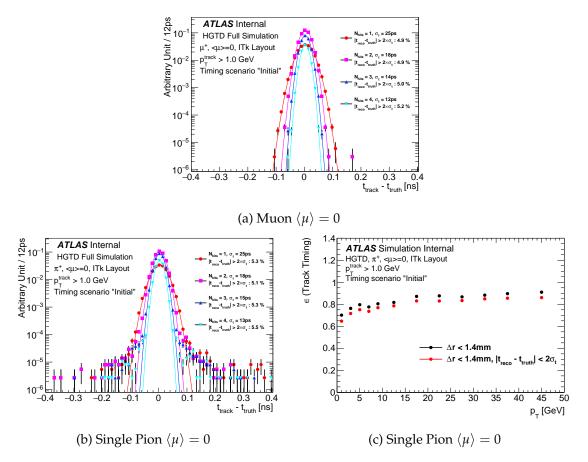

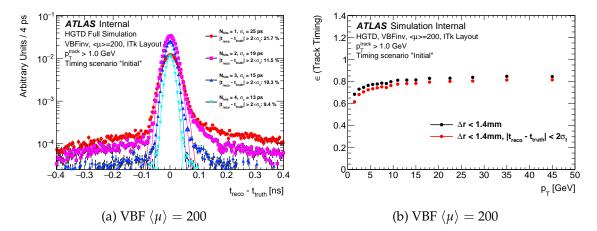

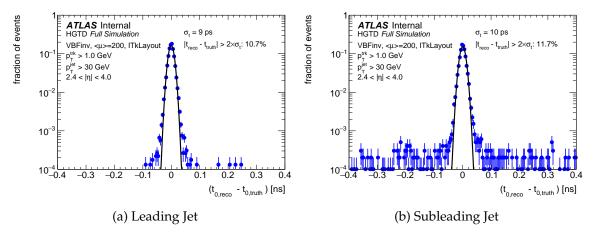

#### 614 Timing Resolution Scenarios

Four timing performance scenarios are defined: *Initial*, two *Intermediate* scenarios and *Final* corresponding to integrated luminosities of 0 fb<sup>-1</sup>, 2000 fb<sup>-1</sup>, 2001 fb<sup>-1</sup> and 4000 fb<sup>-1</sup> which are shown in Fig. 3.6. The scenarios correspond to the performance expected at the beginning, after half of the expected integrated luminosity, after half of the expected

Figure 3.6: The HGTD timing resolution is shown as function of the radius for four timing scenarios. The sensor resolution and the contribution from the electronics are considered, added in quadrature.

integrated luminosity after replacement of the inner part of the HGTD and at the end of the HL-LHC data taking. Two additional scenarios for  $1000 \text{ fb}^{-1}$  and  $4000 \text{ fb}^{-1}$  are also shown to illustrate the change of the resolution as the integrated luminosity increases. Maintaining this performance as the clock is distributed across the detector will require intercalibrating the reference  $t_0$ , discussed in Sec. 10.2.

As the integrated luminosity increases, the damage to the sensors and electronics caused 624 by radiation will deteriorate their timing resolution inducing a dependence on the radial 625 distance from the beam axis. The replacement of the inner part (r < 320 but outofdate) 626 of the HGTD after half of the HL-LHC programme leads to identical performance of the 627 timing resolution in this region for the *Intermediate* for  $2000 \, \text{fb}^{-1}$  and *Final* scenarios. In 628 the simulation the replacement has been implemented only as function of the radius so 629 only pads at a radius below 320 but outofdate are replaced. This is conservative as the 630 entire module will be replaced which will lead to an improved performance above 320 but 631 outofdate. Fig. 3.6 has bins of 10 mm so that after the replacement the transition region at 632 320 but outofdate has contributions from both regions. The timing resolution for a hit at a 633 radius of 120 mm is expected to be degraded to the order of 70 ps after  $2.5 \times 10^{15}$  n<sub>ea</sub> cm<sup>-2</sup>. 634 including the replacement. 635

The resulting timing resolution for tracks is shown in Fig. 3.6(b) for the four scenarios as 636 well as for the two additional scenarios of  $1000 \, \text{fb}^{-1}$  and  $4000 \, \text{fb}^{-1}$ . At radii lower than 320 637 but outofdate ( $|\eta| \approx 3.1 but out of date$ ), the increased number of hits compensates the effects 638 of radiation damage such that the resulting timing resolution is fairly independent of the 639 radius. The per-hit resolution was implemented in full simulation. The reconstructed timing 640 resolution for tracks shown here was determined using the single-muon events by comparing 64 the reconstructed hit or track time to the expected time from the truth information. The hits 642 closest to the extrapolation of the reconstructed muon track within a window of 1.4 mm are 643

| Process                                                          | Generator      | N events, $\langle \mu \rangle = 0$ | N events $\langle \mu \rangle = 200$ |

|------------------------------------------------------------------|----------------|-------------------------------------|--------------------------------------|

| Minimum Bias, high- $p_{\rm T}$                                  | Pythia8        | 1000000                             |                                      |

| Minimum Bias, low- $p_{\rm T}$                                   | Pythia8        | 1000000                             |                                      |

| Single $\pi^+$ , $p_T = 5$ GeV, flat $\eta$ [2.3-4.3]            |                | 200000                              | 200000                               |

| Single $\pi^+$ , $p_{\rm T} = 20$ GeV,                           |                | 200000                              | 200000                               |

| Single $\pi^+$ , $p_{ m T}=45$ GeV,                              |                | 2000000                             | 2000000                              |

| Single $\pi^+$ , flat $\eta$ [2.3-4.1], flat $p_T$ [0.1-5.0]GeV  |                | 200000                              | 200000                               |

| Single $\pi^0$ , flat $\eta$ [2.3-4.1], flat $p_T$ [0.1-5.0] GeV |                | 200000                              | 200000                               |

| Single $\gamma$ , $p_{\rm T} = 20$ GeV, flat $\eta$ [2.3-4.3]    |                | 200000                              | 200000                               |

| Single $\gamma$ , $p_{\rm T} = 45$ GeV, flat $\eta$ [2.3-3.2]    |                | 200000                              | 200000                               |

| Single $\gamma$ , $p_{\rm T} = 100$ GeV, flat $\eta$ [2.3-3.2]   |                | 50000                               | 50000                                |

| Single $\mu$ , $p_{\rm T} = 45$ GeV, flat $\theta$               |                | 400000                              | 400000                               |

| Single $\mu$ , $p_{\rm T} = 45$ GeV, flat $\eta$ [2.3-3.2]       |                | 300000                              | 300000                               |

| Single $\mu$ , $p_{\rm T} = 45$ GeV, flat $\eta$ [3.2-4.3]       |                | 100000                              | 100000                               |

| Single electron, $p_T = 45$ GeV, flat $\eta$ [2.3-4.3]           |                | 400000                              | 400000                               |

| Single electron, $p_{\rm T} = 20$ GeV, flat $\eta$ [2.3-4.3]     |                | 200000                              | 200000                               |

| NCB beam–gas, oxygen                                             |                | 400000                              |                                      |

| NCB beam–gas, carbon                                             |                | 400000                              |                                      |

| NCB Beam–gas, hydrogen                                           |                | 400000                              |                                      |

| $Z \rightarrow ee$                                               | Powheg+Pythia8 | 100000                              | 100000                               |

| m Z  ightarrow 	au 	au                                           | Powheg+Pythia8 | 400000                              | 400000                               |

| $t\bar{t}$                                                       | Powheg+Pythia8 | 1000000                             | 1000000                              |

| VBF $H \rightarrow ZZ \rightarrow 4\nu$                          | PowhegPythia8  | 500000                              | 500000                               |

| Dijet production, X GeV $\hat{p}_{T} < Y$ GeV                    | Pythia8        | 1000 000                            | 1000000                              |

| Dijet production, X GeV $\hat{p}_{T} < Y$ GeV                    | Pythia8        | 1000 000                            | 1000000                              |

| Dijet production, X GeV $\hat{p}_{T} <$ Y GeV                    | Pythia8        | 1000 000                            | 1000000                              |

Table 3.1: Monte Carlo events simulated, digitized and reconstructed with Athena releases AtlasProduction-20.20.14.4-6 using the Step 3.1 ITk geometry (geometry tag ATLAS-P2-ITK-17-04-02).

<sup>644</sup> used in this study. The distribution is dominantly Gaussian with negligible tails.

#### 645 **Production**

The simulation, digitisation and reconstruction was implemented in the ATLAS upgrade 646 software releases 20.20.14.1 and 20.20.14.2 deployed on the grid. Samples of single particles, 647 electrons, muons and pions as well as non-collision background (NCB) and selected physics 648 processes such as  $t\bar{t}$ , VBF  $H \rightarrow Z(\nu\nu)Z(\nu\nu)$  and monopoles were produced using the ATLAS 649 production system. Pythia8 [7] was used together with Powheg [8–10] for most of the 650 samples. In the simulation step the beamspot was simulated with the spread in z and t. 651 Samples with  $\langle \mu \rangle = 0$  as well as  $\langle \mu \rangle = 200$  were processed. A summary of the samples 652 is shown in Tab. 3.1. For the minimum bias (inelastic collisions in the underlying event) 653 samples, a signal set of single neutrinos was used at  $\langle \mu \rangle = 200$ . 654

#### 655 3.1.3 Simulation using silicon hits

#### 656 Digitisation

<sup>657</sup> The Geant4 simulated hits are processed in a digitisation step in order to emulate the detector <sup>658</sup> electronics output. THe HGTD LGADs are simulated adapting the ATLAS ITk pixel offline <sup>659</sup> software. They are described as planar n-in-p pixel sensors with electron carriers. The <sup>660</sup> channel efficiency is simulated as perfect for hits above threshold, also without simulated <sup>661</sup> defects. As described in Sec. 3.1.2, the HGTD sensors are implemented to have pixels with <sup>662</sup> a size of 1.3 mm × 1.3 mm, a 0.5 mm thick guard ring and inter-pixel dead zones of 50  $\mu m$ . <sup>663</sup> The active thickness of the silicon sensors is 50  $\mu m$ .

During digitisation, the energy deposited for each Geant4 step in the active silicon volume 664 is used to evaluate the free charge and the drift time to the readout surface accordingly to 665 the sensor thickness, carries mobility, depletion and bias voltage and Lorentz shift. The 666 front-end electronics in-time threshold is set to 600 electrons, with an intrinsic standard 667 deviation of 40 electrons added in quadrature with a noise standard deviation of 75 electrons. 668 Given the characteristics of the sensors, the capacitive coupling to nearby pixels is considered 669 negligible as studied in LGAD beam tests and discussed in Chap. 5 and cross-talk effects 670 are not simulated. 671

The time measurement associated to each energy deposition in the sensor is obtained smearing the time of the Geant4 interaction in the silicon with a sensor time resolution of 30 ps. At this point, the algorithm estimates the total charge released in each pad and checks if it is above threshold. Pads above threshold are labelled as fired.

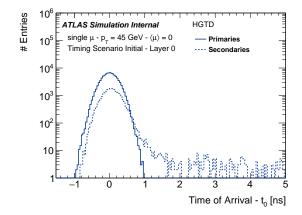

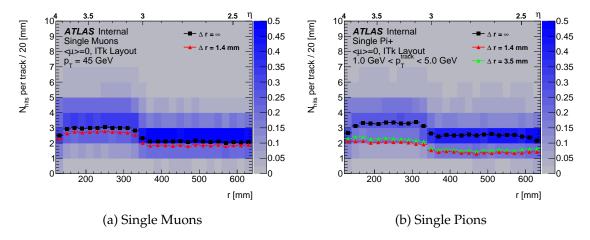

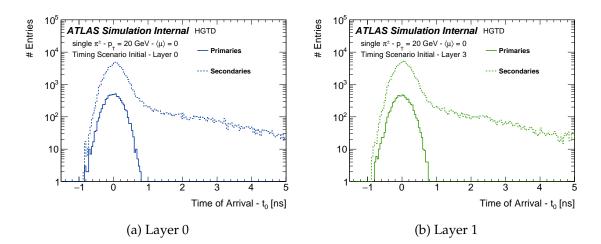

The time structure of the energy depositions in the active area of HGTD sensors in the first 676 layer is shown in Fig. 3.7 for the Initial timing scenario. The time distribution is obtained 677 subtracting for each deposit the expected time of arrival accordingly to the position of the 678 sensor and assuming a straight line trajectory from the center of the detector. For all layers, 679 the deposits originating from primary and secondary particles are in time for the bulk of the 680 distribution. However secondaries create also a pronounced tail in the timing distribution. 681 In the following, only fired pads characterised by energy depositions in [-1.0, +1.0] ns 682 time window around the expected time of arrival are taken into account. The first energy 683 deposition determines the time measurement to be associated to each of them. 684

#### 685 Clustering

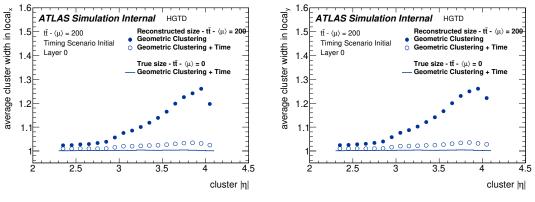

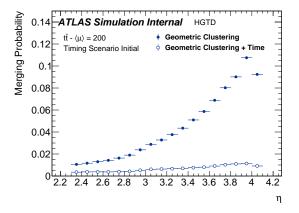

The first step of event reconstruction is the formation of clusters from the individual channels of the HGTD. For silicon-based detectors, like the ITk pixel and strip detectors, this is a local

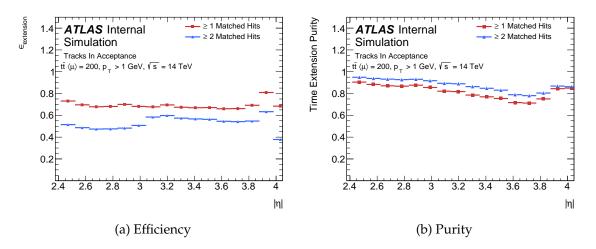

pattern recognition step where adjacent readout channels are grouped together in clusters,