# Update on TPC R&D at IHEP

Huirong Qi and Zhi Deng Zhiyang Yuan, Yiming Cai, Yue Chang, Jian Zhang, Ye Wu, Wei Liu, Yulan Li, Hongyu Zhang, Hui Gong IHEP and Tsinghua 2, June, 2020

#### Outline

# Status of TPC detector Status of ASIC R&D Status of the collaboration

✓ All of update progress will be reported: "Development of IBF suppression TPC integrated with low power ASIC and laser beams", ICHEP2020

| Introduction                                                                                  |                        | International collaboration | Leading institutions |

|-----------------------------------------------------------------------------------------------|------------------------|-----------------------------|----------------------|

| TPC limitations for Z                                                                         | MOST1<br>2016.6-2021.6 | LCTPC, KEK,<br>Saclay       | IHEP, Tsinghua       |

| <ul> <li>Ions back flow in chamber</li> <li>Calibration and alignmensf<sup>C</sup></li> </ul> | NSFC<br>2016.1-2020.12 | LCTPC, KEK,<br>Nikehf       | IHEP, Tsinghua       |

| <ul> <li>Low power consumption For A<br/>chip</li> </ul>                                      | ASIC                   |                             |                      |

IP

Compare with ALICE TPC and CEPC TPC

**Preliminary results**

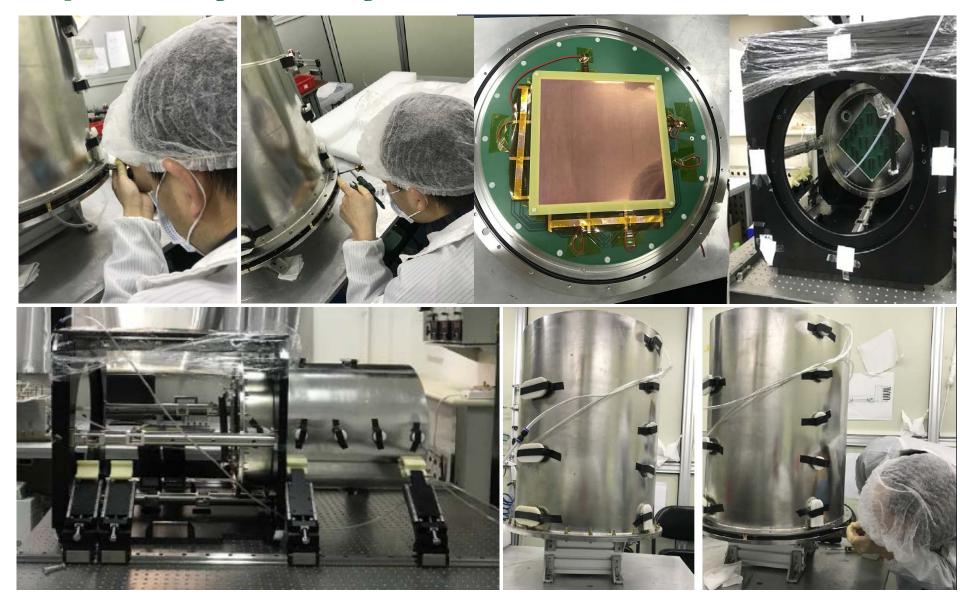

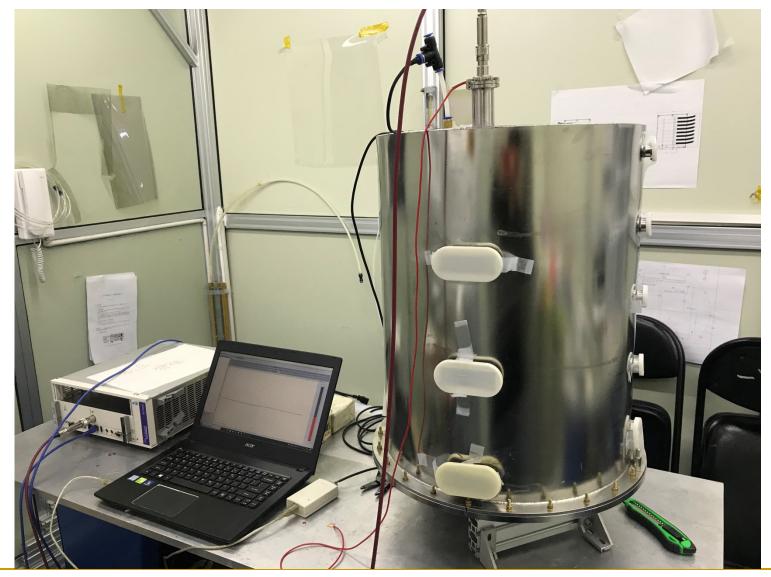

## Status of the prototype

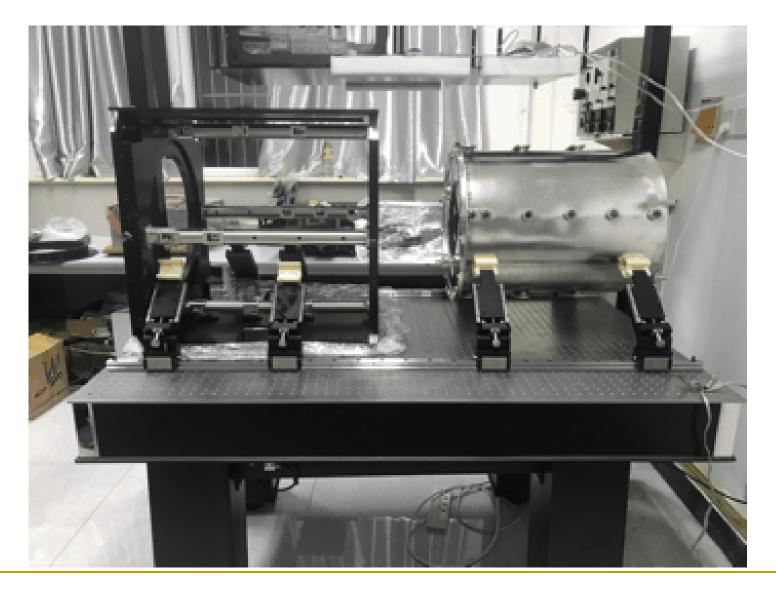

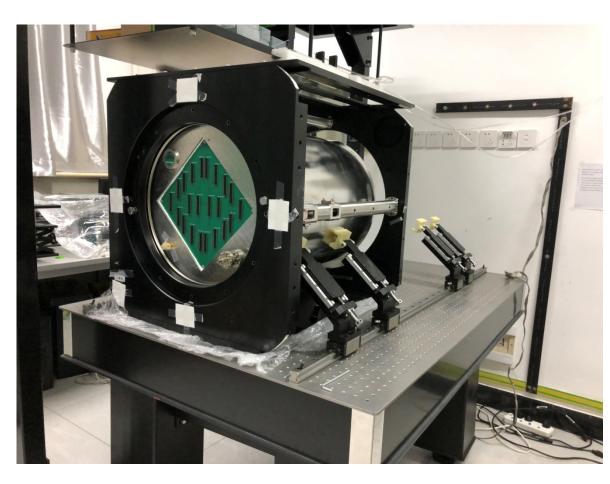

#### Re-assembled TPC prototype in last three months

#### Optimization of gas leak, O ring seal, detector HV connectors and UV beam devices.

#### >15000V high voltage training (Ready)

#### Assembled and removed motion

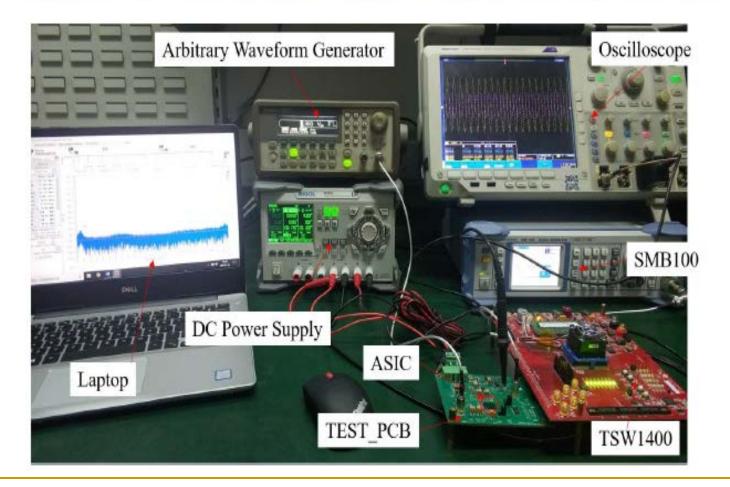

#### TPC prototype and FEE R&D

- Main parameters

- Drift length: ~510mm, Readout active area: 200mm × 200mm

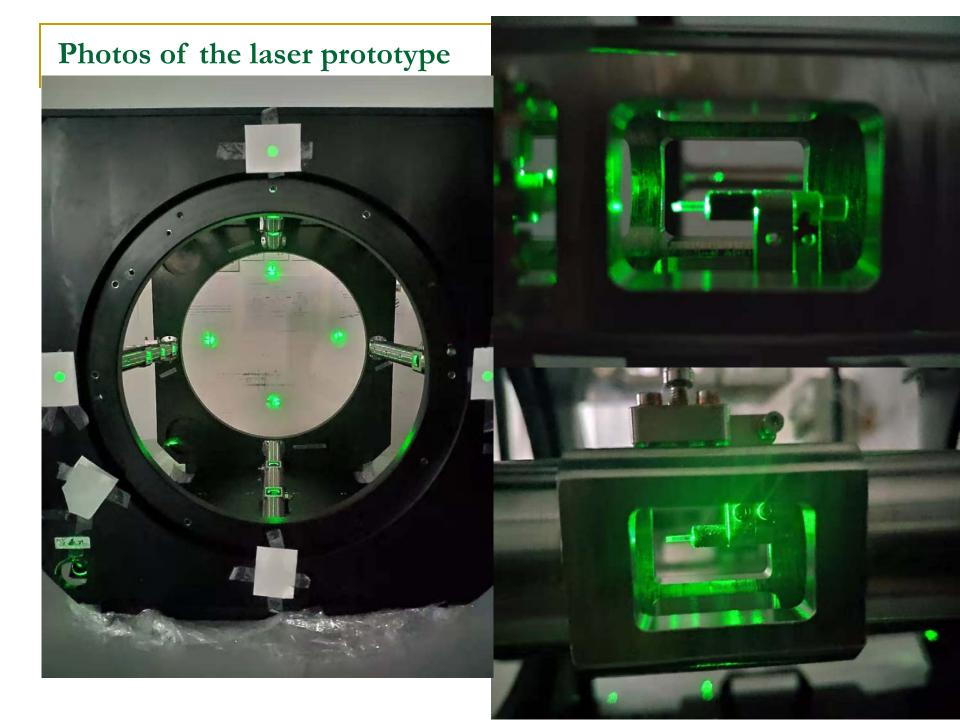

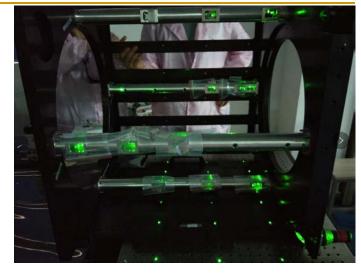

- Integrated the laser calibration with 266nm

- **GEMs/Micromegas as the readout**

- Amplifier (Assembled)

- CASAGEM chip

- 16Chs/chip

- Shape time: 20ns

- DAQ (Assembled)

- FPGA+ADC

- 4 module/mother boar

- 64Chs/module

- Sample: 40MHz

- **1280chs**

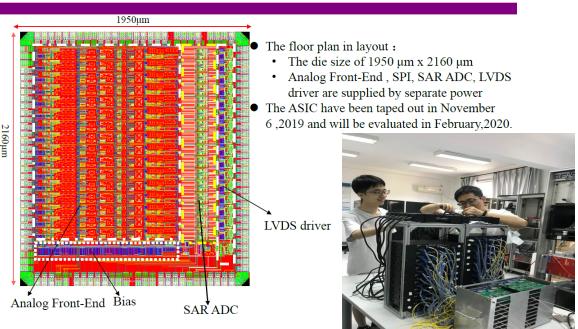

Layout of 16-ch TPC Readout ASIC

Diagram of the TPC prototype with the laser calibration system .9-

#### All prototype in the lab (Ongoing Studies)

#### Manpower

- In last three months, Jian Zhang and Huirong

- Our biweekly meeting has been maintained

- Students will join in this month

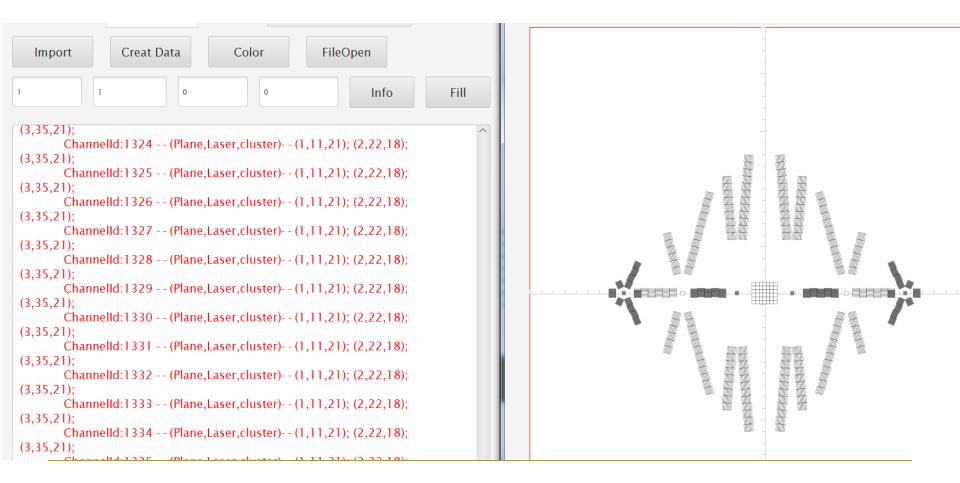

#### Event display interface @V1.7

- Event display software

- Integrated with DAQ software packages

- **Event and some information display interface developed**

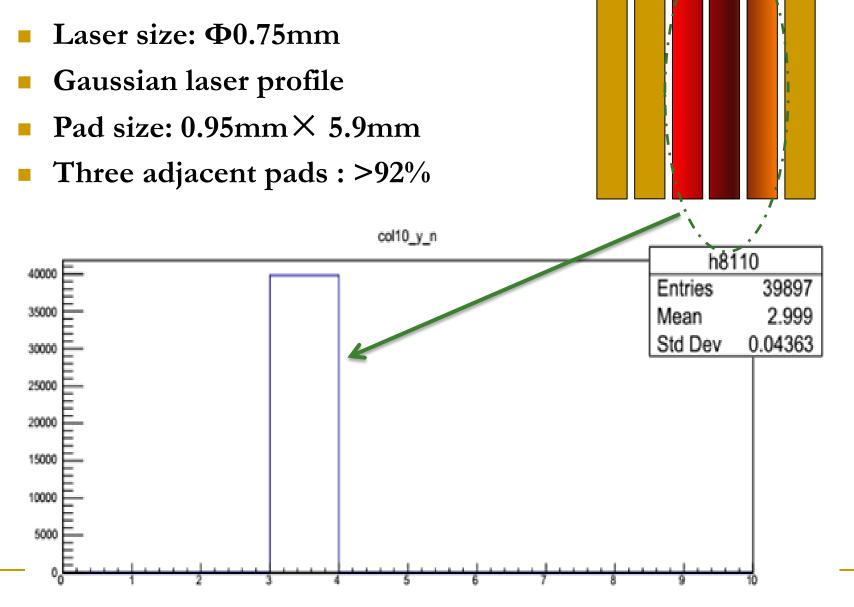

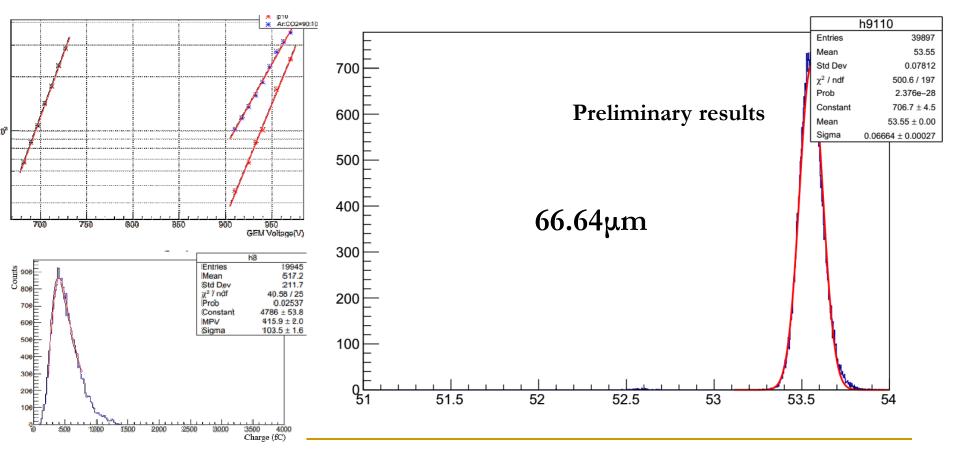

#### Resolution

#### Resolution

- Laser size: Φ0.75mm

- Gaussian laser profile

Gain and energy of 266nm laser

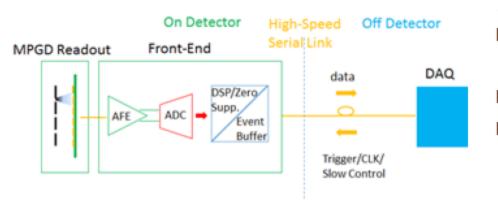

### Status of ASIC R&D

#### ASIC in 65nm CMOS

#### Architecture and Specification

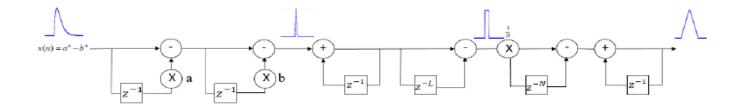

The waveform sampling front end:

- a preamplifier and a shaper as the analog front-end (AFE)

- a waveform sampling ADC

- a dedicated digital signal processing (DSP) and data compression unit for each channel

#### The Key Specifications of the AFE and the ADC

| AFE     | ENC           | 500 e @ 10pF input cap. | Shaper            | CR-RC             |

|---------|---------------|-------------------------|-------------------|-------------------|

|         | Gain          | ~10 mV/fC               | Shaping time      | ~160 ns           |

|         | Crosstalk     | <1%                     |                   |                   |

| ADC     | Sampling rate | ≥20 MSPS                | Resolution        | 10 bit            |

| Process |               | TSM C 65nm LP           | Power consumption | ≤5 mW per channel |

#### ASIC in 65nm CMOS

- Current Progress

- First MPW tape out in 2017, including three prototype chips

- 5-channels analog front end (preamplifier + CR-RC shaper)

- Single channel SAR-ADC

- Single channel full function ASIC (analog front and SAR-ADC)

- 5-channels analog front end, SAR-ADC and full function

- Preliminary testing in Oct.,2019 and re-test in April, 2020

- Second MPW tape out in Nov. 2019

- Second MPW will be tested in Tsinghua University

- Second MPW will used for TPC prototype's testing

#### First MPW ASIC tests

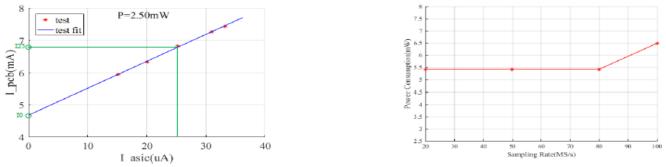

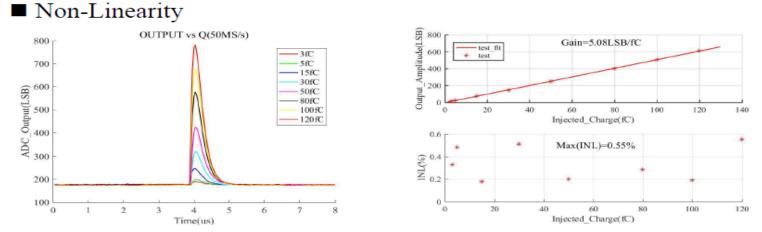

#### Results of power consumption and lineartity

#### Power Consumption

- Adjustable by an external resistor. At normal bias current of 25 μA, the power consumption of AFE part is 2.50 mW/ch

- The power consumption of ADC part is **5.41 mW/ch** at 50MS/s. ADC core circuits consume 1/4 of the total ADC power (**1.35 mW/ch**)

The maximum INL is 0.55% for the dynamic range up to 120 fC (gain = 5.08 LSB/fC)

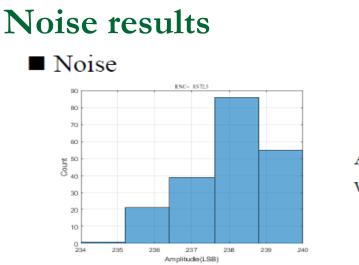

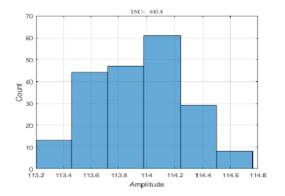

Amplitude distribution of the direct ASIC outputs with 50 fC injected charge: ENC = 1572 e @ 4.3 pF.

Amplitude distribution of the trapezoidal filter outputs implemented in Matlab: ENC = 883 e @ rising time = 1  $\mu$ s and flat top time = 0.2  $\mu$ s

#### Status of the collaboration

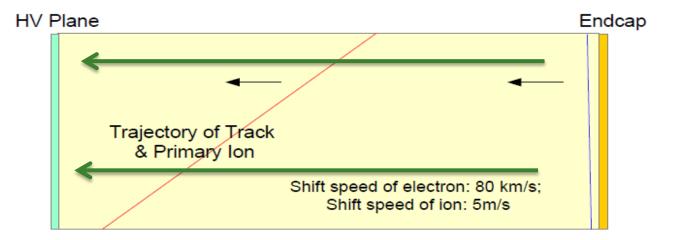

New consideration for lowest IBF at low gain

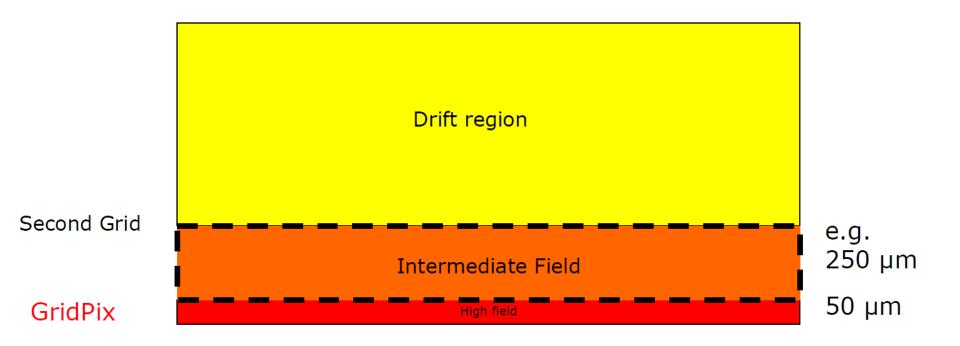

# CEPC Pixel TPC with double meshes

- Question: can one reduce the Ion Back Flow of a GridPix detector?

- IHEP and Nikehf

- Too design a GridPix detector using a double grid

- The idea is that by creating two field regions, one with a medium field and one with a high field (Standard Grid Pix) one could reduce the ion backflow in two stages.

- The high field avalanche region has a measured IBF of 1.3%

- The aim is to reduce the IBF by another factor 100

- The second Grid replaces the Gating device and is always operational

Concept of the double meshes

#### CEPC Pixel TPC with double meshes

#### Concept

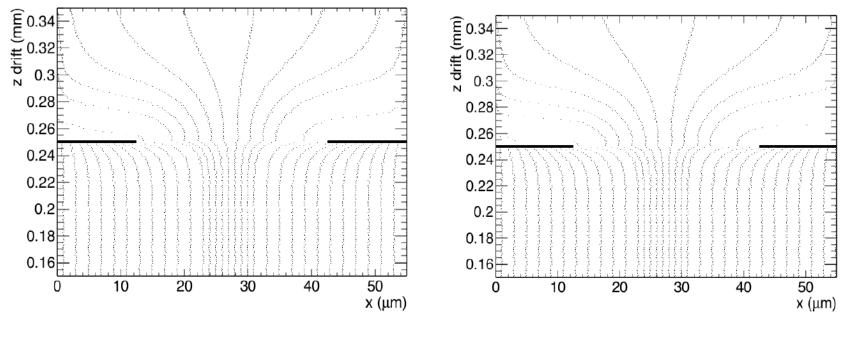

#### Simulation of backflow trajectories second Grid

Field ratio 40

Field ratio 240

Field ratio =  $E_2/E_1$

#### Ion backflow for a double grid

Calculations for the IBF of the two meshes in case one has a total FR240 – normal GridPix operation. The lower Grid(Pix) was at FR16 too.

| lon backflow             | Hole 30 µm          | Hole 25 µm         | Hole 20 µm         |

|--------------------------|---------------------|--------------------|--------------------|

| Top grid                 | 2.2%                | 1.2%               | 0.7%               |

| GridPix                  | 5.5%                | 2.8%               | 1.7%               |

| Total (IBF)              | 12×10 <sup>-4</sup> | 3×10 <sup>-4</sup> | 1×10 <sup>-4</sup> |

| Electron<br>transparency | 100%                | 99.4%              | 91.7%              |

- In order to reach IBF×Gain (Gain 10<sup>3</sup>) below one has to choose a slightly

- Smaller hole size of 25 or 20 microns. (460LPI- 510LPI)

- The new meshes delivered to Nikehf and tests will be collaborated.

#### Summary

- All of contents will be reported: "Development of IBF suppression TPC integrated with low power ASIC and laser beams", ICHEP2020

- Some update progress of the TPC prototype R&D in last three months.

- Some update progress of the TPC ASIC chips R&D and the results of the power consumption and noise.

- Some update collaboration of the new concept R&D with Nikehf.

Thanks!