#### **Digital Pixel Measurement** of TaichuPix1

Tianya Wu **CEPC MOST2 Meeting** twu@ifae.es 17-08-2020

CENTRAL CHINA NORMAL UNIVERSITY

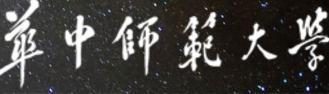

◆The left figure shows the ALPIDE like scheme and the right are the FE\_I3 like one.

◆ With the default state of the analog front end, PIX\_INB="1", then DPLSE="1",

→When MASK\_EN="1", ALPIDE like part will be shielded; FE-I3 like part is working fine.

→ When MASK\_EN="0", FE-I3 like part will be shielded; ALPIDE like part is working fine.

No matter what the status of MASK\_EN, half part of the pixel array should be working with DPLSE.

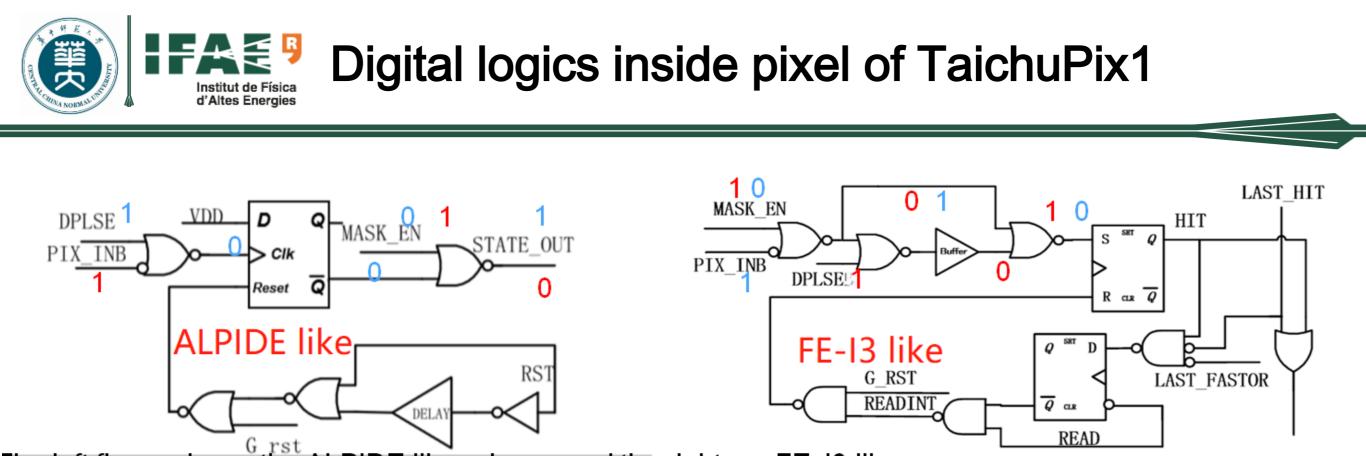

#### Testing results of masking digital pixels d'Altes Energies

◆40MHz chip system CLK, 10MHz SPI speed, with digital pulse injection. →MASK\_EN="1", spi\_write('00110','0000000');MASK\_EN="0",spi\_write('00110','0111111');

Institut de Física

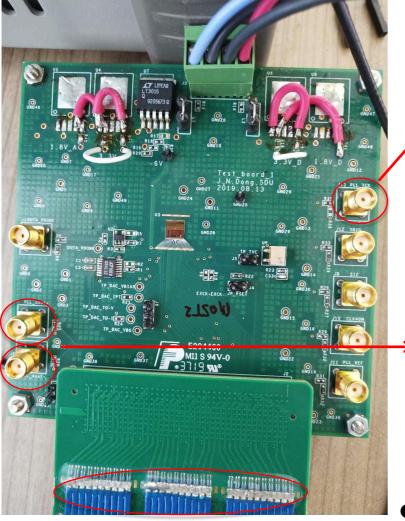

### PLL & Serializer preliminary test results

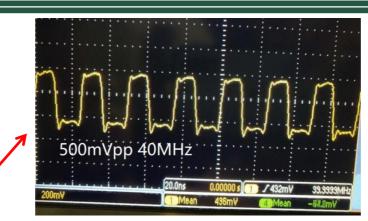

- With the 40MHz Reference Clock, the PLL will generate a 40MHz and 500mVpp signal at the PIN of TCK.

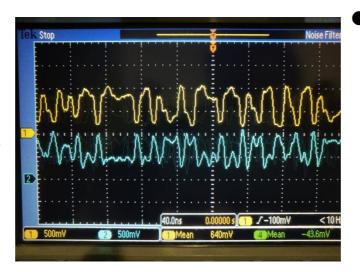

- The Oscilloscope could receive the differential signal but hard to recognize the digital sequences information.

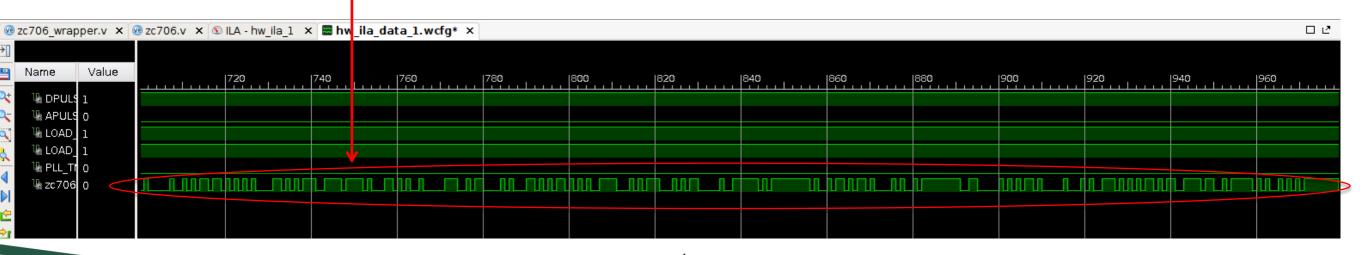

Use the FPGA hardware debug core to check the data. It could show the digital sequences, but the frame header is hard to recognize.

## PLL & Serializer preliminary test results

The last line is the serial to parallel conversion output, this is the result of DSEL=1, data is from the internal generator, but it mismatch the PRBS-2^7 pattern? And the time period of each data is different.

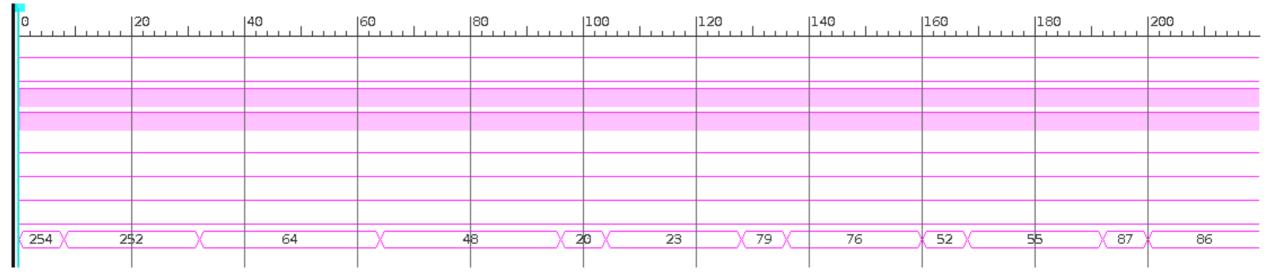

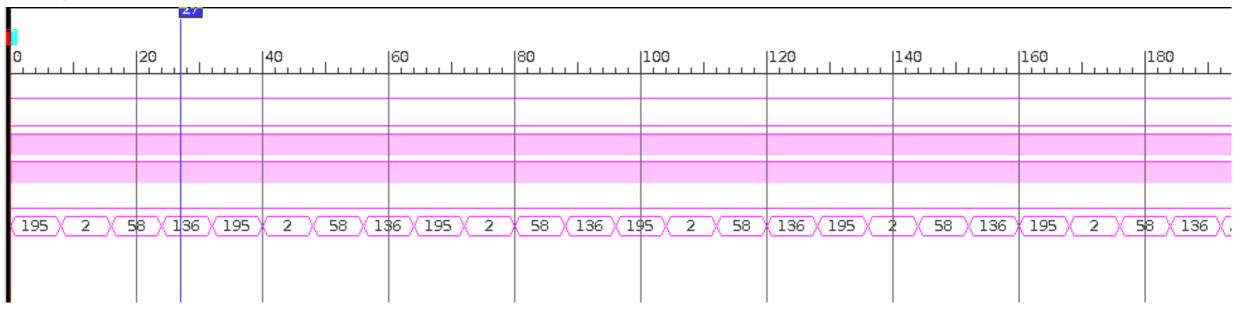

This is the result of DSEL=0, data is from the periphery, the time period of each data is the same, but the repeat result (136-195-2-58) not so sure where is the header of byte ?

- The principle of digital logics shows the pixel array will be response with digital pulse injection no matter the masking state.

- It proves the function of masking signal is working fine.

- Even all the pixels are shielded by the masking blocks, the noisy signal will still come from the COL95\_ROW0 and COL63\_ROW0.

- The strategy to test serializer blocks will need to be optimize.

- → Next step is to improve the firmware on deserializing the LVDS signal.

- → Do final test together with the analog front end

# Thanks for your attention.