#### **TaichuPix1 Measurement**

Tianya Wu CEPC MOST2 Meeting twu@ifae.es 02-11-2020

CENTRAL CHINA NORMAL UNIVERSITY

### Preliminary test results(Analog Front End)

Fig 4

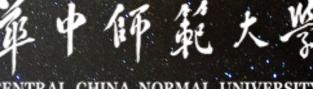

Here are schematic of Analog front end with the design parameters and the waveform result from Ying Zhang.

Institut de Física d'Altes Energies

> There will be a 400mV pulse generated at the rising edge of the Apulse.

> OUTA should be response at the rising edge

The DC bias of OUTA is around 800mV

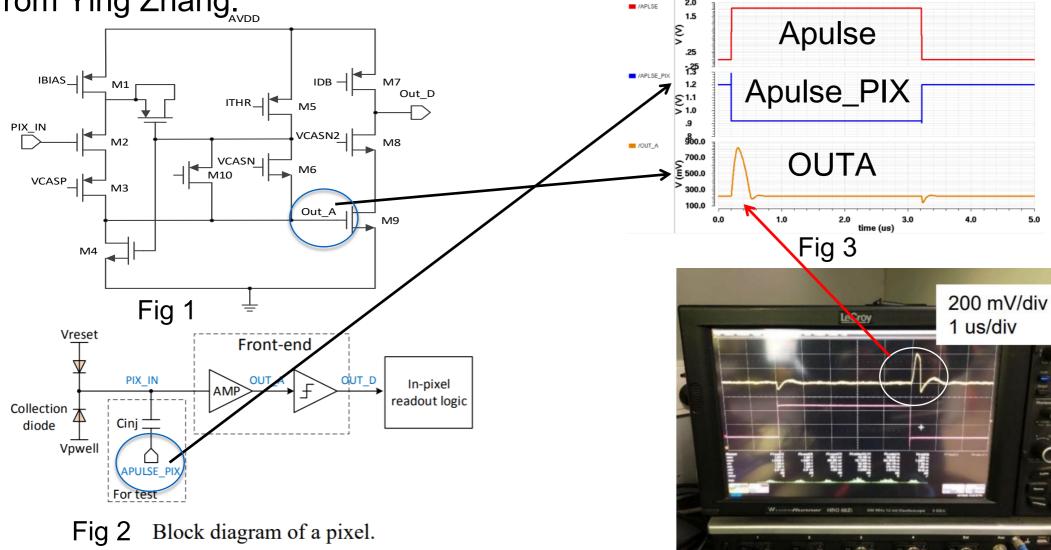

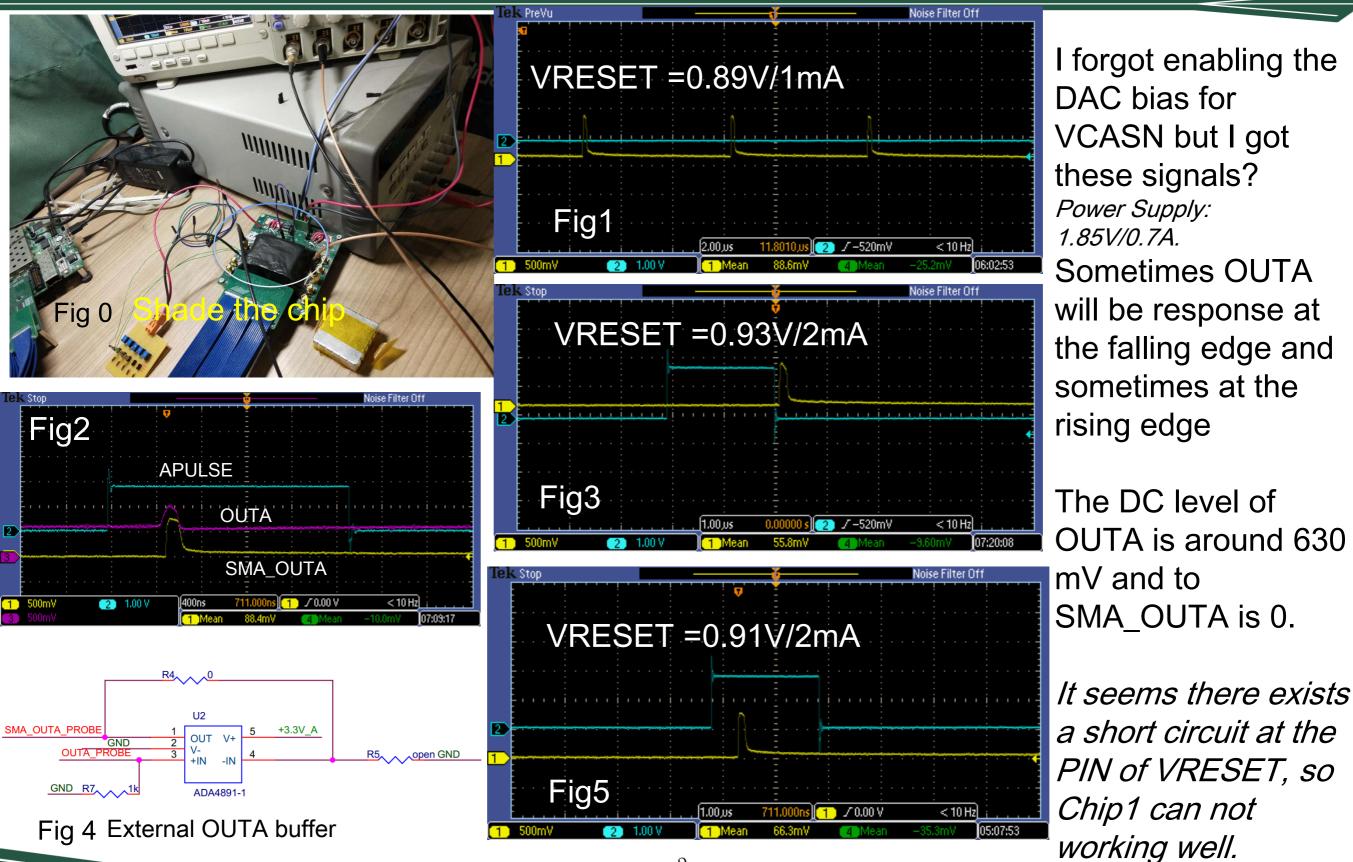

|         | Bias             | IBIAS  | ITHR   | IDB  | VCLIP   | VCASP | VCASN  | VCASN2        | VRESET |

|---------|------------------|--------|--------|------|---------|-------|--------|---------------|--------|

| Table 1 | Design<br>value  | 440 nA | 4.5 nA | 1 µA | 0/0.2 V | 0.6 V | 0.55 V | 0.5 V         | 1.4 V  |

| Chip1   | Config.<br>value | 450nA  | 1.16nA | 1uA  | 0.068V  | 0.6V  | 0.073V | <b>?</b> 0.5V | 0.93V  |

|         | 9                |        |        |      |         |       |        |               |        |

#### Preliminary test results(Analog Front End)

3

#### Preliminary test results(Analog Front End)

Chip2 performance is the same as what I expect, and consistent with Ying as well.

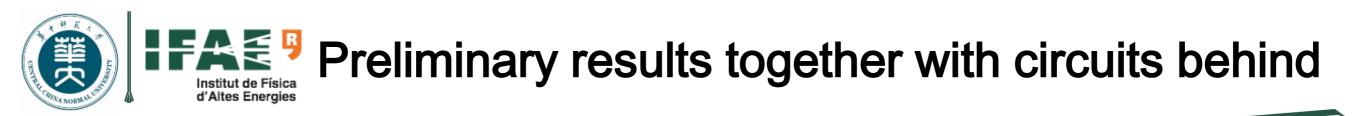

Fig 1 Readout flow diagram for one pixel

- Following the DACs configuration parameters as the previous slide.

- Give a pulse as the injection to the test capacitor inside analog front end.

- Turn on the in-pixel readout logic , periphery and PLL blocks.

- Readout the data from the LVDS output interface.

## Preliminary results together with circuits behind

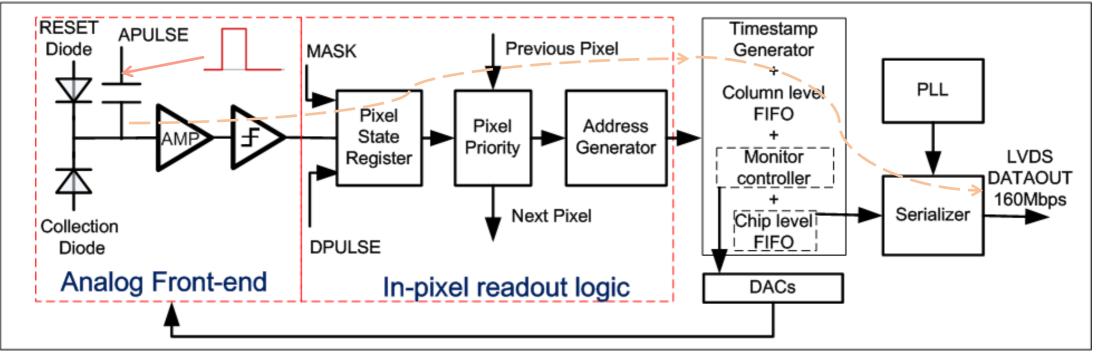

- The Chip2 is working at 1.85V/0.716A.

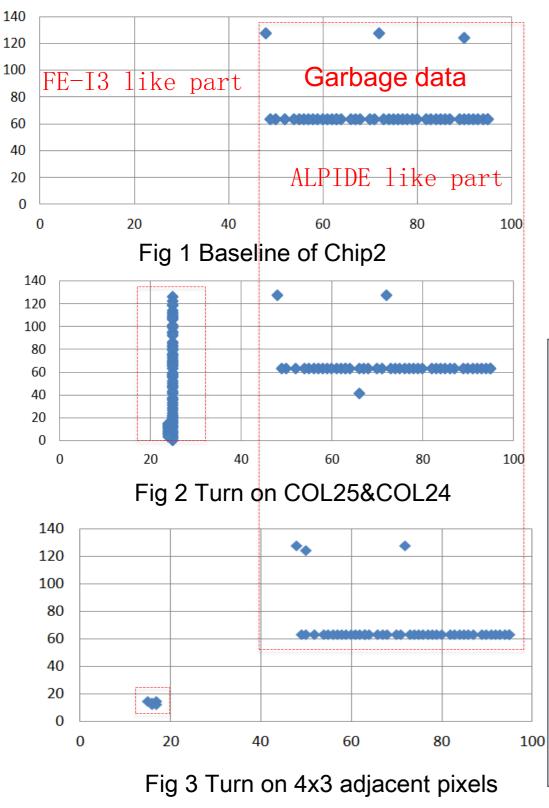

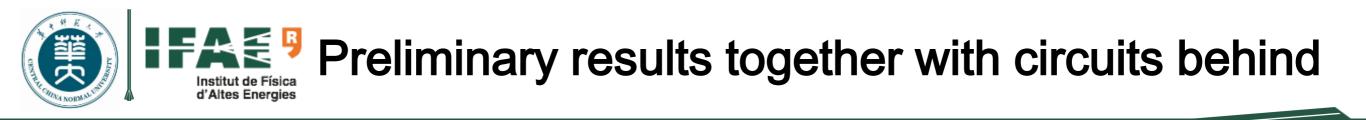

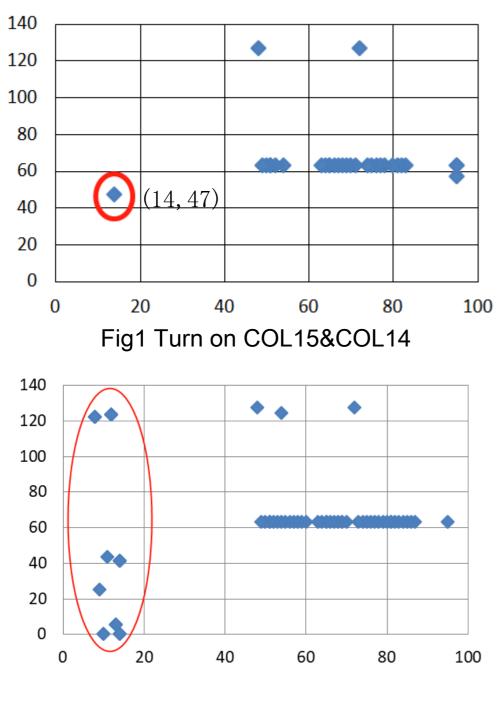

- Fig1 is the original state of the chip without any injection. The ALPIDE like part has hot pixels due to the power.(2V is better).

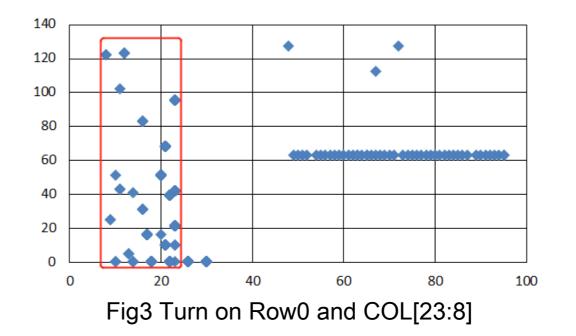

- Fig2 and Fig3 show the FE-I3 like part performance. Only part of data were read out. (I guess it is the power reason)

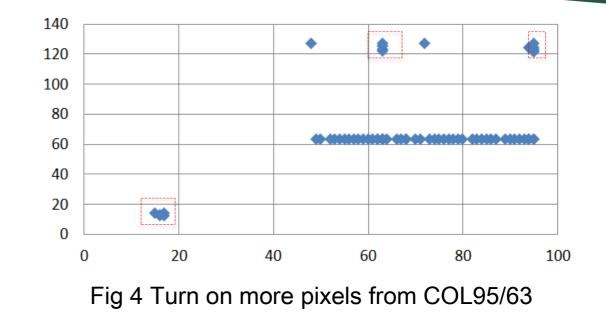

- Fig4 shows the COL95&COL63 is working fine.

→From the preliminary test, digital readout part is not working at the best state with 1.85V power supply.

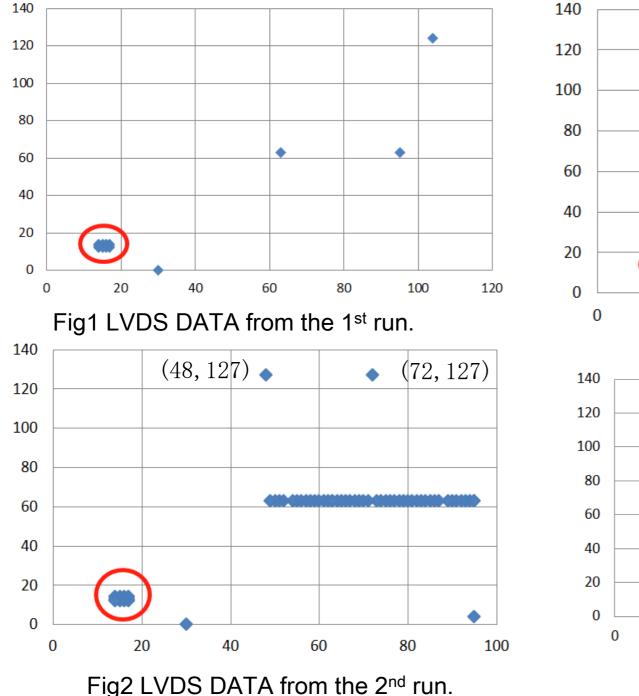

- Set up the Chip with 1.9V/0.76A and VRESET of 1.76V with shading.

- Turn on (COL30, ROW0) to observe analog OUTA signal

- Open a specific region and do APULSE injection.(COL17/16/15/14,ROW14/13/12 ) and fire COL15/14

Comparing with1.85V power supply, 1.9V is more reliable.

Here is no valid data loss.

It meets what we expect, when there are too many pixels, may throw away some blocked data.

VDD 1.9V and VRESET 1.76V are good operating point for my Chip2.

#### Further test with full chip

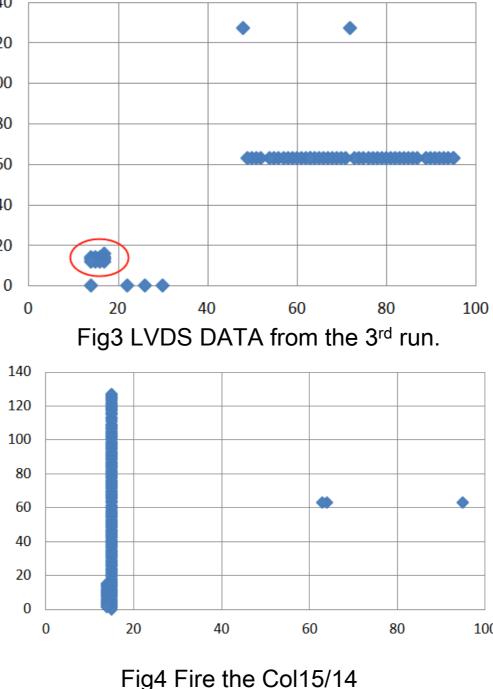

- Set up the Chip with 1.9V/0.76A and VRESET of 1.78V without shading.

- Expose the chip to mouse infrared or cell phone flashlight.

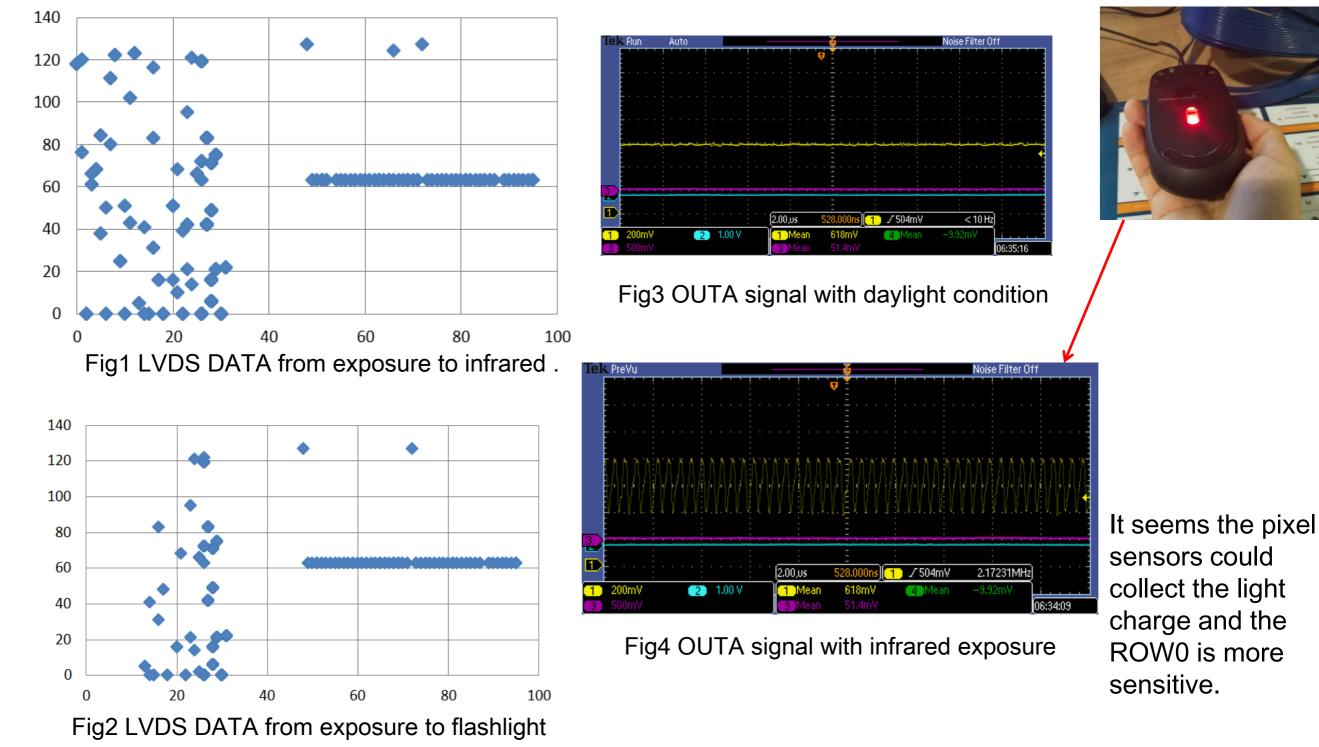

- Set up the Chip with 1.9V/0.76A and VRESET of 1.78V without shading.

- Expose the chip to mouse infrared.

- There are many positions with multiple hits, this is not the real hit map.

- It seems around 1 infrared hit per double column.

- It proves the function of MASKING PIXELS is working fine.

- The ROW0 is the bound to digital periphery, and it is more sensitive.

- The function of COL31~COL0 satisfies the design requirement.

Fig2 Turn on COL15/14/13/12/11/10/9/8

- Analog front end of Chip2 is working properly.

- Analog front end of Chip1 is not so good, and the circuits behind can not detect the signal correctly, because the low VRESET make the pixels more sensitive.

- The FE-I3 like section (COL0~COL31) is working fine at the power supply of 1.9V/0.76A;

- ◆ ALPIDE like part could perform at the COL95 and COL63.

- $\rightarrow$ Then I will try to do more test and draw the real hit map.

- $\rightarrow$  Start to organize the preliminary results into a paper.

# Thanks for your attention.

11