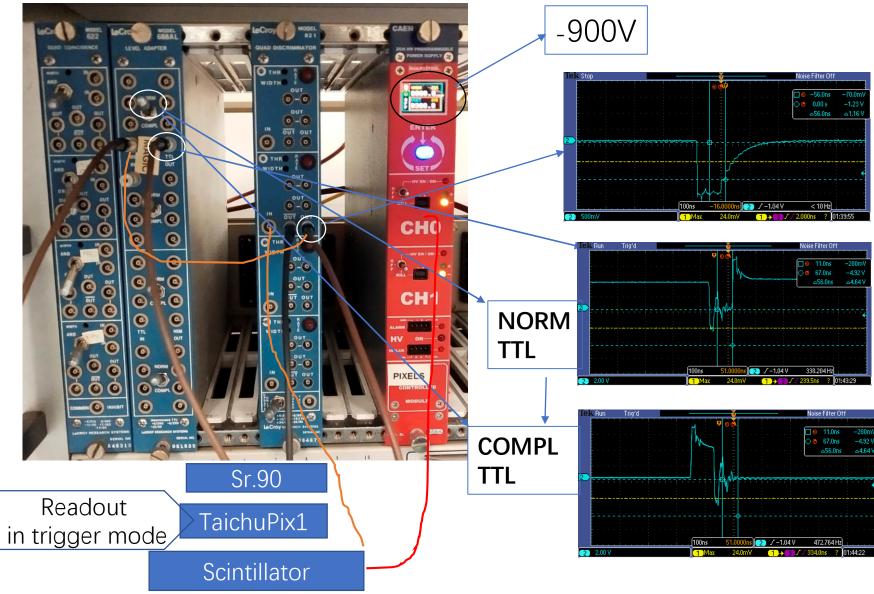

#### **Scintillator Setup**

Tianya Wu CEPC Meeting twu@ifae.es 19-04-2021

# Scintillator setting

- High Voltage source set to -900V ٠

- Negative OUTD signal of 100 ns pulse with -1.5 V

- NIM to TTL, set to the COMPL • to obtain the positive TTL

4.64

The Lemo to BNC connector has a big signal ringing due to the impedance matching. With the oscilloscope probe seems better.

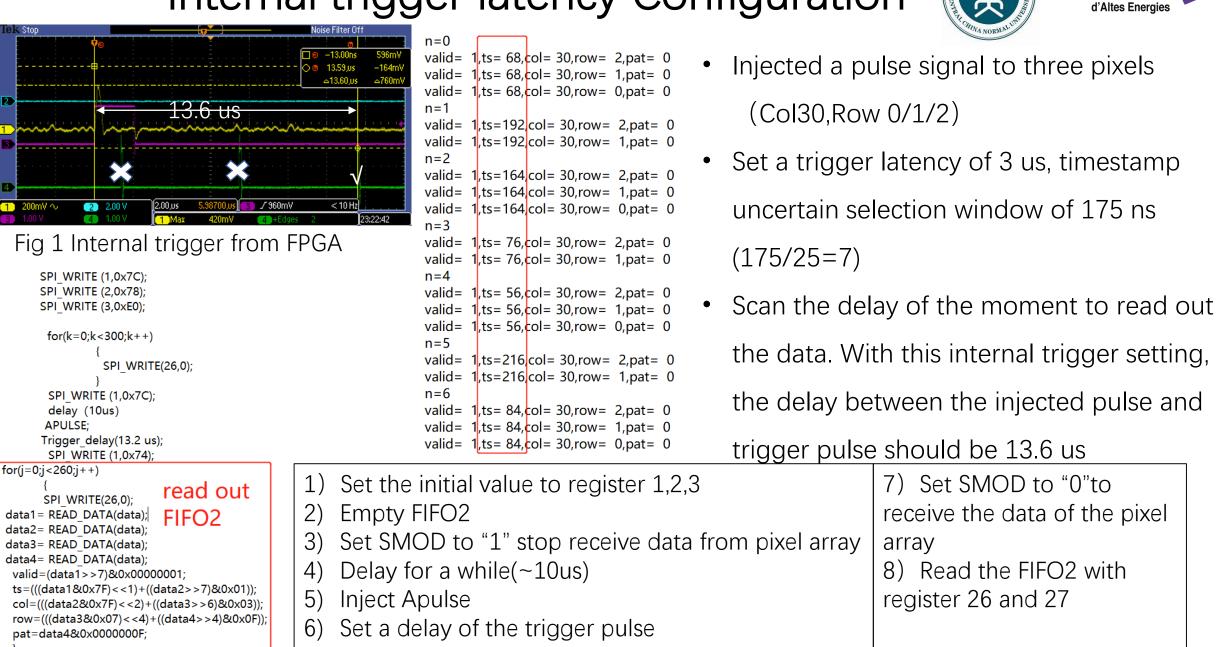

## Internal trigger latency Configuration

EXCELENCIA SEVERO OCHOA

Institut de Física

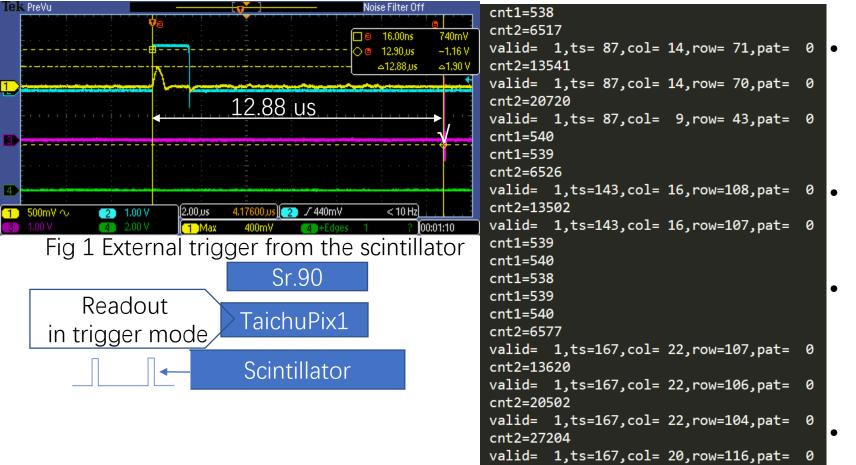

# External trigger latency Configuration

- Scintillator pulse is connected to the FPGA as a trigger to the system readout

- The Chip is placed in the middle between the Sr.90 and scintillator

- Calibrate the latency with the

- APULSE, an APULSE is generated as

- soon as the FPGA received a trigger

- Remove the APULSE ,then readout

data with the Sr.90 injection.

- 1) The trigger will reset a 32bits counter inside FPGA, the counter is running at 20MHz

- 2) cnt1 is the 540( 540x50ns = 27 us) when the FIFO2 starts to readout, and cnt2 is the moment when the data is read out.

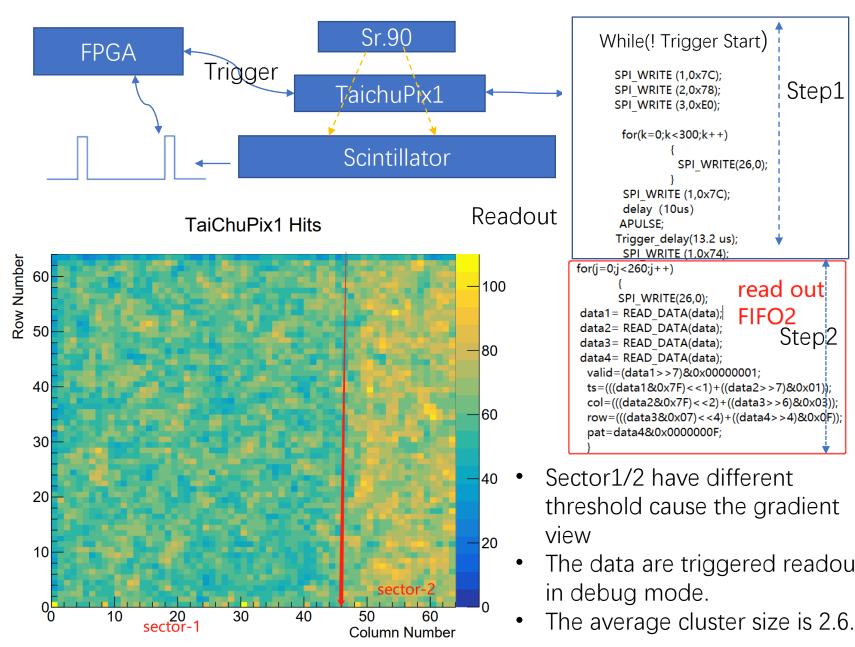

## Hit map and cluster with external trigger

|                                                                                                                                                                 | Jyei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ENTRAL CRIMA                                                                                                                                                                                                                                                              | NORMALONU                                                                                                  | Institut o<br>d'Altes I                                                                                                                                                                                          | de Física<br>Energies           | BIST S                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------|

| SPI_WRITE (3,0xE0);<br>for(k=0;k<300;k++)<br>{                                                                                                                  | cep1 valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | l=1, ts=53,                                                                                                                                                                                                                                                               | col=26,<br>col=25,<br>col=25,<br>col=28,<br>col=28,<br>col=28,<br>col=28,<br>col=10,<br>col=10,<br>col=21, | row=27, pat=0<br>row=27, pat=0<br>row=26, pat=0<br>row=25, pat=0<br>row=32, pat=0<br>row=31, pat=0<br>row=30, pat=0<br>row=117, pat=0<br>row=114, pat=0<br>row=99, pat=0                                         | 4<br>3<br>2<br>1                |                               |

| 4= READ_DATA(data);                                                                                                                                             | ut<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>valid<br>vav | I=1, ts=125,   I=1, ts=101,   I=1, ts=93,   I=1, ts=93, | col=1,<br>col=9,<br>col=7,<br>col=7,<br>col=6,<br>col=30,<br>col=30,<br>col=19,<br>col=11,<br>col=11,      | row=126, pat=0<br>row=57, pat=0<br>row=56, pat=0<br>row=108, pat=0<br>row=96, pat=0<br>row=109, pat=0<br>row=19, pat=0<br>row=16, pat=0<br>row=56, pat=0<br>row=55, pat=0<br>row=54, pat=0<br>uster Distribution | 2<br>1<br>2<br>2<br>2<br>2<br>2 |                               |

| d=(data1>>7)&0x00000001;<br>(((data1&0x7F)<<1)+((data2>>7)&0;<br>=(((data2&0x7F)<<2)+((data3>>6)&0;<br>=(((data3&0x07)<<4)+((data4>>4)&0;<br>=data4&0x0000000F; | 0x03));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                           |                                                                                                            |                                                                                                                                                                                                                  | Me                              | his<br>htries<br>ean<br>d Dev |

| r1/2 have different<br>hold cause the gradi                                                                                                                     | 2000<br>ient <sup>1500</sup><br>1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                           |                                                                                                            |                                                                                                                                                                                                                  |                                 |                               |

| ata are triggered re<br>bug mode.                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                           | <br>6                                                                                                      | 8 10 12                                                                                                                                                                                                          | <u> </u>                        | 16<br>16                      |

EXCELENCIA SEVERO OCHOA

hist

97584

2.627

18

**Cluster Size**

ona Institute of and Technolog

## Data acquisition from LVDS interface

#### Data acquisition from LVDS interface

#### DOFREQ =00, 2MHz

| valid= 1,ts | =210,col= 27,row= 94,pat= 0 |

|-------------|-----------------------------|

| valid= 1,ts | =210,col= 27,row= 94,pat= 0 |

| valid= 1,ts | =210,col= 27,row= 94,pat= 0 |

| valid= 1,ts | =230,col= 19,row= 51,pat= 0 |

| valid= 1,ts | =230,col= 19,row= 51,pat= 0 |

| valid= 1,ts | =230,col= 19,row= 51,pat= 0 |

| valid= 1,ts | =230,col= 19,row= 48,pat= 0 |

| valid= 1,ts | =230,col= 19,row= 48,pat= 0 |

| valid= 1,ts | =230,col= 19,row= 48,pat= 0 |

| valid= 1,ts | =230,col= 18,row= 50,pat= 0 |

| valid= 1,ts | =230,col= 18,row= 50,pat= 0 |

| valid= 1,ts | =230,col= 18,row= 50,pat= 0 |

| valid= 1,ts | =230,col= 18,row= 49,pat= 0 |

| valid= 1,ts | =230,col= 18,row= 49,pat= 0 |

| valid= 1,ts | =230,col= 18,row= 49,pat= 0 |

| valid= 1,ts | = 50,col= 13,row= 43,pat= 0 |

| valid= 1,ts | = 50,col= 13,row= 43,pat= 0 |

| valid= 1,ts | = 50,col= 13,row= 42,pat= 0 |

| valid= 1,ts | = 50,col= 13,row= 42,pat= 0 |

| valid= 1,ts | = 98,col= 28,row= 82,pat= 0 |

| valid= 1,ts | = 98,col= 28,row= 82,pat= 0 |

| valid= 1,ts | = 98,col= 28,row= 82,pat= 0 |

|             | = 22,col= 31,row= 74,pat= 0 |

| valid= 1,ts | = 22,col= 31,row= 74,pat= 0 |

| valid= 1,ts | = 22,col= 31,row= 74,pat= 0 |

#### DOFREQ =01, 5MHz

valid= 1,ts=225,col= 28,row= 84,pat= 0 valid= 1,ts=193,col= 28,row= 84,pat= 0 valid= 1,ts=129,col= 28,row= 84,pat= 0 valid= 1,ts= 97,col= 28,row= 84,pat= 0 valid= 1,ts= 1,col= 28,row= 84,pat= 0 valid= 1,ts=225,col= 28,row= 12,pat= 0 valid= 1,ts= 70,col= 31,row= 20,pat= 0 valid= 1,ts= 70,col= 31,row= 18,pat= 0 valid= 1,ts= 70,col= 22,row=121,pat= 0 valid= 1,ts= 70,col= 22,row=118,pat= 0 valid= 1,ts= 70,col= 13,row= 33,pat= 0 valid= 1,ts= 70,col= 13,row= 30,pat= 0 valid = 1,ts = 70,col = 2,row = 71,pat = 0valid= 1,ts= 10,col= 27,row= 56,pat= 0 valid= 1,ts= 10,col= 27,row= 55,pat= 0 valid= 1,ts=182,col= 31,row= 40,pat= 0 valid= 1,ts=182,col= 31,row= 39,pat= 0 valid= 1,ts=182,col= 30,row= 41,pat= 0 valid= 1,ts=182,col= 30,row= 38,pat= 0 valid= 1,ts=182,col= 22,row= 99,pat= 0 valid= 1,ts=182,col= 22,row= 96,pat= 0 valid= 1,ts=182,col= 22,row= 95,pat= 0 valid= 1,ts=182,col= 21,row= 98,pat= 0 valid= 1,ts=182,col= 21,row= 97,pat= 0 valid= 1,ts=182,col= 21,row= 94,pat= 0

#### DOFREQ = 10, 10MHz

valid= 1,ts=162,col= 12,row=123,pat= 0 valid= 1,ts=162,col= 12,row=122,pat= 0 valid= 1,ts=162,col= 12,row=120,pat= 0 valid= 1,ts=162,col= 11,row=122,pat= 0 valid= 1,ts=162,col= 11,row=121,pat= 0 valid = 1,ts=162,col=1,row=64,pat=0valid= 1,ts=162,col= 0,row= 65,pat= 0 valid= 1,ts=162,col= 0,row= 64,pat= 0 valid= 1,ts= 74,col= 29,row= 0,pat= 0 valid = 1, ts = 74, col = 28, row = 2, pat = 0valid= 1,ts= 74,col= 26,row= 35,pat= 0 valid= 1,ts= 74,col= 26,row= 34,pat= 0 valid= 1,ts= 74,col= 26,row= 33,pat= 0 valid= 1,ts= 74,col= 9,row= 98,pat= 0 valid = 1,ts = 74,col = 9,row = 97,pat = 0valid = 1,ts = 74,col = 9,row = 96,pat = 0valid= 1,ts= 74,col= 7,row= 91,pat= 0 valid = 1,ts = 74,col = 6,row = 90,pat = 0valid = 1,ts = 74,col = 4,row = 21,pat = 0valid= 1,ts= 74,col= 4,row= 20,pat= 0 valid= 1,ts=146,col= 21,row= 6,pat= 0valid= 1,ts= 18,col= 30,row=107,pat= 0 valid= 1,ts= 18,col= 10,row=125,pat= 0 valid= 1,ts= 18,col= 10,row=124,pat= 0 valid= 1,ts= 18,col= 10,row=123,pat= 0 valid= 1,ts= 18,col= 10,row= 64,pat= 0 valid= 1,ts= 18,col= 9,row= 65,pat= 0

#### DOFREQ =11, 20MHz

valid= 1,ts= 94,col= 28,row=121,pat= 0 valid= 1,ts= 94,col= 22,row= 27,pat= 0 valid= 1,ts= 94,col= 21,row=124,pat= 0 valid= 1,ts= 94,col= 16,row= 84,pat= 0 valid= 1,ts= 94,col= 16,row= 80,pat= 0 valid = 1,ts = 94,col = 2,row = 38,pat = 0valid= 1,ts=238,col= 24,row= 35,pat= 0 valid= 1,ts=238,col= 24,row= 89,pat= 0 valid= 1,ts=238,col= 16,row=122,pat= 0 valid= 1,ts=238,col= 10,row= 12,pat= 0 valid= 1,ts=238,col= 9,row= 92,pat= 0 valid= 1,ts=238,col= 8,row= 94,pat= 0 valid= 1,ts=238,col= 4,row= 17,pat= 0 valid= 1,ts=206,col= 30,row= 94,pat= 0 valid= 1,ts=206,col= 30,row= 92,pat= 0 valid= 1,ts=206,col= 29,row= 48,pat= 0 valid= 1,ts=206,col= 29,row= 46,pat= 0 valid= 1,ts=206,col= 28,row= 50,pat= 0 valid= 1,ts=206,col= 28,row= 48,pat= 0 valid= 1,ts=206,col= 31,row= 61,pat= 0 valid = 1,ts=206,col= 9,row= 4,pat= 0 valid= 1,ts=206,col= 2,row=118,pat= 0 valid= 1,ts=206,col= 2,row=116,pat= 0 valid= 1,ts=206,col= 1,row=119,pat= 0 valid = 1,ts=206,col=0,row=5,pat=0

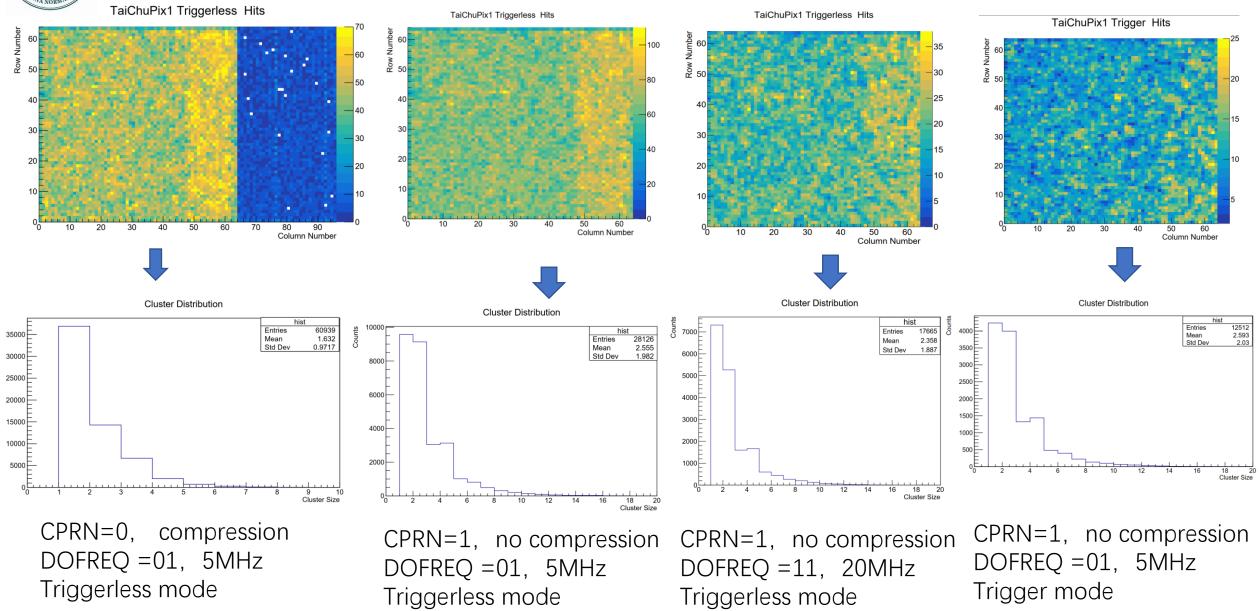

- With the LVDS interface set to 160 MHz, when the data speed set to 2 MHz, every pixel will be read out 3 times.

- Since the matched speed of the interface is 5MHz\*32bits=160Mbps, there are no obvious errors when the DOFREQ is set with 10MHz or 20MHz, but it may affect the cluster size distribution.