ARCADIA Status Report

CEPC Day June 25<sup>th</sup>, 2021

Istituto Nazionale di Fisica Nucleare

Manuel Da Rocha Rolo (INFN) on behalf of the ARCADIA Collaboration

# ARCADIA: CMOS DMAPS platform at INFN

**What do we want**: to develop a design and fabrication platform for large-area fully-depleted CMOS sensors, at the moment targeting space, medical and future HEP infrastructures (thin sensors) and X-ray detectors (thicker sensors)

#### What do we need from the silicon foundry:

- access to an engineered CMOS process (developed in collaboration with LFoundry) and custom starting substrates

- access to future SPW runs for dedicated reticle size (next 3 years) and larger-than-reticle (from 2023) designs

#### Medical

- Low power ( $\leq 40 \text{ mW/cm}^2$ )

- Medium rate  $\approx$  10 MHz 100 MHz/cm<sup>2</sup>

- Ultra low material budget (low energy)

- Very large area (≥ 16 cm<sup>2</sup>)

- 3-side buttable design

- Low to medium rad-tolerance  $\approx$  10 kGy

#### e⁺e⁻

- Low power ( $\leq 40 \text{ mW/cm}^2$ )

- Medium rate ≈ <u>10 MHz 100 MHz / cm²</u>

- Very low material budget

- Large area (≥ 6 cm<sup>2</sup>)

- 3-side buttable design

- Low to medium rad-tolerance  $\approx$  10 kGy

#### Space

- <u>Ultra low power (≤ 10 mW/cm²)</u>

- Very low rate ≈ kHz/cm<sup>2</sup>

- Low material budget

- Large area (≥ 6 cm<sup>2</sup>)

- 3-side buttable

- Low rad-tolerance ≈ 1 kGy

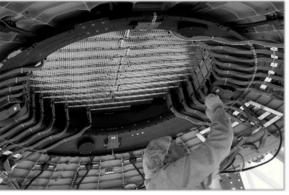

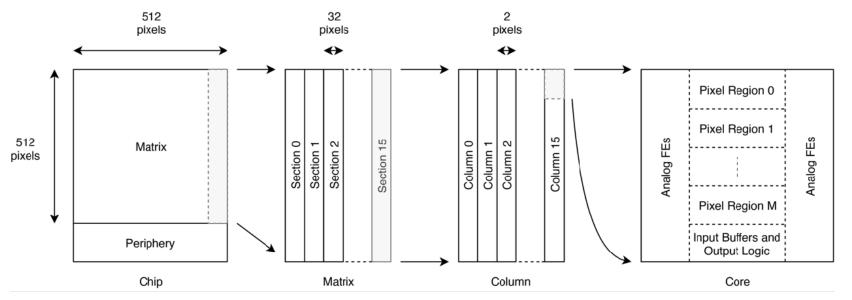

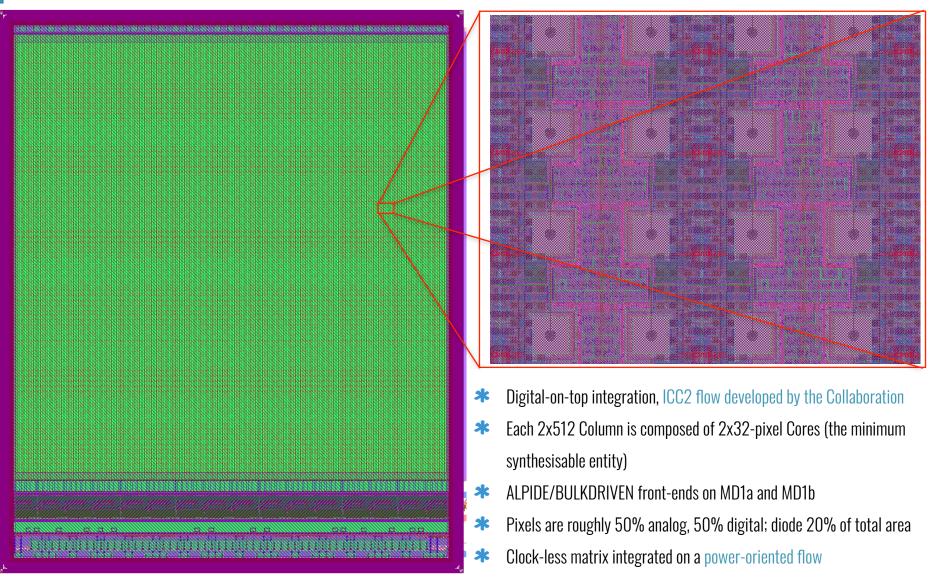

## **ARCADIA-MD1: Main Demonstrator Chip**

- Pixel size 25 µm x 25 µm: process, back-side pattern and geometry validated in silicon (both MATISSE and pseudo-matrices, electrical, laser, radioactive source and microbeam).

- Matrix core 512 x 512, "side-abuttable" to accomodate a 1024 x 512 silicon active area (2.56 x 1.28 cm<sup>2</sup>). Matrix and EoC architecture, data links and payload ID: scalable to 2048 x 2048\*

- Triggerless binary data readout, event rate up to 100 MHz/cm<sup>2</sup>

- First Engineering Run (SPW) with ARCADIA-MD1 by 11/2020, 2<sup>nd</sup> full CMOS maskset mid-2021 (higher data throughput, SEU protection, on-chip data compression), 3<sup>rd</sup> SPW mid-2022 with design fixes, explorative sensor and CMOS designs

### **ARCADIA - Main Demonstrator Chip**

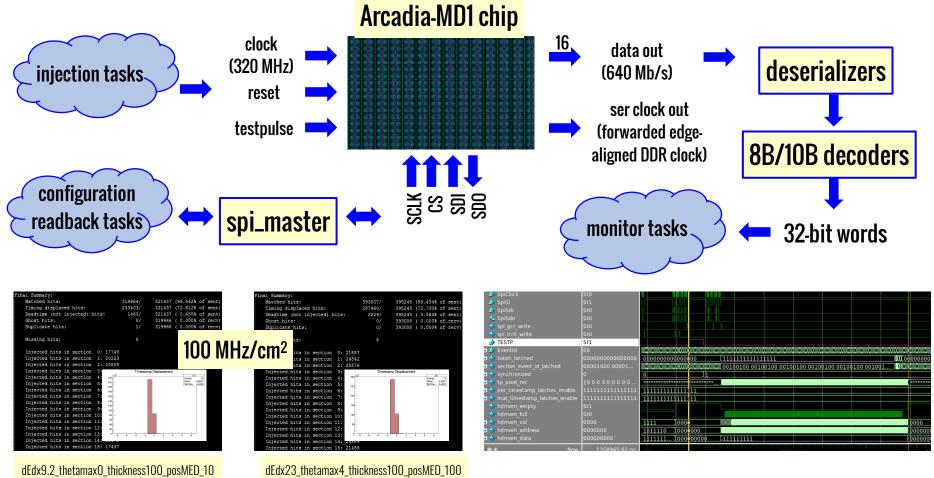

## **ARCADIA-MD1 Verification Framework**

OMHz\_50mmColl\_uniform

Manuel Rolo [INFN]

5

MHz\_50mmColl\_uniform

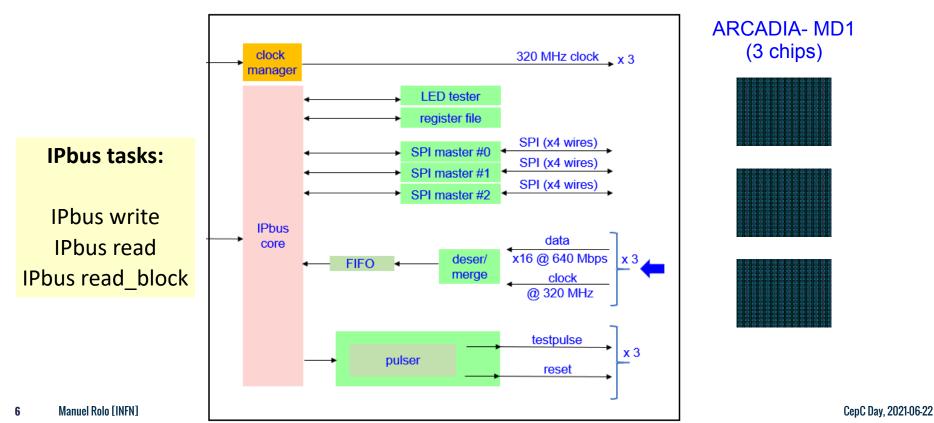

### **ARCADIA DAQ Firmware**

- The DAQ firmware blocks have also been inserted into the same simulation framework used for the ARCADIA-MD1 chip verification;

- \* We currently have a **universal simulation framework** in which the **ARCADIA-MD1 chip is configured and readout** via IPbus atomic operations **through the DAQ blocks**. This list of atomic operations is also being translated into the software running on the PC, which is being designed.

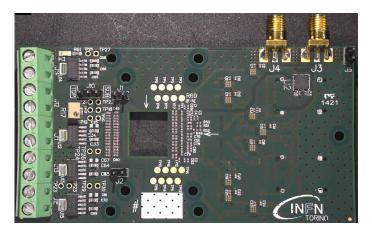

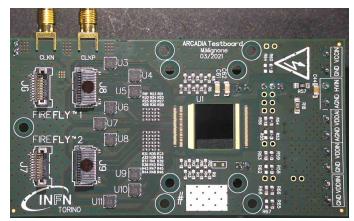

## **Front-End and Breakout Boards**

- 2 Samtec FireFly connectors for ASIC signals (Clock, SPI, Data)

- Possibility to use both an external low jitter Clock (via SMA connectors) or the clock provided by the FPGA

- Possibility to connect the high voltage on the DMAPS substrate or via the (wire bonded) pads on top

- Independent voltage regulators for the regional domains on-chip (IO Buffers, Analog Core, Digital Core)

- PCB through-hole for matrix BSI

- $\blacktriangleright$  custom FMC-to-Firefly breakout board

CepC Day, 2021-06-22

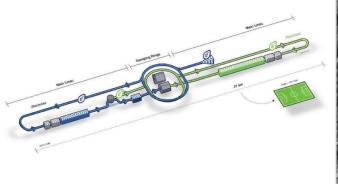

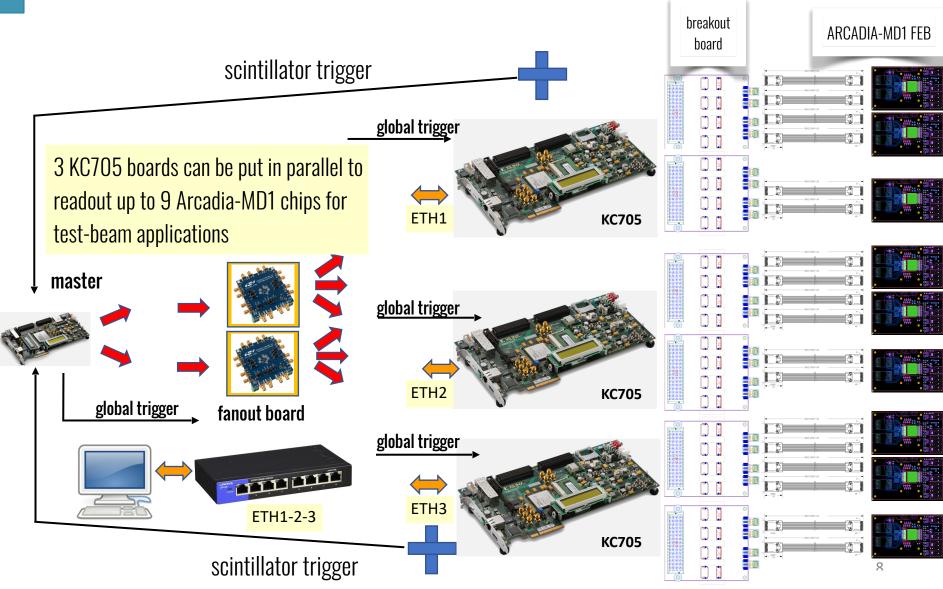

# Multi-plane MD1 Telescope Configuration

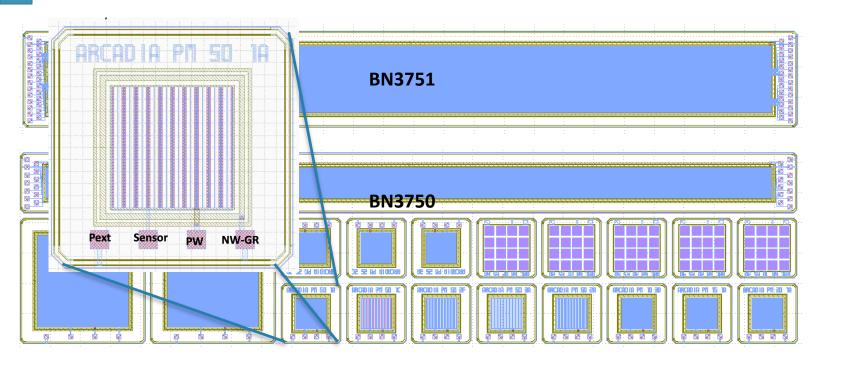

## **Pixel/Strip Test Structures**

BN3

49

#### **\*** strips come in different flavours:

- 25  $\mu$ m pitch pixelated + 25  $\mu$ m continuous (10+10) [2 variants]

- 10 µm pixelated (4 groups of 12 strips connected to pads) [4 variants]

#### $\ast$ and pixels as well:

- Pseudo-Matrices of 1x1 and 2x2 mm<sup>2</sup>

- 50  $\mu\text{m}$  (5 variants)

- 25 µm (3 variants)

- 10 µm (6 variants)

## **Getting ready for silicon: priorities**

### \* Measurements on bonded test structures (first non-irradiated and then irradiated with xrays and neutrons), front-side and back side

- IV curves with temperature, extraction of depletion, punch-through voltages, dark current and capacitance

- Charge collection with focused pulsed laser (back-side). On pixels: only signal evolution with time and position of the laser spot. On strips: charge sharing is also possible.

- Lab. sources. (top-side and back-side)

### **\*** Characterisation of the ARCADIA-MD1

- functional and electrical characterisation (basic functionalities with on-chip test pulse and hit injection, scurves, threshold calibration, rate assessment)

- laser scans with red and IR light (CCE vs bias voltage, uniformity, clustering and resolution)

- tests with x-ray and radioactive sources (55Fe, 241Am, 90Sr)

- cosmic ray stand (sync and event building, efficiency, resolution) and beam tests with MD1 telescopes

### Platform for sensor design and fabrication

Discussion on the use of SEED/ARCADIA for the R&D towards CEPC started in 2019.

2019-11-25

INFN and IHEP can share CMOS design databases and program shared tapeouts to foundry

#### \* Discussion started on <u>design and fabrication flow towards a Joint IHEP-INFN MAPS</u>:

- INFN provides IHEP with a signal sample database and a simplified sensor geometry

- ▶ IHEP designs (in-house or in cooperation with INFN) a CMOS MAPS using LFoundry LF11is

- ▶ INFN cares the final DRC on IHEP's gds2, validation of the design and production

### **ARCADIA: status and plans in a nutshell**

- **\* ARCADIA** has now secured a total budget of 1.4 M $\in$  with several groups working on:

- Sensor R&D and Technology

- CMOS IP Design and Chip Integration

- Data Acquisition for electrical characterisation and beam tests with multi-chip telescopes

- Radiation Hardness qualification

- System-level characterisation for Medical (pCT), Future Leptonic Colliders and Space Instruments

### \* Schedule for 2021-2022

- ▶ all hardware and firmware ready for testing, first silicon just delivered

- Ist SPW run included <u>800 mm2 of innovative DMAPS</u>, sensor and CMOS technology (first tests on sensors are ok, wafers currently being diced)

- 2nd run mid-2021: in preparation, <u>3rd run planned for mid-2022;</u>

# Thank you for listening!