# **ARCADIA** A novel platform for the implementation of innovative CMOS monolithic sensors

#### International Workshop on the CEPC November 8<sup>th</sup> - 12<sup>th</sup>, 2021

Manuel Rolo (INFN), on behalf of the ARCADIA Collaboration

Istituto Nazionale di Fisica Nucleare

#### **ARCADIA (INFN CSNV Call Project)**

Advanced Readout CMOS Architectures with Depleted Integrated sensor Arrays

Creation of a novel platform for the implementation of innovative monolithic sensors compatible with standard CMOS fabrication processes

- Challenge: deployment of large-area system-grade CMOS sensors implementing scalable readout architectures with ultra-low power capability (O(10 mW/cm2))

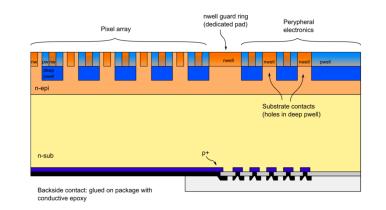

- Technology: LFoundry 110nm CMOS node, quad-well, high-resistivity bulk

- $\blacktriangleright$  Active sensor thickness in the range 50  $\mu m$  to 500  $\mu m$

- Operation in full depletion with fast charge collection only by drift

- Small charge collecting electrode for optimal signal-to-noise ratio

#### **ARCADIA CMOS DMAPS at CEPC**

https://indico.ihep.ac.cn/event/15229/session/6/contribution/3/material/slides/3.pdf

#### Projects overview: R&D schedule

| PBS             | Task Name                                             | Start                            | Finish                   | 2020 |    | 2021 |    | 2022  |      | 2023   |       | 2024             |       | 2025 |    | 2026 |          | 2027       |          | 2028  |          | 2029 |     |

|-----------------|-------------------------------------------------------|----------------------------------|--------------------------|------|----|------|----|-------|------|--------|-------|------------------|-------|------|----|------|----------|------------|----------|-------|----------|------|-----|

|                 |                                                       |                                  |                          | H1   | H2 | H1   | H2 | H1    | 12   | H1     | H2    | H1               | H2    | H1   | H2 | H1   | H2       | H1         | H2       | H1    | H2       | H1   | H2  |

|                 | CEPC Detector R&D Project                             | 2020/5/7                         | 2026/12/31               | -    |    |      |    |       | _    |        |       |                  |       |      |    |      |          | 1 CEP      | PC Det   | ector | R&D      | Proj | ect |

| 1               | Vertex                                                | 2020/5/7                         | 2023/12/29               | l r  | _  | -    | _  |       | -    |        | -     | Ver              | tex   |      |    |      |          | -          | -        |       |          | -    |     |

| 1.1             | Vertex Prototype                                      | 2020/5/7                         | 2023/12/29               |      |    |      |    |       |      |        |       | Vert             | ex Pi |      |    |      |          |            |          |       |          |      |     |

| 1.2             | ARCADIA CMOS MAPS                                     | 2020/5/7                         | 2021/12/31               |      |    |      |    | ARCA  | DIA  | CMOS   | 5 MAI | PS               |       |      |    |      |          |            |          | 47    | <b>`</b> |      | 000 |

|                 |                                                       |                                  |                          |      |    |      |    |       |      |        |       |                  |       |      |    |      |          |            |          |       |          |      |     |

| z               | Tracker                                               | 2020/5/7                         | 2024/12/31               |      |    |      | _  |       |      |        |       |                  |       |      | ρχ | ΤΑ   | n        | <b>U P</b> | n        |       | //       | 7    | 17  |

| 2<br>2.1        | Tracker<br>TPC Module and Prototype                   |                                  | 2024/12/31<br>2021/12/31 |      |    |      |    | TPC N | odu  | ule an | d Pro | totyp            | e     |      | ex | Te   | <b>n</b> | Cle        | <b>C</b> |       | 27       | Z    | 022 |

| 2<br>2.1<br>2.2 |                                                       | 2020/5/7                         |                          |      |    |      |    | TPC N | odu  | ule an |       | totyp<br>Silicor |       |      | ех |      | <b>n</b> | <b>d</b> e | d        |       | 27       | Z    | UZZ |

|                 | TPC Module and Prototype                              | 2020/5/7<br>2020/5/7             | 2021/12/31               |      |    |      |    | TPC N | lodu | ule an |       |                  |       |      |    |      |          |            | ed.      |       | 21       | Z    | UZZ |

| 2.2             | TPC Module and Prototype<br>Silicon Tracker Prototype | 2020/5/7<br>2020/5/7<br>2020/5/7 | 2021/12/31<br>2023/10/31 |      |    |      |    | TPC N | lodu | ule an |       |                  |       |      |    | mper |          | ues        | ed       |       | 21       | 21   | UZZ |

CEPC detector R&D Project for preliminary evaluation by the CEPC International Detector R&D Committee

https://indico.ihep.ac.cn/event/15229/session/6/contribution/3/material/slides/4.pdf

#### **1.2 ARCADIA CMOS MAPS**

| Document Responsible: | Manuel Rolo           |

|-----------------------|-----------------------|

| Last saved by on      | 11/01/2021 5:00:00 PM |

| Revision number:      | 2                     |

|                       |                       |

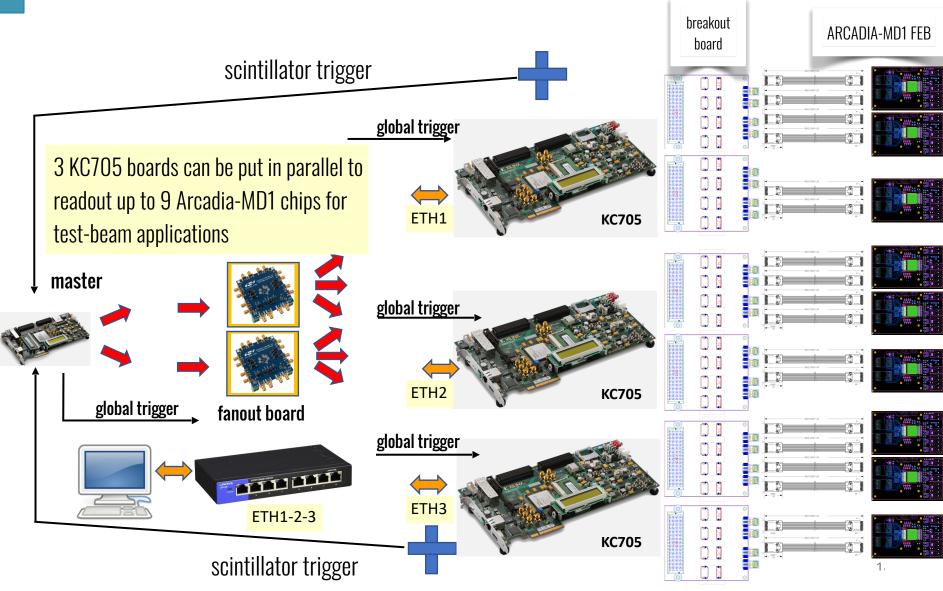

"The main goal of the project, started in 2019 with a timescale of 3 years, is the design, production and commissioning of an array of 512x512 pixels with a pitch of 25 x 25  $\mu$ m2 (total matrix area 1.28x1.28 cm2), embedded electronics performing sparsified readout and power consumption at the level of 20 mW/cm<sup>2</sup>. This test vehicle is expected the be a viable prototype for applications at the next generation lepton colliders."

## **ARCADIA-MD1: Main Demonstrator Chip**

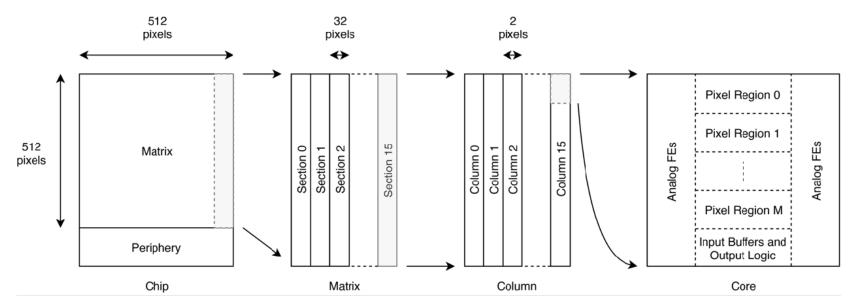

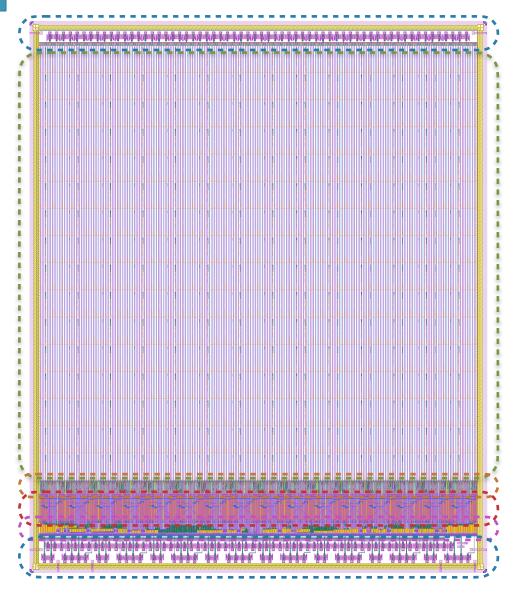

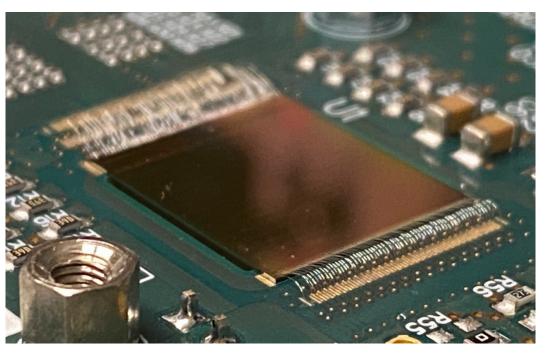

- Pixel size 25 μm x 25 μm, Matrix core 512 x 512, 1.28 x 1.28 cm<sup>2</sup> silicon active area, "side-abuttable"

- Triggerless binary data readout, event rate up to 100 MHz/cm<sup>2</sup>

- First Engineering Run (SPW) takeout 11/2020, silicon being tested

- 2<sup>nd</sup> full CMOS maskset mid-2021, fab out expected January 2022

- 3<sup>rd</sup> SPW mid-2022 with design fixes, explorative sensor and CMOS designs, new architectures with higher data throughput, full chip demonstrator for fast timing (R&D on sensors and electronics already started with 2nd SPW)

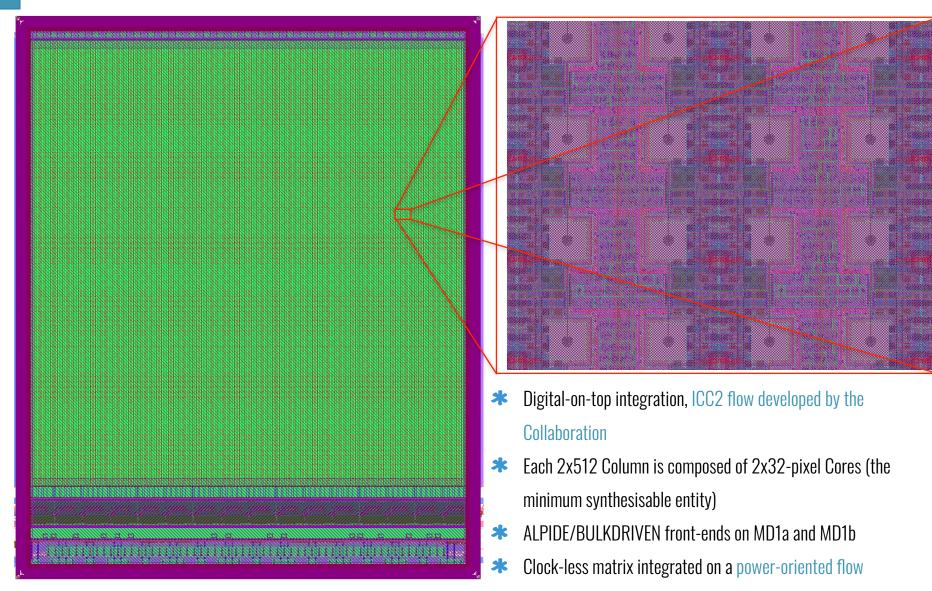

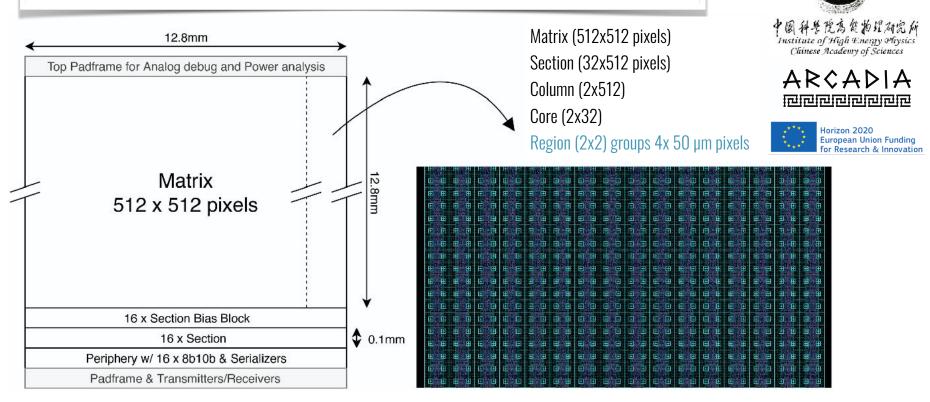

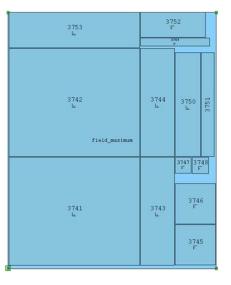

## **ARCADIA-MD1 - Floorplan**

#### **Top Padframe**

Auxiliary supply, IR Drop Measure

#### **Matrix**

512x512 pixels, Double Column arrangement

#### End of Sector (x16)

Reads and Configures 512x32 pixels

#### Sector Biasing (x16)

Generates I/V biases for 512x32 pixels

#### Periphery

SPI, Configuration, 8b10b enc, Serializers

#### **Bottom Padframe**

**Stacked Power and Signal pads**

5

### **ARCADIA - Main Demonstrator Chip**

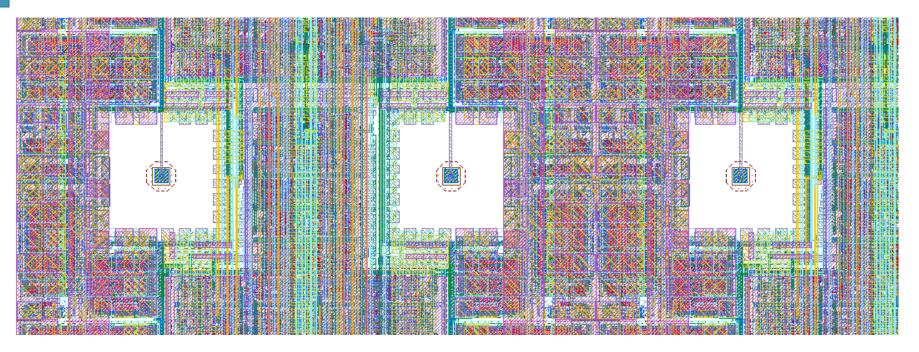

## **ARCADIA-MD1 - Pixels**

- \* The pixel's area is occupied by the collection diode (16%), analog and digital circuitry

- \* 2-bit pixel configuration for masking and injection enabling

- \* Digital injection capability for readout chain testing, bypassing FEs

- \* Custom power distribution scheme to maximize metal occupancy

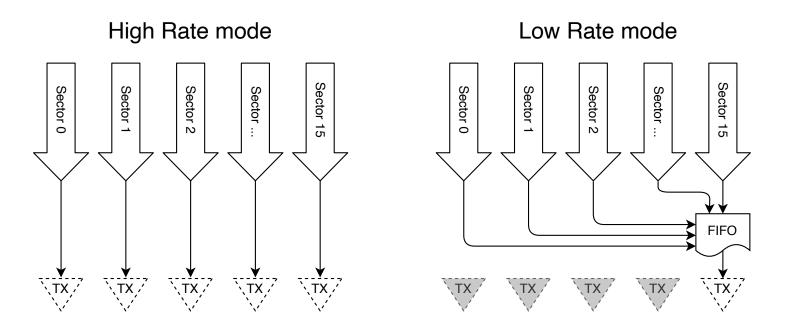

## **ARCADIA-MD1 - Peripheral Dataflow**

- Each Column (32x512 pixels) has a readout BW of 443Mbps

- Sector data is sent out (8b10b encoded) via dedicated 320MHz DDR Serialisers

- In Low Rate Mode, the first serialiser processes data from all the sections. The other serialisers and C-LVDS TXs<sup>(\*)</sup> are powered off in order to reduce power consumption.

\* "A 2 Gbps custom LVDS transceiver for the ARCADIA project", talk at IEEE NSS-MIC 2021

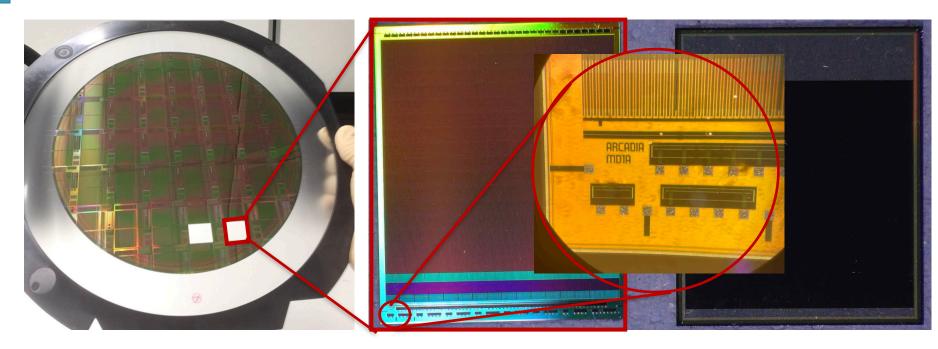

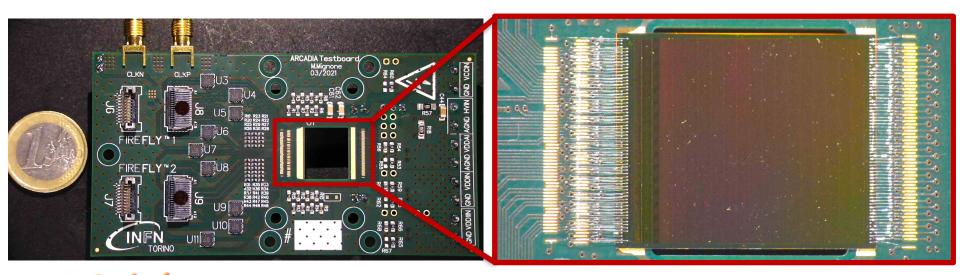

## Silicon from 1st Eng. Run - MD1

- First samples of **ARCADIA-MD1 powered-on** this summer

- Later-than-tapeout simulations identified bug on pad frame connections, simple to solve with FIB

- First data looks good & sensor depletion OK

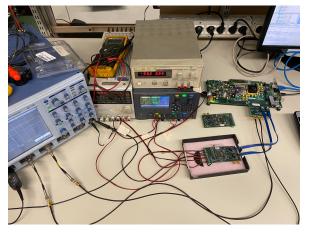

## Front-end FEB-MD1 and breakout boards

- 2 Samtec FireFly connectors for ASIC signals (Clock, SPI, Data)

- Connection to external low jitter Clock (via SMA connectors)

- High voltage to the DMAPS backside or (wirebonded) to pads on top

- Independent LDOs for IO Buffers, Analog Core, Digital Core

- PCB through-hole for matrix BSI

- custom FMC-to-Firefly breakout board

## MD1: check-list from electrical tests

- Chip configuration write/readback

- Space Mode enable/disable

- $\mathbf{M}$  Clock Gating and Clock Dividers

- ☑ Digital Injection

- ☑ LVDS SER1-15 enable/disable

- ☑ Test Pulse connectivity

- $\mathbf{M}$  Analog FE bias and threshold scan

- Soft (SPI-enabled) and Hard (through Ext pin) Resets

- tests with analogue front-end ongoing:

- test pulse charge injection with FE, s-curves, FE baseline map, noise measurements, depletion studies

- next: characterisation with radioactive sources and laser

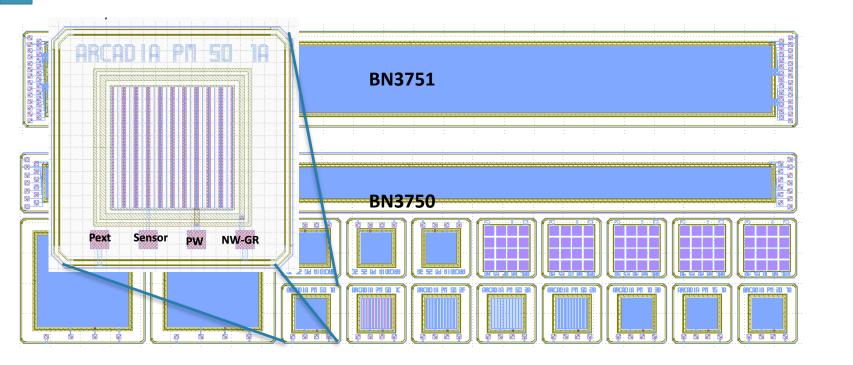

## **Pixel/Strip Test Structures**

BN3

49

#### **\*** strips come in different flavours:

- 25  $\mu$ m pitch pixelated + 25  $\mu$ m continuous (10+10) [2 variants]

- 10 μm pixelated (4 groups of 12 strips connected to pads) [4 variants]

#### \* and pixels as well:

- Pseudo-Matrices of 1x1 and 2x2 mm<sup>2</sup>

- 50  $\mu$ m (5 variants)

- 25  $\mu\text{m}$  (3 variants)

- 10  $\mu\text{m}$  (6 variants)

### Status of silicon testing - 1st SPW

- Measurements on bonded test structures (first non-irradiated and then irradiated with x-rays and neutrons), front-side and back side

- now

- 11/21

- IV curves with temperature, extraction of depletion, punch-through voltages, dark current and capacitance, first laser tests

- Charge collection with focused pulsed laser (back-side). On pixels: only signal evolution with time and position of the laser spot. On strips: charge sharing is also possible.

- Lab. sources. (top-side and back-side)

#### \* Characterisation of the ARCADIA-MD1

13

Manuel Rolo [INFN]

- functional and electrical characterisation (basic functionalities with on-chip test pulse and hit injection, s-curves, threshold calibration, rate assessment)

- laser scans with red and IR light (CCE vs bias voltage, uniformity, clustering and resolution)

- tests with x-ray and radioactive sources (55Fe, 241Am, 90Sr)

- cosmic ray stand (sync and event building, efficiency, resolution) and beam tests with MD1 telescopes

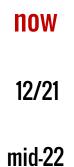

## Multi-plane MD1 Telescope Configuration

## **ARCADIA-MD2**

A second main demonstrator (codename ARCADIA-MD2) has been submitted in Summer 2021, featuring design and architecture improvements targeting power reduction, scalability.

- \* 16x2 pixel Cores, 8 Cores in the Matrix

- Logic and buffering optimization -> Acknowledge signal propagates 7 times faster!

- Simulations validated matrices up to 8192 pixels high

- Power optimization in the periphery

- I GHz DDR serializer -> 2Gbps bandwidth!

- Now in foundry, expected dies in January 2022.

### **Pixel Readout ASIC for photon-counting**

#### in collaboration with the Division of Nuclear Technology and Applications at IHEP

- Implementation of the sensor matrix for photon-counting ASIC using a 100 x 100 µm ARCADIA super-pixel

- Chip design and sensor simulations ongoing, silicon prototype production scheduled for 2022-Q2

- Final version should allow both a hybrid assembly of a CdTe detector and a fully-depleted silicon sensor

## **CMOS Embedded Si-strip and readout**

Design and Production of continuous and "pixelised" strips, range 10 - 100µm pitch

Proof-of-concept: CMOS monolithic strip block and readout electronics

Manuel Rolo [INFN]

## **Summary and Outlook**

- **\* ARCADIA** has now secured a total budget of 1.4 M $\in$  with several groups working on:

- Sensor R&D and Technology

- CMOS IP Design and Chip Integration

- Data Acquisition for electrical characterisation and beam tests with multi-chip telescopes

- Radiation Hardness qualification

- System-level characterisation for Medical (pCT), Future Leptonic Colliders and Space Instruments

#### **\*** Schedule for 2021-2022

- ARCADIA-MD1 submitted in October 2020, first dies in June 2021

- Ist SPW run included <u>800 mm2 of innovative DMAPS</u>, sensor and CMOS technology (tests on sensors are ok, tests on all digital and analog features confirmed the expected functionality)

- 2nd run mid-2021: in foundry, <u>3rd run scheduled for mid-2022;</u>

# Thank you for your time!