## Zhijun Liang (IHEP)

Institute of High Energy Physics Chinese Academy of Sciences

## MOST2 vertex detector R & D: Research Goal

- Produce a world class vertex detector prototype

- Spatial resolution  $3 \sim 5 \mu m$  (pixel detector)

- Radiation hard (>1 MRad)

- Preliminary design of prototype •

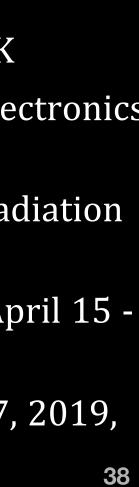

- Three layer, module  $\sim 1 \text{ cm} \times 12 \text{ cm}^2$

### **Typical tracker**

**Typical module**

Resolution

**ATLAS/CMS upgrade** (~15 µm)

> Alice upgrade (**5~10 µm**)

World leading This project (3~5 µm)

## Overview of task2: vertex detector R & D

- Can break down into sub-tasks:

- CMOS imaging sensor chip R & D

- Detector assembly

- Data acquisition system R & D

## • Detector layout optimization, Ladder and vertex detector support structure R & D

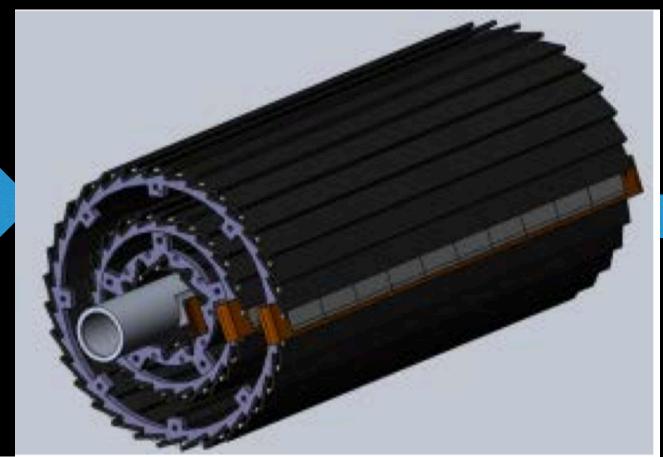

### Full size vertex detector Prototype

### Beam test to verify its spatial resolution

## Achievement Presentation and Assessment Methods

|                             | 考核                     | 指标2                                                        |                |                                                                                                                        |                                |

|-----------------------------|------------------------|------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 指标<br>名称                    | 立时<br>有<br>行<br>状<br>态 | 中期指标值<br>/状态 <sup>3</sup>                                  | 完成<br>时指<br>状态 | 考核方式(方<br>法)及评价手<br>段 <sup>4</sup>                                                                                     |                                |

| 硅径迹探<br>测器原型<br>分辨率         | 无                      | 研制出小型<br>传感器芯<br>片,像素单<br>元尺寸小于<br>或等于 25<br>微米 ×25<br>微米。 | 3-5<br>微米      | 同行专家评<br>间。过束流分析空家子、<br>高、大学、<br>市、<br>市、<br>市、<br>市、<br>市<br>の<br>市<br>の<br>市<br>の<br>市<br>の<br>市<br>の<br>市<br>の<br>市 | S<br>- Mid-terr<br>- Final : 3 |

| 所设计的<br>抗辐器器<br>承<br>到<br>量 | 无                      | 完成传感器<br>的初步设<br>计,通过仿<br>真初步验证<br>其抗辐照性<br>能              | 1<br>MRad      | 同行专家评<br>审(提供传<br>感器的设计<br>与测试报告<br>供专家评审)                                                                             | F<br>- mid-te<br>- Final :     |

Silicon Detector

Assessment index

## Spatial resolution

m: produce 25\*25 µm pixel size chip 3-5 µm resolution in Beam test

### **Radiation hardness**

erm: verified by TCAD simulation : Total ionization dose >1 Mrad

4

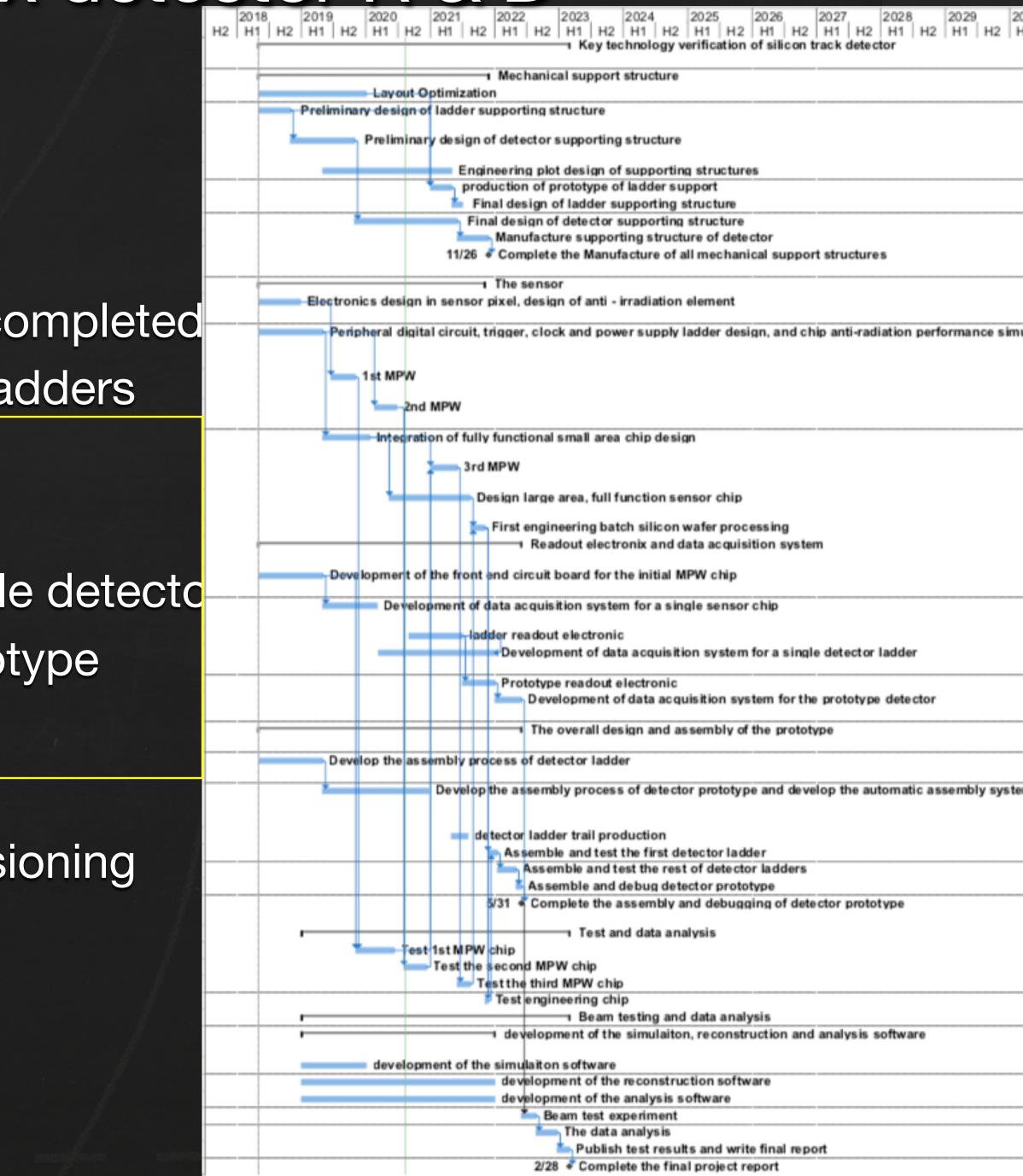

## Overall plan of task2: Vertex detector R & D

### • 3rd Year:

- 3<sup>rd</sup> CMOS sensor fabricated and tested

- $\rightarrow$  skipped , since 2<sup>nd</sup> MPW chip is working well

- Final support structure engineering design completed

- Fabricated support structure prototype for ladders

- 4th Year (2021.7 2022.6) :

- Competed R & D full-size TaichuPix sensor

- Manufactured the support structure for whole detector

- Assembling and installing the detector prototype

- Completed DAQ system for whole detector

### 5th Year:

- Completed detector assembly and commissioning

- Test beam and data analysis

- Finish assembling of prototype

| 030<br>H1 H2 | 203 |  |

|--------------|-----|--|

| H1   H2      | H   |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

| ulation      |     |  |

| alation      |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

| em           |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

|              |     |  |

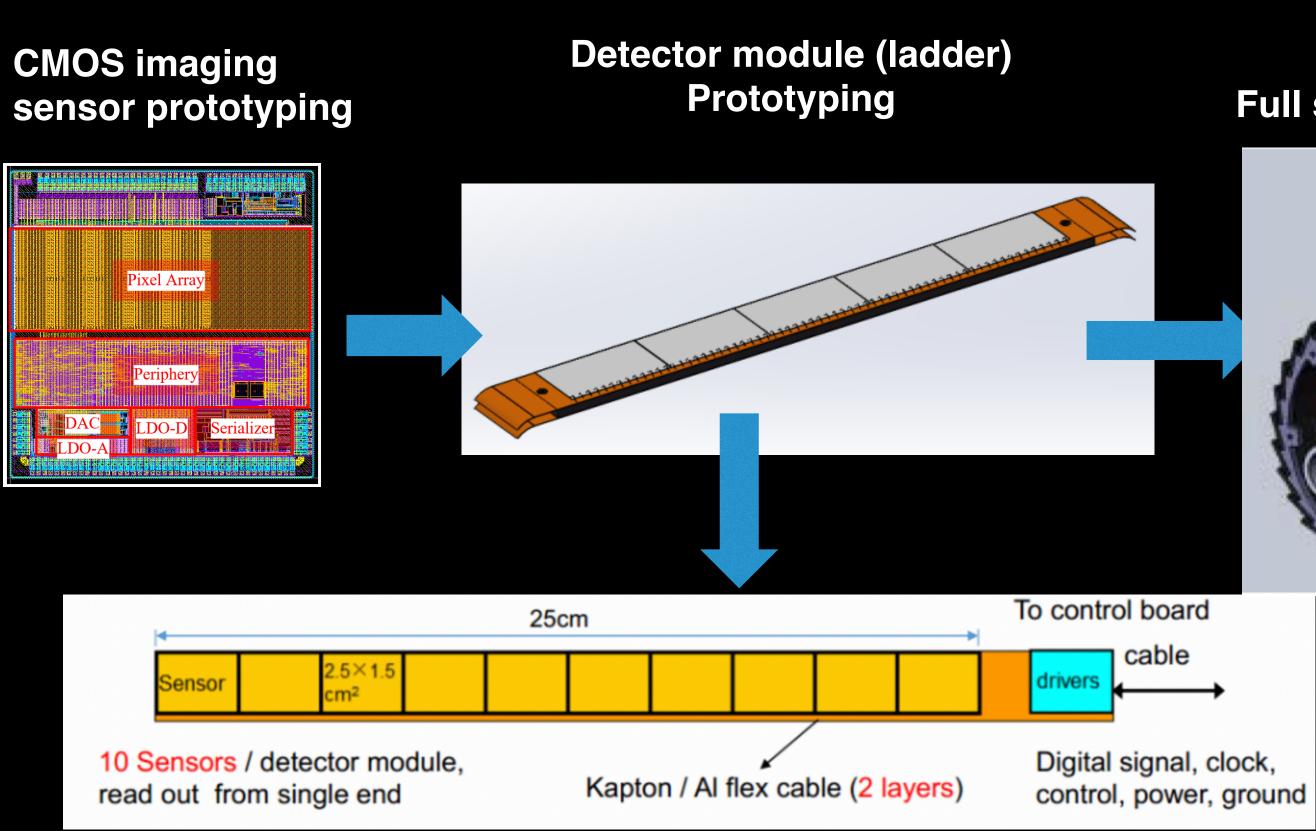

# CMOS Sensor chip R & D

- The existing CMOS monolithic pixel sensors can't fully satisfy the requirement

- Major Challenges for the CMOS sensor •

- Small pixel size -> high resolution (3-5 μm)

- Radiation tolerance (per year): 1 MRad

|               | ALPIDE       | ATLAS-MAPS<br>(MONOPIX / MALTA) | MIMOSA       |

|---------------|--------------|---------------------------------|--------------|

| Pixel size    | $\checkmark$ | Χ                               | $\checkmark$ |

| Readout Speed | Χ            | $\checkmark$                    | Χ            |

| TID           | X (?)        |                                 | $\checkmark$ |

# • High readout speed (<500ns deadtime @40MHz at Z pole) -> for CEPC Z pole high lumi

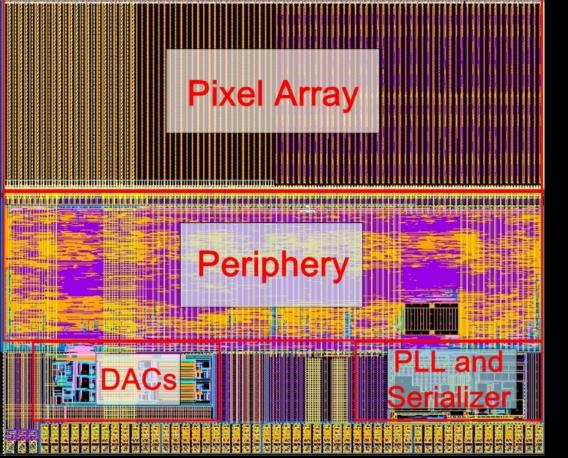

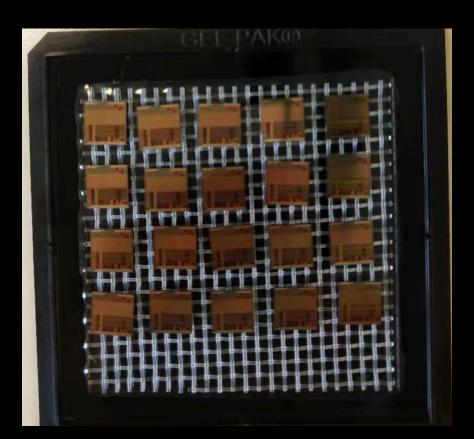

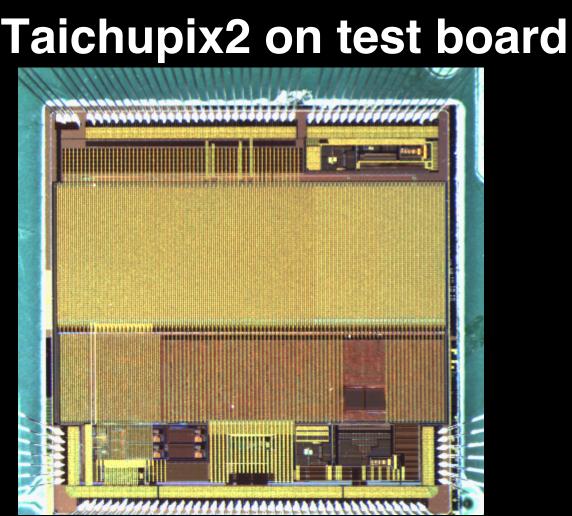

# Sensor prototyping

- Completed two round of sensor prototyping

- 1<sup>st</sup> Multi-wafer project chip (Taichupix1)

- Submitted in June 2019, received in November 2019

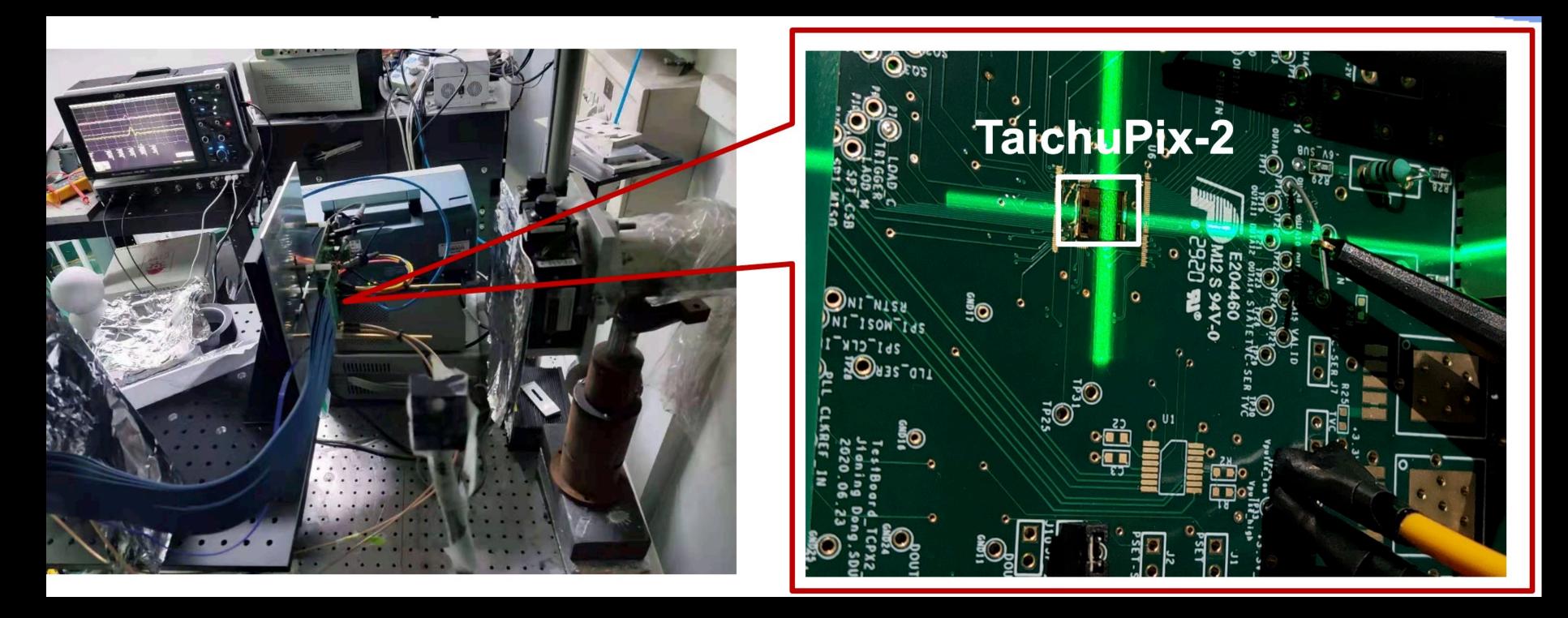

- 2<sup>nd</sup> Multi-wafer project chip(Taichupix2)

- Submitted in Feb 2020, received in July 2020

- Major bugs fixed in Taichupix1

- Radiation hard design (enclosed gate) in pixel analog

- A full functional pixel array (64×192 pixels)

- **Periphery logics**

- Fully integrated logics for the data-driven readout •

- Fully digital control of the chip configuration •

- Auxiliary blocks for standalone operation

- High speed data interface up to 4 Gbps

- **On-chip bias generation**  $\bullet$

- Power management with LDOs ullet

### Taichupix1 Chip size: 5mm×5mm Pixel size: 25µm×25µm

# Taichupix2

## Chip size: 5mm×5mm Pixel size: 25µm×25µm

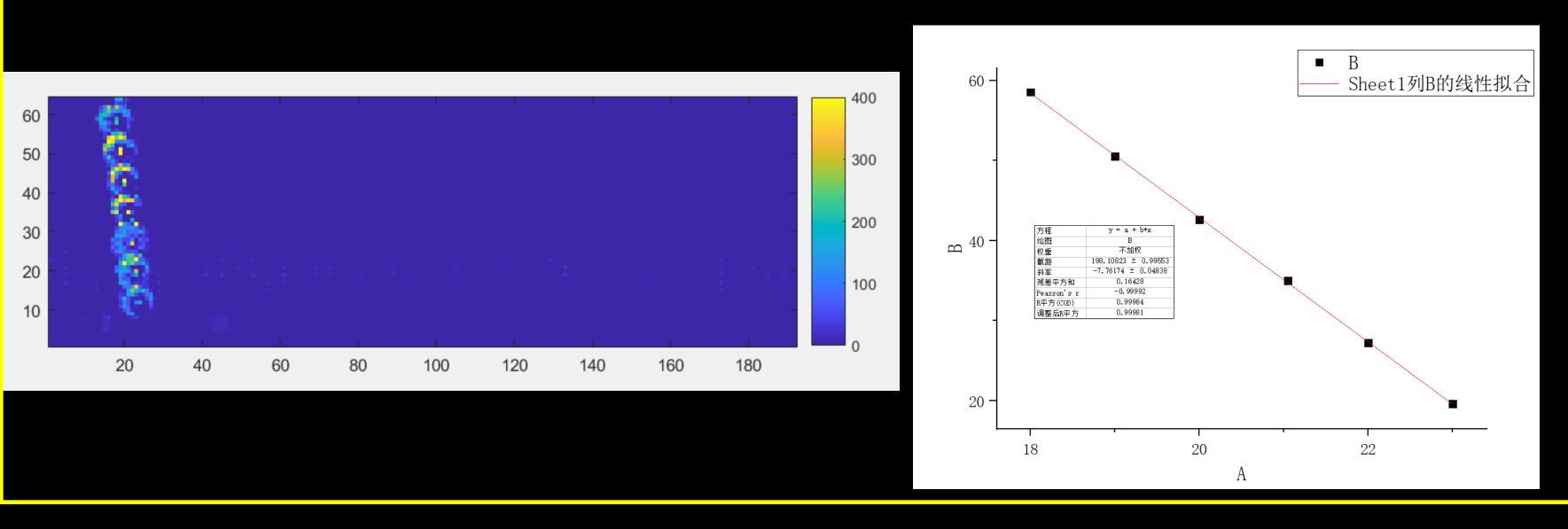

## Laser test in last report (coarse scan) • Triggerless mode was used for the laser test $\rightarrow$ full readout chain verified • Measured positions from Taichupix is consistent with expected laser movements

### Light spot fitting for laser moving in y-direction with step of 200 $\mu$ m

Laser (1064 nm)

**TaichuPix-2**

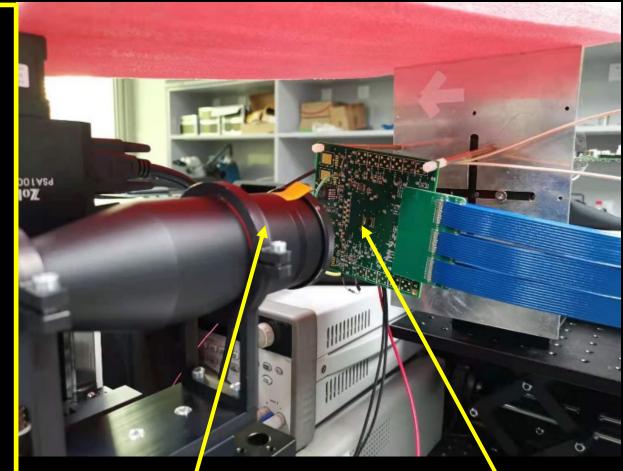

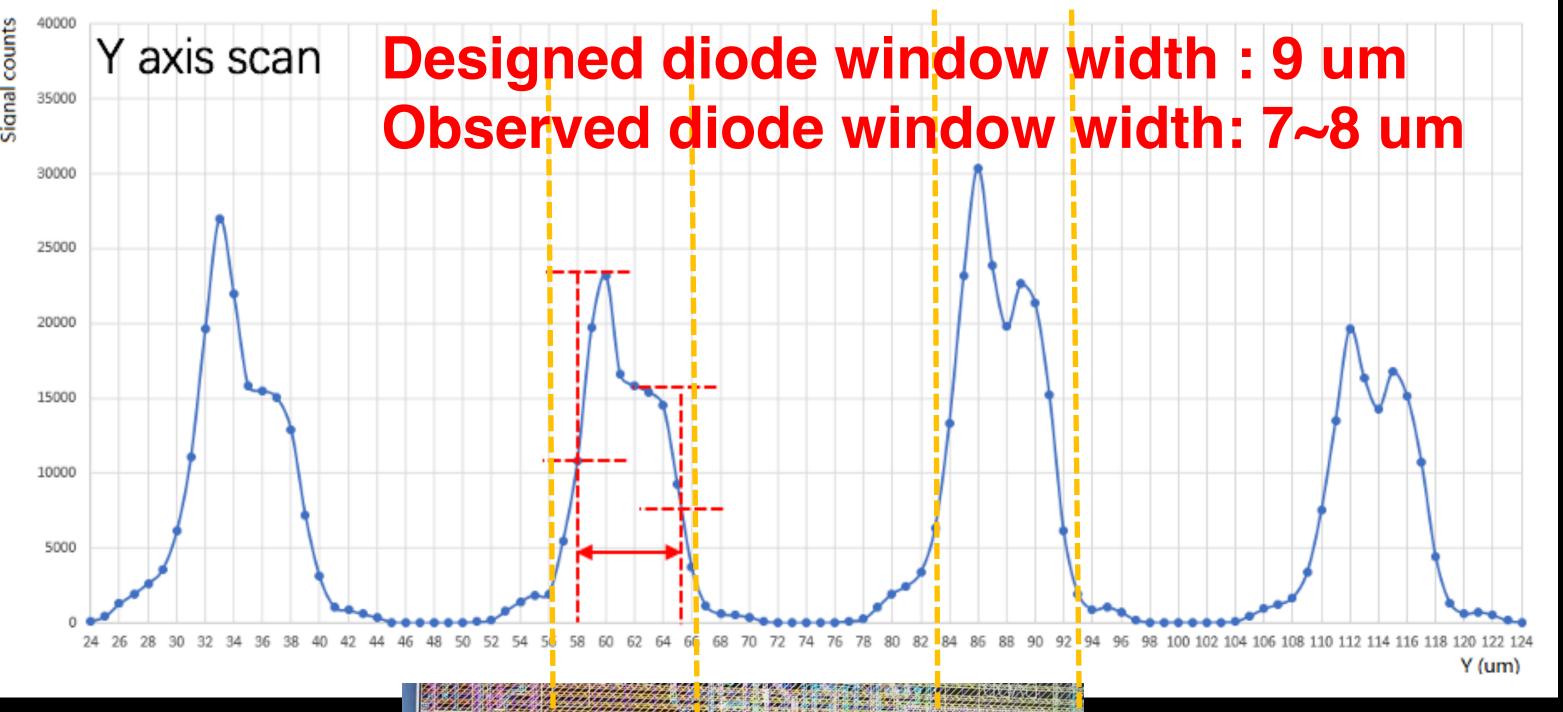

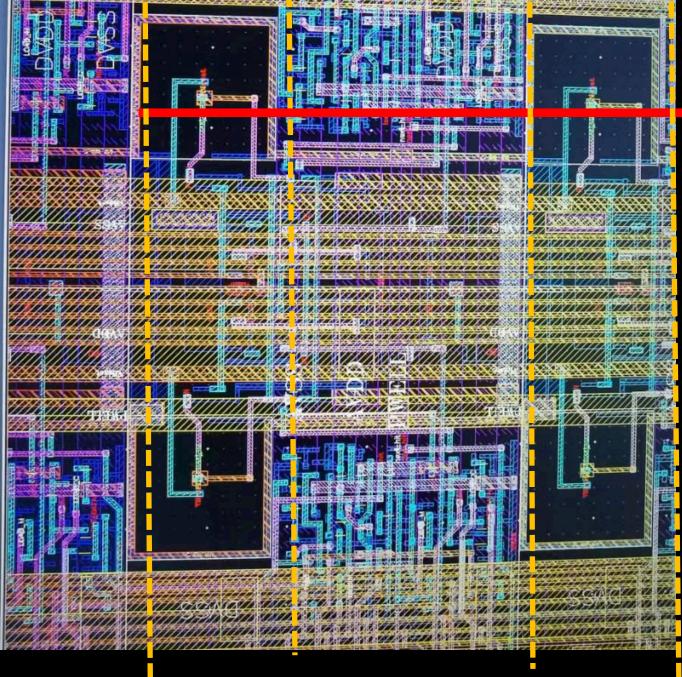

# Laser test (fine scan)

- Improved laser setup

- Beam spot focused to few um

- Study pixel internal structure

- Study Uniformity of response

### **Scan direction**

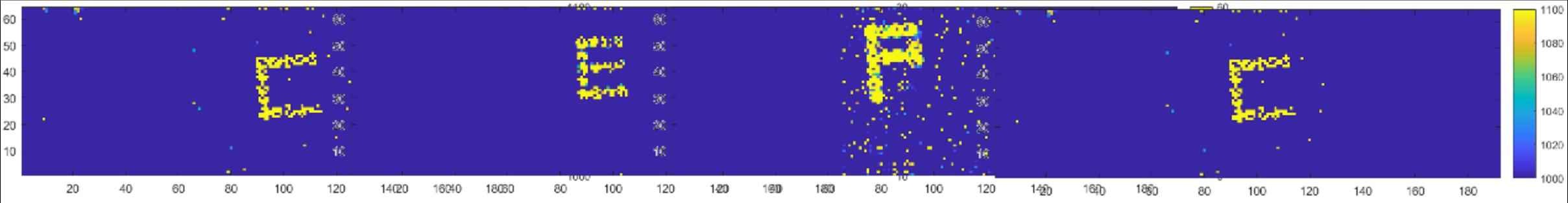

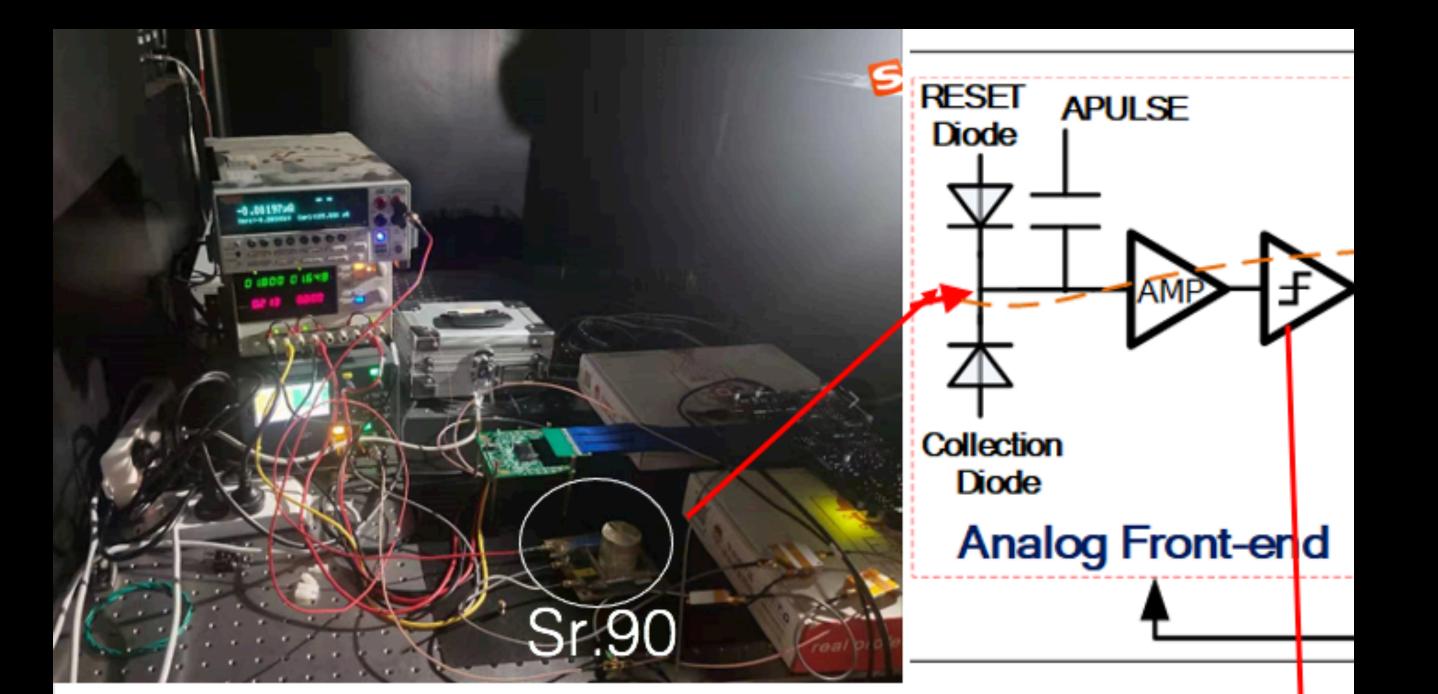

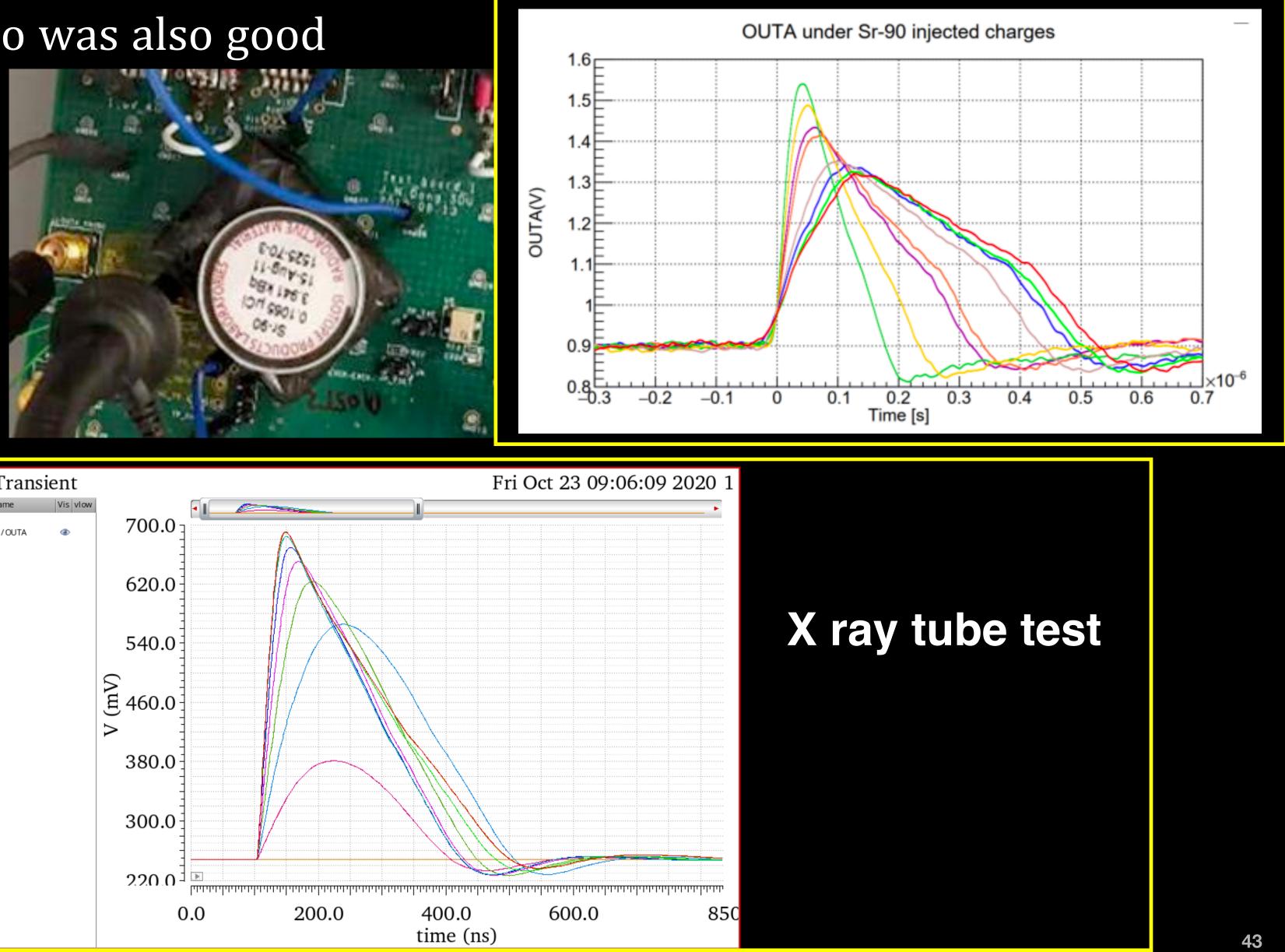

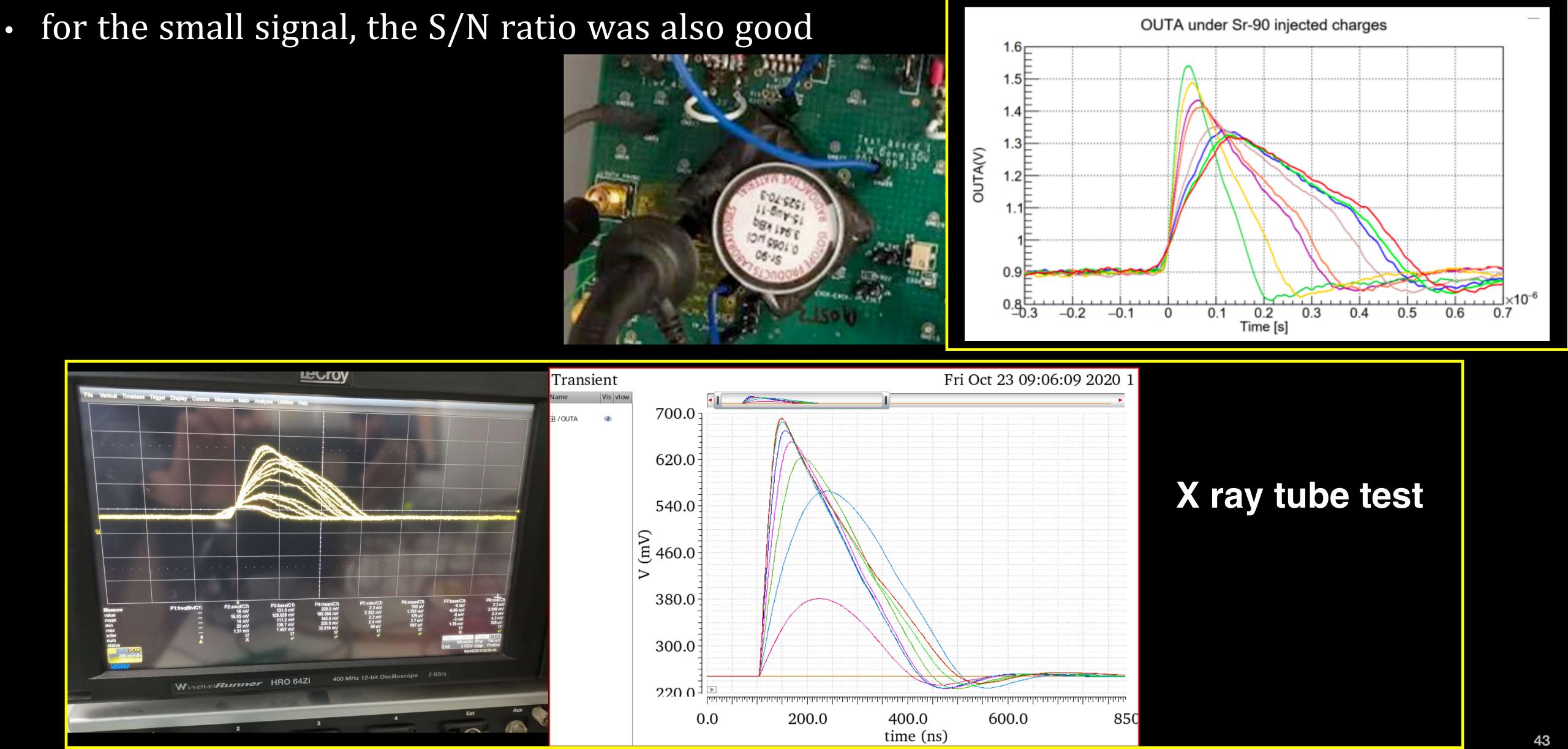

## TaichuPix2 test with <sup>90</sup>Sr source

- Digital readout (full chip)

- Analog readout (debug mode for one row of pixel)

- High signal to noise ratio found in analog readout

- More studies are on-going

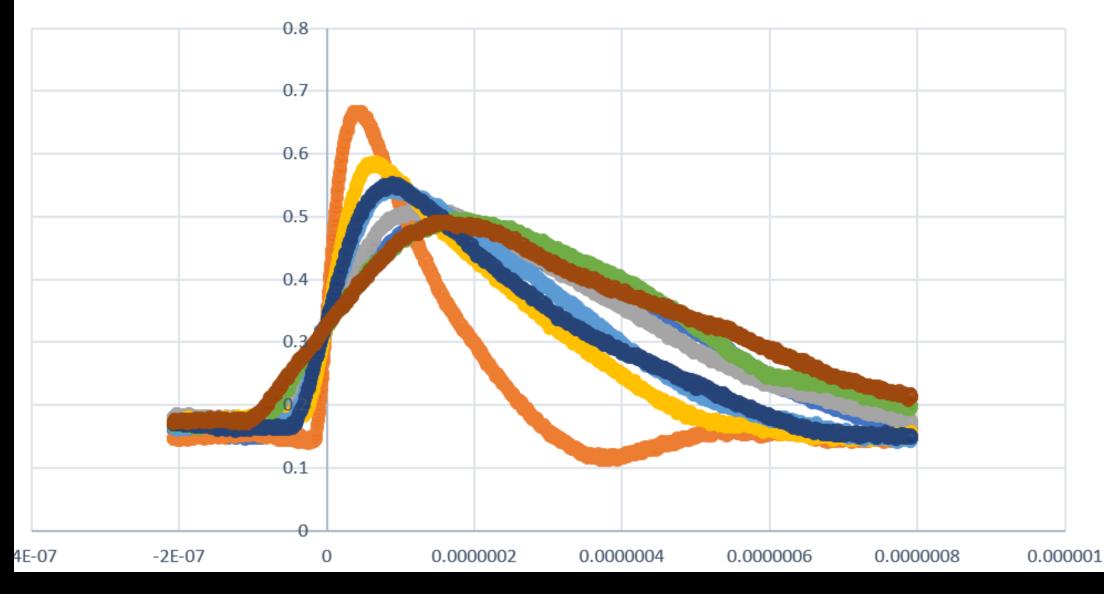

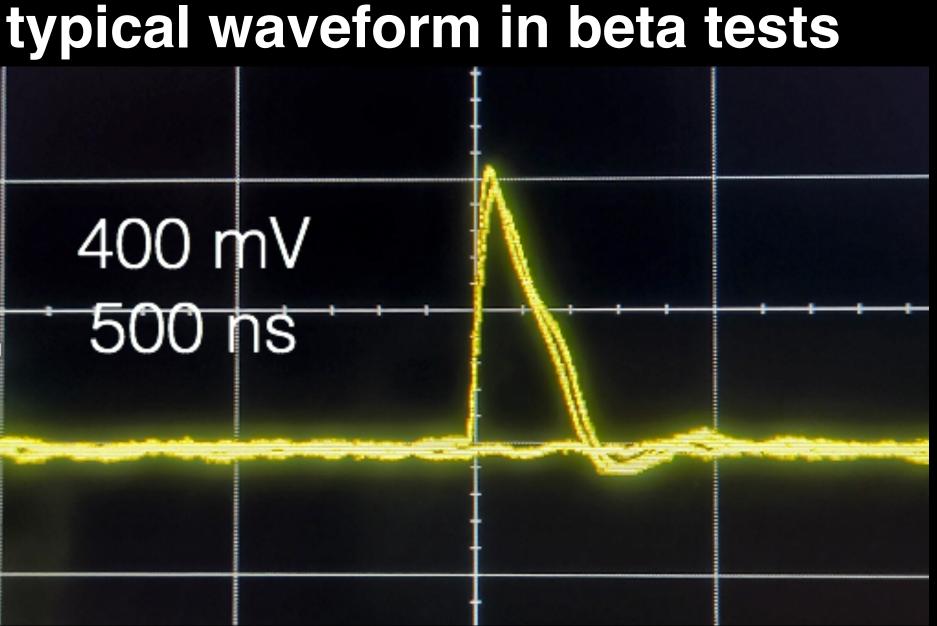

## Analog waveform in beta tests

### typical waveform in beta tests

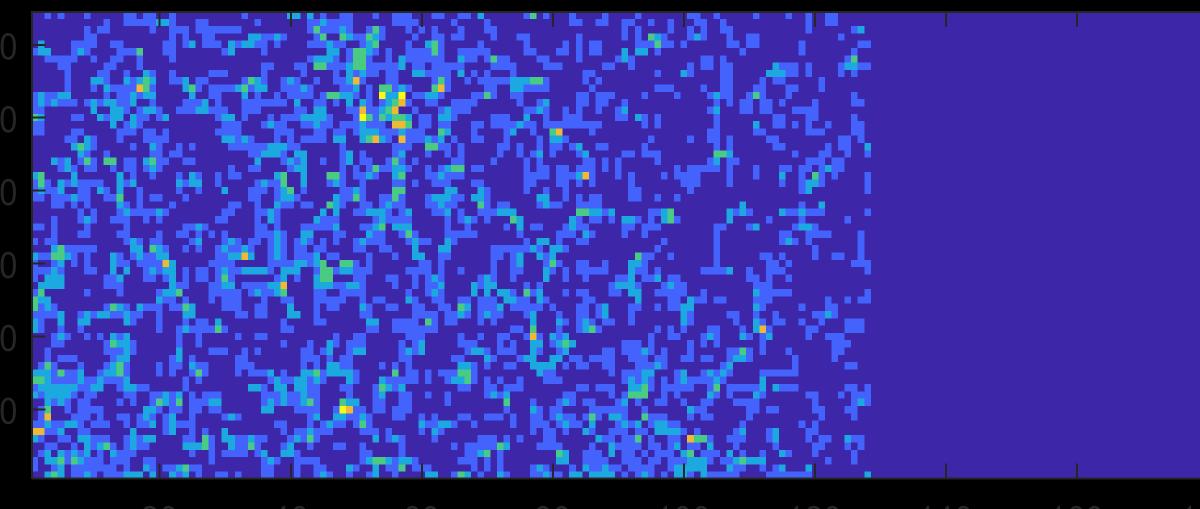

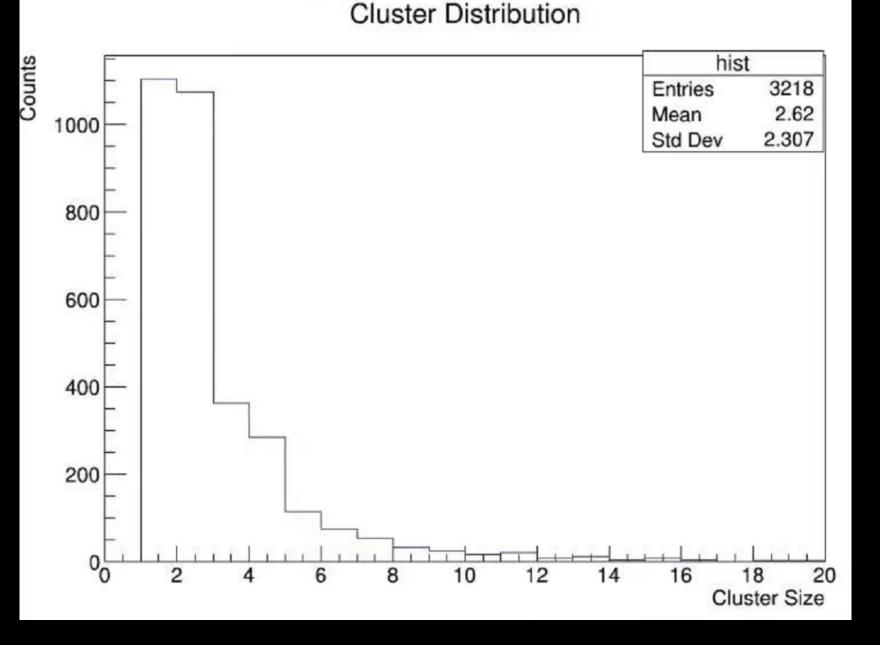

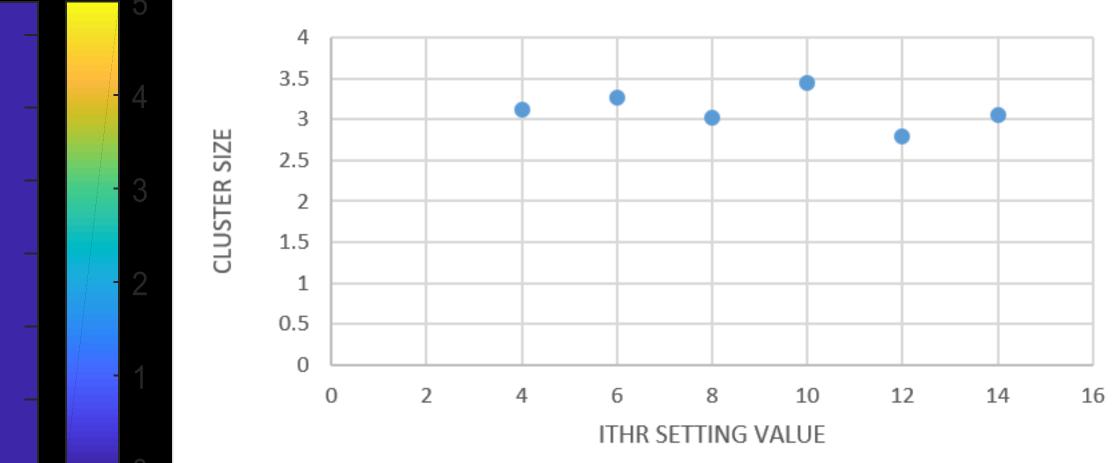

## TaichuPix2 test with $^{90}$ Sr source (2)

- exposure to <sup>90</sup>Sr at different threshold (ITHR)

- Finding a cluster for adjacent pixels with a timestamp window of 100 ns

- Mean cluster size around 3 for different ITHR

### Hit map of TC2 exposure to <sup>90</sup>Sr for 400 s

## **Cluster size distribution**

## <Mean Cluster size> VS Threshold

Cluster size vs. ITHR of Sector 1

11

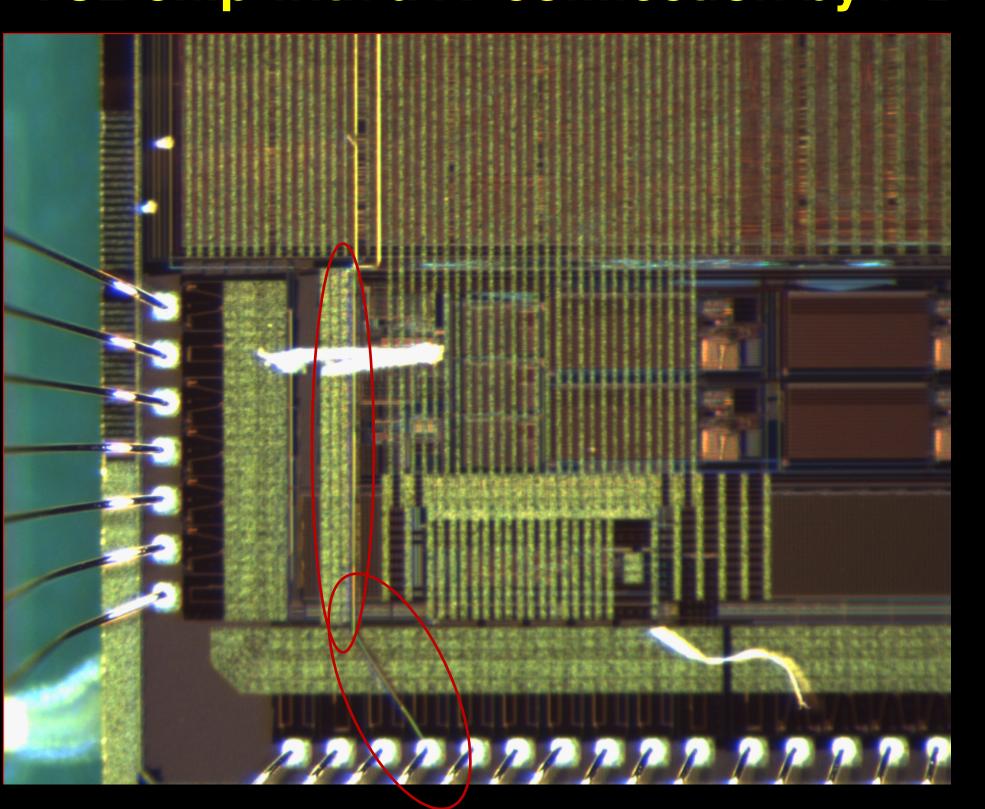

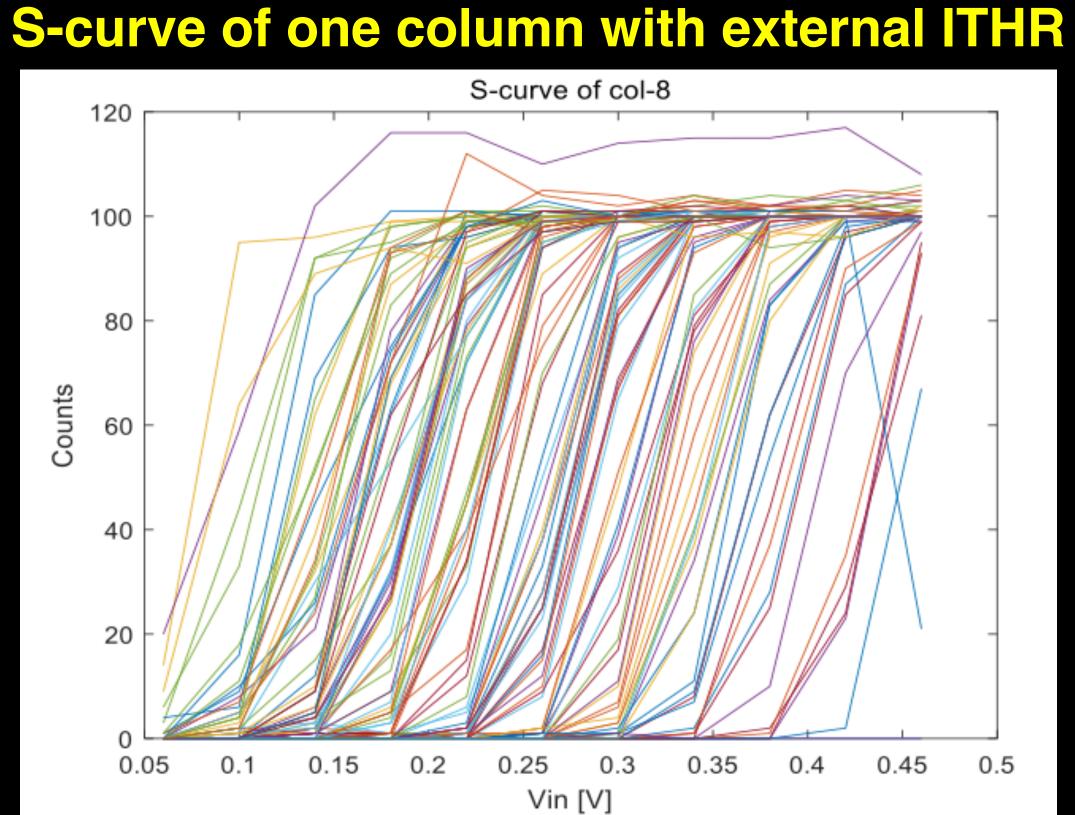

# Threshold tuning for TaichuPix2

- For TC2, threshold current ITHR can not be set less than 5.4 nA

- unexpected from design (nominal design value 4.5 nA). •

- Connected the internal ITHR to an IO-pad through FIB (Focused Ion beam) technology to provide an external ITHR voltage.

- Applying an external voltage @ Pad-A to tune the ITHR current

- ITHR can not as low as expected (min.  $\sim$ 7.8 nA). Need more investigation. TC2 chip with a Al connection by FIB

12

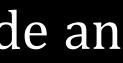

# DAC design in the full scale chip TC3

- Original design suffers from the leakage current and the output range is too large

- LSB: 0.1nA •

- Aiming at: 2~4nA

- Modified design tuned the output range specifically for small current:

- Range: 0~8nA •

DAC was also modified by adding a optional 6-bit current DAC for the low current biasing

# Simulations on DAC of Taichu3

- TC2 includes two current DACs to provide ITHR

- One 8-bit DAC same as in TC2

- An optional 6-bit DAC (design LSB of 0.1nA, range of 0-8 nA)

- Simulation results indicate the parasitic resistance increases the DAC output current, and the understood well.

| Name      | Input<br>code | Output with<br>Simu-sch. | Output with<br>Parasitic R<br>@extraction<br>rule 1 | Output with<br>Parasitic R<br>@extraction<br>rule 2 |

|-----------|---------------|--------------------------|-----------------------------------------------------|-----------------------------------------------------|

| IBIAS     | 1011          | 463.9 nA                 | 551.2 nA                                            | 481.8 nA                                            |

| ITHR_8bit | 101100        | 4.7 nA                   | 9.3 nA                                              | 5.5 nA                                              |

| ITHR_6bit | 100011        | 4.5 nA                   | 7.5 nA                                              |                                                     |

| IDB       | 11000         | 1.02 uA                  | 1.12 uA                                             | 1.05 uA                                             |

parasitic extraction rule effects the value of R and then the simulation result. Have not been

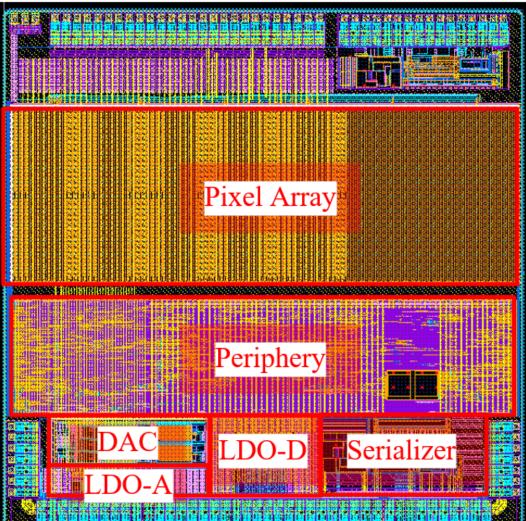

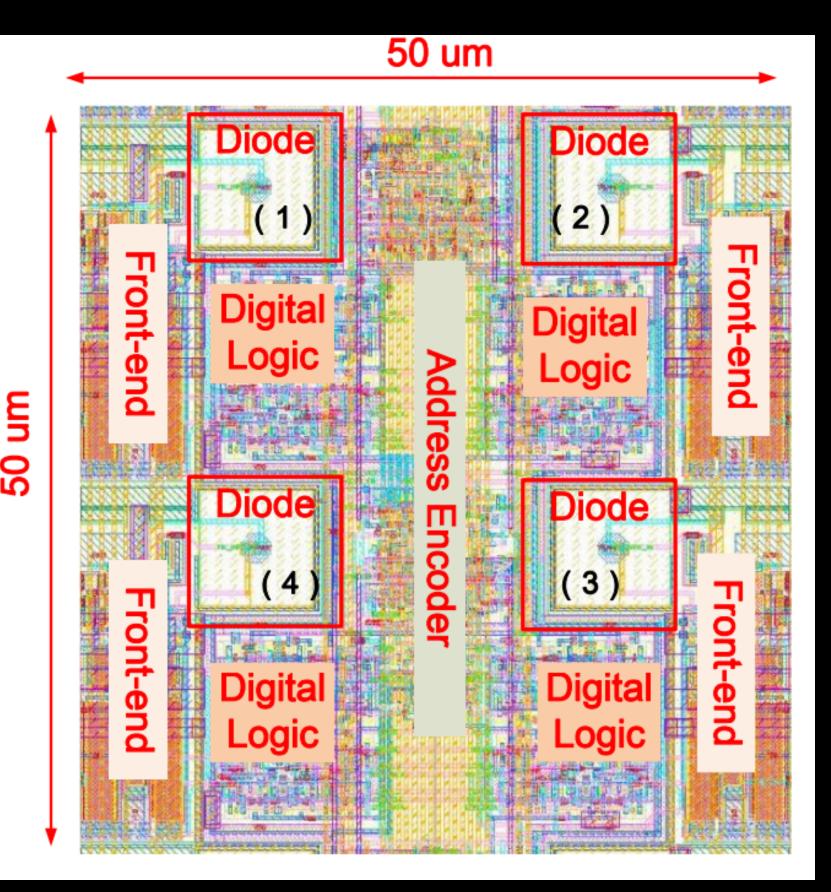

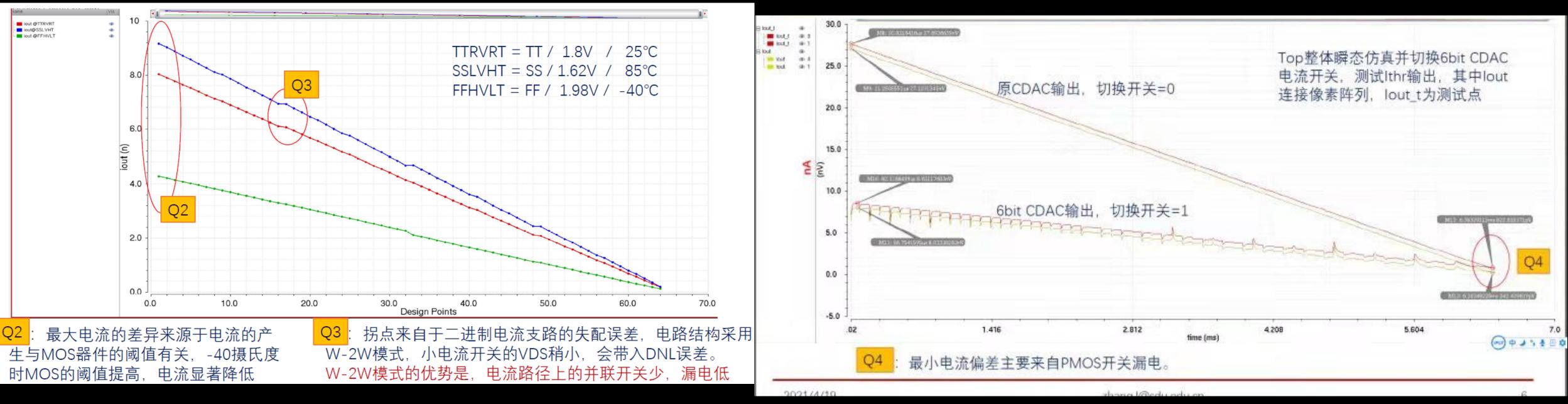

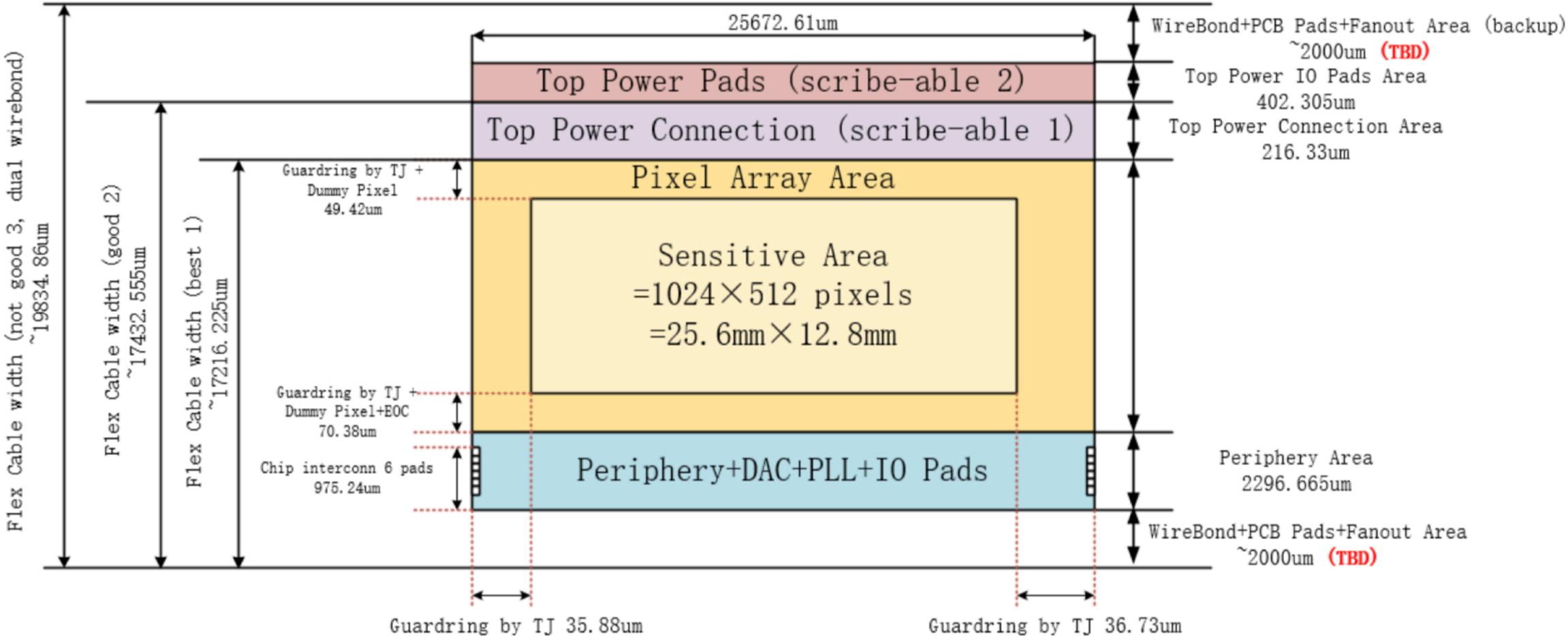

### Full-size TaichuPix3 design (engineering run) Full-size Taichu pixel design ready, passed review, ready for submission **1024×512** Pixel array (25μm×25μm pixel size), Process: Towerjazz 180nm ulletFE-I3 like Periphery digital readout, high speed data interface ightarrow

- - - Time stamp precision: 25ns-50ns

| Pixel | array |

|-------|-------|

| 1024* | 512   |

- Periphery

- DAC & Bias generation

- Data interface

- LDO (test blocks)

- Chip interconnection features

- Scribe-able top

features

- Process improved for better power supply: 6 Metals to 7M with 1 Thick Top

- Will help for the full size chip power integrity  $\succ$

- 25 µm×25 µm pixel, unique design (S1)

- A 1024×512 Pixel array

### **Periphery logics**

- Unique design for FE-I3 like readout

- High speed data interface

- Optimized for trigger mode and low power: optional low power LVDS port added

- **On-chip bias generation**

- Bugs detected & solved from the Tcpx2 test

- IO placement in the final ladder manner

- chip interconnection bus features included for ladder

- LDO will be independently tested as a test block due to the remain issues

15

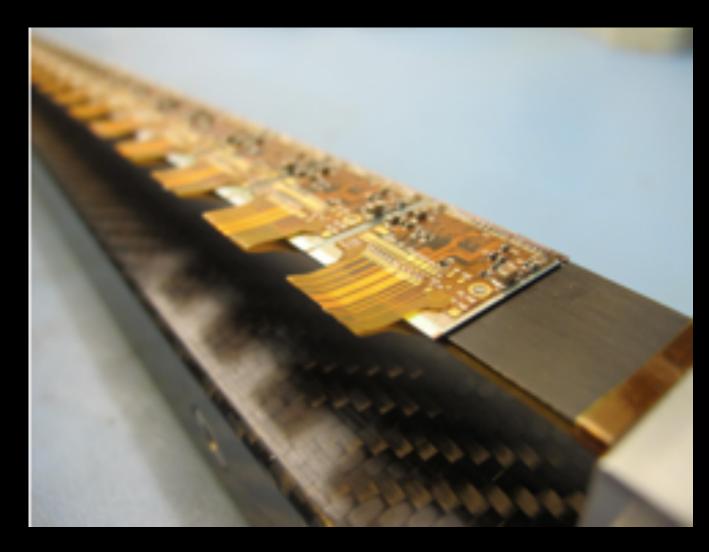

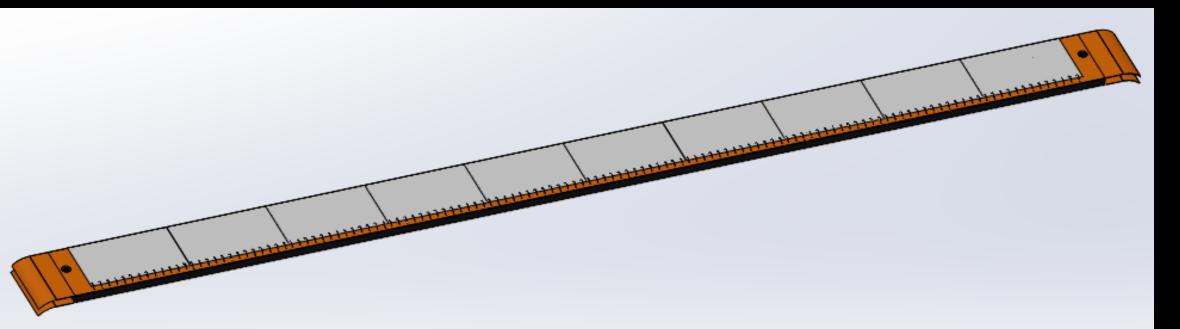

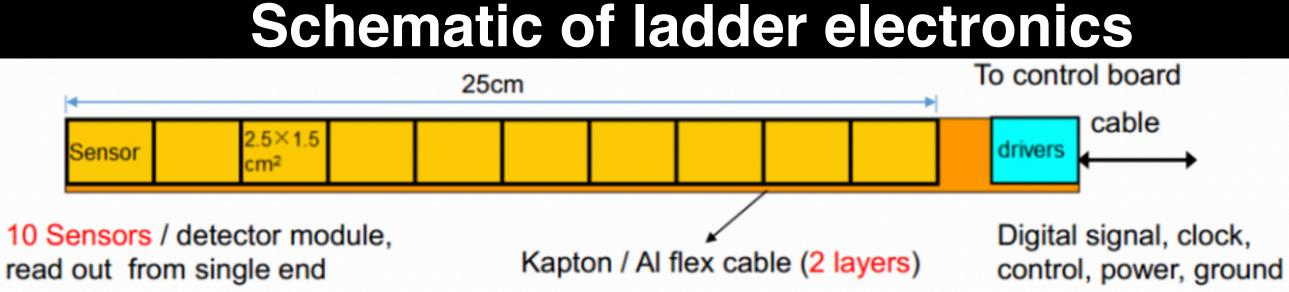

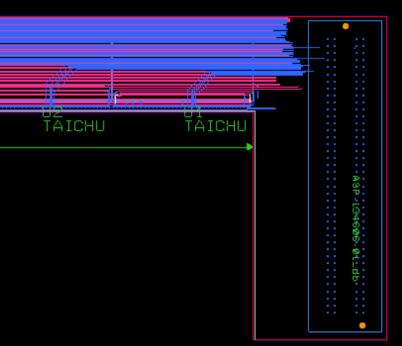

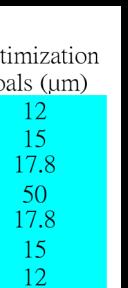

# Detector module (ladder) R & D

- Completed preliminary version of detector module (ladder) design

- Detector module (ladder)= 10 sensors + support structure+ flexible PCB+ control board

- Sensors will be glued and wire bonded to the flexible PCB

- Flexible PCB will be supported by carbon fiber support structure

- Signal, clock, control, power, ground will be handled by control board through flexible PCB

### **3D model of the ladder**

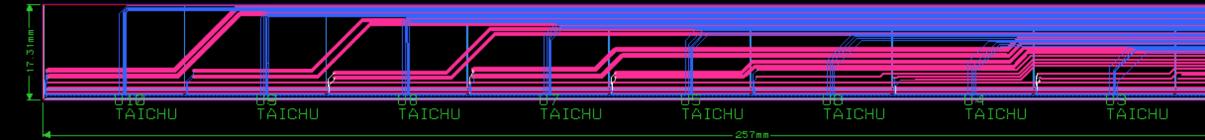

### **Design of Flexible PCB prototype**

- Double side flex + rigid PCB for 10 chips(15.31 X 25.6mm)

- 17.31mm X 257mm for flex part.

- Copper thickness: 0.5oz (18um)

- Signal width: 3mil/3mil, power supply width:20~60mil

## **Profile of flexible PCB**

|            | Achieved       | Opti |

|------------|----------------|------|

|            | Thickness (µm) | goa  |

| Polyimide  | 25             |      |

| Adhesive   | 28             |      |

| Plating Cu | 17.8           |      |

| kapton     | 50             |      |

| Plating Cu | 17.8           |      |

| Adhesive   | 28             |      |

| Polyimide  | 25             |      |

|            |                |      |

16

# New idea in Taichu pixel design – inter-chip connection

- Inter-chip connection for slow controls through wire bonding

- → Save some metal for PCB (reduce material budget)

ough wire bonding rial budget)

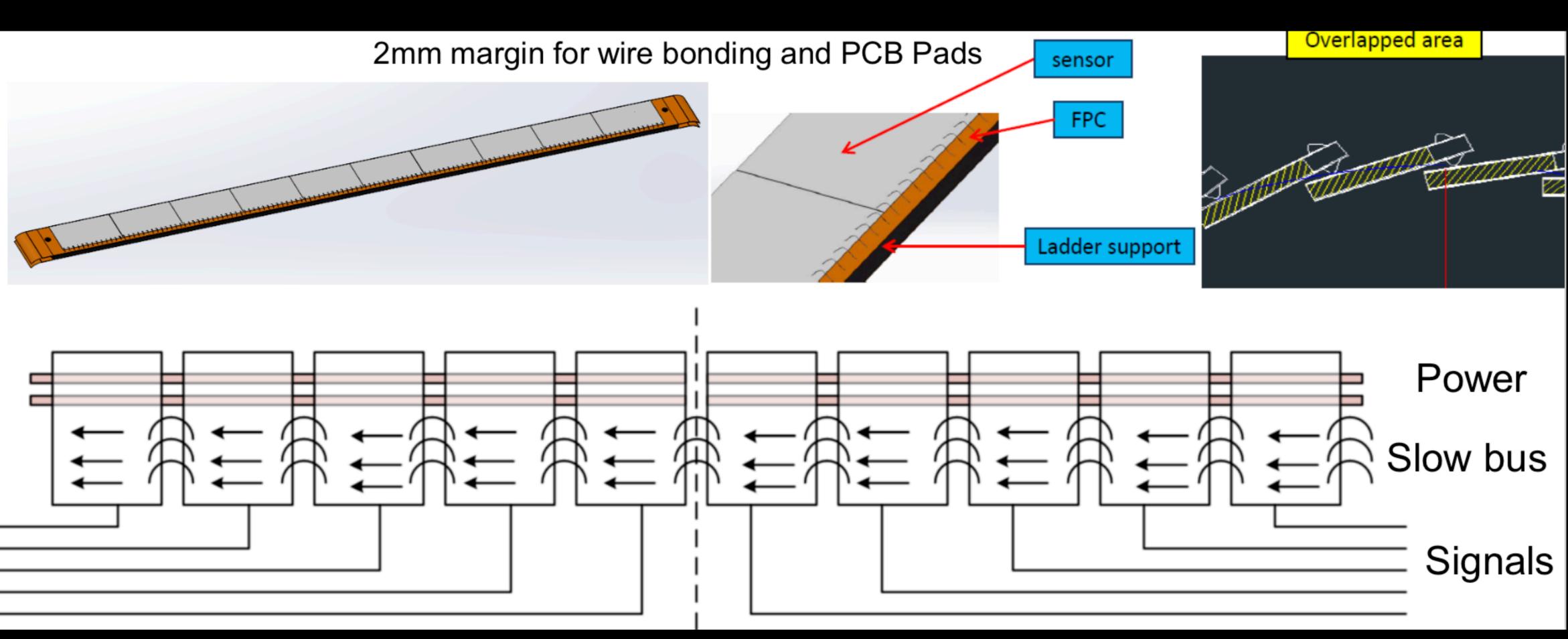

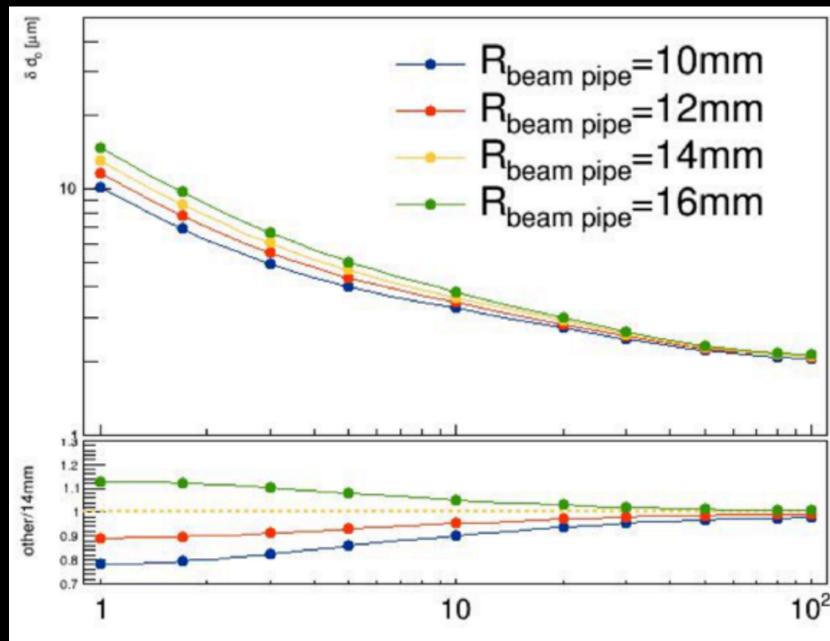

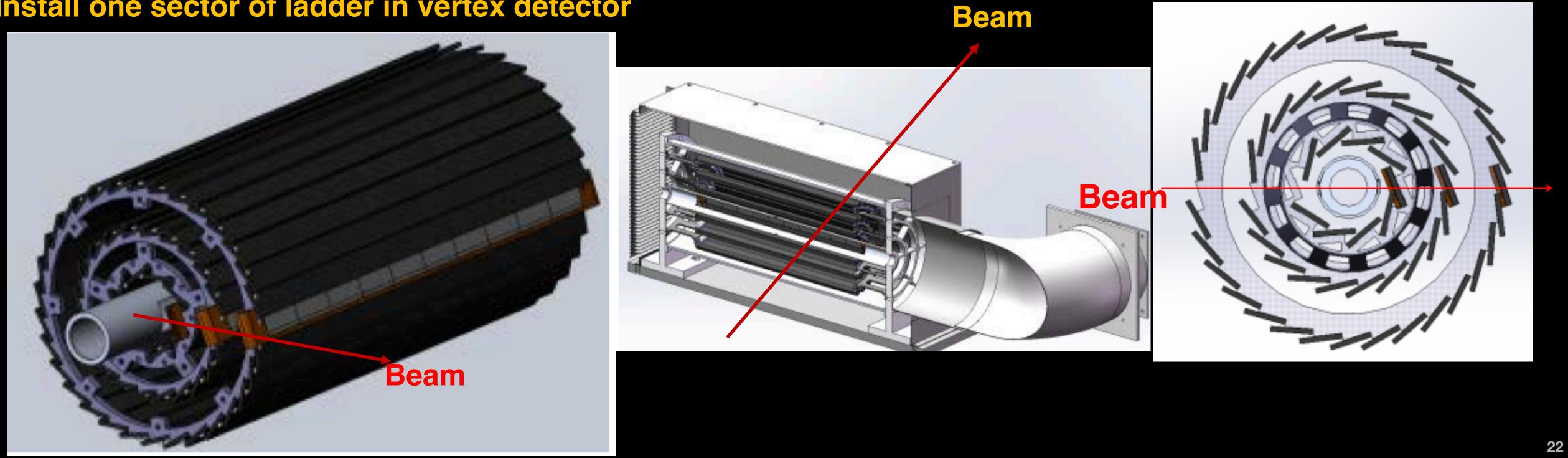

## Vertex Detector Prototype R & D Completed preliminary version of detector engineering design

- - 3 double layer barrel design

- 7 modules in inner layer, 22 modules in 2<sup>nd</sup> layer, 32 modules in outer layer

- Physics simulation to optimize vertex detector layout design.

- The length of inner layer pixel should be the same as other two layers

- Inner pixel radium should be as close to beam pipe as possible •

## Impact parameter resolution Vs beam pipe radius

18

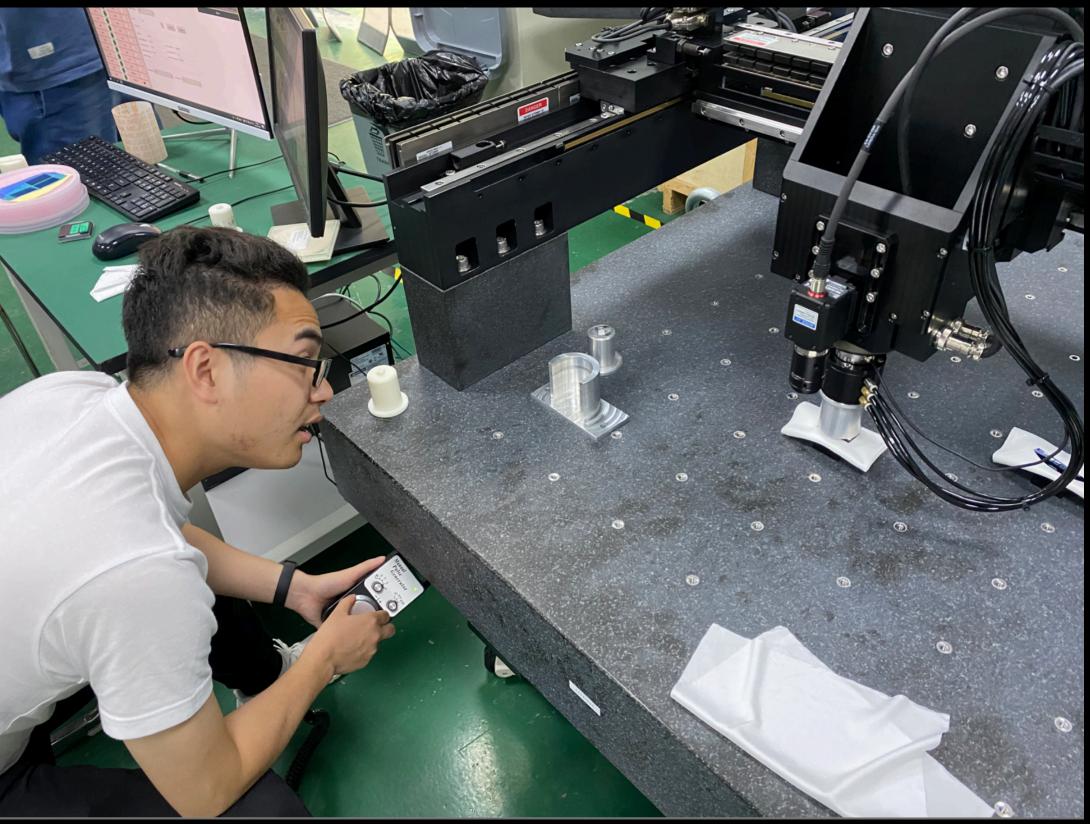

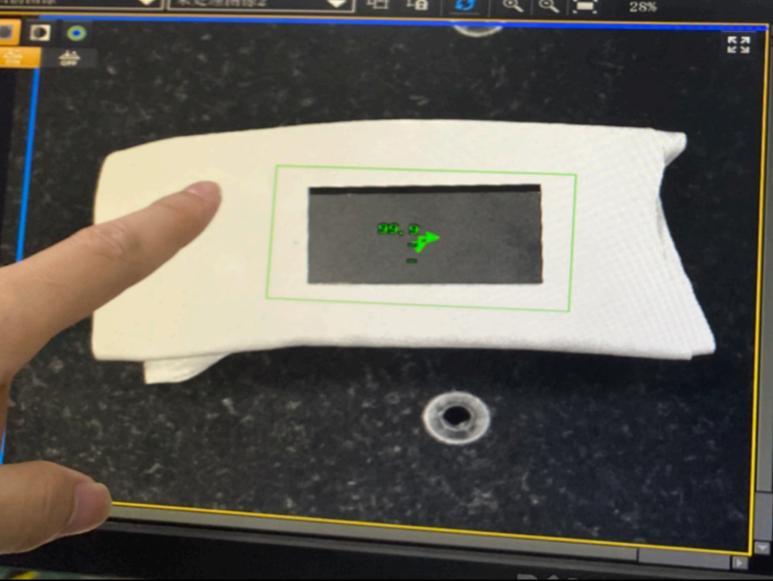

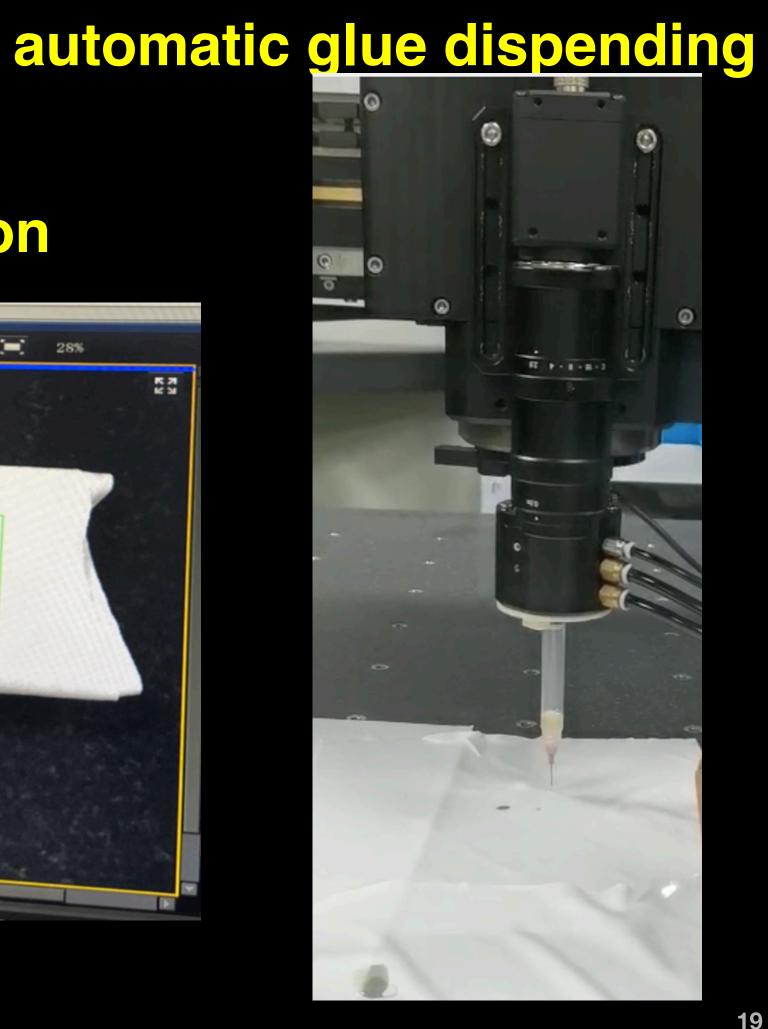

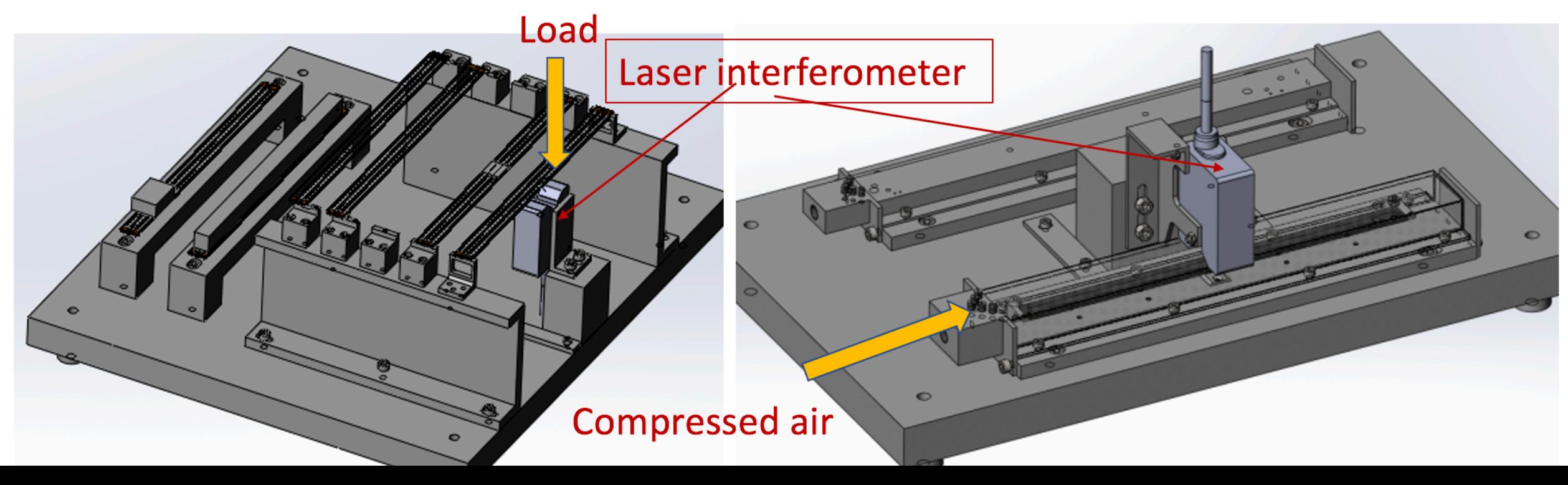

## Gantry for vertex detector prototype assembly 3~5um good position resolution require high assembly precision Cooperate with domestic company on R & D Gantry automatic module assembly. Pattern recognition with high resolution camera

- •

- Automatic chip pick-up and positioning •

- Automatic Glue dispending •

## Gantry system

# **Pattern recognition** 〒日日 🥴 🭳 🔍 28% ▼ 未处理图像: 2 3

# Tooling Design for Barrels Assembling

- 3 sets of tooling for 3 layer of barrel assembling.

- Tooling and special tool for inner and middle barrels assembling.

## bling. lle barrels assembling.

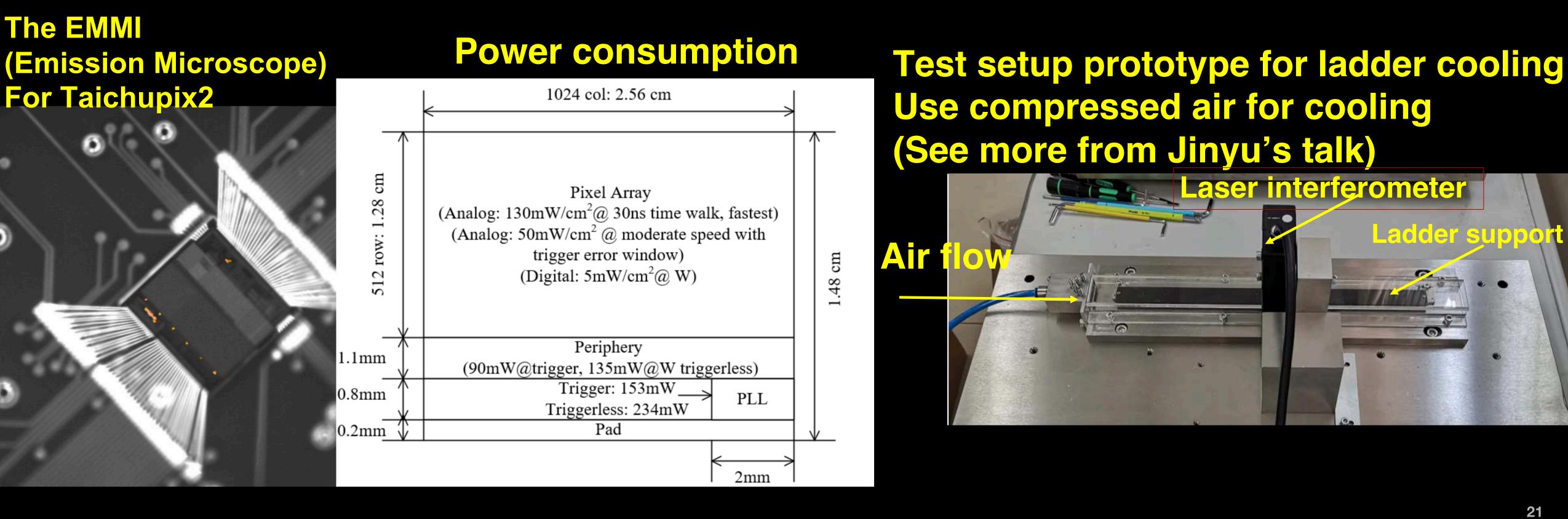

# Cooling design

- Air cooling is baseline design for CEPC vertex detector

- Sensor Power dissipation:

- Taichupix :  $\leq 100 \text{ mW/cm}^2$ . (trigger mode) ; CEPC final goal :  $\leq 50 \text{ mW/cm}^2$

- Cooling simulations of a single complete ladder with detailed FPC were done. •

- Testbench setup has been designed and built for air cooling, vibration tests

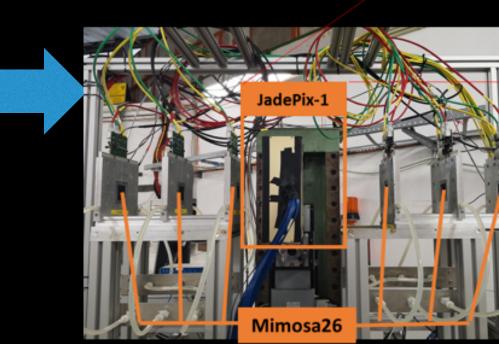

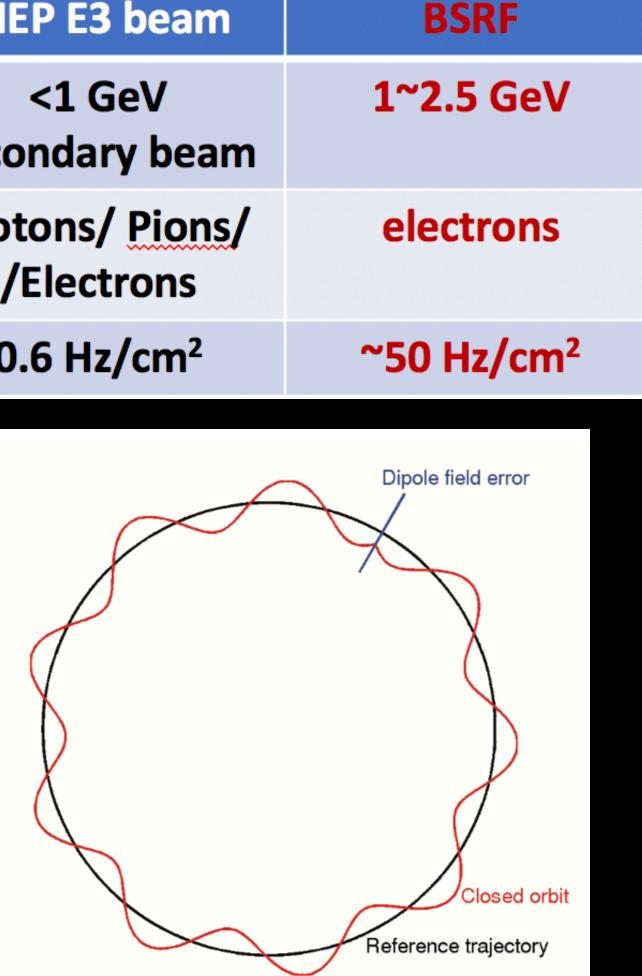

# Plan for test beam

- Expect to perform beam test in DESY(3 7GeV electron beams)

- IHEP test beam facility as backup plan (a few hundreds MeV 2.5GeV electrons)

- Enclosure for detector with air cooling is developed for beam test

- Beam is shooting at one sectors of vertex detectors  $\bullet$

### Install one sector of ladder in vertex detector

Plan for test beam (2)

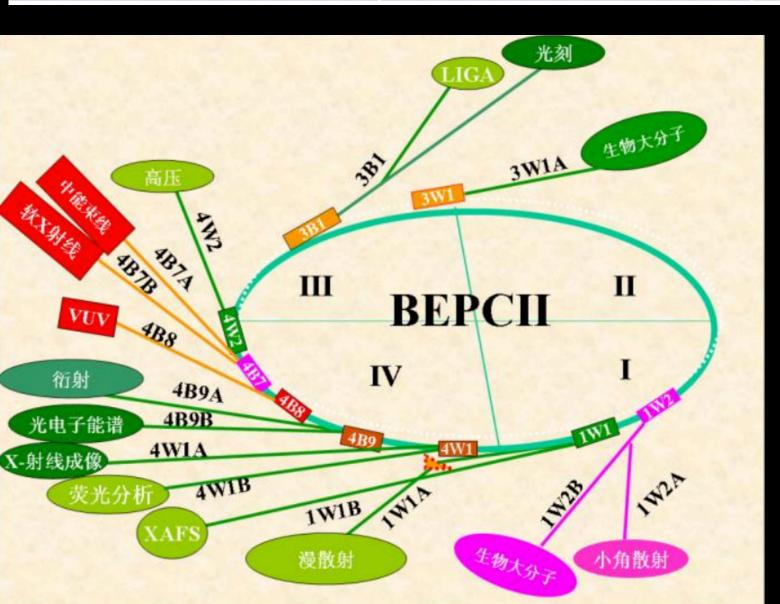

New opportunity in Beijing Synchrotron Radiation Facility (BSRF)

- High energy electron (0.2~2.5 GeV) leakage from BEPC •

- High trigger rate (up to 50Hz/cm<sup>2</sup>)

- Need to filter low energy particles for vertex test beam

|              | DESY                    | IHEP E3 beam                          |   |

|--------------|-------------------------|---------------------------------------|---|

| Momentum     | 1-6 GeV                 | <1 GeV<br>secondary beam              |   |

| Particles    | electrons               | Protons/ <u>Pions</u> /<br>/Electrons |   |

| Trigger rate | 4000 Hz/cm <sup>2</sup> | 0.6 Hz/cm <sup>2</sup>                | ^ |

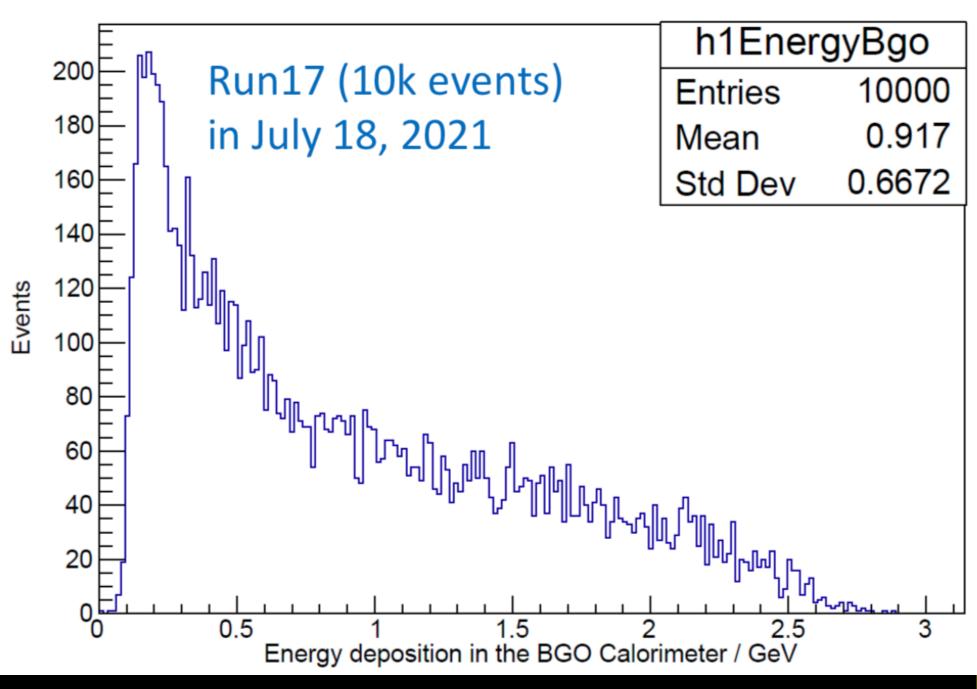

## **Energy spectrum measured** by calorimeter (by Yong Liu)

### Energy deposition in the BGO Calorimeter

# Summary

- Sensor:

- Completed two round of CMOS sensor prototyping, finalized full-size sensor design

- New readout architecture to reduce pixel size to  $25 \mu m^* 24 \mu m$

- → Reach midterm Assessment index (实现中期指标)

- First irradiation test up to 30 Mrad >1Mrad total ionization dose radiation

- Mechanics:

- Build the support structure prototype for ladder prototype

- Finalize the design for full vertex detector

|                    | Mid-term                      | Final goal                      | Status                                                |

|--------------------|-------------------------------|---------------------------------|-------------------------------------------------------|

| Spatial resolution | Pixel size less than 25*25 µm | Spatial<br>resolution<br>3~5 µm | Reach mid-term goal                                   |

| Radiation hardness | > 1MRad in simulation         | >1MRad<br>In radiation test     | First test up to 30 Mrad.<br>Chip is still functional |

yping, finalized full-size sensor design e to 25µm\*24µm

## Outlook for the next year

- Competed R & D large area sensor

- Manufactured the support structure for whole detector

- Assembling and installing the detector prototype

- Completed DAQ system for whole detector

| 2021<br>年<br>7月<br> <br>2022<br>年<br>6月 | 第四年年初进行大面积、全功能传感<br>器芯片的工程批硅晶圆加工,并在加<br>工完成后工程批芯片对进行全面的测<br>试;<br>加工探测器原型机的整机支撑结构;<br>开始组装装探测器原型机;研发与调<br>试原型机整机的数据获取系统。 | <ol> <li>完成探测器原型机<br/>整机支撑结构的设计<br/>报告,并年底前研制出<br/>探测器原型机的整机<br/>结构。</li> <li>完成全功能的传感<br/>器芯片的测试,完成测<br/>试报告。</li> </ol> | 课题年度报告<br>国际会议报告 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|

|                                         |                                                                                                                          | 3.研发出探测器原型<br>机整机的数据获取系<br>统。                                                                                             |                  |

## e detector ype

## Outlook for the next year

- Competed R & D large area sensor

- Manufactured the support structure for whole detector

- Assembling and installing the detector prototype

- Completed DAQ system for whole detector

| 2021<br>年<br>7月<br> <br>2022<br>年<br>6月 | 第四年年初进行大面积、全功能传感<br>器芯片的工程批硅晶圆加工,并在加<br>工完成后工程批芯片对进行全面的测<br>试;<br>加工探测器原型机的整机支撑结构;<br>开始组装装探测器原型机;研发与调<br>试原型机整机的数据获取系统。 | <ol> <li>完成探测器原型机<br/>整机支撑结构的设计<br/>报告,并年底前研制出<br/>探测器原型机的整机<br/>结构。</li> <li>完成全功能的传感<br/>器芯片的测试,完成测<br/>试报告。</li> </ol> | 课题年度报告<br>国际会议报告 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|

|                                         |                                                                                                                          | 3.研发出探测器原型<br>机整机的数据获取系<br>统。                                                                                             |                  |

## e detector ype

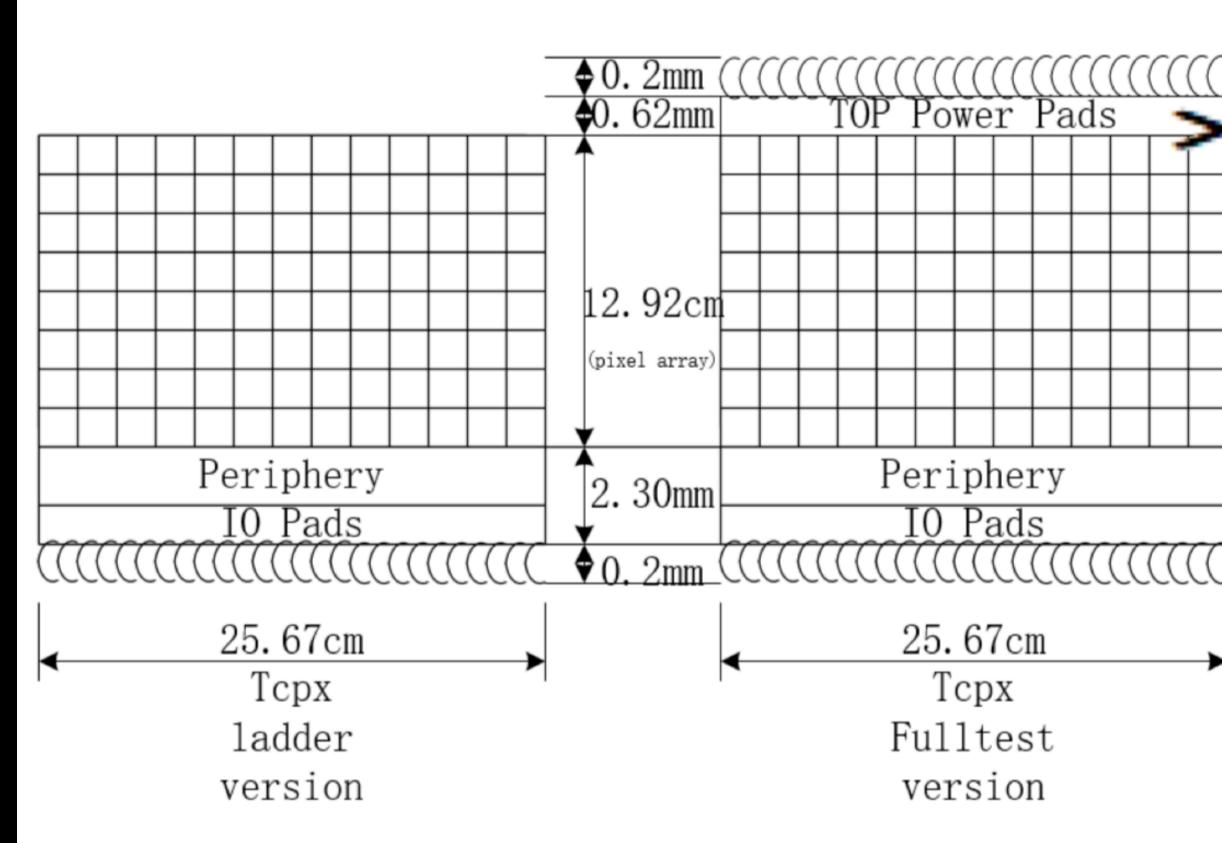

# Backup : Preparation for the full size engineering run

Signal pads/routing on ladders were kept minimum with 9/8 wires, other common bus were routed by chip interconnection features

## Two versions possibilities were kept within one tapeout

- Fulltest version keeps all test pads features for the chip study before ladder assembly

- Top power pads & top power bus connections will help for the full chip power integrity, concerning Tcpx is aiming for fast readout with high power

- Tcpx final ladder version

- If top power bus not necessary, stays in minimum dead zone

- If top power bus needed for less IR drop, + 200um dead zone on the top but with a good chip

- If all needed, we learned by test thanks to the full test features

# Backup : Preparation for the full size engineering run

Guardring by TJ 35.88um

## Backup: International collaboration

- **IFAE(Spain)**: very active in CMOS Sensor design and testing

- Liverpool (UK): Tracker mechanical design,

- Oxford(UK): CMOS sensor design validation, thermal design

- RAL(UK): Pixel module design

- Queen Mary(UK): module mechanical design (Zero mass concept)

- Strasbourg (FR): CMOS sensor design, Tracker mechanical design

- University of Massachusetts (US): Tracker mechanical design, thermal design

In 2019, we have one engineer visited Oxford and Liverpool for 4 weeks, learned a lots about silicon.

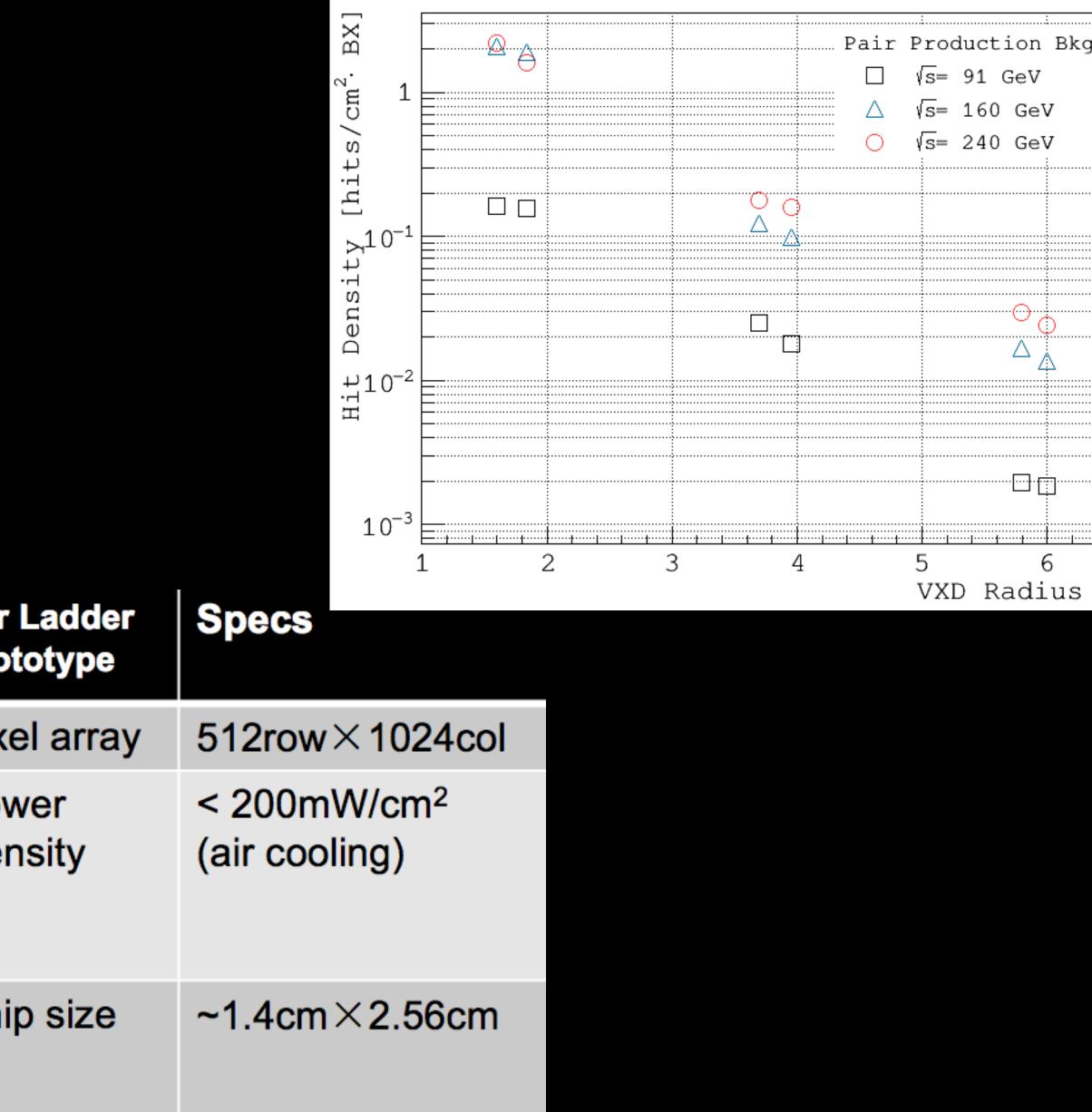

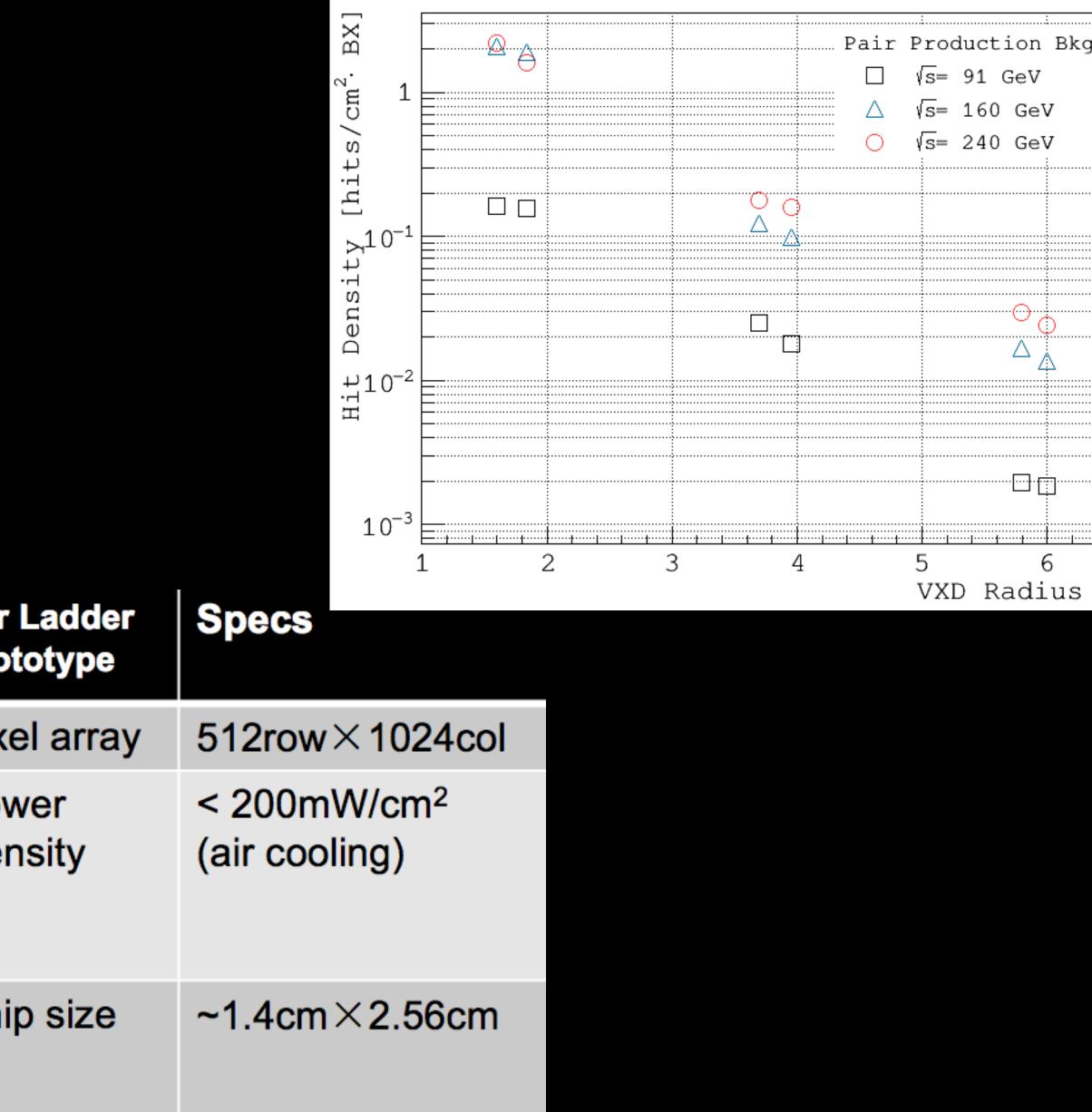

# Main specs of the full size chip for high rate vertex detector

- Bunch spacing

- CEPC Z+Higgs (240GeV): 680ns;

- WW threshold scan (160GeV): 210ns;

- CEPC Z pole runing (90GeV) Z: 25ns

- High Hit density

- 2.5hits/bunch/cm<sup>2</sup> for Higgs/WW runs

- 0.2hits/bunch/cm<sup>2</sup> for Z pole running

| For<br>Vertex | Specs  | For High rate<br>Vertex | Specs                                                 | For<br>Prot |

|---------------|--------|-------------------------|-------------------------------------------------------|-------------|

| Pixel pitch   | <25µm  | Hit rate                | 120MHz/chip                                           | Pixe        |

| TID           | >1Mrad | Date rate               | 3.84Gbps<br><u>triggerless</u><br>~110Mbps<br>trigger | Pov<br>Der  |

|               |        | Dead time               | <500ns<br>for 98%<br>efficiency                       | Chi         |

| • |   |   |   |   |   |   | • |   |   |   |   |   | • |   |   |   |   |   | • | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   | _ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| ] | ſ |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | : | : | : | : | : |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | : | : | : | : | : | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | : | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : |   |

| • | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | : | • |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   | : | ł | ŀ | : | : | : | : | : | ł | ŀ | : | : | : | : | : | : | ŀ | : | : |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

[cm]

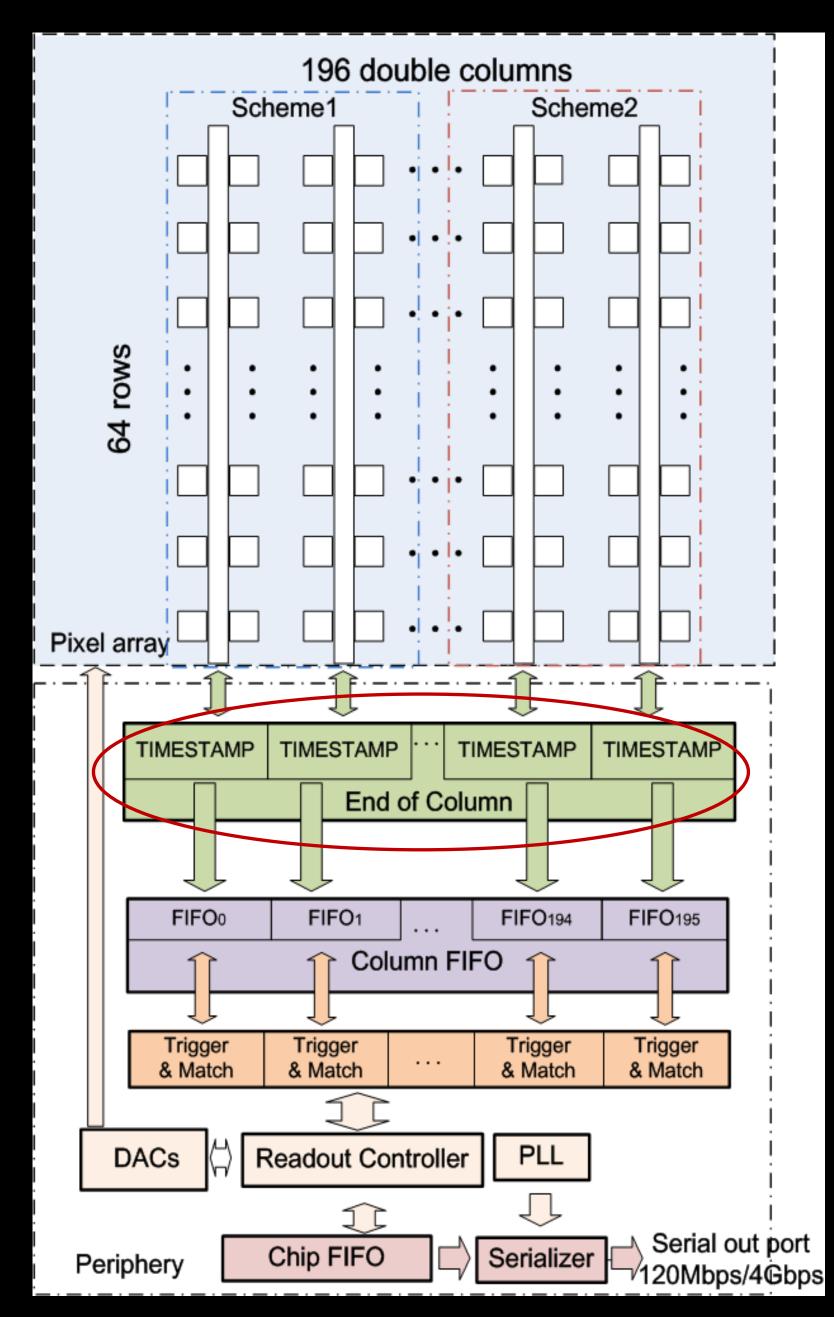

# New proposed readout architecture in TaichuPix

- New readout architecture ullet

- $\rightarrow$  reduce power consumption and reduce pixel size **CEPC** readout time requirement: <500ns deadtime @40MHZ(Z pole)

- ullet

- - Priority based data driven readout; time stamp at EOC Dead time: 2 CLK for each pixel (50ns @40MHz CLK)

- Two digital pixel designs: FEI3-like and ALPIDE-like design **2-level FIFO architecture**

- L1: column level, to de-randomize injecting charge

- L2: chip level, to match in/out data rate between core and interface

- Trigger readout:

- Coincidence by time stamp, matched event read out

## Taichu-1 Column-drain readout

31

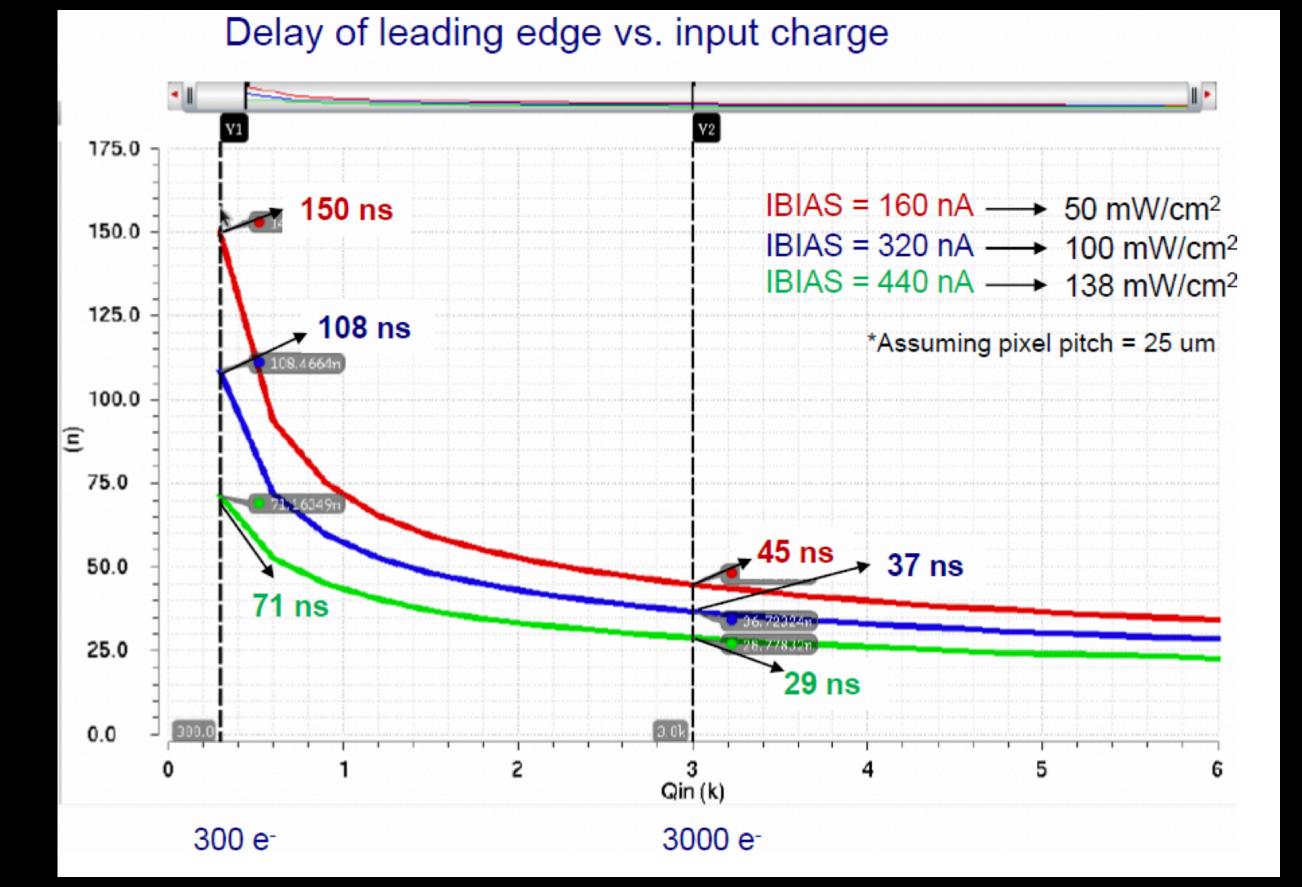

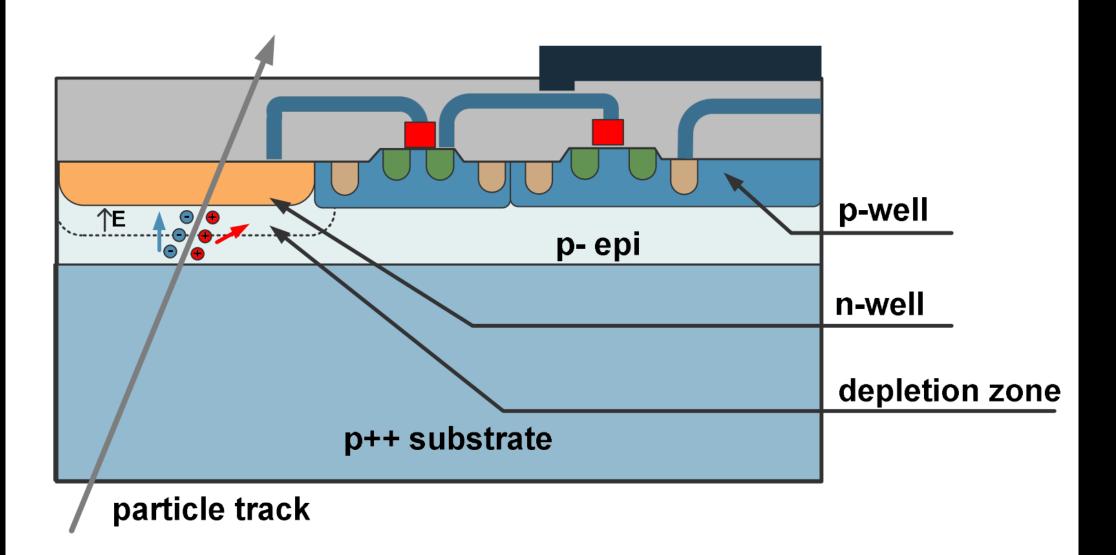

## Pixel Analog design

- **CEPC time stamping precision requirement:**

- 25-100ns, better to time stamping each collision at Z pole

- **Taichu-1 pixel analog design:**

- 50ns~150ns (based one standard CMOS MAPS tech.)

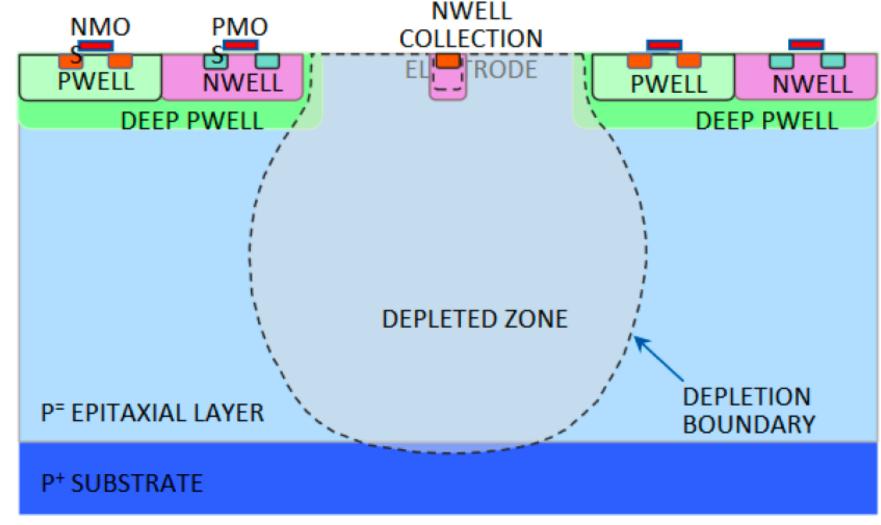

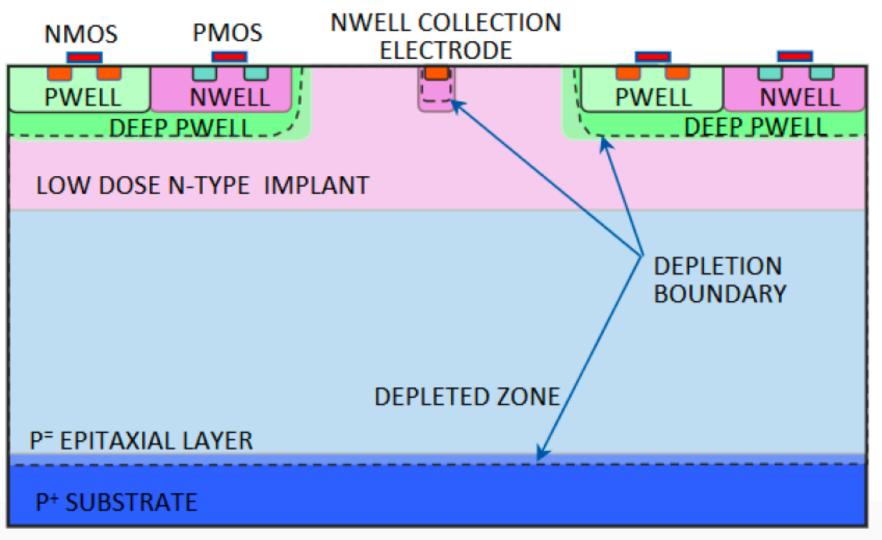

- **Consider to use depleted CMOS MAPS**  $\bullet$

### Standard : no full depletion

### Modified : full depletion, faster charge collection

# Backup: Ladder Mechanical testing

**Detailed designs of platform and tooling for different test.**

Static (different support and load cases)

>Vibration and cooling + pressed air (different cases): >Measure Deformation, temperature, air speed, flow rate, etc. Soal: Measure vibration to 1 µm level with air cooling with laser interferometer

Static mechanical test

### Vibration and cooling test

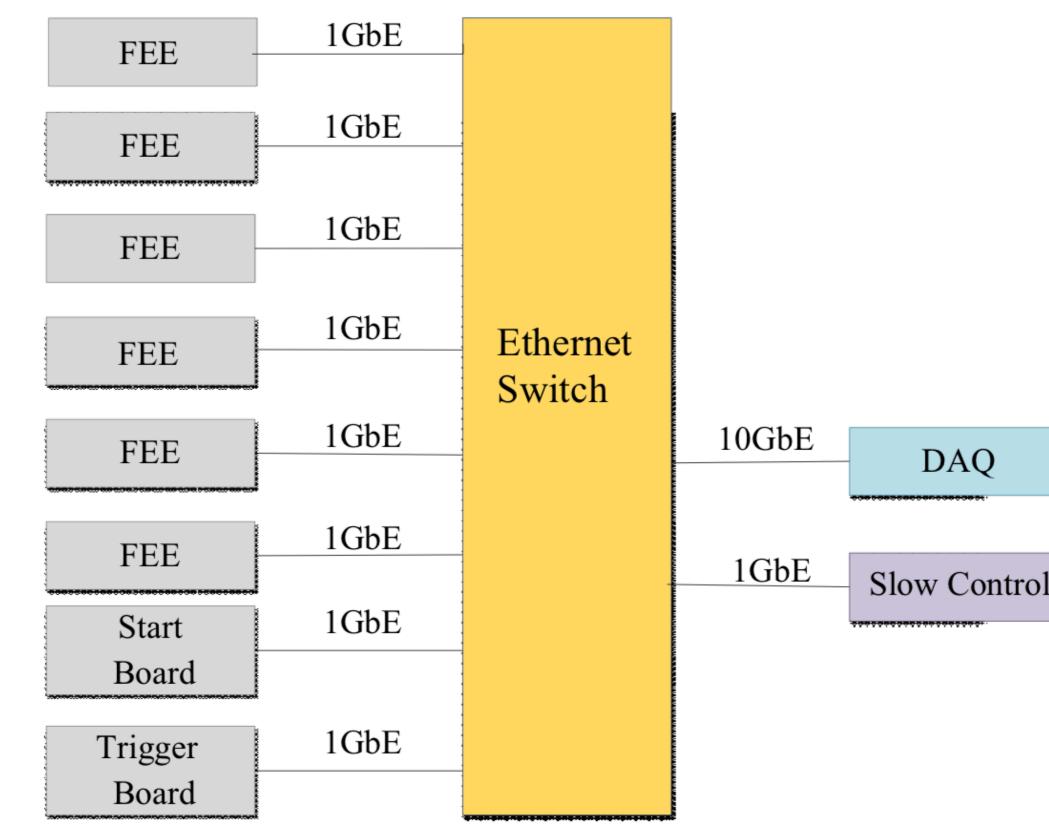

## Data acquisition system

- Preliminary design of data acquisition system(DAQ) •

- Ladders are reader by readout boards ullet

- All readout boards connected to computer through a switch ullet

- User interface developed ullet

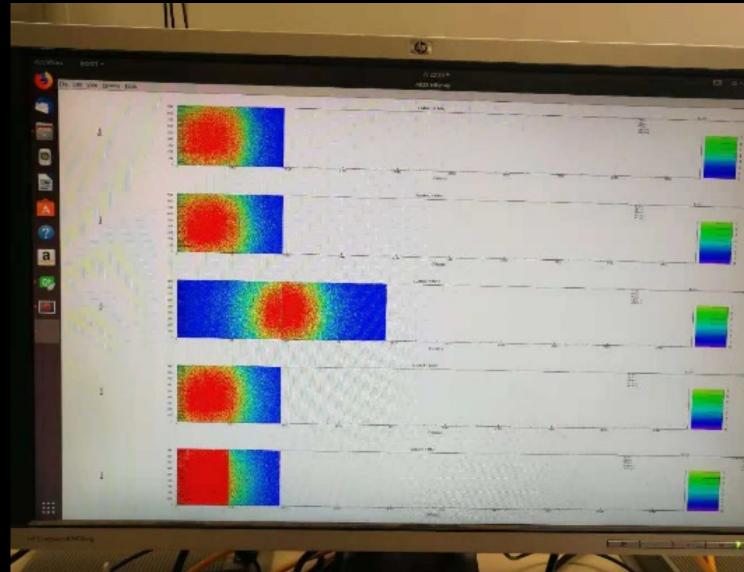

- DAQ tested in five modules equipped with MIMOSA sensors  $\bullet$

## **DAQ Tests with 5 MIMOSA chips**

### DAQ system data display **Tested with MIMOSA modules**

# Main specs of the full size chip for high rate vertex detector

- Bunch spacing

- CEPC Z+Higgs (240GeV): 680ns;

- WW threshold scan (160GeV): 210ns;

- CEPC Z pole runing (90GeV) Z: 25ns

- High Hit density

- 2.5hits/bunch/cm<sup>2</sup> for Higgs/WW runs

- 0.2hits/bunch/cm<sup>2</sup> for Z pole running

| For<br>Vertex | Specs  | For High rate<br>Vertex | Specs                                                 | For<br>Pro |

|---------------|--------|-------------------------|-------------------------------------------------------|------------|

| Pixel pitch   | <25µm  | Hit rate                | 120MHz/chip                                           | Pixe       |

| TID           | >1Mrad | Date rate               | 3.84Gbps<br><u>triggerless</u><br>~110Mbps<br>trigger | Pov<br>Der |

|               |        | Dead time               | <500ns<br>for 98%<br>efficiency                       | Chi        |

|   | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ | _ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   | ſ |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • |   |   | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | : | : | : | : | : | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | : | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | • | : | j |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   | : | : | : | : | : | : | : | - | : | : | : | : | : | : | : | : | : | : | : | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | : | • | • | • | • | • | j |

|   | : |   | : | : |   | : | : |   | : |   |   | : |   |   | : |   | : | : | : | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | : |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

| • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | J |

|   | • |   |   | • |   |   | • |   |   | Ĩ |   |   | Ĩ |   | • | Ĩ |   | • |   | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • | • | ; |   | • | • | • | • | • | 2 |   | • | • | • | • | • | • |   | : | • | j |

|   | • | 1 |   | • | • | • | • | • | 1 | • | • | • | • | • | • | • | 1 | • | • | 1 |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

[ Cm ]

# backup:

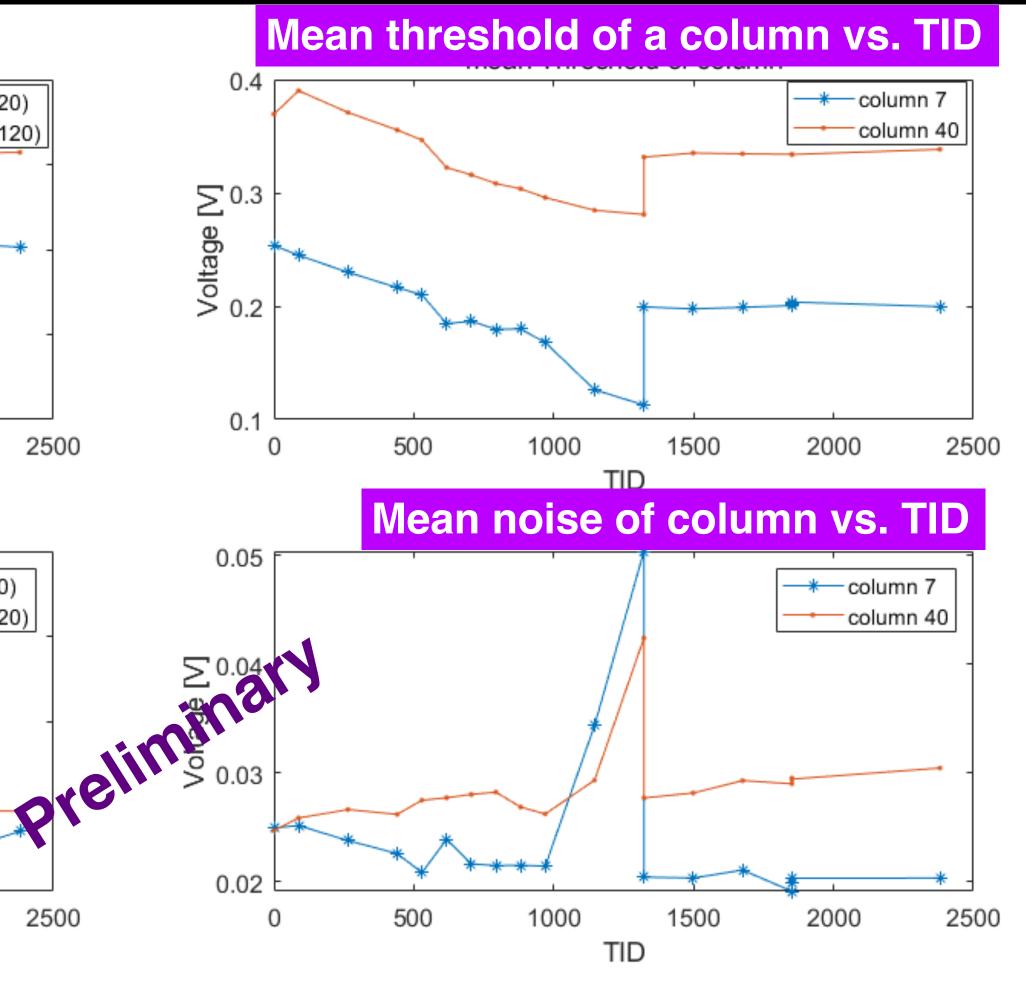

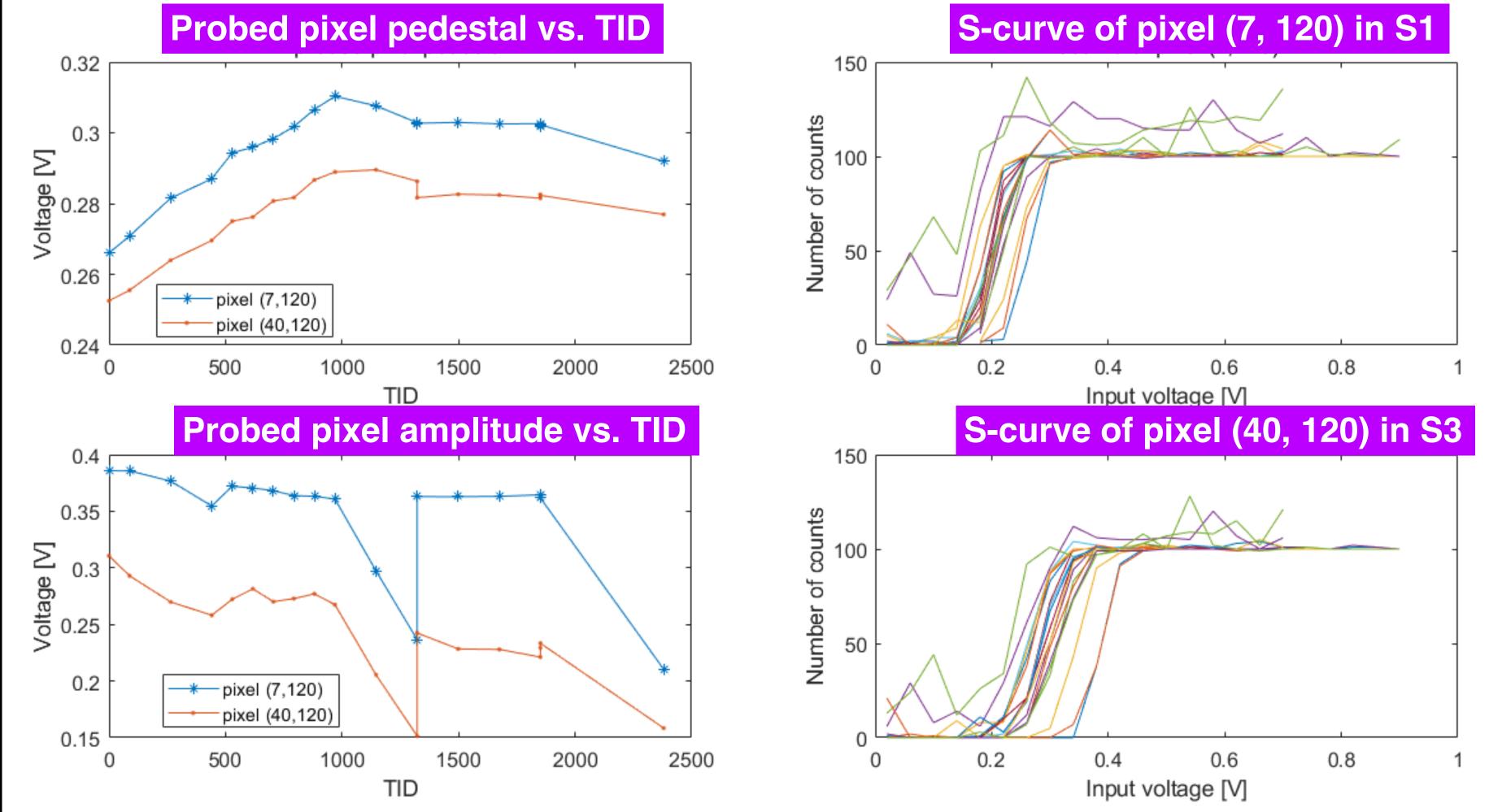

Good chip function and noise performance proved to 2.5 Mrad,

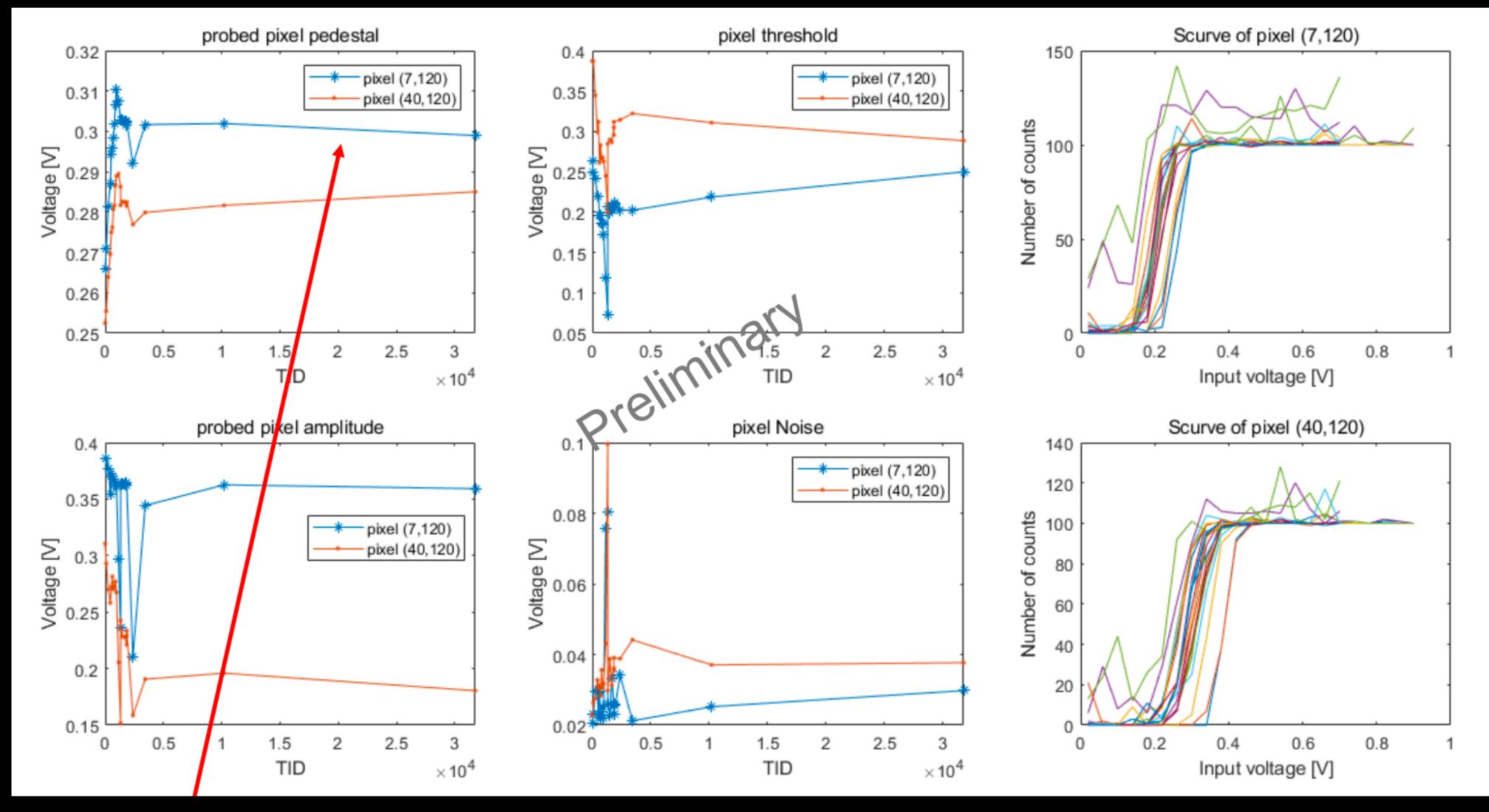

# Backup:

shifted to see noise floor in S-curves, so the threshold level was set higher.

The threshold was initially set at the minimum level. After ~1 Mrad, the pedestal level was

## Publications and International talks **Publication:**

#### International conference talks:

- $\bullet$

- Circuits and Systems, Nov. 27-29, 2019, Genova, Italy.

- imaging detectors, International workshop on radiation imaging detectors, July 2019, Crete, Greece

- 17, 2019, Oxford, UK

- Oxford, UK

#### High data-rate readout logic design of a $512 \times 1024$ pixel array dedicated for CEPC vertex detector

X. Wei,<sup>a,1</sup> W. Wei,<sup>b</sup> T. Wu,<sup>c,d</sup> Y. Zhang,<sup>b</sup> X. Li,<sup>b</sup> L. Zhang,<sup>e</sup> W. Lu,<sup>b</sup> Z. Liang,<sup>b</sup> J. Dong,<sup>e</sup> L. Li,<sup>e</sup> J. Wang,<sup>*a*</sup> R. Zheng,<sup>*a*</sup> R. Casanova,<sup>*d*</sup> S. Grinstein,<sup>*d*</sup> Y. Hu<sup>*f*</sup> and J. Guimaraes da Costa<sup>*b*</sup>

## JINST 14 (2019) C12012

### A full functional Monolithic Active Pixel Sensor prototype for the CEPC vertex detector

Tianya Wu<sup>1,2</sup>, Raimon Casanova<sup>2</sup>, Wei Wei<sup>3</sup>, Xiaomin Wei<sup>4</sup>, Ying Zhang<sup>3</sup>, Liang Zhang<sup>5</sup>, Xiaoting Li<sup>3</sup>, Zhijun Liang<sup>3</sup>, Joao Guimaraes da Costa<sup>3</sup>, Weiguo Lu<sup>3</sup>, Jianing Dong<sup>5</sup>, Long Li<sup>5</sup>, Wang Jia<sup>4</sup>, Ran Zheng<sup>4</sup>, Ping Yang<sup>1</sup>, Guangming Huang<sup>1</sup> and Sebastian Grinstein<sup>2</sup>

**IEEE ICECS** (doi: 10.1109/ICECS46596.2019.8965105.)

Joao Guimaraes Da Costa, CepC phys/detectors, Workshop on the Circular Electron-Positron Collider, EU Edition, April 15 - 17, 2019, Oxford, UK T. Wu, A full functional Monolithic Active Pixel Sensor prototype for the CEPC vertex detector, in proceeding of International Conference on Electronics

Xiaomin Wei, High data-rate readout logic design for 1024\*512 CMOS pixel array dedicated for CEPC experiment, International workshop on radiation

Ying Zhang, Overview of the chip design for the MOST2 CEPC vertex project, Workshop on the Circular Electron-Positron Collider, EU Edition, April 15 -

Wei Wei, Full size pixel chip for high-rate CEPC Vertex Detector, Workshop on the Circular Electron-Positron Collider, EU Edition, April 15 - 17, 2019,

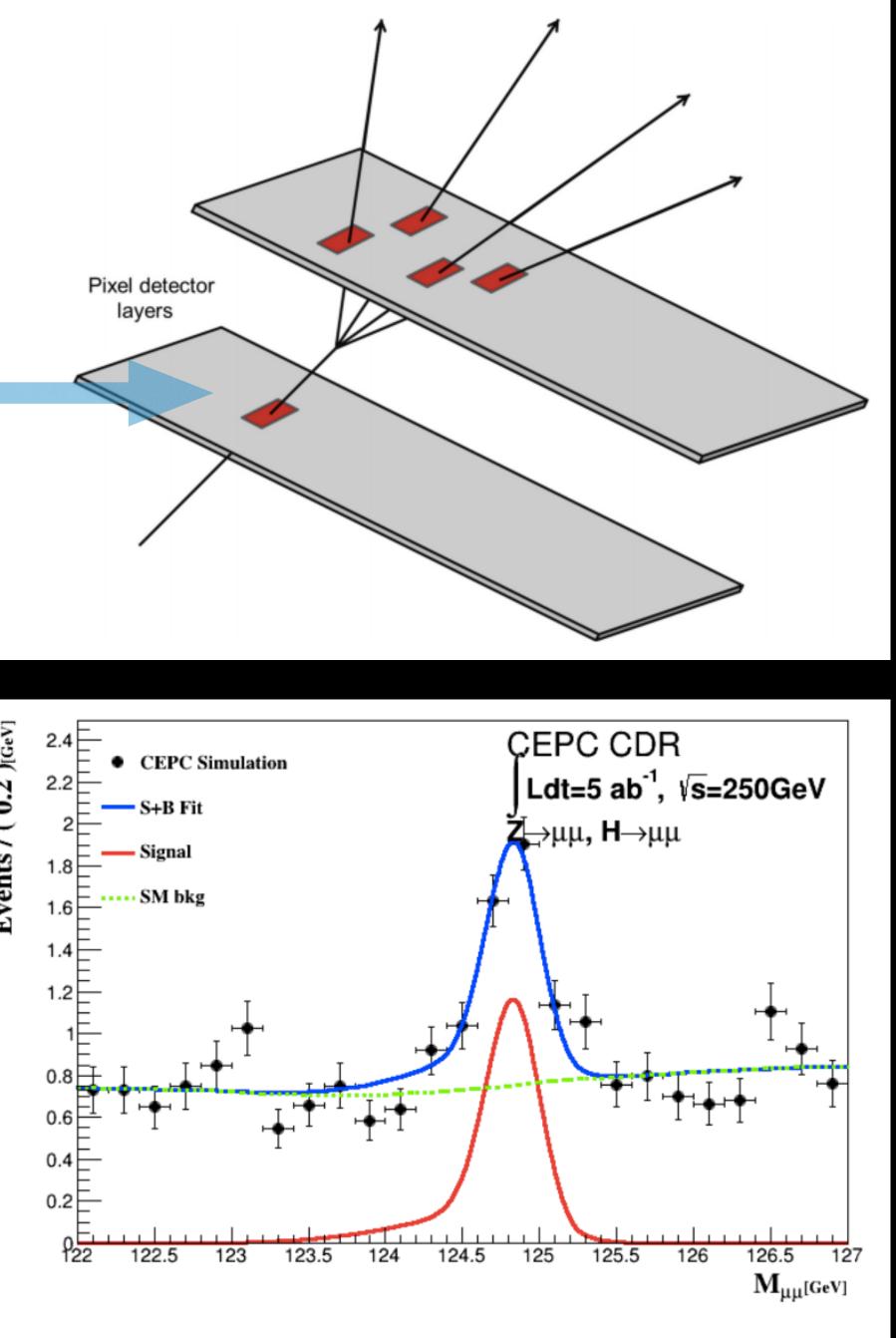

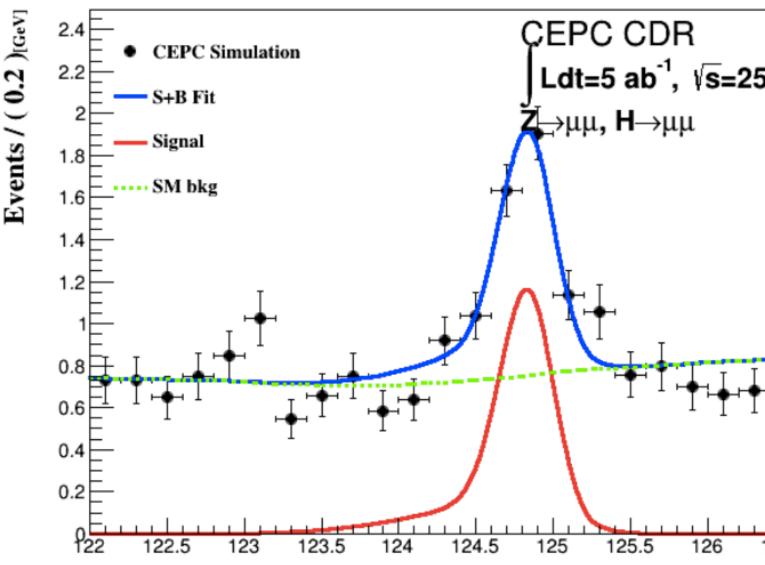

# Task 2: Physics goal

- Higgs precision measurement

- $H \rightarrow bb$  precise vertex reconstruction ullet

- $H \rightarrow \mu \mu$  (precise momentum measurement) ullet

## Need tracking detector with high spatial resolution, low material

### Main technology

- High spatial resolution technology  $\rightarrow$  pixel detector ullet

- Low-mass detector technology ullet

- Radiation resistance technology ullet

## Goal for the third year (2020.7 - 2021.6)• Achieve the target in task book for the 3<sup>rd</sup> years

- Build the support structure prototype for ladder ullet

- Finalize the full-size sensor design , and write a design report ullet

- Complete the testing of 2<sup>nd</sup> MPW Taichu chip, write a testing report

- Complete initial design of readout electronics and DAQ for vertex detector prototype

| 2020<br>年<br>7月<br> <br>2021 | 加工并完成探测器模块单元的结构样<br>品;对第二次 MPW 流片的芯片做全面<br>的测试(包括大剂量的辐照测试)以<br>验证其功能性。根据测试结果,优化<br>外围数字电路设计,并修正像素内前<br>端故太器电路 | <ol> <li>研制出探测器单元<br/>模块的结构样品。</li> <li>完成全功能的传感<br/>器芯片的设计,并完成<br/>设计报告。</li> </ol>           | 课题年度报告 |

|------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|

| 2021<br>年<br>6月              | 端放大器电路,优化抗辐照电路器件<br>的设计,并整合芯片各模块功能的设<br>计,并提交第三次多项目晶圆(MPW)<br>流片加工,加工后进行快速验证性的<br>测试;设计大面积、全功能的传感器            | <ul> <li>3.完成第二次的 MPW 流<br/>片后芯片的测试,完成<br/>测试报告。</li> <li>4. 完成探测器原型机<br/>整机的读出电子学与</li> </ul> |        |

|                              | 芯片,为大批量的工程批流片做好准备;初步设计探测器原型机整机系统<br>读出电子学的数据获取系统。                                                             | 並1100000000000000000000000000000000000                                                         |        |

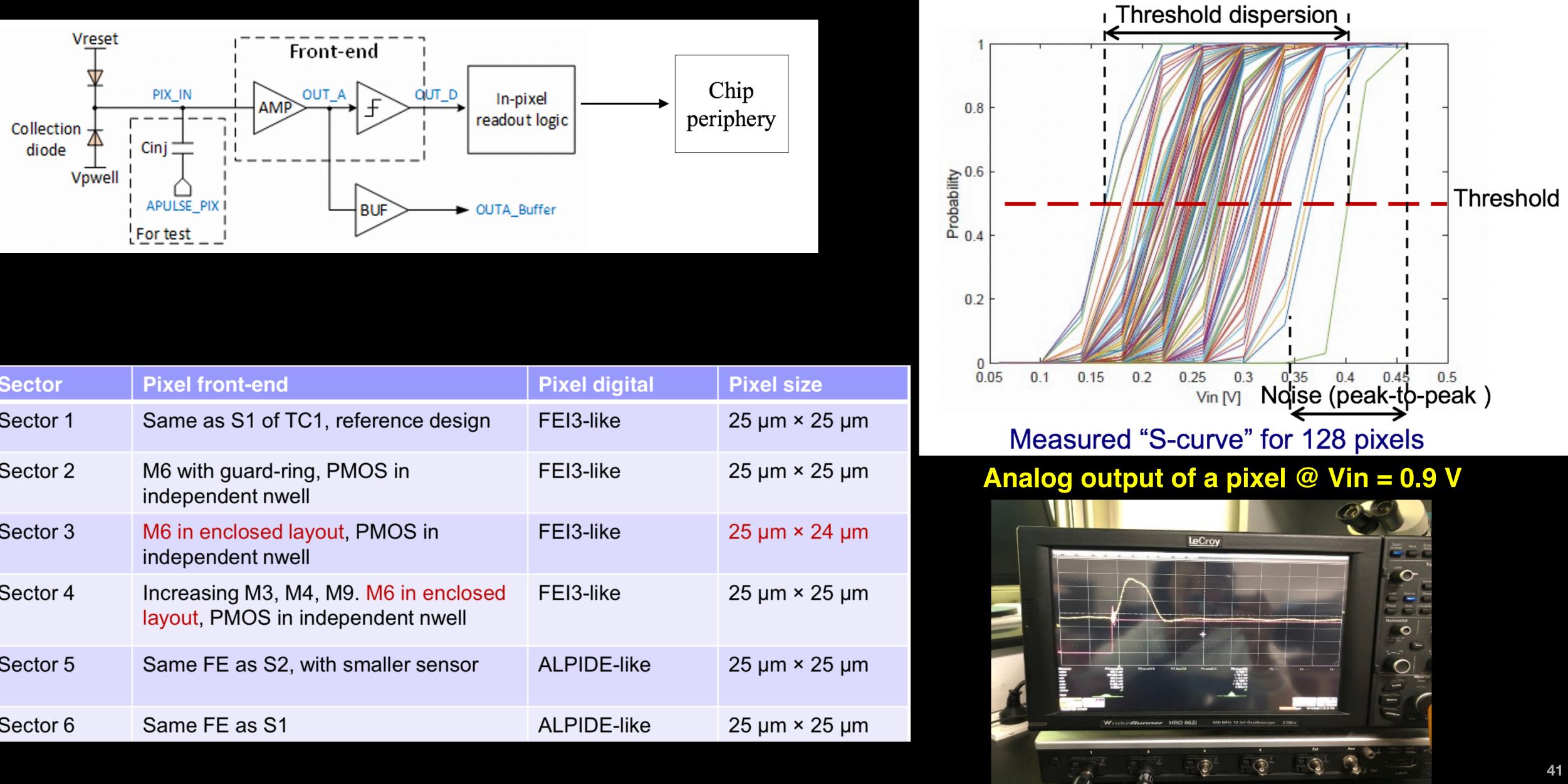

## Electrical test Electrical performance verified by injecting an external charge into pixel front-end

| Sector   | Pixel front-end                                                         | Pixel digital | F |

|----------|-------------------------------------------------------------------------|---------------|---|

| Sector 1 | Same as S1 of TC1, reference design                                     | FEI3-like     | 2 |

| Sector 2 | M6 with guard-ring, PMOS in<br>independent nwell                        | FEI3-like     | 2 |

| Sector 3 | M6 in enclosed layout, PMOS in<br>independent nwell                     | FEI3-like     | 2 |

| Sector 4 | Increasing M3, M4, M9. M6 in enclosed layout, PMOS in independent nwell | FEI3-like     | 2 |

| Sector 5 | Same FE as S2, with smaller sensor                                      | ALPIDE-like   | 2 |

| Sector 6 | Same FE as S1                                                           | ALPIDE-like   | 2 |

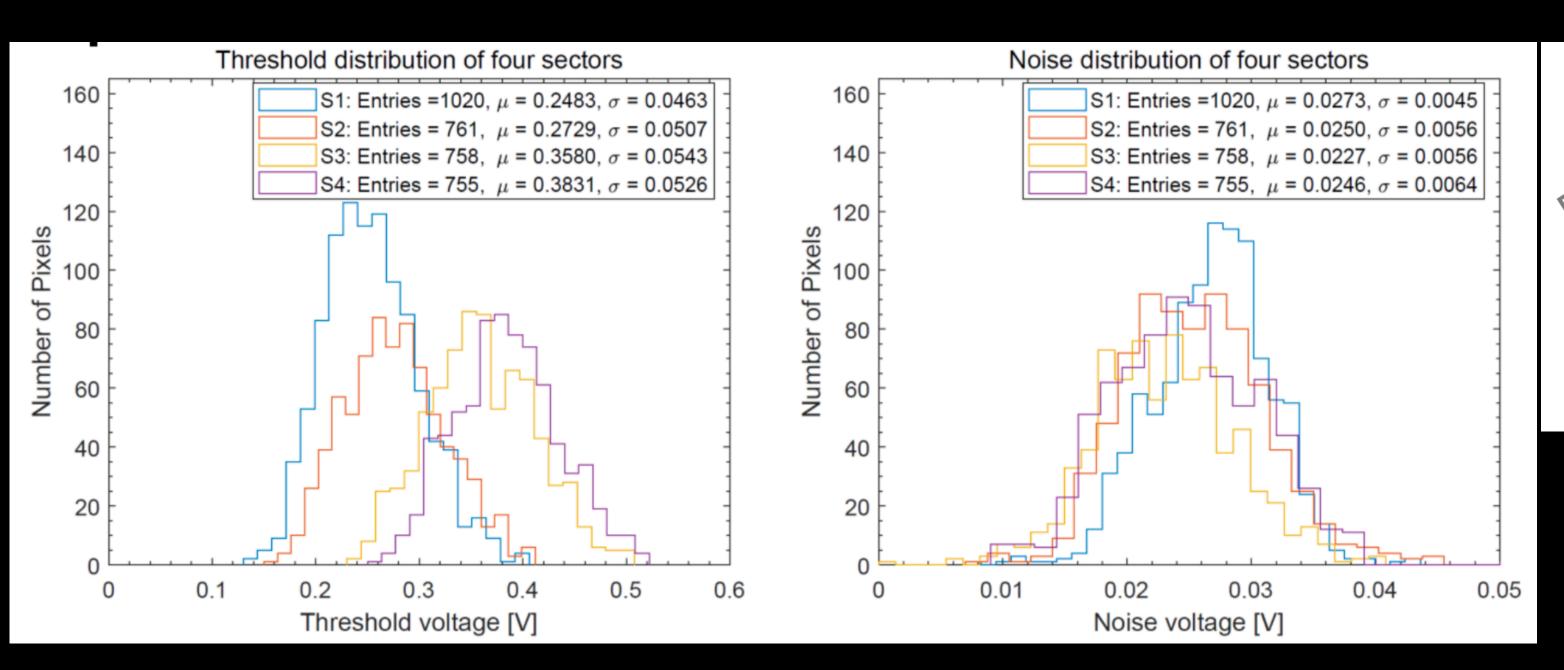

## Electrical test (2)

- Four sectors with FEI3-like digital logic works well

- and show similar noise performance for 4 different pixel design.

- S1 sector design shows the minimum threshold.

## rks well different pixel design. hold.

|   |         | 2         |                              |                      |                                |

|---|---------|-----------|------------------------------|----------------------|--------------------------------|

| 0 | relimin | Mean (mV) | Threshold<br><u>rms</u> (mV) | Random<br>noise (mV) | Total equivalent<br>noise (mV) |

|   | S1      | 248.3     | 46.3                         | 27.3                 | 53.8                           |

|   | S2      | 272.9     | 50.7                         | 25.0                 | 56.5                           |

|   | S3      | 358.0     | 54.3                         | 22.7                 | 58.9                           |

|   | S4      | 383.1     | 52.6                         | 24.6                 | 58.1                           |

|   |         |           |                              |                      | 1                              |

## X ray tests and beta source tests

- Analog output waveform agreed with the simulation

### **Beta source Tests**

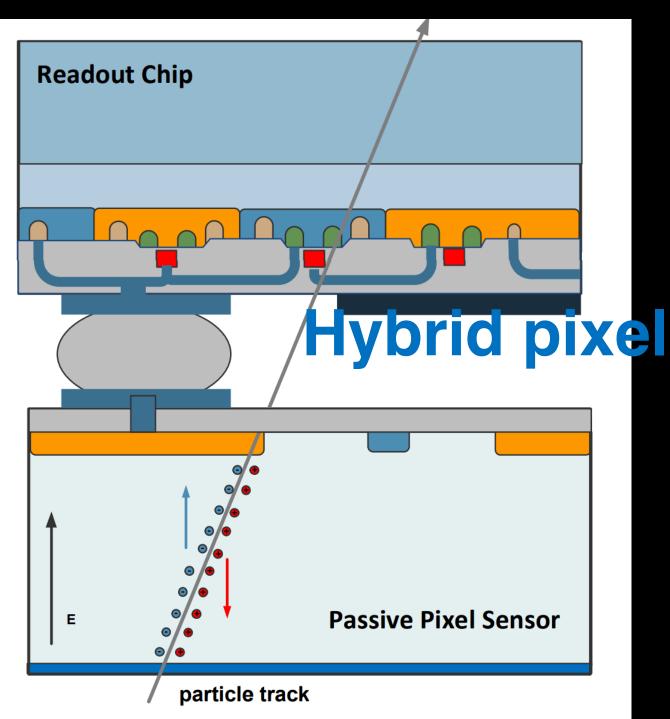

# **CMOS MONOLITHIC PIXEL SENSOR**

- CMOS Monolithic pixel (CIS process) is ideal for CEPC application

- low material budget (can be thin down to 50μm)

- This project use TowerJazz CIS 180nm technology

- Hybrid pixel technology developed by ATLAS and CMS

- Thickness of sensor is about 200~300 μm

- Need to bump bonding with readout ASIC (ASIC thickness is about  $300 \mu m$ )

- Material budget about silicon sensor is about 10 times larger than CIS process

**Monolithic Pixels**

## Research Team in task 2

#### 4 institutes

### 课题2: IHEP - 中国科学院高能物理研究所 SDU - 山东大学 NJU - 南京大学 NWU - 西北工业大学

|                    | Institutes |

|--------------------|------------|

| Full CMOS          | IHDP       |

|                    |            |

| Vertez             |            |

|                    | CCNU/IFAE  |

| C                  | NWPU       |

| <b>CMOS</b> sensor | SDU        |

|                    |            |

|                    | NJU        |

#### Tasks

chip modeling, Pixel Analog, PLL block **Detector module (ladder) prototyping** Data acquisition system R & D x detector assembly and commissioning **CMOS sensor chip: Pixel Digital** CMOS sensor chip: Periphery Logic, LDO chip: Bias generation, TCAD simulation Sensor test board design Irradiation, test beam organization

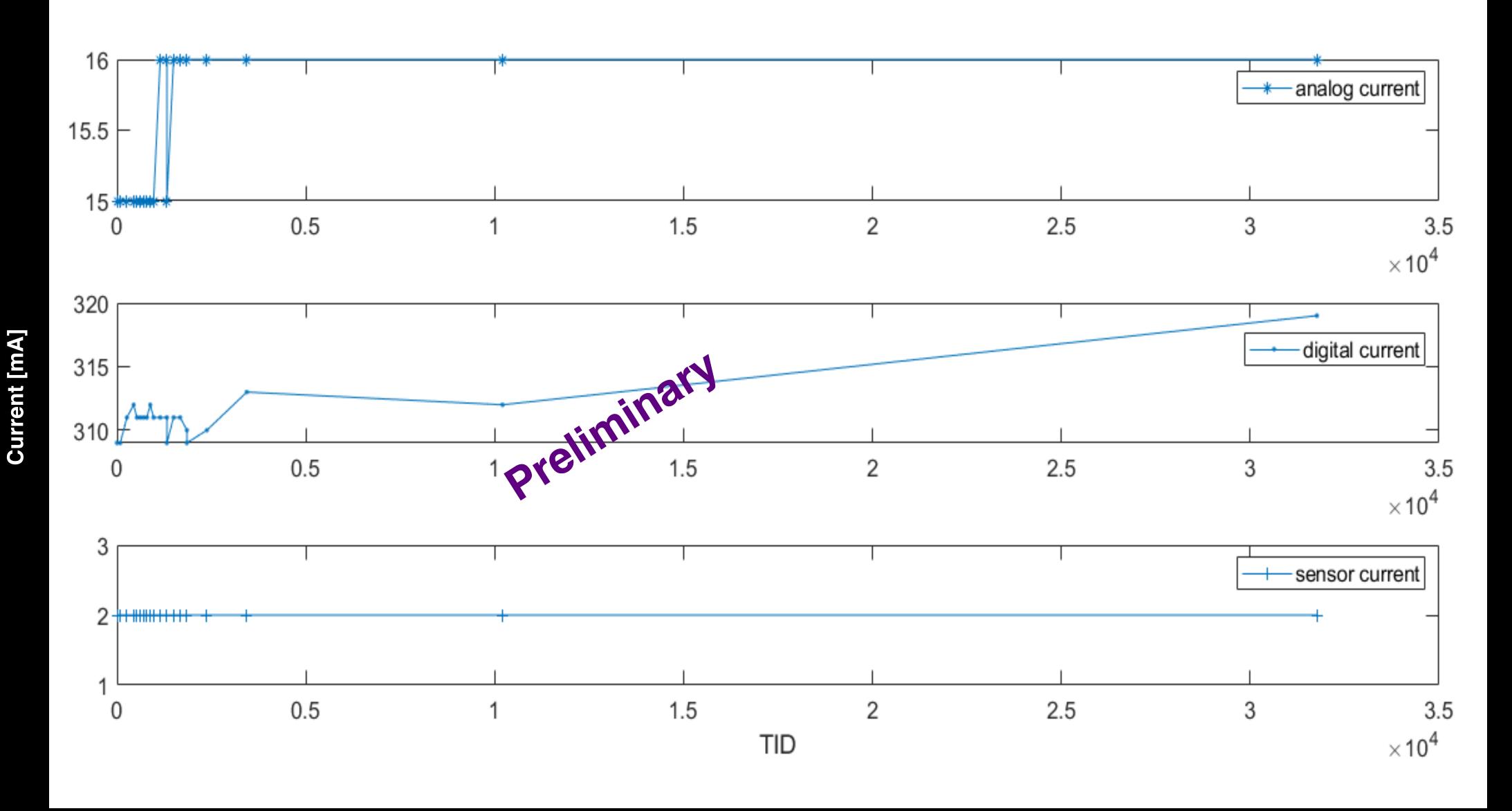

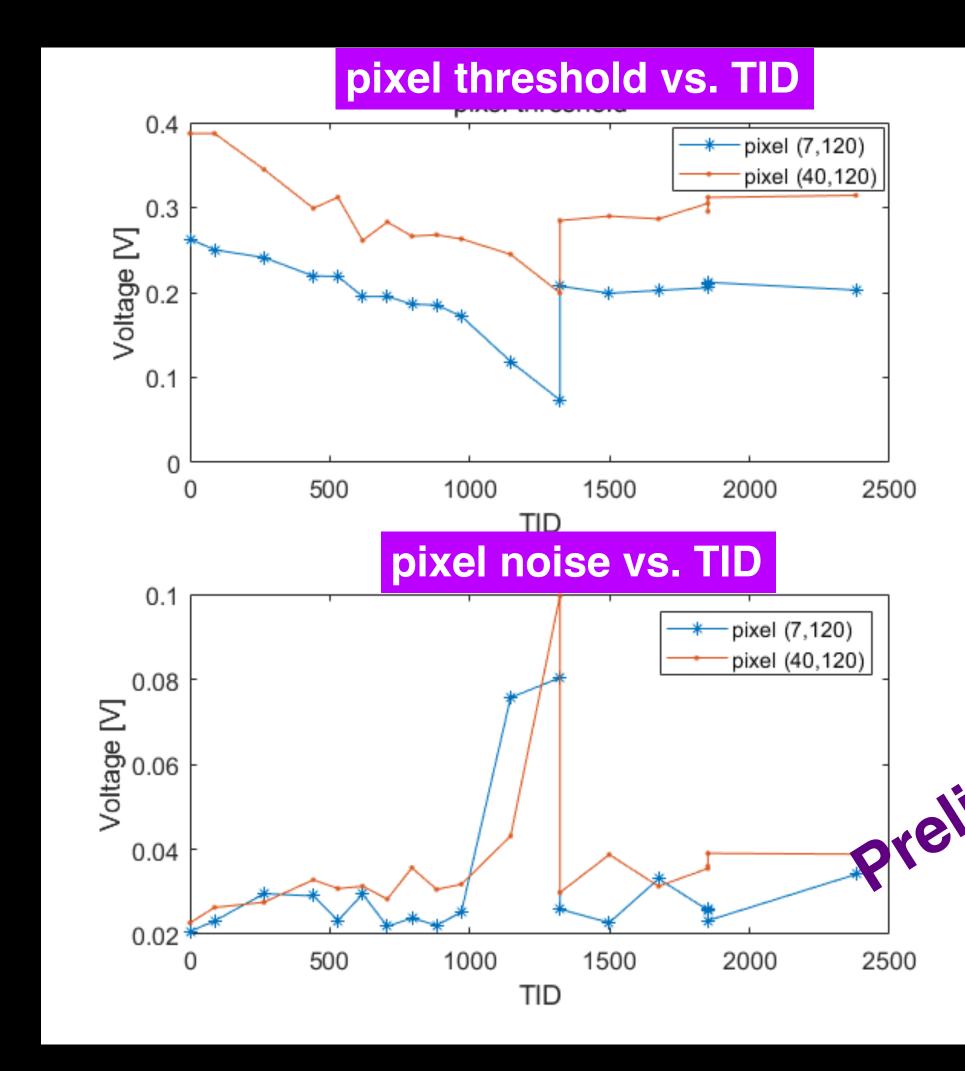

## TaichuPix radiation test

- Completed two round of CMOS sensor prototyping

- First Radiation test up to 30Mrad at BSRF, TaichuPix2 is still functional ullet

- TaichuPix-2 irradiated at BSRF 1W2B beamline (6 keV X-ray)  $\bullet$

- Dose rate ~17.63 krad/min for the first 2.5 Mrad

- then 211.56 krad/min for 51 min, then 1.24 Mrad/min for 15 min

- Dose rates were calibrated with an ion chamber before test

### **Radiation test at BSRF for 2nd MPW chip**

46

## TaichuPix radiation test (2)

- Good chip function and noise performance proved to 2.5 Mrad,

- no deterioration observed when TID up to 30 Mrad.

## proved to 2.5 Mrad, 30 Mrad.

## TaichuPix radiation test (3)

#### No deterioration observed when TID up to 30 Mrad. •