# Fast Simulation for CEPC Tracker Optimization

Yun Youhui, Wei Zhiling, Li Zepeng Fu Chengdong, Wu Linghui Sep.9th,2021

#### **Baseline Design**

There are 6 VXDs, 4 SITs,1 DC and 1 SET,their parameters are as follows.

[Detector | 1 aver | Padius (mm | Material budget [X0])]

| Detector | Layer | Radius(mm | Material budget[X0] |  |

|----------|-------|-----------|---------------------|--|

| VXD      | 1     | 16        | 0.15%               |  |

|          | 2     | 18        | 0.15%               |  |

|          | 3     | 37        | 0.15%               |  |

|          | 4     | 39        | 0.15%               |  |

|          | 5     | 58        | 0.15%               |  |

|          | 6     | 60        | 0.15%               |  |

| SIT      | 1     | 80        | 0.65%               |  |

|          | 2     | 320       | 0.65%               |  |

|          | 3     | 560       | 0.65%               |  |

|          | 4     | 800       | 0.65%               |  |

| DC       | 100   | 800~1800  | 0.34%               |  |

| SET      | 1     | 1815      | 0.65%               |  |

(From youhui's talk)

### Optimization

| Detector   | Layer | Radius(mm) | Material budget[x/X0] |  |  |

|------------|-------|------------|-----------------------|--|--|

| shell      | 1     | 78         | 0.0015                |  |  |

| SIT        | 1     | 80         | 0.0065                |  |  |

|            | 2     | 320        | 0.0065                |  |  |

|            | 3     | 560        | 0.0065                |  |  |

|            | 4     | 800        | 0.0065                |  |  |

| Inner wall | 1     | 800        | 0.00104               |  |  |

| DC         | 100   | 800-1800   | 0.000116              |  |  |

| Outer wall | 1     | 1800       | 0.01346               |  |  |

- VXDS and SET stay unchanged

- The outer radius of DC stays unchanged

• Change the radius of DC and SITs and the number of DC's layers at the same time

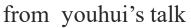

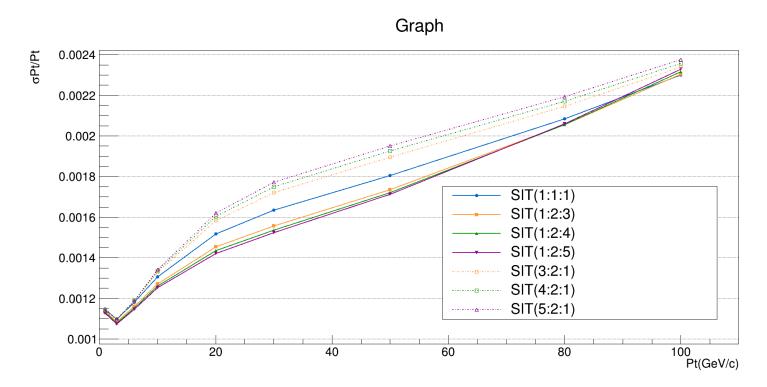

#### Optimization of SITs layout

- Layers at 80 and 800mm fixed

- Only two layers can move

#### Optimization of SITs layout

- Layers at 80 and 800mm fixed

- Only two layer can move

Consistent with Hao and Cheng's result

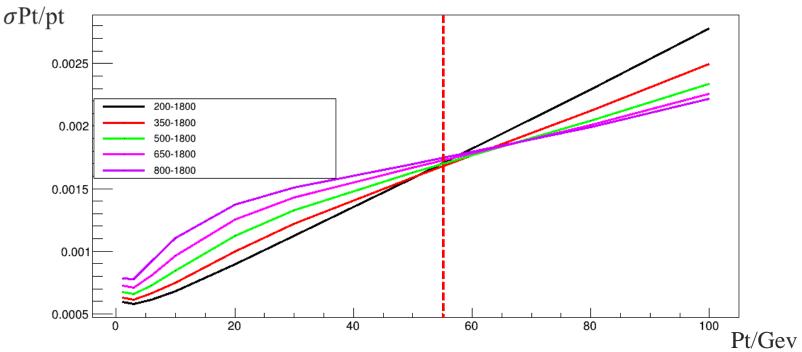

#### Optimization of radius and # of layers

- 10x10 cell, material budget 0.000116

- SIT spacing 1:1:1

| Radius of DC | #of layer | Radius of SITs |     |     |     |

|--------------|-----------|----------------|-----|-----|-----|

| 200-1800     | 160       | 80             | 120 | 160 | 200 |

| 350-1800     | 145       | 80             | 170 | 260 | 350 |

| 500-1800     | 130       | 80             | 220 | 360 | 500 |

| 650-1800     | 115       | 80             | 270 | 460 | 650 |

| 800-1800     | 100       | 80             | 320 | 560 | 800 |

#### Optimization of radius and # of layers

#### sigmaPt MSON

- Pt below ~55Gev, smaller inner radius makes better resolution

- Pt above ~55Gev, on the contrary

#### **Summary**

- SIT layers favor to be near to beamline except the two fixed layers(from Gang's talk)

- At low Pt, smaller inner radius(and more layers) of DC(1:1:1) makes better resolution and at high Pt opposites

## THANKS!