# SDHCAL R&D Activities

**LAGARDE** Francois

On behalf of SDHCAL Group

## **Outline**

- Introduction

- New SDHCAL prototype

- Timing developments

- RPC and MRPC developments

- Woven strips

- Summary

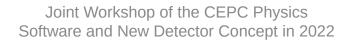

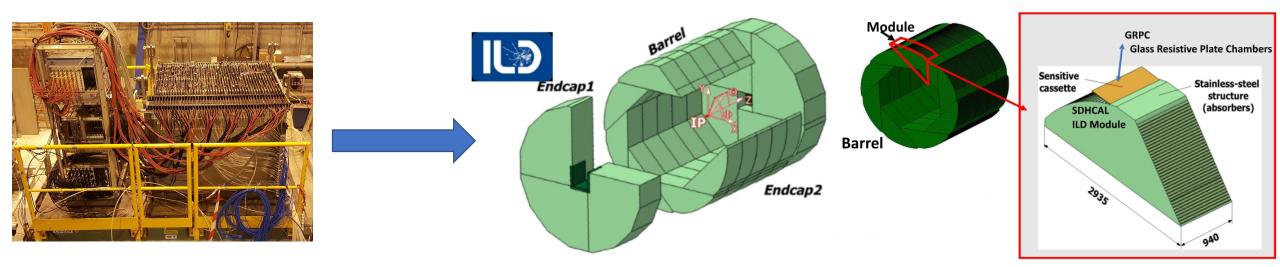

# Semi-Digital Hadronic CALorimeter

The SDHCAL-GRPC is one of the two HCAL options based on PFA and proposed for **ILD of ILC/CEPC**. Modules are made of **48/40 RPC chambers** equipped with **semi-digital**, **power-pulsed electronics** readout and placed in **self-supporting mechanical** structure to serve as absorber as well.

### The structure of SDHCAL :

- Very compact with negligible dead zones

- Eliminates projective cracks

- Minimizes barrel / endcap separation (services leaving from the outer radius)

- Homogeneity for large surfaces

- Thickness of only few mms

- Lateral segmentation of 1 cm X 1 cm

- Services from one side

- Embedded power-cycled electronics

- Self-supporting mechanical structure

Hits associated to 3 different thresholds :

- 1st threshold = 110fC

- 2nd threshold = 5pC

- 3rd threshold = 15pC

Active medium : 48 GRPC layers  $(-6\lambda_I)$ Dimensions :  $1m \times 1m \times 1.3m$ Granularity :  $1cm \times 1cm (-500\ 000ch)$ Power-pulsed electronics Self-supported mechanical structure

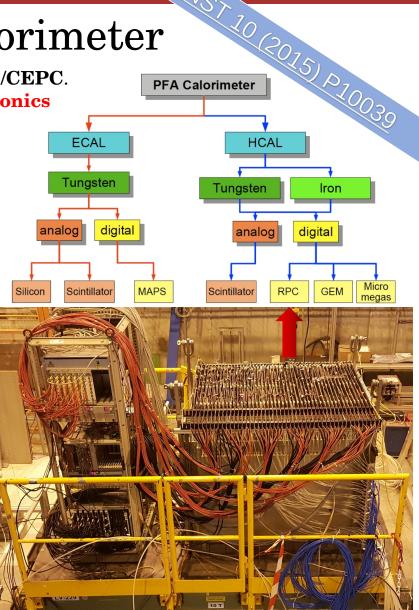

# Futher improvements on the energy reconstruction

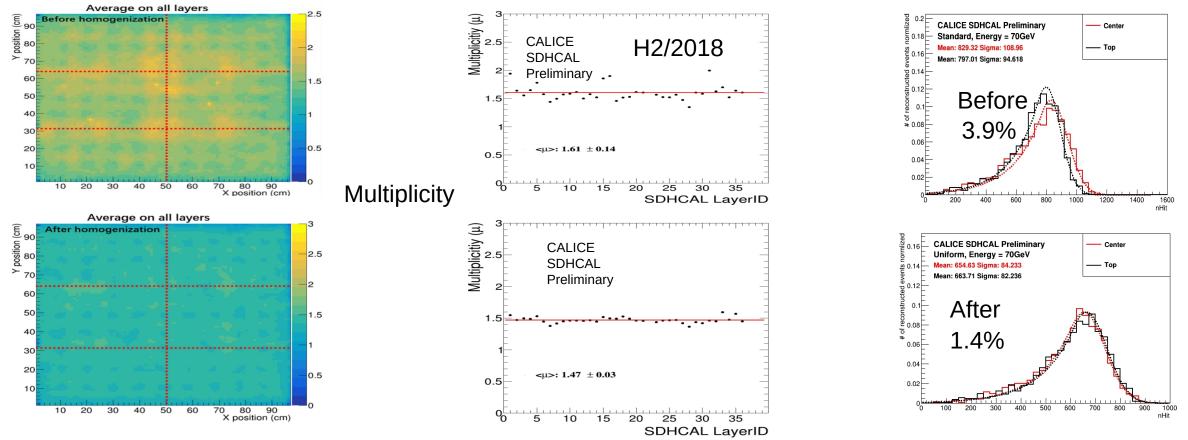

The homogeneity of the detector response is important to achieve better energy reconstruction

A new calibration method based on varying the thresholds rather than the electronic gain was found to be powerful. Muon runs with different thresholds Thr1: 0.1-0.42 pC, Thr2: 0.4-5, Thr3:4.7-24) and efficiency and multiplicity were measured for each value. The values of the three thresholds of each ASIC were fixed to obtain same multiplicity (first threshold) and the same efficiency for thr2 and thr3.

### 5/25/2022

Software and New Detector Concept in 2022

# SDHCAL

- $\checkmark$  Excellent not only to apply PFA by separating nearby showers but also to measure their energy.

- ✓ Excellent linearity and very good resolution.

- ✓ Hadronic shower is an excellent asset to identify particles and then better measure their energy.

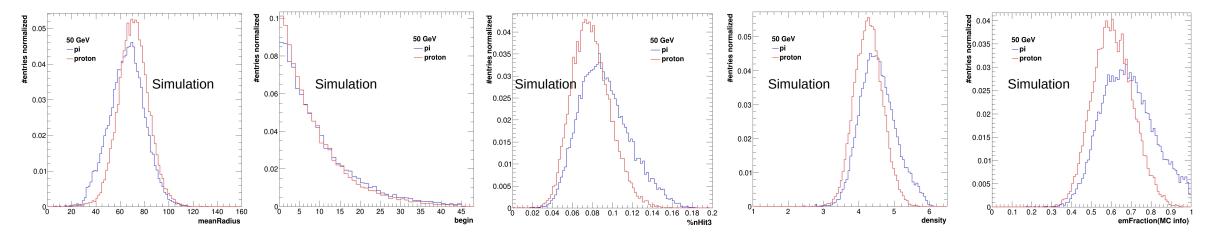

# Next step : Hadron identification

Identify the nature of the hadrons.  $\rightarrow$  Better reconstruction

No distinction was made between pions and protons or others. Hadronic showers of pions and protons are not identical

2022 beam test : study pion vs proton and kaon showers using Cerenkov detectors. Use BDT technique to develop hadron PID and then energy construction algorithm with different parameters could be used.

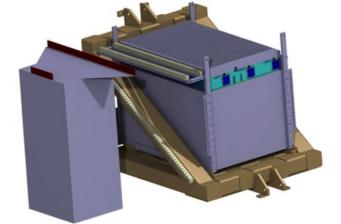

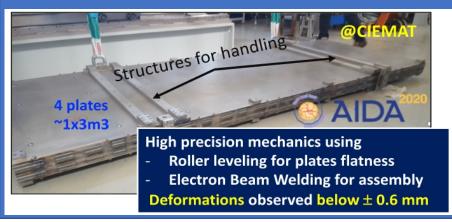

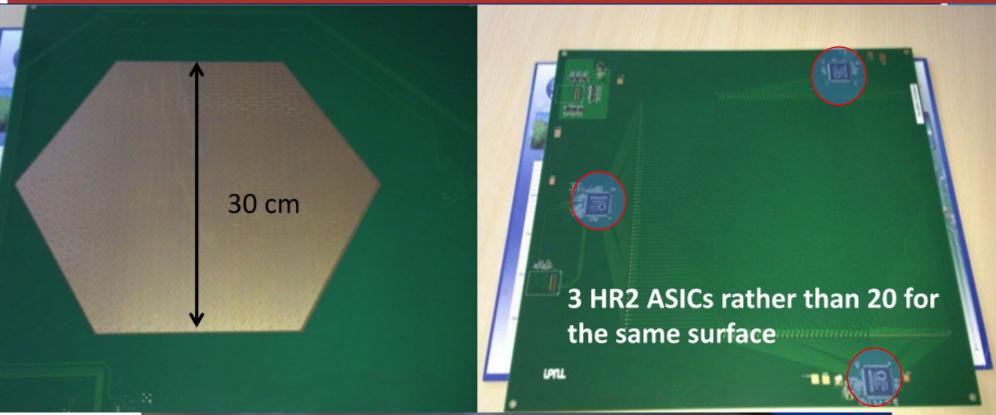

# New SDHCAL prototype

### Move from 1m\*1m to ~3m\*1m (real design)

.implies new challenges for the detector, embedded electronics and mechanics.

New prototype with a mechanical structure of 4 plates of  $\sim 1 \times 3m^2$ (assembled with similar procedures to the final one) with large RPCs equipped with a new improved electronics.

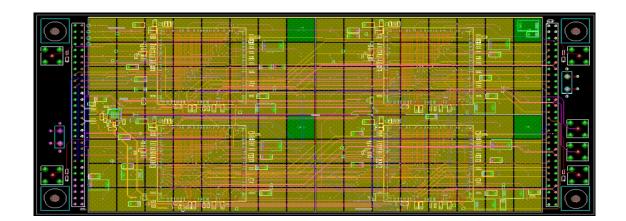

# Status of the new prototype

### Electronics

- New ASIC : HARDROC3

- ASU: 1x0.33 m<sup>2</sup> with 13 layers

- 1 DIF / chamber (up to 1x3 cm<sup>2</sup>)

- 432 chips ~38k ch

|     | ← 36 columns of HR3 → |               |             |     |                |  |  |  |  |  |

|-----|-----------------------|---------------|-------------|-----|----------------|--|--|--|--|--|

|     | ASU                   | ASU           | 9 ASU cards | ASU | Î              |  |  |  |  |  |

| DIF |                       |               |             |     |                |  |  |  |  |  |

|     |                       |               |             |     | HR3            |  |  |  |  |  |

|     |                       |               |             |     | 12 rows of HR3 |  |  |  |  |  |

|     |                       |               |             |     | 12 rc          |  |  |  |  |  |

| -   |                       |               |             |     |                |  |  |  |  |  |

|     |                       |               |             |     |                |  |  |  |  |  |

|     | HR3 chips             | 48 on each AS | U)          |     | Ŷ              |  |  |  |  |  |

# Chambers

### Mechanical structure

# Timing developments

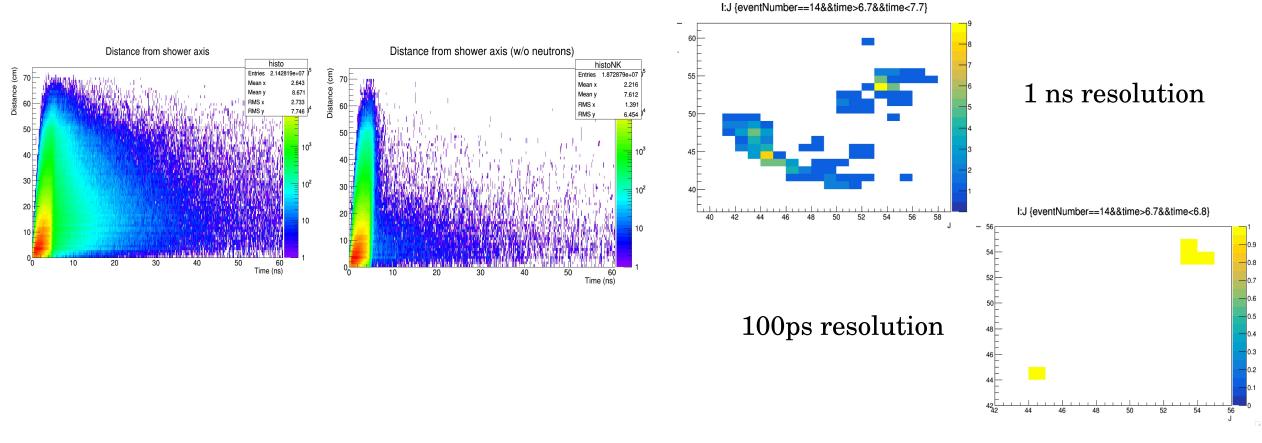

Goal : Extend the SDHCAL to include timing information (100-200ps resolution) for a 5D-calorimeter (x,y,z,E,t).

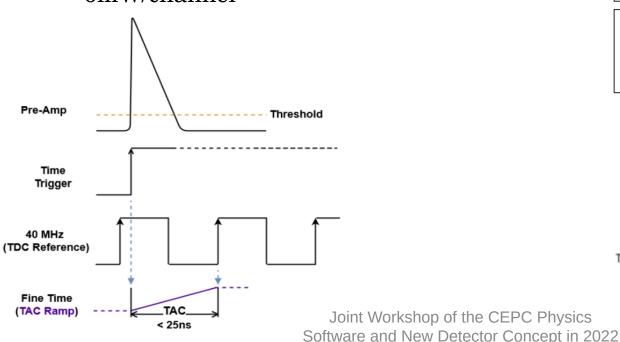

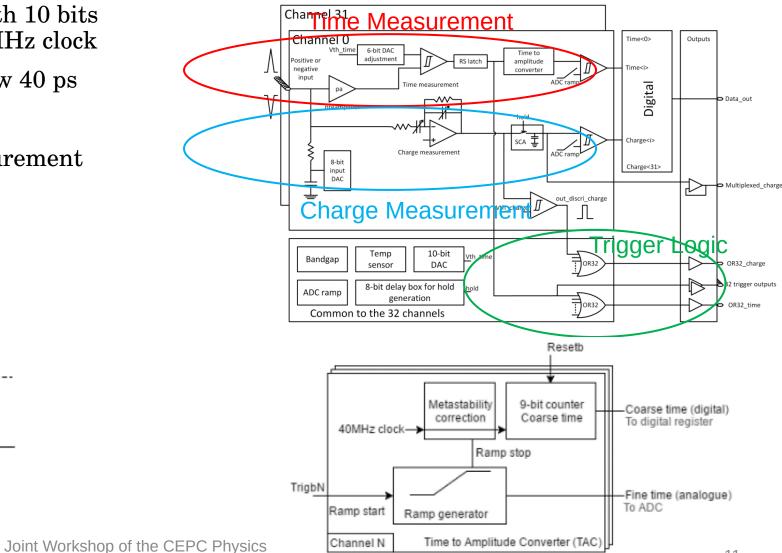

Need to move to Multi-gap RPC (~1ns to ~20-100ps ). Need to change the electronics : from HARDROC2B to PETIROC2A (200ns to <40 ps)

# **Timing information**

• Timing could be an important factor to identify delayed neutrons.

• Separate close-by showers and reduce the confusion. Improve PFA.

- Time measurement with 10 bits TDC interpolating 40MHz clock

- Timing resolution below 40 ps

- 32 input channels

- charge and time measurement

- Power consumption:

~6mW/channel

5/25/2022

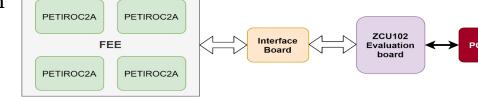

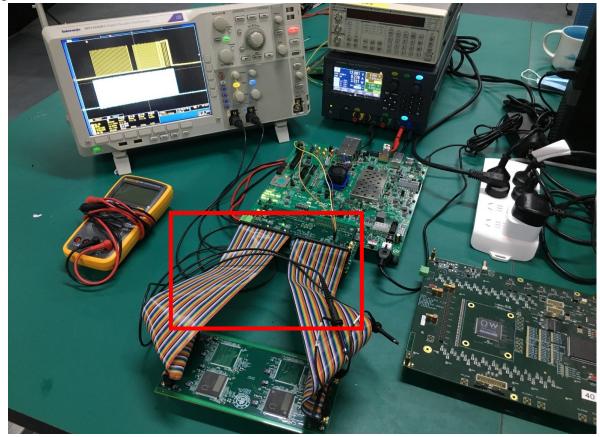

### **FEE** Prototype

- The FEE : 4 PETIROC, 128 pads.

- Detector Interface (DIF) : connect FEE and FPGA board, data transmission

- power rail, clock source.

### **FE Board**

ZCU102

128 pads with the

Joint Workshop of the CEPC Physics cell size 1cm × 1cm oftware and New Detector Concept in 2022

5/25/2022

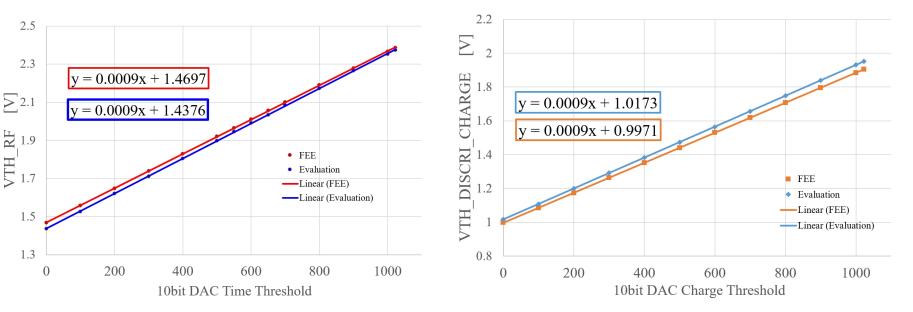

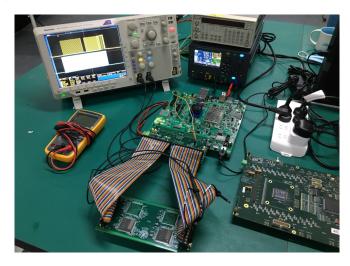

# Time and Charge Threshold Voltage Test

- All of bias voltage values are correct.

- Output data has been checked, after sending trigger signals.

- Time threshold is correct according to the voltage value with 10bit DAC.

- Time and Charge threshold can be well controlled.

# Bias Voltage Value(V) vref\_inpdac 0.989 vref\_time 1.664 vref\_charge 0.976 vref\_tdc 0.133 vref\_adc 0.961 vref\_time\_pad 1.658

### Crosstalk exists in the injection test : New version of FE Hardware

# **New version of FE Hardware**

- Purpose : test Petiroc timing measurement performance

- Remove jump cables to reduce noise and crosstalk.

- Schematic and layout design has been finished, fabrication is starting soon.

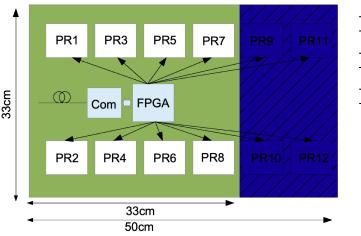

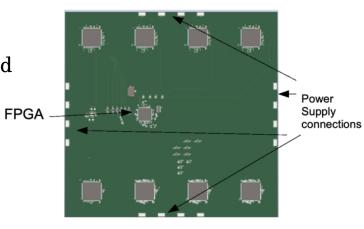

# **Toward Larger prototypes**

Board with 8 ( could be extended to 12 ) Petircoc2B ASICs Pads 2cm x 2cm, 256 channels

Local FPGA (Xilinx Spartan-6 TQFP) embedded on board

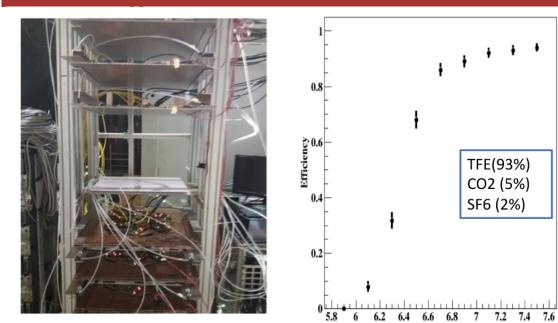

# **RPC and MRPC developments**

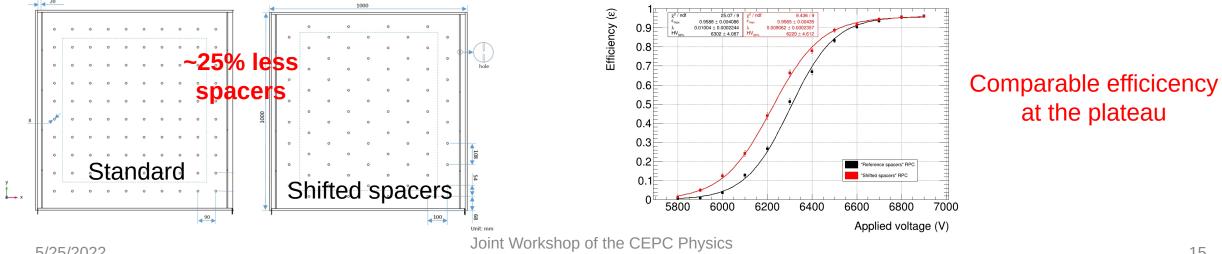

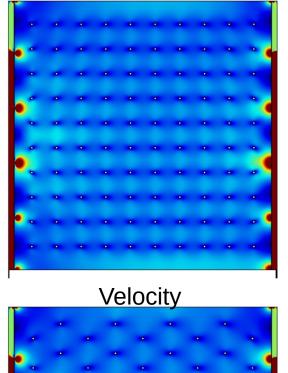

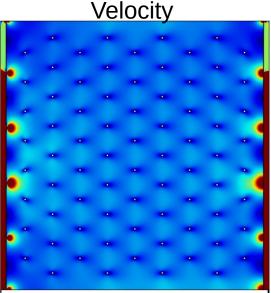

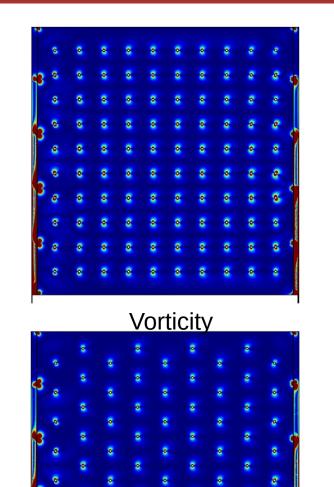

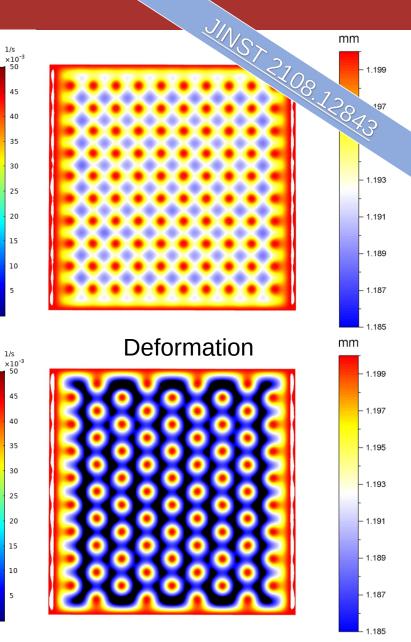

1m<sup>2</sup> RPC chamber has been built @ SJTU and a new spacer configuration has been studied

5/25/2022

Software and New Detector Concept in 2022

0.04

0.03

0.02

0.01

cm/s

Joint Workshop of the CEPC Physics Software and New Detector Concept in 2022

| Shanghai Shao Tong Oniversity                      |                                          |                                          |            |

|----------------------------------------------------|------------------------------------------|------------------------------------------|------------|

|                                                    |                                          | SINST                                    | 2108.12843 |

|                                                    |                                          |                                          | 408.120    |

| Model                                              | "Reference spacers" RPC                  | "Shifted spacers" RPC                    | ×3         |

| Mean velocity $\bar{v}$                            | $0.238 \ (\mathrm{mm \ s^{-1}})$         | $0.241 \text{ (mm s}^{-1}\text{)}$       |            |

| RMS of velocity $\sigma_v$                         | $0.049 \ (\mathrm{mm}  \mathrm{s}^{-1})$ | $0.042 \ (\mathrm{mm}  \mathrm{s}^{-1})$ |            |

| $\sigma_v/\bar{v}$                                 | 20.3 (%)                                 | 17.5 (%)                                 |            |

| Mean vorticity near spacers region                 | $0.0199 (s^{-1})$                        | $0.0196 (s^{-1})$                        |            |

| RMS of vorticity near spacers region               | $0.0129 (s^{-1})$                        | $0.0127 (s^{-1})$                        |            |

| Mean vorticity excluding the vicinity of spacers   | $0.0022 (s^{-1})$                        | $0.0018 (s^{-1})$                        |            |

| RMS of vorticity excluding the vicinity of spacers | $0.0028 (s^{-1})$                        | $0.0026 (s^{-1})$                        |            |

| Mean thickness between gas gap $\bar{d}$           | 1.193 (mm)                               | 1.189 (mm)                               |            |

| RMS of deformation $\sigma_d$                      | 0.003 (mm)                               | 0.005 (mm)                               |            |

| $\sigma_d/\bar{d}$                                 | 0.25 (%)                                 | 0.42 (%)                                 |            |

### **Next step : Build MRPCs with Shifted spacer configuration**

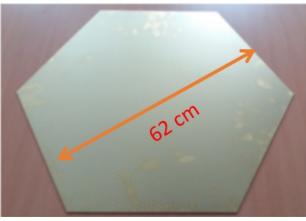

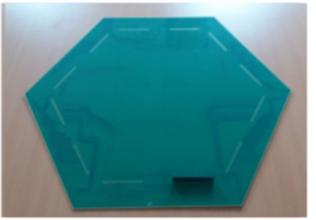

# **MRPC** construction

- MRPCs are planed to be built @ SJTU, small size started @ Lyon

- Use spacer, study the new spacer configuration on MRPC

- 40cm×30cm

- Paint with a surface resistivity in the range 1-10M  $\Omega/\Box$

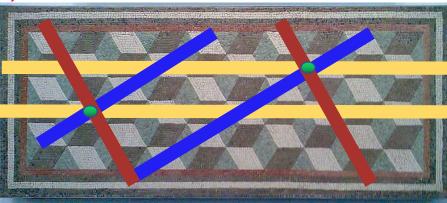

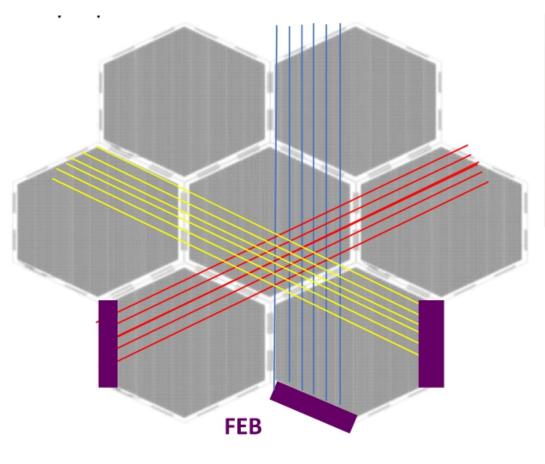

# **Woven strips**

Patent: PCT/EP2018/053561

Pads : High granularity, cost, power, heat (cooling system, pulsed electronics) Strips : ghost, less channels, less power consumption, ...

### N\*N to 3N : Reduction of electronic channels, power consumption and occupancy Other tessellation possible !

Joint Workshop of the CEPC Physics Software and New Detector Concept in 2022

PCB with lozenges-based structure and 3 directions.

The readout electronics was set on the same PCB. HARDROC2B ASICs (64-ch, 2-bit).

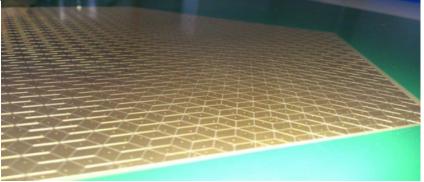

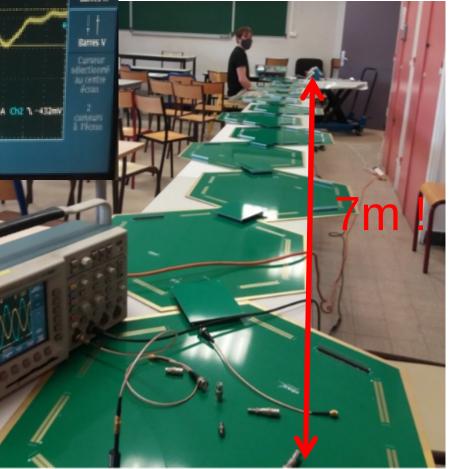

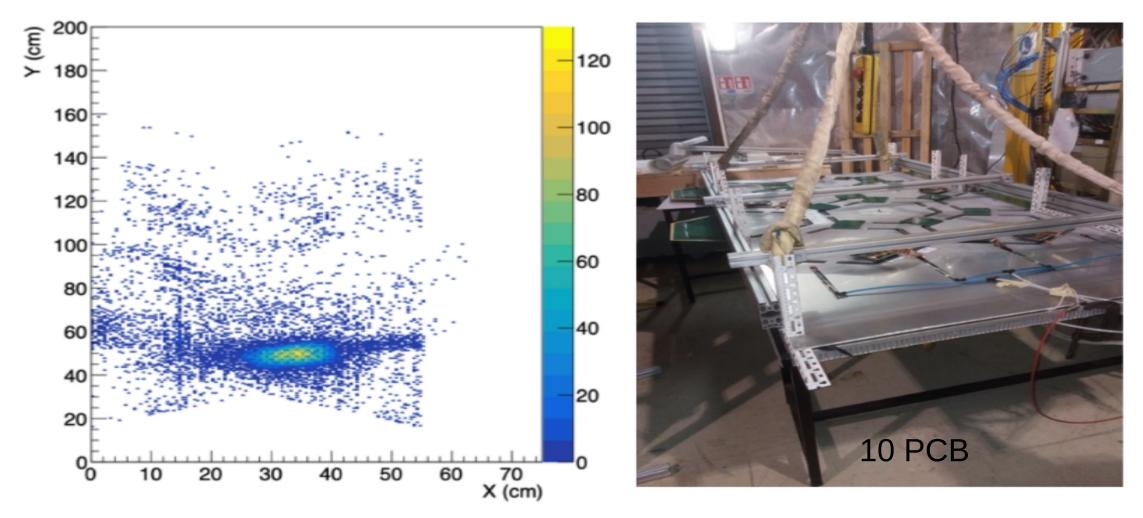

# **To large surface**

To instrument very large gaseous detectors the readout electronics could not be part of the PCB. Separate strip panels from the readout electronics.

PCBs with only woven strips :

With connectors to transmit signal :

- Two adjacent PCBs

- The electronics board

Plugged directly on the back of the PCB (64 channels)

Setup with 8 detectors equipped with the new readout scheme Large PCB A: 23.2mV

Ferction

A: 23.2mV

Ferction

Curseur

Descrive

Descrive

RPC-like signal shape injected on one end and detected on the opposite one is different but the charge loss is rather small.

### Tested on a large GRPC (2m x 1m) with several PCBs Reconstruction efficiency (1 direction efficiency is not included) is around 90%

# Summary

- SDHCAL has good linearity and energy resolution

- Real size prototype has been built

- New electronics are under study to use timing information.

- Woven strips electronics are studied

- Improvements on RPCs (gas flow, spacer configuration)

# Backup

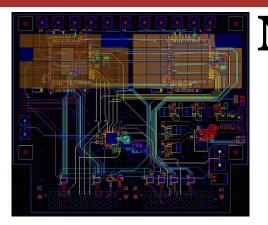

# Design of Front-end Board

| L. |   |        |   | 1          | _  |        |    |  |  |

|----|---|--------|---|------------|----|--------|----|--|--|

| Ι  |   | AIR    |   | SURFACE    |    |        |    |  |  |

| 1  | • | COPPER | - | CONDUCTOR  |    | TOP    | 2  |  |  |

| 1  | - | FR-4   | - | DIELECTRIC |    |        | 3  |  |  |

| 1  | - | COPPER | - | CONDUCTOR  |    | GN 21  | 4  |  |  |

| 1  | - | FR-4   | - | DIELECTRIC |    |        | 5  |  |  |

| 1  | • | COPPER | - | CUNCURTOR  |    | SIG1   | 6  |  |  |

| 1  | - | FR-4   | • | DIELECTRIC |    |        | 7  |  |  |

| 1  | • | COPPER | - | CONDUCTOR  |    | SIG2   | 8  |  |  |

| 1  | • | FR-4   | - | DIELECTRIC |    |        | 9  |  |  |

|    | - | COPPER | - | PLANE      |    | GND2   | 10 |  |  |

| 1  | • | FR-4   | - | DIELECTRIC |    |        | 11 |  |  |

| 1  | - | COPPER | - | PLANE      |    | VDDA   | 12 |  |  |

| 1  | - | FR-4   | - | DIELECTRIC |    |        | 13 |  |  |

| 1  | - | COPPER | - | PLANE      |    | VDDD   | 14 |  |  |

| 1  | - | FR-4   | - | DIELECTRIC |    |        | 15 |  |  |

|    |   | COPPER | - | PLANE      |    | GND3   | 16 |  |  |

| 1  | - | FR-4   | • | DIELECTHIC |    |        | 17 |  |  |

| 1  | • | COPPER | - | CONDUCTOR  |    | SIG3   | 18 |  |  |

| 4  | - | FR-4   | - | DIELECTRIC |    |        | 19 |  |  |

| 1  | - | COPPER | - | CONDUCTOR  |    | SIG4   | 20 |  |  |

| 1  | - | FR-4   | - | DIELECTRIC |    |        | 21 |  |  |

| 1  | - | COPPER | - | CONDUCTOR  |    | GND4   | 22 |  |  |

| 1  | - | FR-4   | - | DIELECTRIC |    |        | 23 |  |  |

| 1  | - | COPPER | - | CONDUCTOR  |    | воттом | 24 |  |  |

| 1  |   | AIR    |   | SURFACE    | 25 |        |    |  |  |

Stack-up and via design

- 12 layers PCB

- Many induction units are at the bottom

- Laser-drilled Via Technology (small size: ~0.1mm) between outside two layers

- Buried Vias with the size 0.3mm

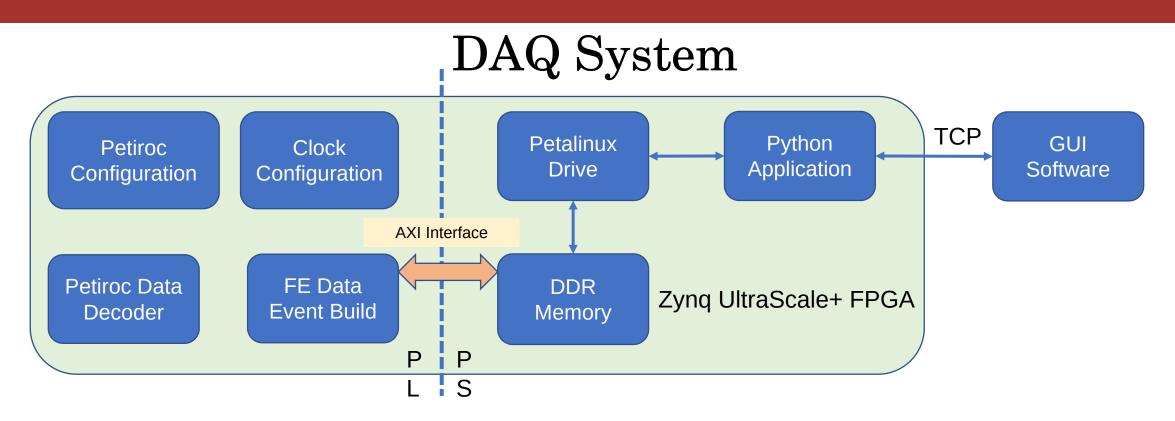

- Front-end interface: Petiroc configuration and data output decoder

- AXI interface between PL and PS, through DDR memory

- The PetaLinux tools allows to customize embedded Linux solutions on Xilinx processing systems.

- Python application access PS memory via linux driver, and communicates with PC via ethernet

# DAQ Software

- The DAQ software is a Python GUI application.

- The GUI is designed via QT designer, which is set of cross-platform C++ libraries that implement high-level APIs.

- PyQt5 modules binding with QT v5.

| II MainWindow                                                                                                     |                                                                               |                                                                                                  | - 🗆 X                                                                                         | Main sett     | ings EN/PP Calibration            | n Connect test | :                  |                               |      |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------|-----------------------------------|----------------|--------------------|-------------------------------|------|

| Main settings EN/PP Calibration                                                                                   | Connect test                                                                  |                                                                                                  |                                                                                               |               |                                   |                |                    |                               |      |

| Mask disci charge           0           1           2           3           4           5           6           7 | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15                                    | ☐ 16<br>☐ 17<br>☐ 18<br>☐ 19<br>☐ 20<br>☐ 21<br>☐ 22<br>☐ 23                                     | 24<br>25<br>26<br>27<br>28<br>29<br>30<br>31                                                  | 待发送费          | 发送                                | 打印648bit       | 导出到文本              | 文本名称: reg_10_14.txt           |      |

| Mask disci time 0 1 2 3 4 5 6 7                                                                                   | 8         9         10         11         12         13         14         15 | □ 16<br>□ 17<br>□ 18<br>□ 19<br>□ 20<br>□ 21<br>□ 22<br>□ 23                                     | 24<br>25<br>26<br>27<br>28<br>29<br>30<br>31                                                  | 254 TA 114 45 |                                   |                |                    |                               |      |

| ☐ ADC ramp compensation<br>☐ External start ADC<br>LatchDiscri no latch ∨<br>Polarity Negative ∨                  | charge 300<br>time 500<br>DAC dummy 0<br>DAC delay 0                          | Cin<br><ul> <li>1. 25pF</li> <li>2. 5pF</li> <li>3. 75pF</li> <li>5pF</li> <li>τ=25ns</li> </ul> | Cf<br><ul> <li>100fF</li> <li>200fF</li> <li>300fP</li> <li>400fF</li> <li>τ =25ns</li> </ul> | 本机ip<br>本机端   | 重定向到文本<br>192.168.31.166<br>12345 |                | 清屏<br>未连接<br>TCP ~ | 文本名称: data_10_14.txt<br>建立服务器 | 断开连接 |

# Status of System Test

|       |    |             | ======10 bit         |         |           |     |          |      |      |   |

|-------|----|-------------|----------------------|---------|-----------|-----|----------|------|------|---|

|       |    |             | 1100011101,          |         |           |     |          |      |      |   |

|       |    |             | 1000010110,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

| Ch5 : | 69 | Coarsetime: | 1111100010,          | Decode: | 101011110 | ==> | Counter: | 350, | Hit: | 0 |

| Ch6 : | 70 | Coarsetime: | 1111100010,          | Decode: | 101011110 | ==> | Counter: | 350, | Hit: | 0 |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1111100010,          |         |           |     |          |      |      |   |

|       |    |             | 1001011110,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      | 1 |

|       |    |             | 1100010101,          |         |           |     |          |      |      | 1 |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      | 1 |

|       |    |             | 1100010101,          |         |           |     |          |      |      | 1 |

|       |    |             | 1100010101,          |         |           |     |          |      |      | 1 |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

|       |    |             | 1100010101,          |         |           |     |          |      |      |   |

| Ch31: | 95 | Coarsetime: | 110001010 <u>1</u> , | Decode: | 100001100 | ==> | Counter: | 268, | Hit: | 1 |

• Crosstalk exists in the injection test

# Summary

- Timing information helps to identify neutrons and separate close-by showers.

- MRPC detector is being built, which has an improved timing performance.

- A front-end prototype and a interface card has been designed and tested.

- $\bullet$  The Xilinx ZCU102 board is used as the DAQ system.

- The firmware and software of DAQ system has been developed.

- A new version of hardware has been designed, and will be fabricated soon.

- The larger prototype is being developed.

# Introduction of PETIROC chip

- Time measurement with 10bits TDC interpolating 40MHz coarse time

- Charge measurement (  $\ensuremath{\mathbf{Q}\xspace{50}\ensuremath{\mathbf{fC}}\xspace}$  ) with 10bits DAC

- Voltage input amplifier, 2000hm matching

- High bandwidth preamp (GBWP> 1.2 GHz)

- PETIROC parameters:

- One chip with 32-channels and mixed analog/digital

- The 32chs input connected with PAD (detector unit)

- One channel split into two parts, respectively for charge and time measurement

- Internal DAC for each channel to adjust the amplitude of the input signal

- Lower power consumption (~6mW/channel)

- Jitter ~18 ps RMS on trigger output (4 photoelectrons injected)