# Proposal for DMAPS Upgrade of the Belle II Vertex Detector

Xu Danwei – CPPM, Aix Marseille Université, CNRS/IN2P3, Marseille, France On behalf of the Belle II VTX Upgrade Group

# outline

- Belle II and SuperKEKB

- The current VXD and the new upgrade VTX

- The TJ-Monopix2 & the OBELIX design

- TJ-Monopix2 test & Test Beam

- Conclusions

UNIVERSITÄT BONN

Belle II and SuperKEKB

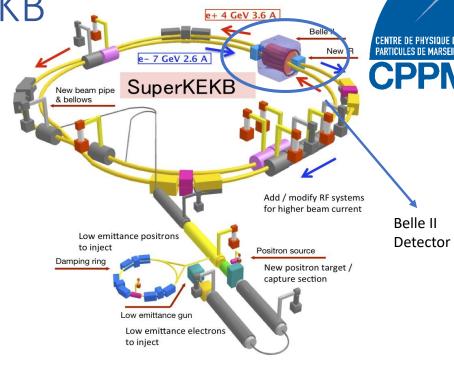

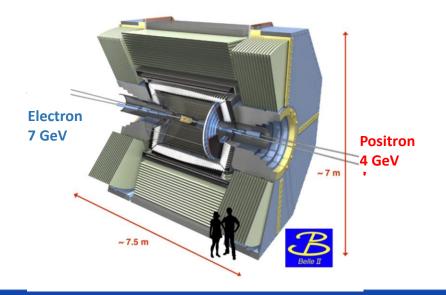

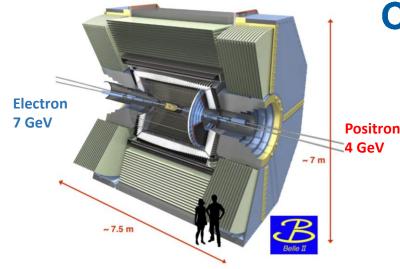

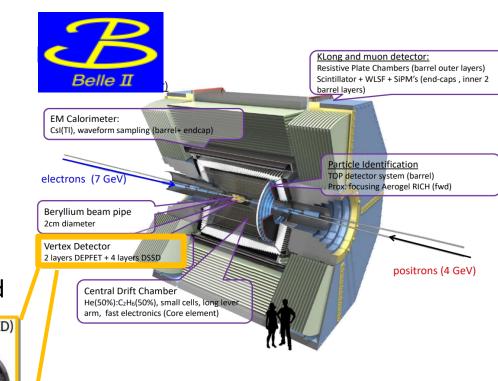

- Located at the SuperKEKB collider in Tsukuba/Japan

- Luminosity frontier experiment, a large ultra-high luminosity asymmetric electron-positron colliding device

- Asymmetric e<sup>+</sup> e<sup>-</sup> collisions at 10.58 GeV

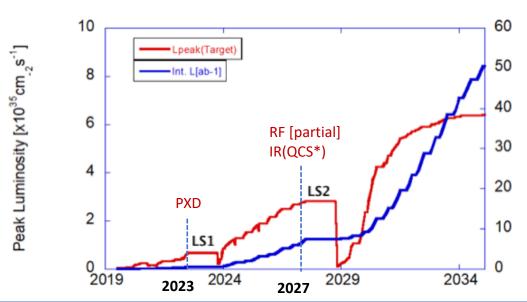

- Current luminosity L<sub>int</sub> = 428 fb<sup>-1</sup> since 2019

- Record  $L_{max} = 0.47 * 10^{35} \text{cm}^{-2} \text{s}^{-1}$  in June 2022

- Long Shutdown1 since June 2022

- Restart at end of 2023

A long way to reach the target peak luminosity:

- Target luminosity  $L_{int} = 50 \text{ ab}^{-1}$

- Target Peak  $L_{max} = 6 * 10^{35} \text{ cm}^{-2} \text{s}^{-1}$

# Belle II and SuperKEKB

# CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE

#### Challenge

- Machine related beam background will increase with high luminosity (high currents & nano-beam scheme)

- Performance could degrade with higher occupancy from background (track finding efficiency, resolution)

- Potential change in Interaction Region

#### Goal of the upgrade:

- Upgraded to cope with the higher luminosity provided by the SuperKEKB accelerator

- To be more robust against high background and match possible new interaction region

- Intend upgrade during Long Shutdown 2 (2027 or later)

#### Current vertex detector VXD

- The main tracker device is the central drift chamber (CDC), which is complemented by a vertex detector (VXD)

- Two technology system:

- Two layers of DEPFET pixel -- PXD see talk Anselm Baur

- Four layers of double-sided strip detector –SVD see talk Jaroslaw Wiechczynski

- Standalone tracking for low momentum (SVD)

- Current VXD performance good & operating with low background occupancy < 1 % , well below limits (PXD  $\sim$  3% SVD  $\sim$  5%)

- Performance degradation possible for higher occupancy

- Extrapolation to target luminosity has large uncertainty and limited safety margin detector limit

Silicon Vertex Detector (SVD)

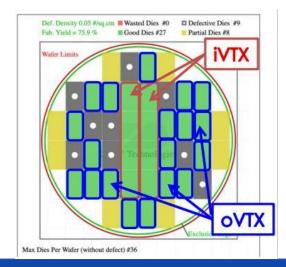

# The VTX baseline Concept

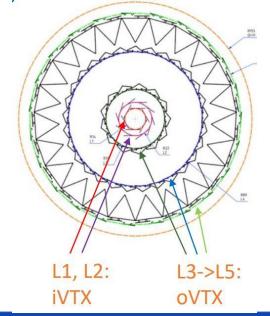

- A new fully pixelated CMOS detector proposed to replace the VXD > VTX

- 5 straight fully pixelated barrel layers

- Same sensor chip for all layers

- Depleted Monolithic Active CMOS Pixel Sensors chip size:  $2x3 \text{ cm}^2$ , moderate pixel pitch  $33 \mu m^2$

- 2 layers iVTX and 3 layers oVTX

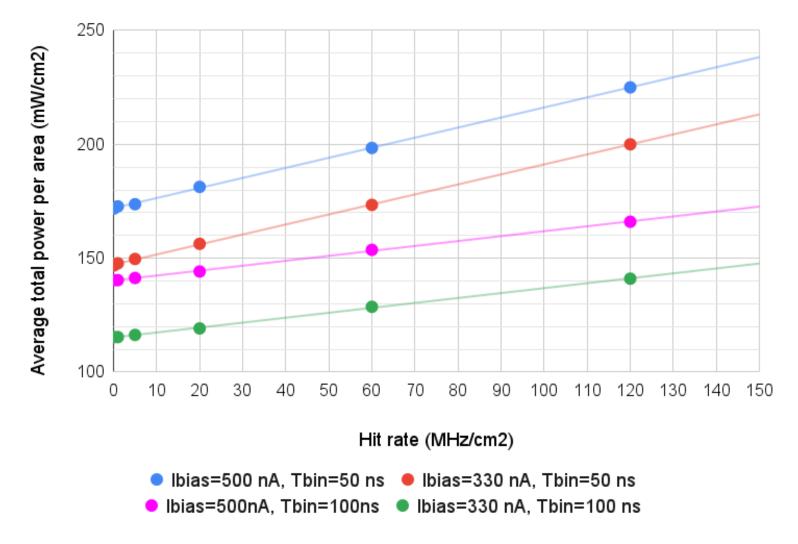

- Power dissipation ~ 200 mW/cm<sup>2</sup>

- Reduced material budget:

3.8% X<sub>0</sub> --- 2.5% X<sub>0</sub> (sum of all layers)

- Increase granularity:

- Space for SVD

- Time for PXD

#### Requirements:

- Radiation tolerance

- TID:  $\sim$  10 Mrad/year

- NIEL:  $\sim 5 * 10^{13} n_{eq}/cm^2/year$

- Hit Rate : up to 120MHZ/cm<sup>2</sup>

- Resolution < 15 μm

- Trigger at 30KHz average frequency with 5-10µs latency

- Fast integration time 50-100 ns

- Reduce occupancy and increase tracking performances

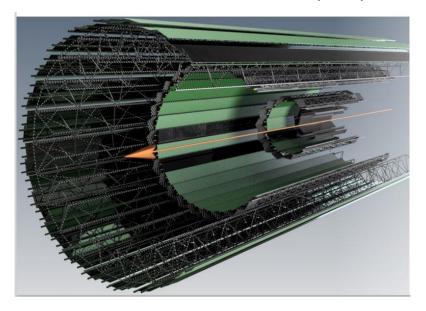

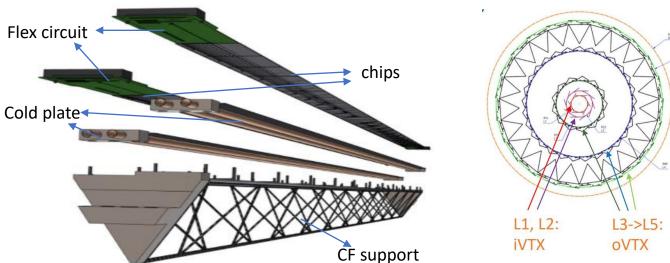

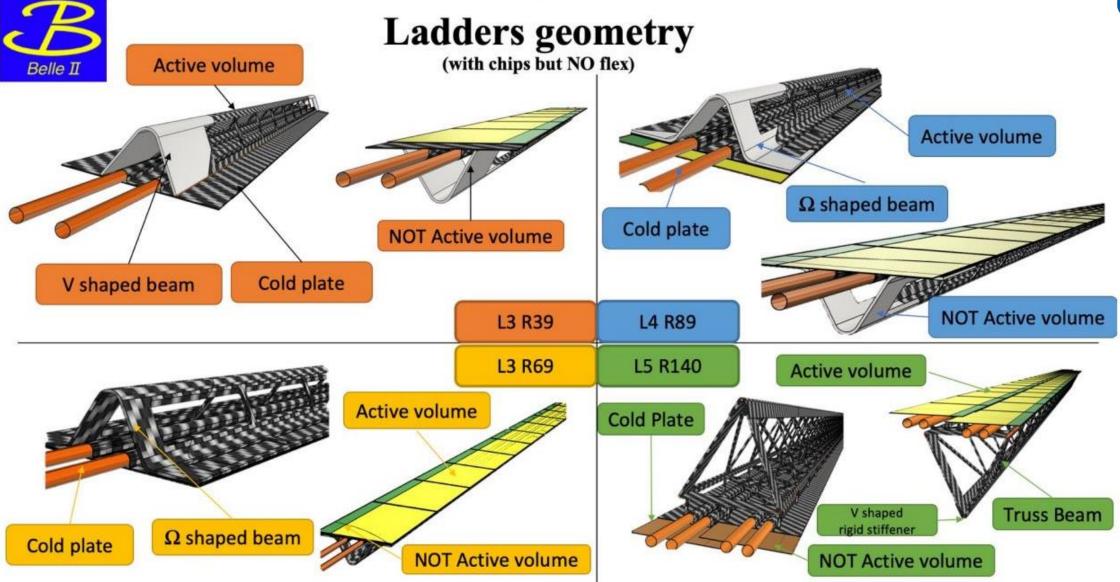

# The VTX detector mechanics

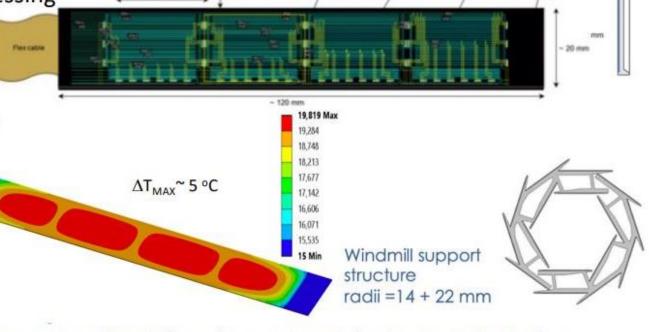

#### L1 and L2 (iVTX):

- Radii innermost layer 14mm

- Self-supported all silicon module

- 4 contiguous sensors blocks diced out of wafer

- Interconnected with redistribution layer

- Heterogeneous thinning

- Air cooling

- $\sim 0.1\% \text{ X}_0 \text{ for L1 \&L2}$

#### L3 to L5 (oVTX):

- Radii outermost layer 140 mm

- Carbon fiber support frame

- Cold plate with water cooling

- $\sim 0.4\% \text{ X}_0 \text{ for L3, } \sim 0.6\% \text{ X}_0 \text{ for L4}$  $\sim 0.8\% \text{ X}_0 \text{ for L5}$

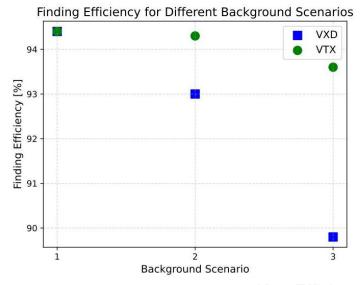

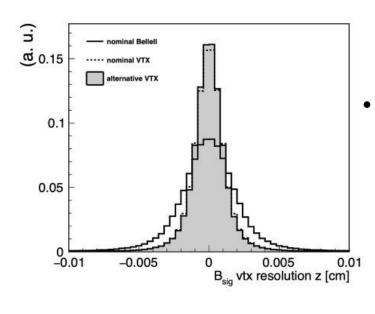

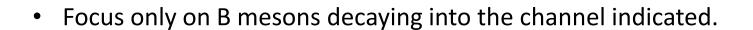

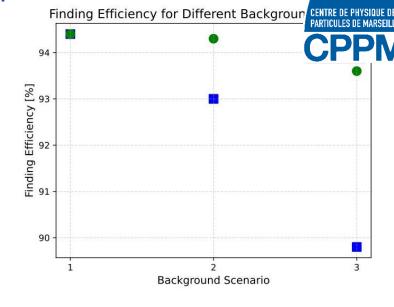

# VTX simulated tracking performance

- VTX performance studied based on the tracking of single event, overlaying to signal events different beam background levels:

- The events are just coming from generic events e+ eproducing a pair of B mesons

- From optimistic BG scenario 1 to conservative BG scenario 3

- Possibility to include all layers in the tracking

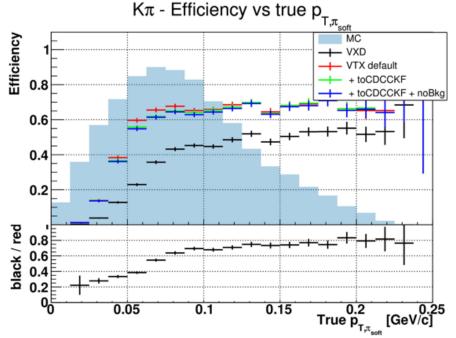

- VTX provides better vertex resolution than the current VXD in the decay channel B<sup>0</sup>

- VTX gives better tracking efficiency than VXD for full tracking (vertex tracking combined with CDC), especially at low momentum (soft pions signal in particular).

VTX Upgrade for Belle II

#### **Physics benchmarking**

Soft  $\pi$  reconstruction in  $B^0 \to D^{*-}\mu^+\nu_\mu$   $\searrow \overline{D^0}\pi^-$

# Technological choice

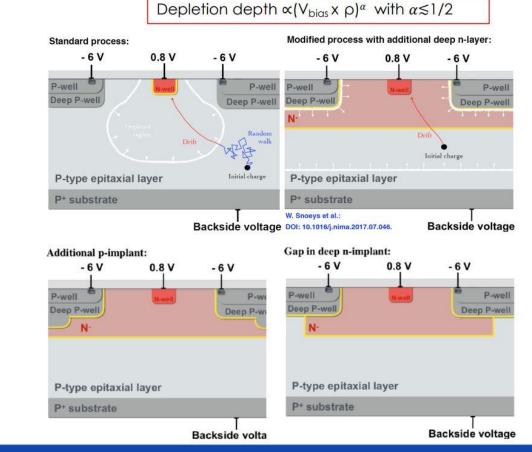

- Depleted MAPS in Tower Jazz 180nm technology:

- Large expertise in the community and many projects

- CMOS pixel sensor + electronics in same silicon die

- Small electrode concept:

capacitance, power, Tpeak, large conversion factor

- Modified process: higher radiation tolerance

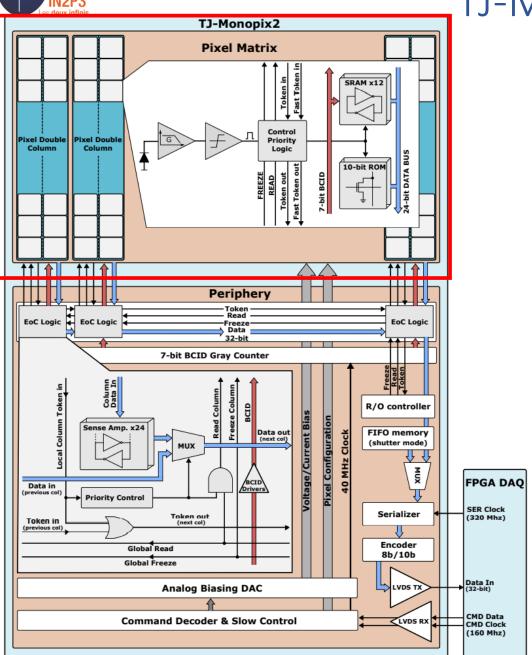

TJ-Monopix2

10

- Developed for ATLAS experiment (2020)

- FE derived from ALPIDE

- Column-drain R/O architecture

- Expected from design:

- 5-10 e- threshold dispersion (tuned)

- >97% efficiency at  $10^{15} n_{eq}$ /cm<sup>2</sup>

- ~ 5 e− noise

- Fully efficient with hit rate 120 MHz/cm<sup>2</sup>

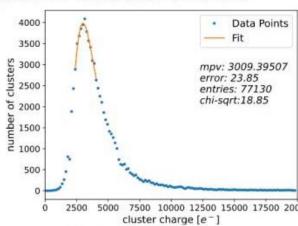

- MIP ~ 2500e-

- Pixel matrix

- TJ 180nm technology

- Proposed as starting point for OBELIX design

- Keep pixel matrix design

- Trigger adaptation in new digital periphery

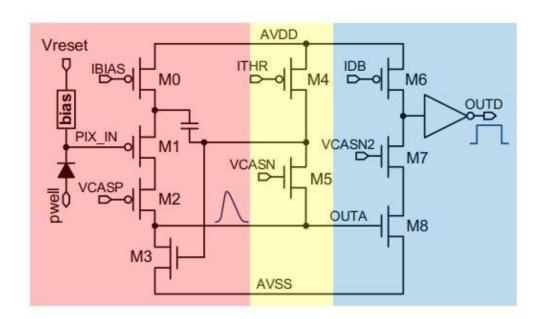

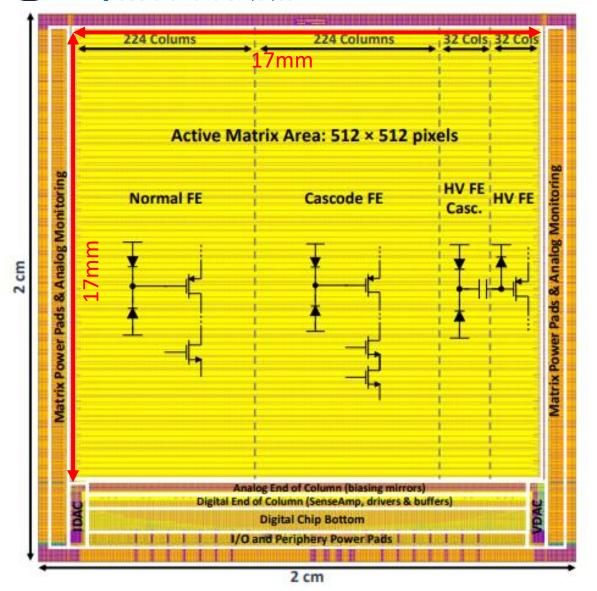

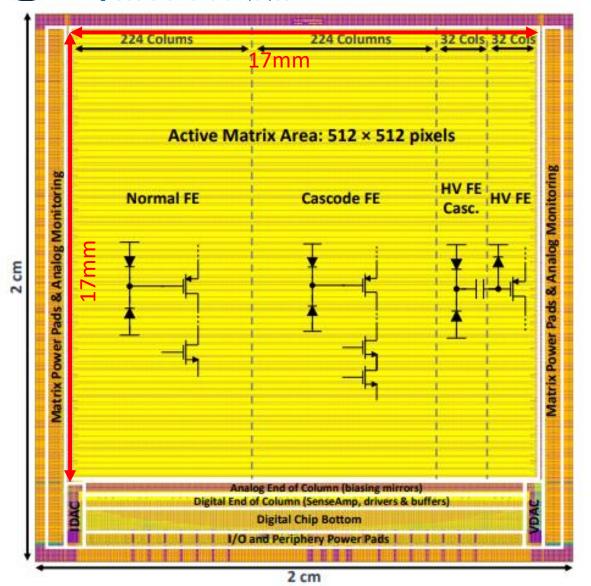

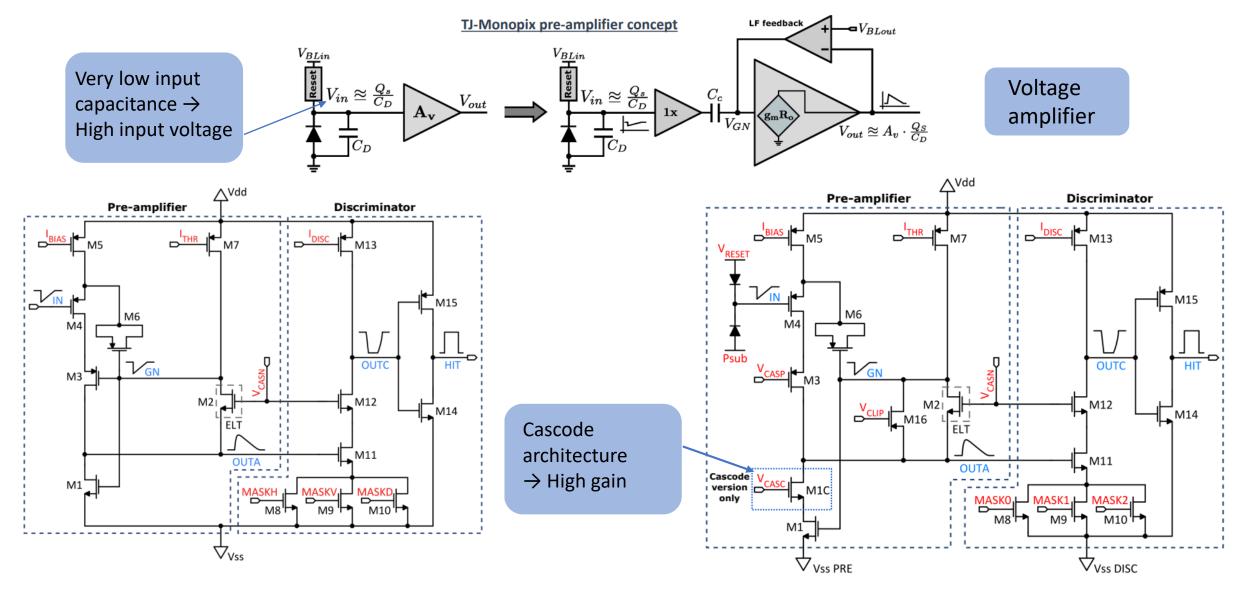

# TJ-Monopix2 – pixel matrix

11

- Pixel pitch: 33.04 × 33.04 μm²

- Pixel matrix:  $2 \times 2$  cm<sup>2</sup> chip , 512 × 512 pixels

- 4 pixel Front-End (FE) flavors with differences in preamplifier, sensor coupling and biasing

- Normal FE

- Cascode FE

- HV Cascode FE

- HV FE

- Two columns for Analog Monitoring

- Flavor need to be decided for OBELIX

- Test done in Bonn, Pisa, HEPHY, CPPM, Göttingen, IPHC

- Detailed information for this part, refer to <u>Lars' talk</u>

Regulator

**IDAC VDAC**

Regulator

Periphery (digital)

TRU (Trigger Unit)

TRG0 (Trigger Group)

EOCO EOC1 EOC2 EOC3

50 50

TXU (Transmission Unit)

Total width = 18812 µm

CRU (Control Unit)

**Pixel Matrix**

DAC EoC & Buffer

Monitoring

ADC

TULAI WIULII - 30 TUO

Temperatur

e Sensor

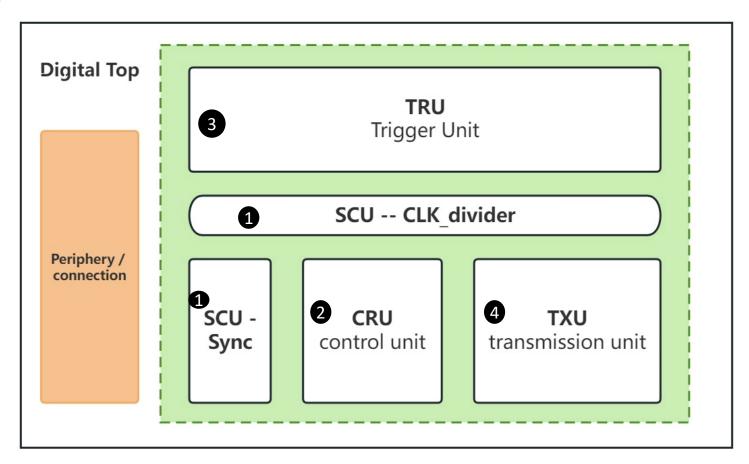

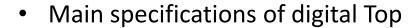

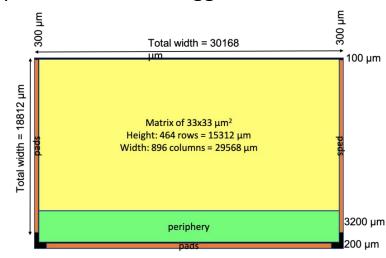

# The OBELIX Design

(Analog)

PowerOn

Reset

TRG111 (Trigger Group)

EOCO EOC1 EOC2 EOC3

51 52

SO

TTT (Track Trigger Transmission)

Clock Divider, Synchronization

The Optimized BELle II pIXel sensor

Main design based on the TJ-Monopix2 chip with TJ180nm

Chip size optimized to maximize the number of 4 contiguous sensor

#### Pixel Matrix

- Transplant from TJ-Monopix2 radiation tolerance granted

- Possible power optimisation

- Freq 10-30MHz

#### New digital periphery

- New EoC adapted to Belle II trigger 30KHz & with 5-10μs latency

- Main Clk at 160MHz, Single output at 320Mb/s

- Signal digitization: ToT (7 bits, 20 MHz)

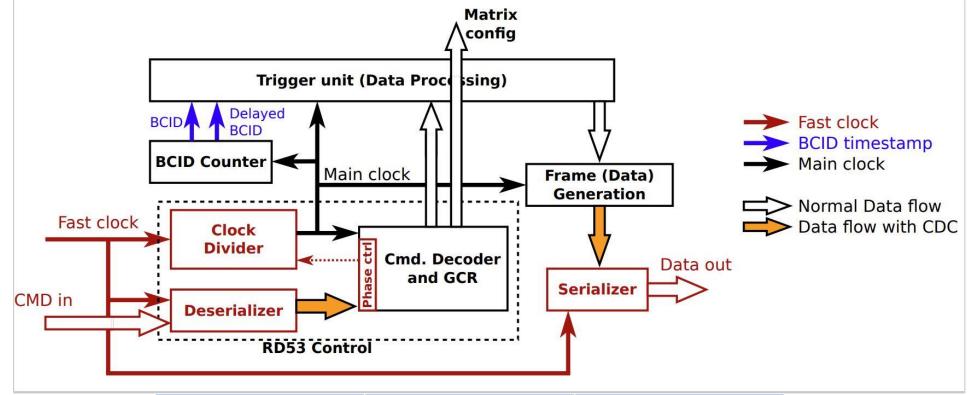

- RD53B\* control protocol

#### Power Pads

- Power regulator added

- Simplified system integration

# Matrix of 33x33 μm² Height: 464 rows = 15312 μm Width: 896 columns = 29568 μm periphery pads 100 μm

- RD53B protocol:

- RD53B users guide CERN Document Server

# The OBELIX Design

13

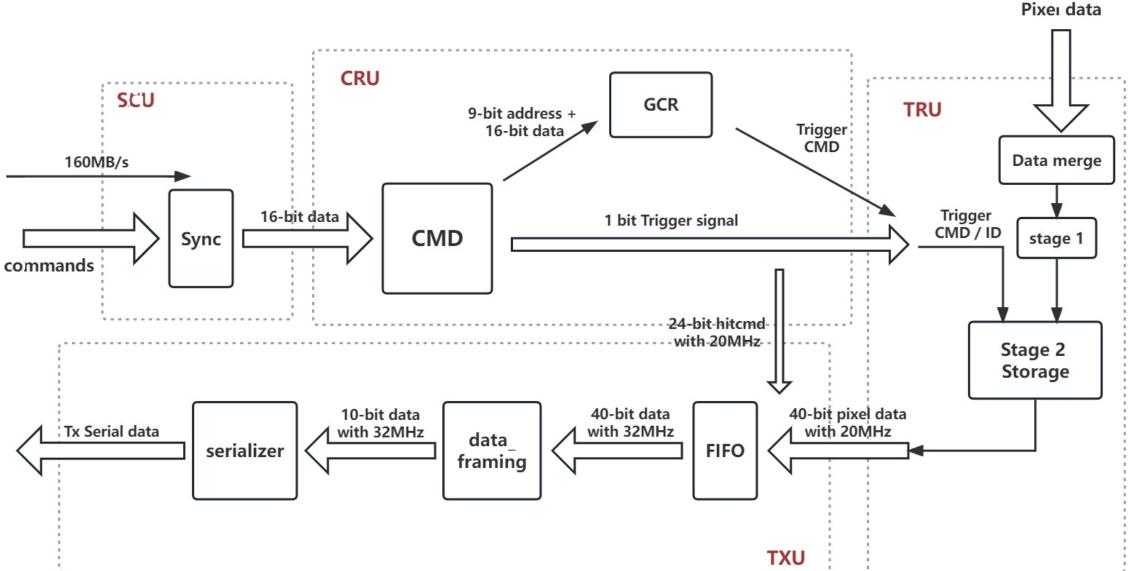

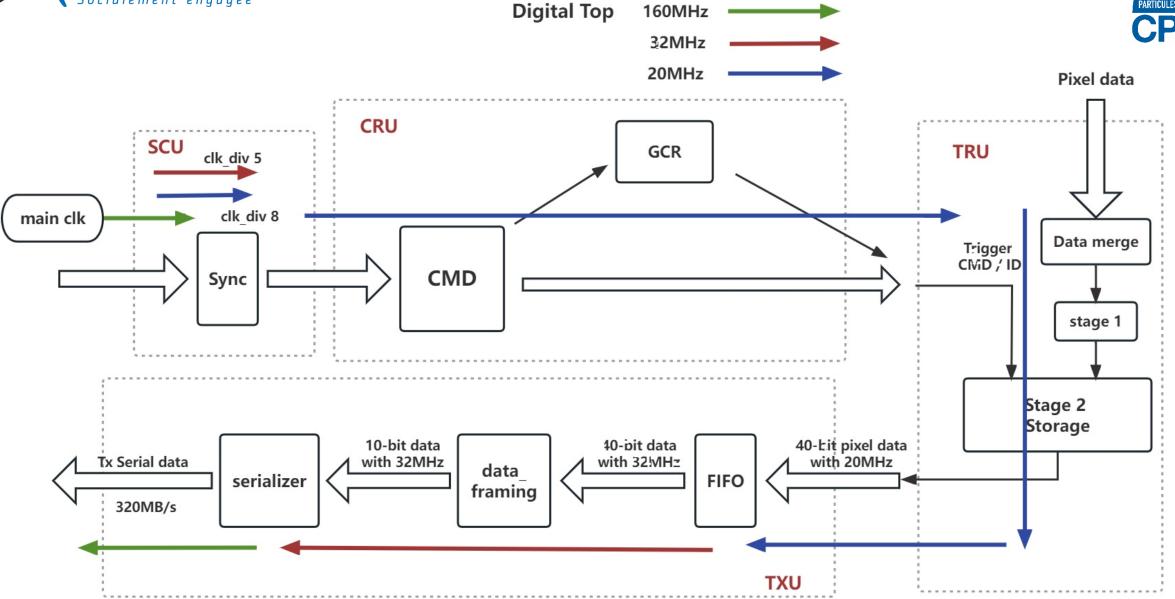

- Module division : 4 main parts

- SCU sync & clk divider: digital clk divider, synchronize circuit & clk divider, RxDat format conversion, main function: clock divider, Rx\_data SIPO synchronization

- 2 CRU Control Unit: Implementation RD53B interface, which almost keeps the same design as TJ-MONOPIX II, main functions: command decoder, global configuration

- **3TRU Trigger Unit**:Manage pixel data from the matrix-EOC and wait for the trigger to pick them for output

- 4 TXU TX Unit: generate output data and sequential output, main functions: data framing, serializer

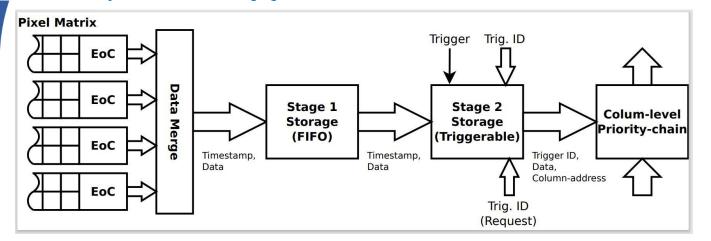

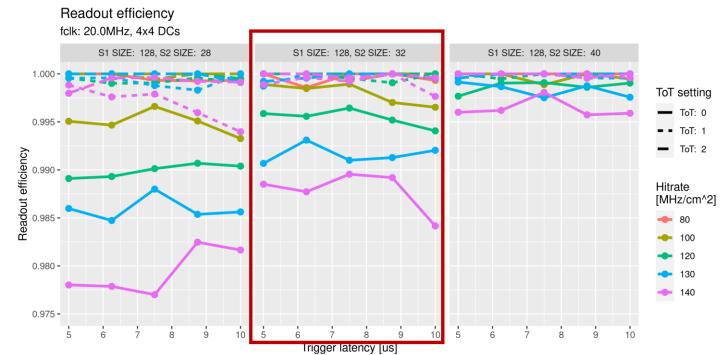

# TRU: trigger unit

14

#### **Trigger Unit**

- A large secondary trigger

- New End-of-column adapted to Belle II trigger

- Timestamped hits stored in memories

- Read-out when timestamps matched with trigger

- Trigger Groups(TRGs) simply process the pixel data to generate BCID packets

- Trigger memory organized in 112 TRGs, each connected to 4 DCs(EoC)

#### **TRU** simulation:

- Simulation included: hit clustering, ToT vs charge

- Trigger latency between 5-10μs

- Can cover hit rate 120MHz/cm²

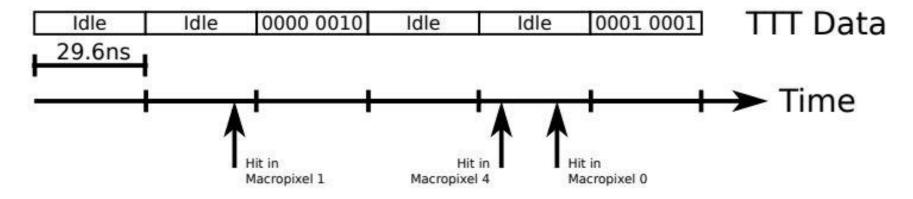

# TTT: track trigger transmission

#### **New trigger features** TTT: Track Trigger Transmission

- Quickly provide the coarse pixel information of all hits to trigger of Belle II

- Allows a Belle II-trigger based on track information

- Low transmission latency required

- Separate transmission logic independent from normal OBELIX readout system (extra LVDS link)

- Power constrains this function to the oVTX

- 2 to 8 logical macropixels per whole chip (configurable, 8 used for simulation)

- 160MHz DDR transmission(320Mb/s, 8b/10b encoded)

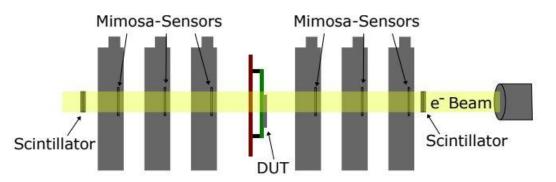

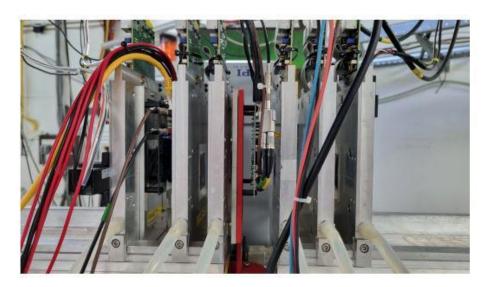

# TJ-Monopix2 Test

16

#### TJ-Monopix2 test :

- Full chacterization on bench: threshold scans, calibrations

- ---- also refer to Lars' talk

- **Test-beams**@DESY: Efficiency/Resolution measurements

- Radiation hardness (NIEL and TID irradiation campaigns in progress)

Setup for BDAQ53 Test – developed by Bonn

Setup for testbeam – @Desy

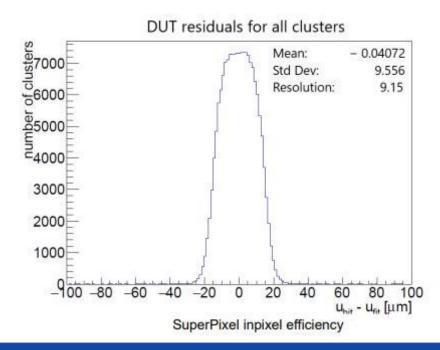

#### Test Beam Results

- Performed at DESY in June 2022:

- Unirradiated chips

- Preliminary settings used, beam e<sup>-</sup> at around 5GeV

- Use very high threshold ~ 550 e<sup>-1</sup>

- Hit efficiency: 99.54 +- 0.04%

- Cluster position residuals: 9.15 μm

#### Test Beam Results

#### SuperPixel inpixel efficiency

Unbiased DUT residuals u for all clusters

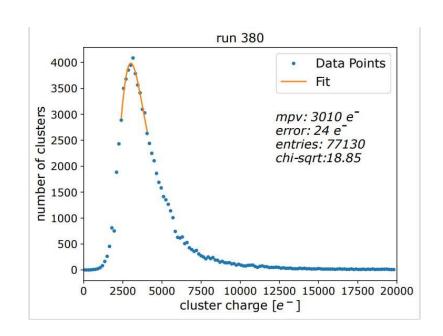

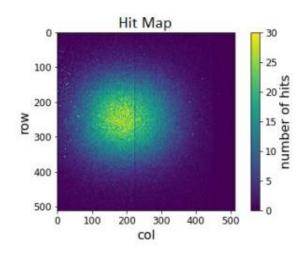

#### New test beam in July 2023:

- Lower threshold settings

- Irradiated chips

- Angle scan

- Data analysis on-going

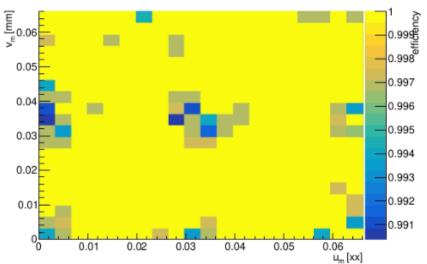

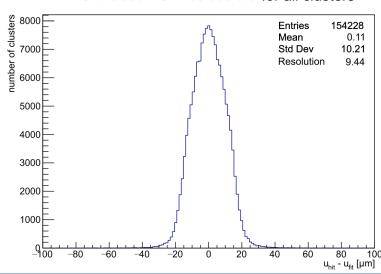

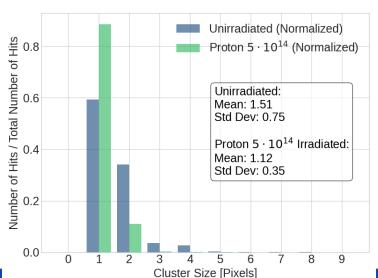

Some preliminary results shown for the irradiated chip at  $5* 10^{14} \, n_{ea}/cm^2$

- Measurements at ~ 310e⁻ threshold

- Efficiency of 99.79% for irradiated chip, with small inefficiency in the pixel corners

- Cluster position residuals : 9.44  $\mu m$  -> about pitch/ $\sqrt{12} \sim 9.5 \ \mu m$  binary resolution

- Decrease in cluster size after irradiation

W02R05 W05R16

23/10/2023

VTX Upgrade for Belle II

### Conclusions

- The new DMAPS VTX will improve the performance of the Belle II vertex detector

- The OBELIX chip is based on the TJ-Monopix2 with TJ180nm technology

- The careful characterization of the TJ-Monopix2 sensor matrix is the key point for the OBELIX design

- Stable module operation over long times and irradiated sensor performance validated in testbeam

#### Outlook

- Analysis of testbeam with irradiated sensors in July 2023 at DESY

- The OBELIX design is in development, with the aim of submitting in Q4 2023 / Q1 2024

- Will contribute to a conceptual design report (CDR) for the Belle II upgrade by Q4 2023 / Q1 2024

20

# Thanks for your attention

21

# Back up slides

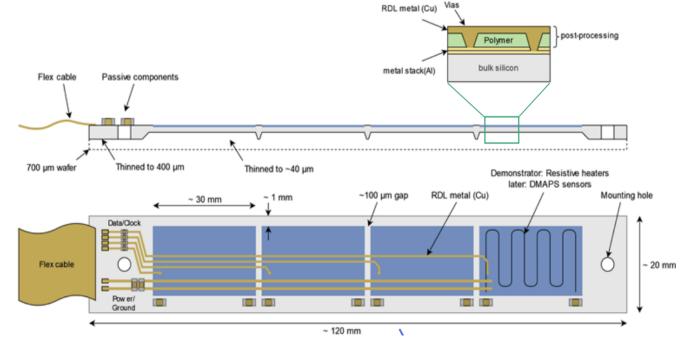

# **iVTX** Demonstrator

#### All-Silicon module concept:

- 4 contiguous sensor block diced

- Hetherogeneous thinning for stiffness

- To interconnet sensors on the ladder, a post processing step etches metal strip on the redistribution layer (prototypes in production by IZM-Berlin)

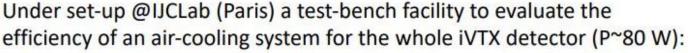

Results from air-cooling simulations on a single ladder: air at 15°C with speed ~10 m/s needed to evacuate a uniform power density of 200 mW/cm², reaching a max. temperature of 20°C.

- heat exchange by convection

- air flow through the actual iVTX geometry

- mechanical vibrations with v<sub>air</sub>~10 m/s to be measured.

Support structure -1 mm

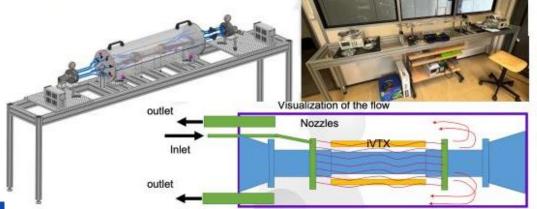

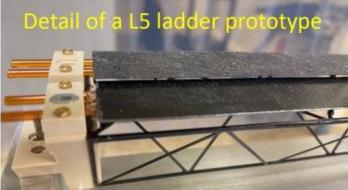

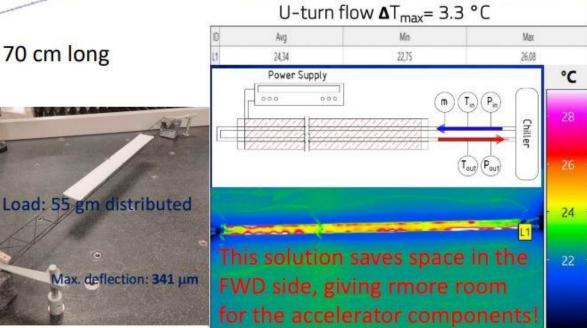

# oVTX Thermomechanics

Ladder structure design inspired by ALICE ITS2, composed of:

CF support structure (truss), cold-plate with pipes for liquid coolant circulation (neg. pressure),

Chip and Flex circuit for power&signal glued on top

Polylanida

Cooling Pipes

L5 ladder: 70 cm long

Performed mechanical characterization of the L5 prototype:

- Distortion: measurements of sagitta (~340 um)

- Vibration: 1st resonance frequency (~250 Hz) (<< earthquake f.)

#### Thermal characterization:

- Used Kapton heaters, inlet (T=10°C) and outlet on one side

- Uniform temperture along the ladder ∆T max=3.3 °C

# oVTX

# TJ-Monopix2 – pixel matrix

25

- 4 pixel Front-End (FE) flavors with differences in preamplifier, sensor coupling and biasing;

- Normal FE => Col\_0 to Col\_223

improved TJ-Monopix I FE, DC coupled pixels

- Cascode FE => Col\_224 to Col\_447

Extra cascode transistor that increase the pre-amplifier gain, the aim is to have 50% reduction of threshold dispersion, DC coupled pixel

- HV Cascode FE => Col\_448 to Col\_479

Front side High Voltage biasing and AC coupled pixel

- HV FE => Col\_480 to Col\_511

Front side High Voltage biasing and AC coupled pixel a variation of the previous one

- Two columns for Analog Monitoring

# **Pixel Matrix: Analog Front End**

26

Normal Front End Design

Cascode Front End Design

# **Pixel Matrix: Analog Front End simulation**

Objective: Reduction of the TJ-MONOPIX2 front-end (FE) preamplifier's power consumption

| Normal FE<br>pixel preamplifier | Improved normal (FE) pixel preamplifier | Cascode FE pixel preamplifier | Improved cascode (FE_casc) pixel preamplifier |

|---------------------------------|-----------------------------------------|-------------------------------|-----------------------------------------------|

| Ibias = 500 nA                  | Ibias= 300 nA                           | Ibias = 500 nA                | Ibias= 300 nA                                 |

| Power consumption = 1μW         | Power consumption = 650nW               | Power consumption = 1μW       | Power consumption =650nW                      |

| Peaking Time = 107,48 ns        | Peaking Time = 129,46 ns                | Peaking Time = 132,85 ns      | Peaking Time = 182,34 ns                      |

| Gain = 1,74 mV/e-               | Gain = 1,53 mV/e-                       | Gain = 3,35 mV/e-             | Gain = 2,81 mV/e-                             |

| SNR = 39,1                      | SNR = 39,13                             | SNR = 56                      | SNR = 57,33                                   |

| ENC = 2,55 e- rms               | ENC= 2,55 e- rms                        | ENC = 1,78 e- rms             | ENC = 1,74 e- rms                             |

The power consumption can be reduced by 35%

# **Pixel Matrix: Analog Front End simulation**

28

- On going: study of reducing the main biasing current in order to have low power dissipation

- Lowering the main biasing current from 500 nA to 300 nA leads to a lowering of the power dissipation by 35% (for both Normal FE and cascode FE).

- However by reducing the current Ibias, we have small variation on peaking time

- The gain of the preamplifier is also reduced but it can be improved by varying the feedback current Ithr

while keeping a signal-to-noise ration (SNR) as high as possible.

The cascode Front End flavor is chosen for OBELIX – so far

Data in

**Priority Control**

Periphery

7-bit BCID Gray Counter

Token out

Global Read

Global Freeze

# OBELIX\_V1: Digital Specifications of Belle II

29

- Main clkin : 160MHz

- General function clk: from 40MHz to 20 MHz;

- Single output at 320Mb/s;

- Area limitation and power consumption;

- New End-of-column adapted to Belle II trigger

- Timestamped hits stored in memories

- Read-out when timestamps matched with trigger

- hit rate ≤ 120MHz/cm2

- RD53B control protocol;

R/O controller

FIFO memory (shutter mode)

Serializer

Encoder

8b/10b

FPGA DAQ

SER Clock

(320 Mhz)

- For IO pins -- LVDS only

- Input --- ClkIn,CmdIn,TTTIn

- Output --- TTTout, DataOut, ClkOut

# OBELIX\_V1 : Digital Data Path

30

# OBELIX\_V1 : Digital Clock Path

31

# OBELIX\_V1 : Digital Clock Path

32

Real situation

| Clock Signal    | Ideal  | MONOPIX  |

|-----------------|--------|----------|

| Main Clock      | 160MHz | 169.7MHz |

| Divider 8 Clock | 20 MHz | 21.2 MHz |

| BCID Clock      | 20 MHz | 21.2 MHz |

| TXU Clock       | 32MHz  | 33.9MHz  |

# Preliminary from simulations

33

how our expected power change with hit rate for different bias and BCID clock scenarios

# VTX simulated tracking performance

• The performance of the tracking on single tracks. The events are just coming from generic events e+ e- producing a pair of B mesons and 'generic' means that we don't care how they decay.

VTX provides better vertex resolution than the current VXD in the decay channel B<sup>0</sup>

34

# TJ-Monopix2 test

VTX Upgrade for Belle II

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE

- Tests done in in Bonn, Pisa, HEPHY, CPPM, Gottingen

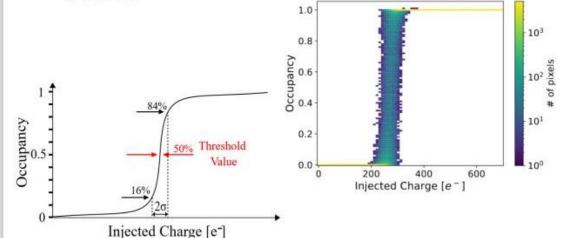

- The internal injection test :

- A deliberate amount of known charge is introduced into the pre-amplifier of the system

- The output generated is then quantified using the Time Over Threshold

- S-curve tests to determine threshold : as the injected charge, at which a 50% occupancy is reached

- The noise level can be determined from the slope of the S-curve

- Beam testing performed at DESY in Jun 2022 (4 GeV e-)

- Unirradiated chips

- Preliminary settings used

- Very high thresholds ~ 550 e-

- Hit efficiency: 99.54 +- 0.04 %

- Cluster position residuals: 9.15 um

- New test beam in July 2023:

- Lower threshold settings

- Angle scan

- Efficiency for irradiated chip  $10^{14}-10^{15}\ n_{eq}\ /\mathrm{cm^2}$

- Data analysis ongoing

36

# Docs & Links:

1. All the previous presetation: VTX talks - Belle II - DESY Confluence

2. VTX official page: <u>VTX sensor - Belle II - DESY Confluence</u>

3. TJ-MONOPIX II: <a href="https://cds.cern.ch/record/2782279?ln=fr">https://cds.cern.ch/record/2782279?ln=fr</a>