# A large area CMOS pixel sensor for particle detection

Liang Zhang<sup>1</sup>

on behalf of

Yang Zhou<sup>2</sup>, Chenxu Wang<sup>3</sup>, Min Luo<sup>3</sup>, Anqing Wang<sup>1</sup>, Leyang Dou<sup>3</sup>, Ruikai Zhang<sup>3</sup>, Guoqiang Yan<sup>2</sup>, Jianing Dong<sup>1</sup>, Mingyi Dong<sup>2</sup>, liangchenglong Jin<sup>2</sup>, Long Li<sup>1</sup>, Qinglin Geng<sup>1</sup>, Linghui Wu<sup>2</sup>, Guangyan Xiao<sup>2</sup>, Meng Wang<sup>1</sup>

<sup>1</sup>Institute of Frontier and Interdisciplinary Science and Key Laboratory of Particle Physics and Particle Irradiation, Shandong University, Qingdao, 266237, Shandong, China

<sup>2</sup>Institute of High Energy Physics Chinese Academy of Sciences, 19B Yuquanlu, 100049, Beijing, China

<sup>3</sup>School of Information Science and Engineering, Harbin Institute of Technology, Weihai 264209, China

# Outline

### Motivation

### □ Wafer-scale CMOS pixel sensor R&D

- ✤ Architecture

- ✤ Pixel circuit

- Digital control and data processing

- Prototype chip

- Readout electronics

- ✤ Wafer thinning and bending

### **Summary**

# **Motivation**

### □ Wafer-scale CMOS pixel sensor using stitching technology

✤ A wafer can be scribed into one die

### □ Attractive features contributing to low material budget

- $\checkmark$  Bending with very thin thickness (~ 50  $\mu m$ )

- ✓ Less support material

- ✓ Need few chips to make a barrel

- Low power consumption

- ✓ The power mainly concentrated on both sides

- ✓ Cooling outside the sensitive area

- ✓ Less electronics required

### □ High potential for particle detection

- Being developed @ CERN for the ALICE-ITS3

- ✤ For the inner tracker of BESIII, CEPC ....

wafer

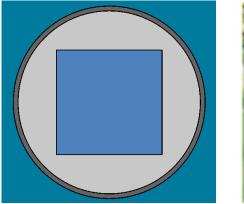

# Wafer-scale CMOS pixel sensor

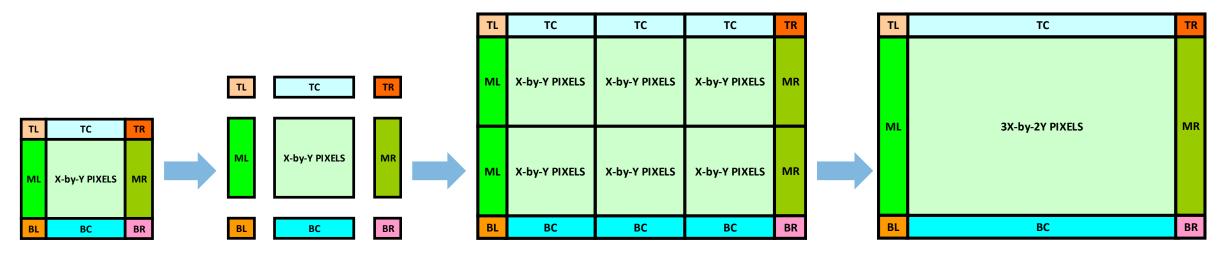

- □ The reticle size of the chip is about few cm<sup>2</sup>

- □ Stitching technique merges multiple structures to realize larger chip

- □ Stitching components

- ✤ 9 segments: TL, TC, TR, ML, MC, MR, BL, BC, BR

- 2-D stitching to make wafer-scale

#### **Reticle size**

# **Chip architecture**

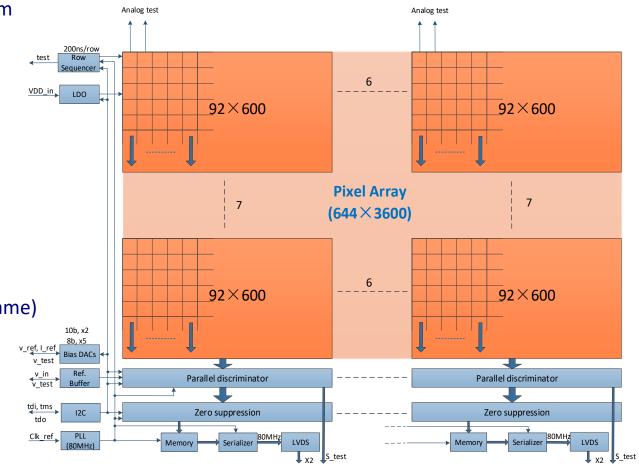

### **350 nm CIS process**

- Epitaxial layer: thickness 14 μm, resistivity 500 2kΩ·cm

- ✤ 4 metal layers

- No deep P-well: PMOS cannot be used in pixel circuit

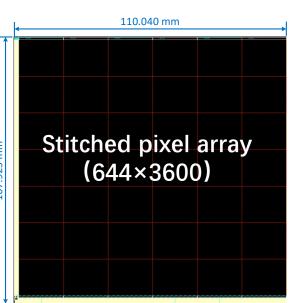

### Total size

☆ ~11×11 cm<sup>2</sup> (only one die in a wafer)

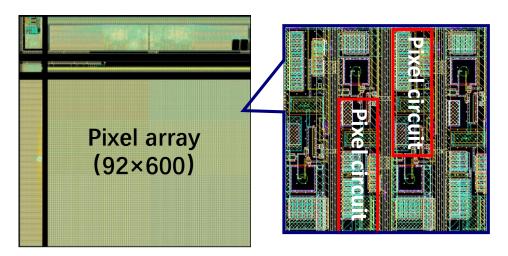

### □ Pixel array (42 segments)

- ✤ Basic pixel array: 92 rows × 600 columns

- ✤ After stitching: 644 rows × 3600 columns

- Rolling shutter readout mode (200 ns/row, ~129 μs/frame)

### □ Full functional chip

- ✤ Analog test point for pixel array

- Column-level discriminator

- On-chip zero suppression

- Interface: Bias DAC/Buffers/I2C/PLL/LVDS/LDO .....

### □ Submitted in Feb 2023

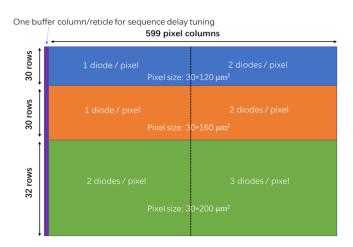

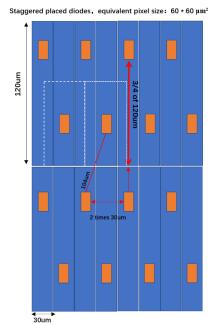

# **Pixel architecture and column readout**

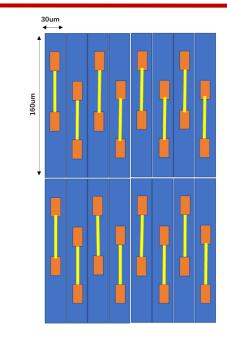

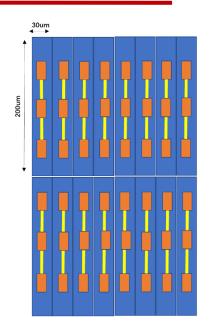

Basic pixel array with 6 submatrices

- \* rφ : 30 μm

- ζ : 120/160/200 μm

□ 6 submatrices: study charge collection and charge sharing

- Different pixel sizes and diode arrangements

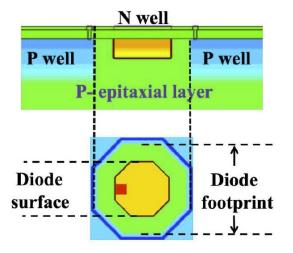

- **Οctagonal diode:** 20 μm<sup>2</sup>

- **Diode surface/footprint:** 0.1

3 different diode arrangements are used

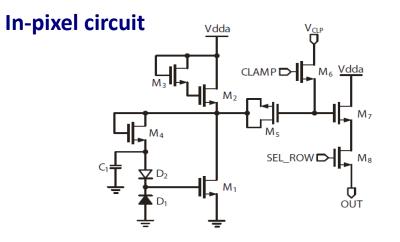

# **Pixel architecture and column readout**

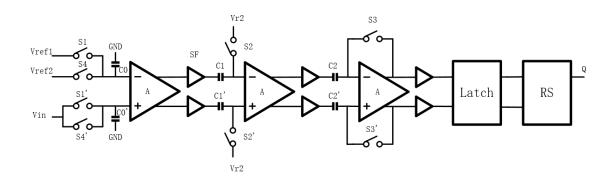

#### **Column-level discriminator**

| Diodes<br>No. | Amp. Gain | SF  | CVF [μV/e <sup>-</sup> ] |

|---------------|-----------|-----|--------------------------|

| 1             | 14        | 0.8 | 135                      |

| 2             | 13.5      |     | 75                       |

| 3             | 11        |     | 40                       |

\*Reference: A.Dorokhov, "Optimization of amplifiers for Monolithic Active Pixel Sensors", IPHC

#### **Discriminator performance:**

- □ Auto-zeroed architecture

- □ Threshold: V<sub>ref1</sub>-V<sub>ref2</sub>

- $\square$  Power consumption: 134  $\mu$ W

- **Δ** Area: 30×290 μm<sup>2</sup>

- $\hfill\square$  Thermal noise: 158  $\mu V$

# **Pixel architecture and column readout**

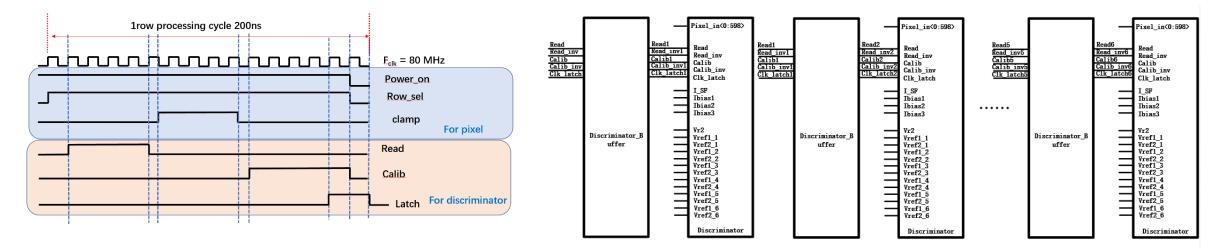

Timing for pixel and discriminator: 200ns @ 80 MHz clock

#### Basic clock 80MHz

- ✤ 200 ns/row

- Readout time: ~ 129 μs/frame

#### **D** Power consumption

✤ ~ 25 mW/cm<sup>2</sup> (pixel matrix area)

Every 600 columns driven by one buffer

Combination of total 3600 column-level discriminators

- Improve driving capability, reduce delay time, keep timing matching

- Threshold voltages Vref1 & Vref2 are divided into 6 groups

- Increase driving capability, reduce settling time

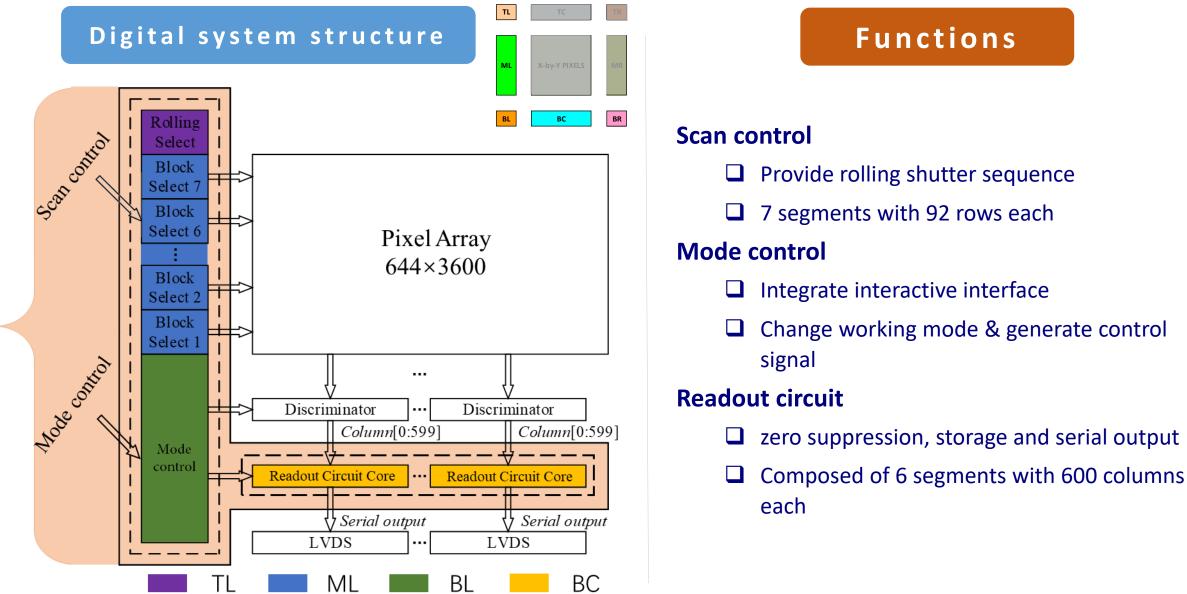

# **Digital control and data processing**

# **Digital control and data processing**

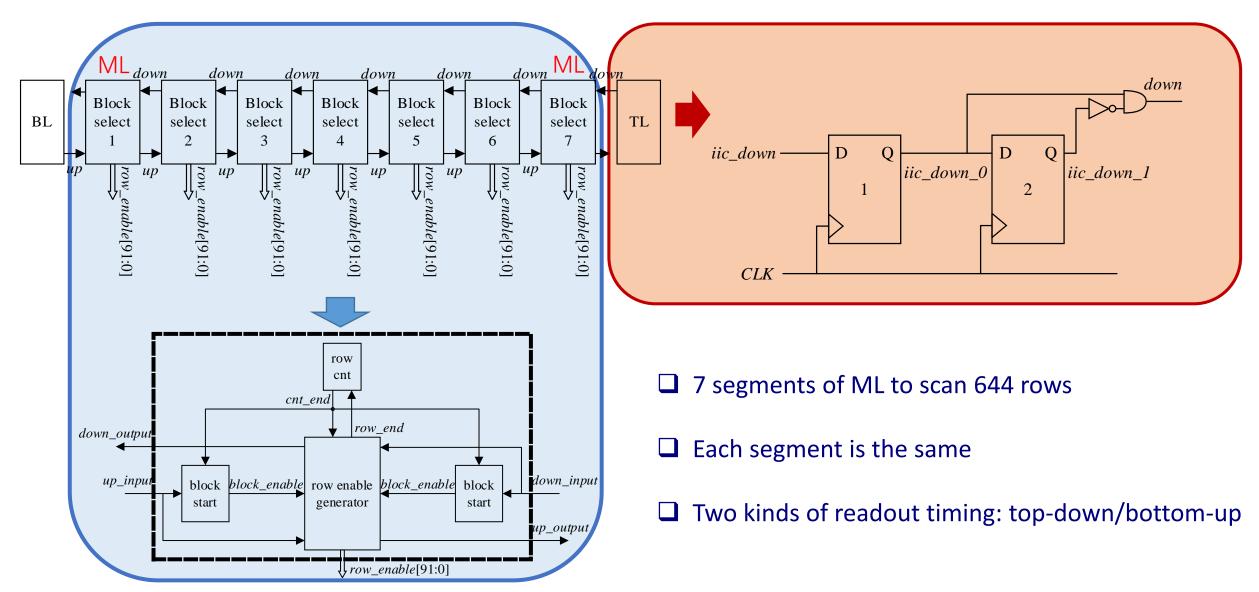

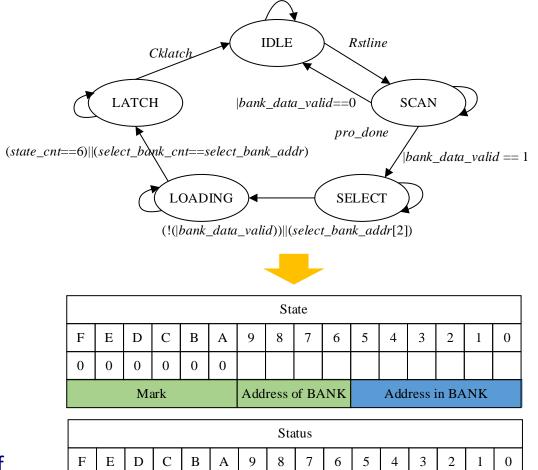

### **Digital control and data processing –** scan control

# **Digital control and data processing** – readout circuit

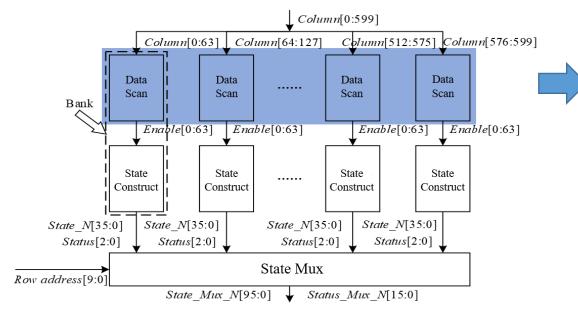

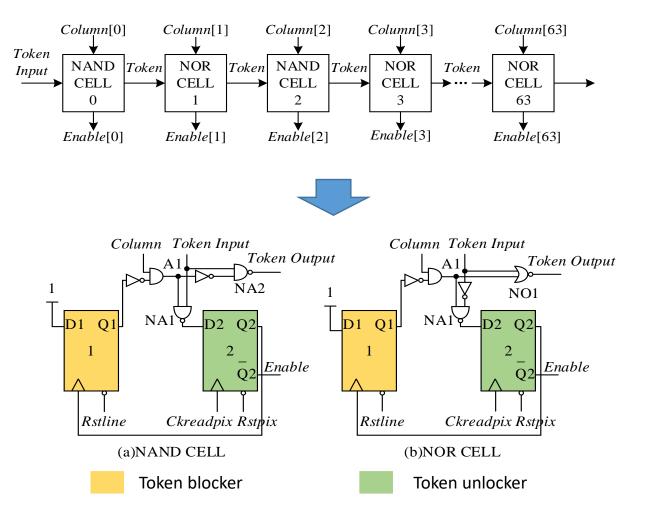

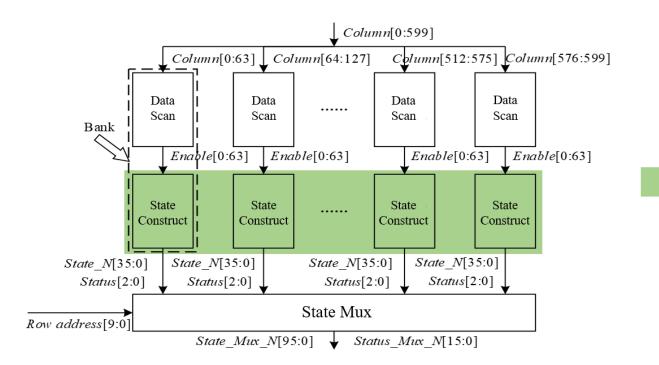

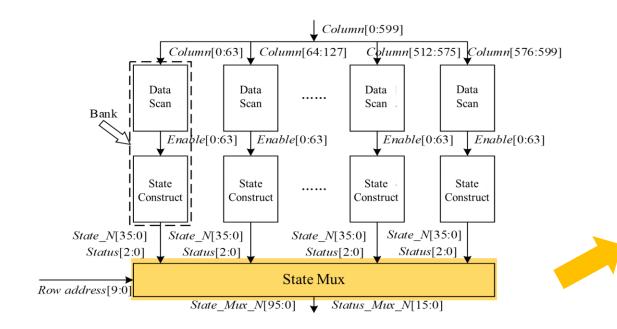

- □ The column outputs are divided into 10 groups, each group consisting of data scan and state construct.

- □ **Token blocker:** if there is a signal in the column, the token is blocked.

- □ **Token unlocker:** if the token is blocked, 'enable' is valid and the token is unlocked after the next input arrives.

- Through the token chain, the hit is readout one by one with a 64-bit data format.

# **Digital control and data processing** – readout circuit

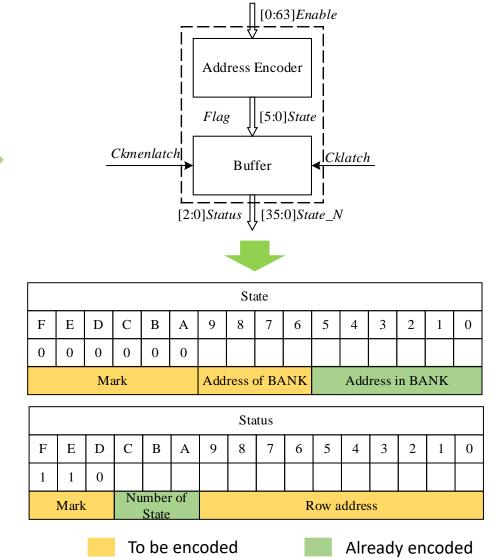

- Address encoder: encode the 64-bit wide Enable signal into a 6-bit wide state.

- **Data buffer:** collect all the states in a bank and encode into status.

# **Digital control and data processing** – readout circuit

- State mux: Add Row and BANK address to status and state, respectively

- Data compression ratio: according to the physics environment, there are maximum 40 pixels in a column of reticle. 77: 1

Number of

State

0

1

Mark

Row address

# **Prototype chip**

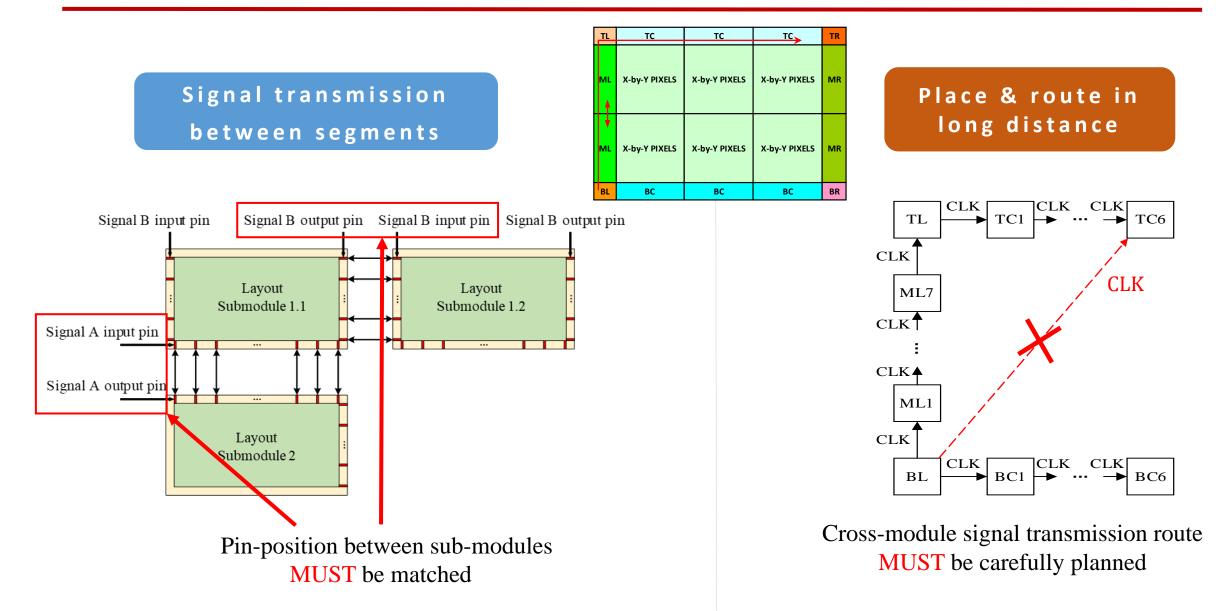

### **Reticle floorplan**

- ✤ Area: ~ 2 × 2 cm<sup>2</sup>

- 9 groups of modules

- > TL,TC,TR,ML,MC,MR,BL,BC,BR

- $\succ$  Pixel array in a reticle: 92  $\times$  600

# □ Stitching

- ✤ Area: ~ 11 × 11 cm<sup>2</sup>

- ✤ Pixel array

- 7 rows and 6 columns

- Total pixel array: 644 × 3600 §

TR

MR

BR

тс

X-by-Y PIXELS

BC

TL

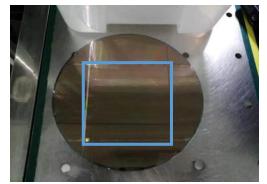

#### 8 inch wafer (die size 11 cm × 11 cm)

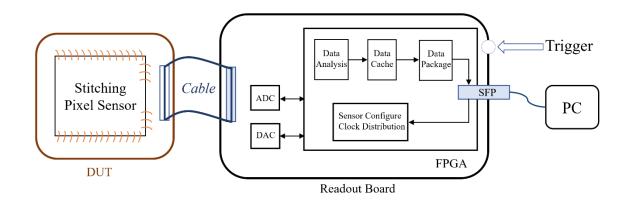

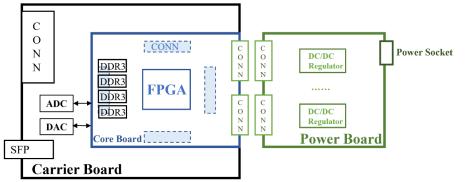

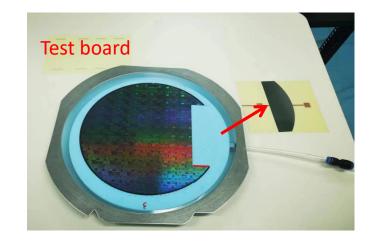

### **Readout electronics**

### **DUT board**

Few components, connector, wire bonding

### Readout board

- FPGA core board: XC7K325T, DDR3

- ✤ Carrier board: ADC, DAC

- Power board: supply different voltages

- ✤ The chip is under testing

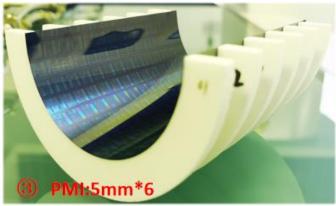

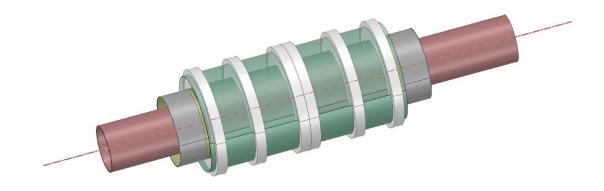

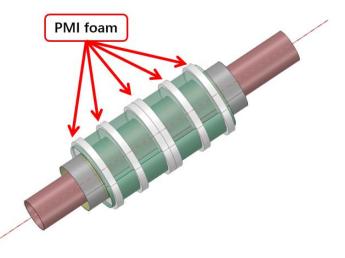

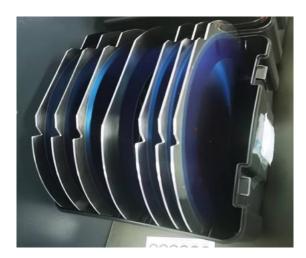

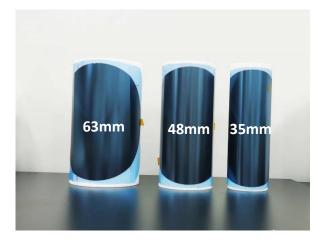

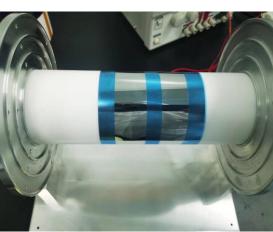

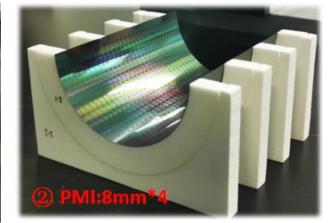

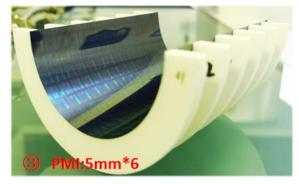

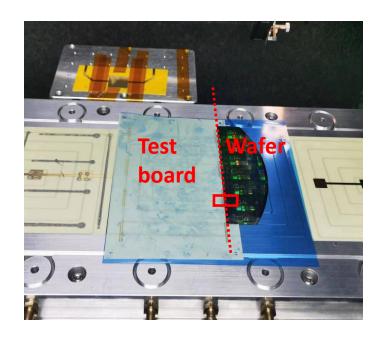

# Wafer bending and bonding study

- **Dummy wafer is thinned down to 50 μm**

- □ Wafer bending with different radii

- **Ring support**

- Wafer bending and fixed with glue

- PMI: high strength, low material, mass density is about 0.05g/cm<sup>3</sup>

Wafer bending with radii 63mm, 48mm and 35mm

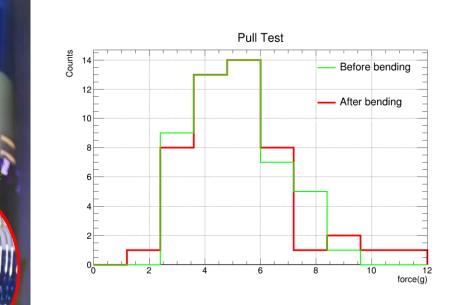

# Wafer bending and bonding study

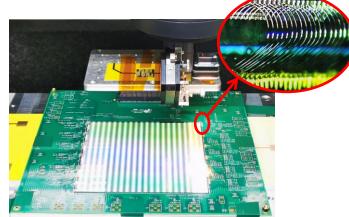

### □ Wire bonding with thinned dummy wafer

- Dicing a part of dummy wafer

- Wire bonding with test board

- The wire shape doesn't change after bending

- The pull test shows not much change

### Summary

- The thinned wafer-scale CMOS pixel sensor will have extremely low material budget, having a high potential for the inner tracker.

- □ A wafer-scale prototype sensor has been developed, and now is under testing.

- □ Wafer thinning and bending have been done, and they perform well so far.

### Acknowledgements

This work was supported by the National Natural Science Foundation of China (NSFC) under Grant U2032203, Grant 12075142 and Grant U2106202.

# **Thanks**