# **Exploration of a 55nm HV-CMOS process for the CEPC silicon tracker**

Yang ZHOU<sup>1</sup>, WeiGuo LU<sup>1</sup>, Mei ZHAO<sup>1</sup>, Zhuojun Chen<sup>4</sup>, Kunyu Xie<sup>1</sup>, Leyi Li<sup>1,5</sup>, Ruoshi Dong<sup>1,2</sup>, Hui Zhang<sup>2</sup>, Ivan Peric<sup>2</sup>, Xuekang Li<sup>6</sup>, Xinyang Guo<sup>6</sup>, Chen Yang<sup>6</sup>, Hongbo ZHU<sup>3</sup>, Jianchun Wang<sup>1</sup>, Yiming Li<sup>1</sup>

<sup>1</sup>State Key Laboratory of Particle Detection and Electronics, Insitute of High Energy Physics, CAS, Beijing 100049, China <sup>2</sup>*Karlsruhe Institute of Technoogy, Karlsruhe, Germany*

<sup>3</sup>Zhejiang University <sup>4</sup>Hunan University <sup>5</sup>Shangdong University <sup>6</sup>Dalian Minzu University

#### zhouyang@ihep.ac.cn

## ABSTRACT

To explore process for next generation HV-CMOS pixel sensors, a prototype was designed and submitted in August 2023 using a 55nm HV-CMOS technology with a  $1k\Omega \cdot cm$  substrate. This prototype includes a guard ring with a width of 170µm, a  $32 \times 20$  pixel-matrix, and 5 diode arrays. The pixel matrix comprises 6 flavor charge sensing diodes with a constant pixel size of  $40\mu m \times 80\mu m$ . Charge sensing amplifier

## Guard ring & pixels

and discriminator are integrated in pixels. The peripheral block includes row/column

selection, bias DACs, a bandgap reference, and readout buffers.

## **INTRODUCTION**

Monolithic Active Pixel Sensors (MAPS) utilizing a specialized High-Voltage CMOS technology (HV-CMOS) have proven to be a promising choice for the CEPC silicon tracker. By applying a high reverse bias voltage (> -50V) to a highly resistive substrate (>a few hundreds of  $\Omega \cdot cm$ ), it becomes possible to create a depletion depth of a few tens of microns. This results in superior time resolution and enhanced radiation hardness compared to standard CMOS processes.

Over the past decade, the development of HV-CMOS MAPS has primarily focused on the 180/150 nm processes. Transitioning to a smaller technology node not only enhances the current design's performance (power dissipation, readout speed, TID, etc.) but also opens up new possibilities. With a smaller technology node, more transistors and functionalities can be integrated into each pixel.

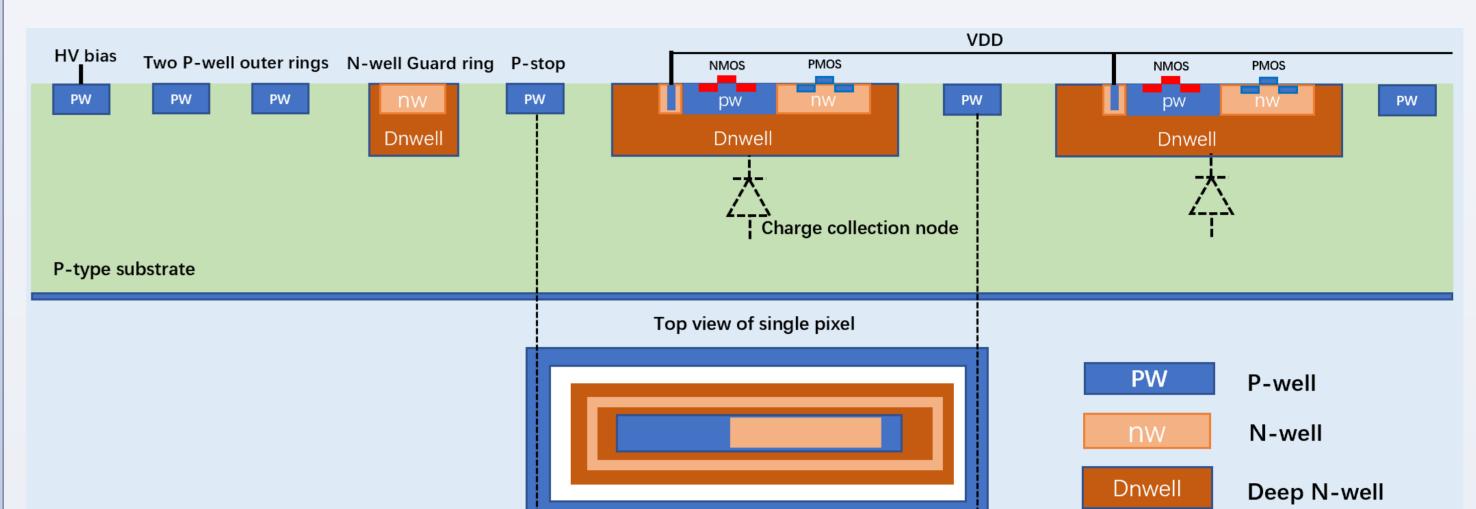

#### Figure: Cross-section and top view of the guard ring and pixel design.

Table: 6 flavor charge sensing diodes comprised in the section 1&2.

| <b>Diodes flavor</b> | Specifications                              |                |

|----------------------|---------------------------------------------|----------------|

| Pix_D10core          | Single DNW size: $30\mu m \times 70\mu m$ , | With P stop    |

| Pix_D10core_wps      | distance between two diodes 10µm            | Without P stop |

| Pix_D15core          | Single DNW size: $25\mu m \times 65\mu m$ , | With P stop    |

| Pix_D15core_wps      | distance between two diodes 15µm            | Without P stop |

| Pix_D20core          | Single DNW size: $20\mu m \times 60\mu m$ , | With P stop    |

| Pix_D20core_wps      | distance between two diodes 20µm            | Without P stop |

## **Charge Sensing Amplifier & Discriminators**

## **PROCESS SPECIFICS**

HV-MAPS

Θ

P-type substrate

Depleted zone

Charge collection node

- **5**5nm High-Voltage CMOS process;

- $\square$  1k $\Omega$ ·cm p-type substrate;

- **□** Custom designed IO;

- $\square$  Core power: 1.2V;

- □ Triple-well process: n/p/deep n-well;

- $\Box$  Deep n-well/p-substrate breakdown Voltage > 50V;

- **1**0-metal layers is possible for fine pitch routing, including 2 thick metal layers for power;

### Layout of the submission

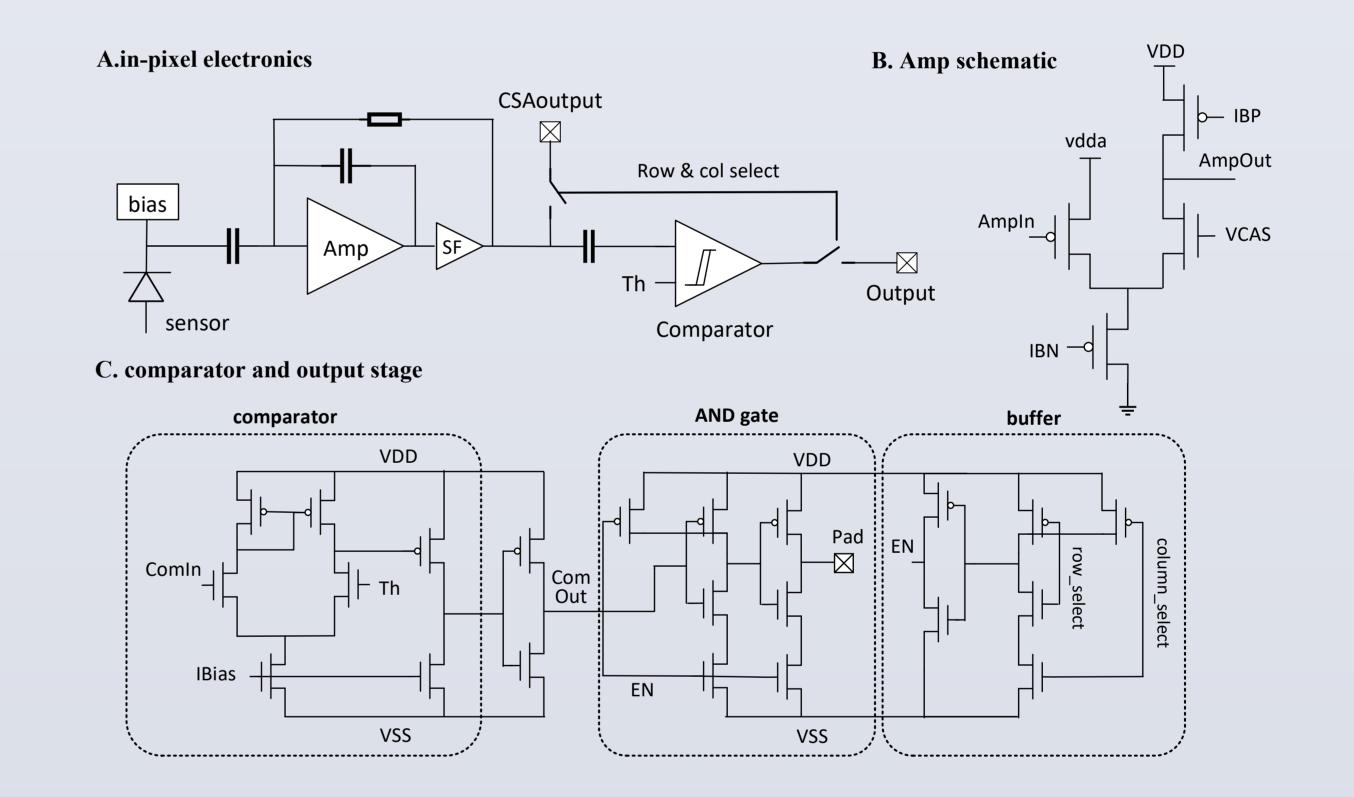

Figure: One version in-pixel electronics in the 1<sup>st</sup> section (two different versions in total). Both the analogue and digital signals are output.

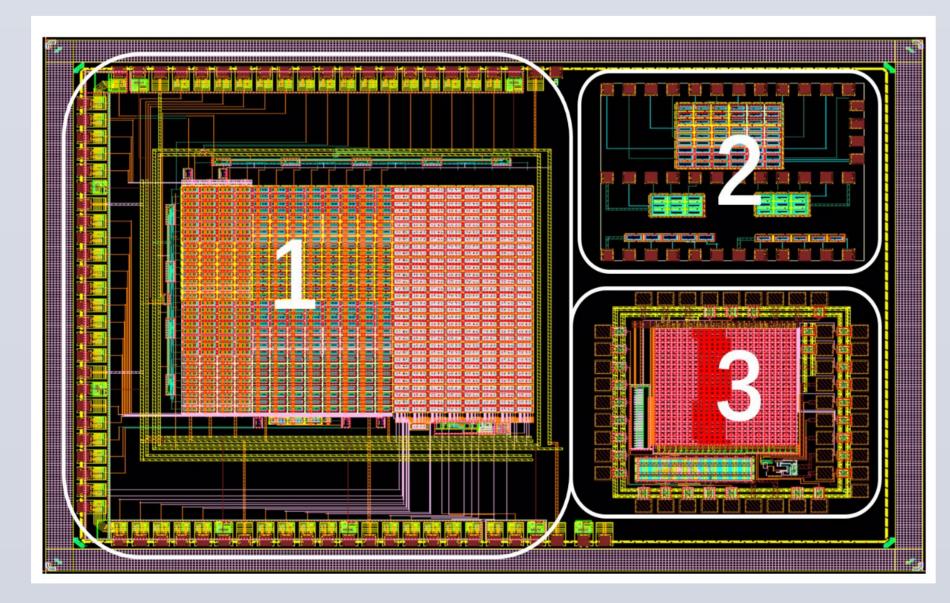

Figure: layout of the first submission on the 55nm HV-CMOS process. 3 independent sections are included for different purpose. The whole chip size is  $4\text{mm} \times 3\text{mm}$ .

$\square$  1<sup>st</sup> section: a 32×20 pixel matrix comprises various diodes and in-pixel amplifier and discriminator design for process validation;

$\square$  2<sup>nd</sup> section: 5 diode array for charge sensing diodes I-V/C-V study;

$\square$  3<sup>rd</sup> section: a 26×26 pixel matrix with relative digital readout periphery for new electronics structure study; (Hui Zhang's talk & Ruoshi Dong' poster)

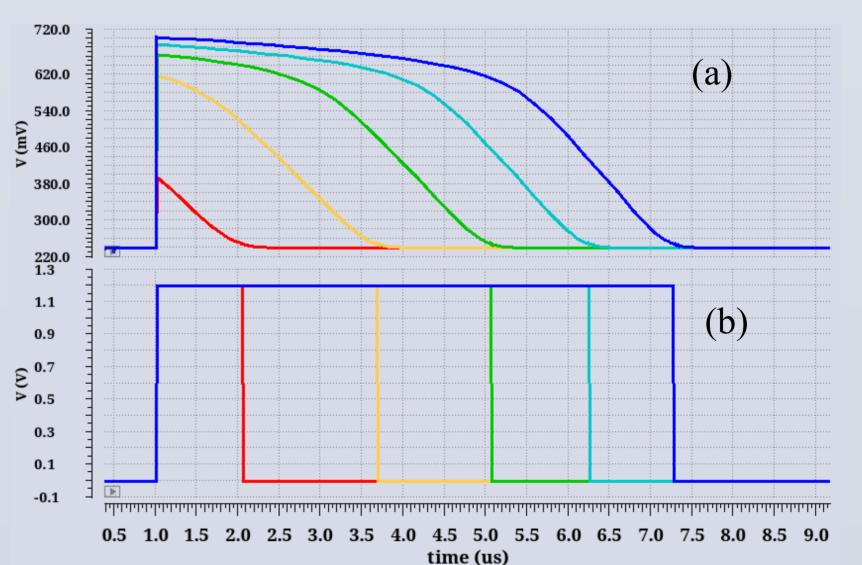

Figure: Output transients voltage of the output of (a) CSA, (b) the discriminator for different charge varied linearly between 2ke<sup>-</sup> and 18ke<sup>-</sup> in 4ke<sup>-</sup> steps (simulation results, C<sub>input</sub>= 150fF)

## **CONCLUSION AND PERSPECTIVES**

The initial submission utilizing the 55nm HV-CMOS process was completed in August 2023. It incorporated various versions of charge sensing diodes, in-pixel electronics, and readout structures. Currently, efforts are underway for preparation of design validation. The forthcoming test results are anticipated to offer vital insights, serving as essential benchmarks for the future advancement of HV-CMOS pixel sensors for the CEPC tracker.