# 十二月研究生季度考核

学生: 裴文溪

导师:季筱璐

专业: 计算机技术

时间: 2023年12月28日

#### 报告提纲

- ◆ TAO-TVT模拟数据源的开发

- ◆ TAO-CD波形读出软件的开发

- ◆ 其他工作

- ◆ 后续工作

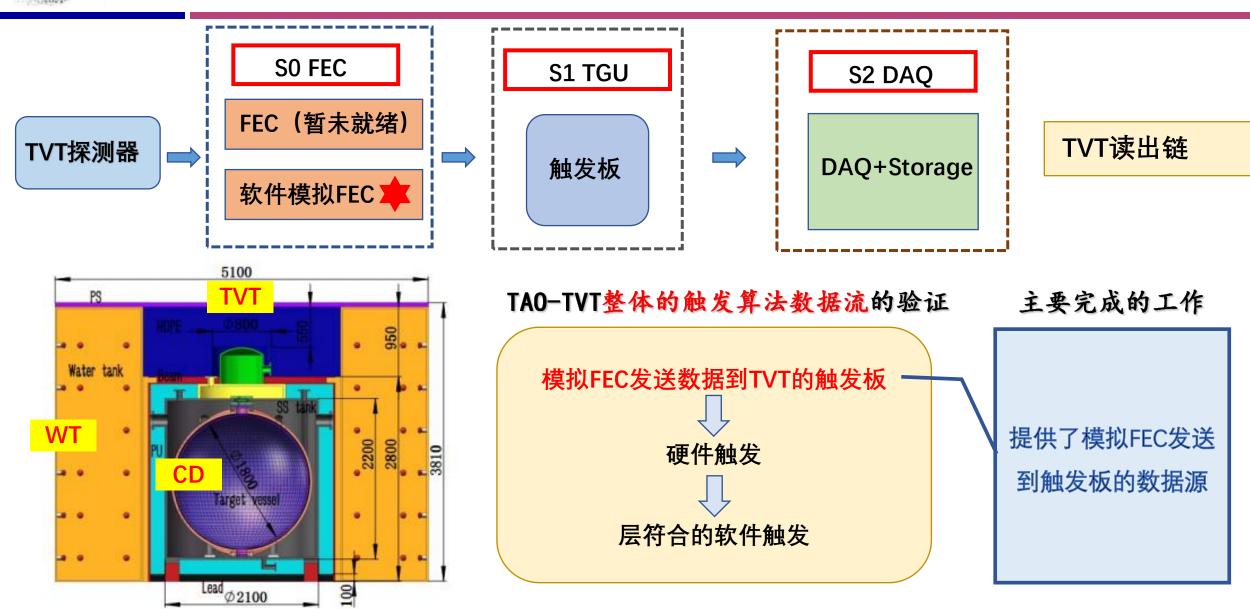

#### 验证TAO-TVT触发算法的链路

#### 模拟TAO-TVT的数据源的开发

#### FEC数据格式

| Header (0XFE)                             | FEC ID[7:0]<br>0-255 | 0 | Channel ID[6:0]<br>0-127 | Status[3:0]<br>Reserved                                  | OF1 OF2<br>Q(Charge) S (sample)<br>over<br>flow flow | Integral window width[9:0]<br>Up to 1024 points | Charge[23:0]<br>sum up to 512 half amplitude points (2us) |                                |

|-------------------------------------------|----------------------|---|--------------------------|----------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|--------------------------------|

| Pedestal[11:0]<br>LSB = 1.8V/2^12≈0.439mV |                      |   |                          | Coarse Timestamp[47:0] Unit=1ns, Up to 2^48ns ≈ 78 hours |                                                      |                                                 |                                                           | Fractional<br>Timestamp[-1:-4] |

#### ➤ TAO-TVT 模拟FEC发送

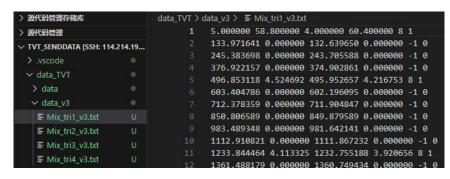

根据<mark>模拟得到的root格式的事例数据</mark>(包含噪声数据和有效事例数据) 组装成指定格式的FEC数据发送到TVT的触发板卡

图1 仿真得到的事例数据

图2 发送并存盘的模拟FEC数据

图3 触发板卡收到的FEC数据

#### TAO-TVT触发算法的数据流的正确性

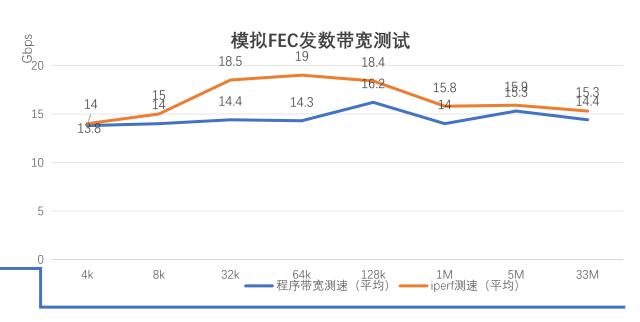

| 服务器名    | hd102(发送方)                                   | hd103(接收方)                                   |  |  |  |

|---------|----------------------------------------------|----------------------------------------------|--|--|--|

| CPU型号   | Intel(R) Xeon(R) Gold<br>6226R CPU @ 2.90GHz | Intel(R) Xeon(R) Gold<br>6226R CPU @ 2.90GHz |  |  |  |

| CPU逻辑核数 | 64                                           | 64                                           |  |  |  |

| 网卡      | 25 x 2 Gbps网卡                                |                                              |  |  |  |

#### 经测试满足千兆连接的上限

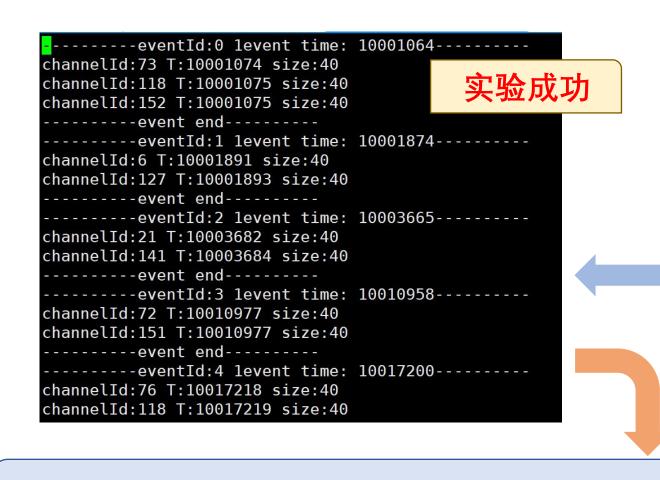

#### 模拟FEC数据发送的程序自检

- 自发自收接收方收数存盘

- 将存盘的数据解析

- 同FEC数据格式和原始数据进行检查

● 程序成功运行

#### 已经完成√

- 对比原始文件检查发送到触发板的数据

- 实验证明发送的数据格式符合FEC的设计

#### TAO-TVT触发算法的数据流的正确性

模拟FEC发送

硬件触发

软件触发

主要内容

帮助系统提前验证功能

实验结果说明模拟数据源可以成功驱动整个 自检数据链的验证

发现硬件触发确实存在问题

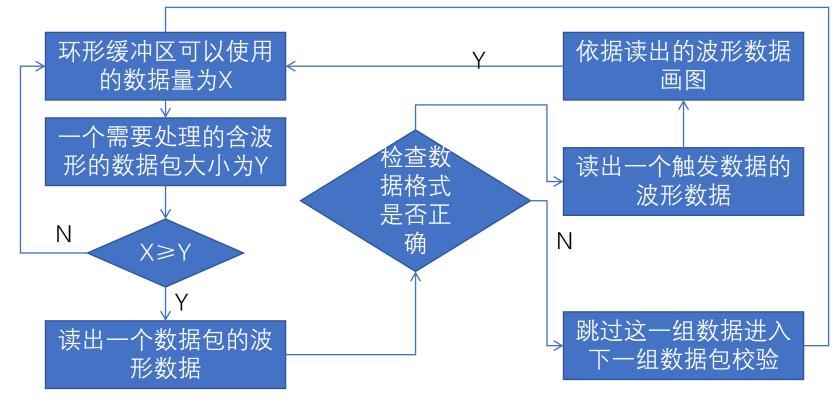

#### TAO-CD的波形读出软件 ——增加环形缓冲区

### 波形读出软件

- ◆数据读出线程

- ◆数据存盘功能

- ◆数据检查线程

- ◆波形显示线程

#### 环形缓冲区优点

- ◆ 避免线程并发的安全问题

- ◆ 无需增加互斥访问机制

- ◆ 提高线程访问环形缓冲区效率

### 已经完成

对比环形缓冲区和共享内存的方式后选择了更为灵活高效的环形缓存区方式

图为环形缓冲区运用到波形读出的逻辑

## 5

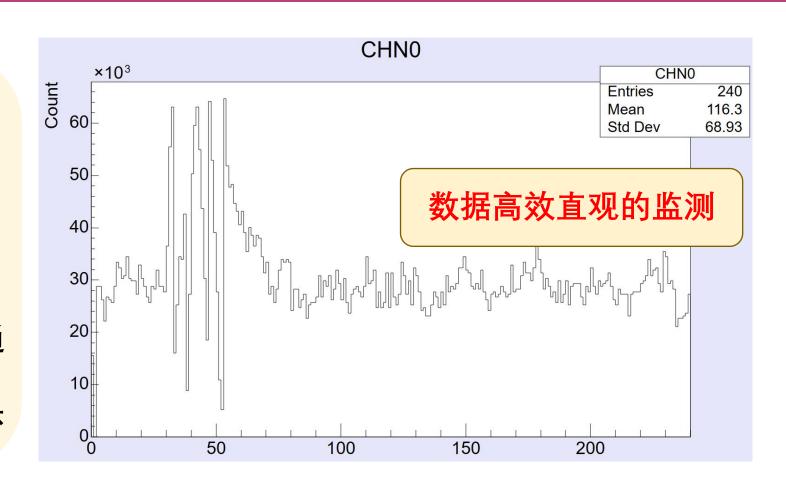

#### TAO-CD的波形显示功能

使用工具: ROOT

#### 目前完成的工作

- 读出线程和检查线程解耦

- 已经接入模拟数据源测试跑通

- 十六个通道波形已经成功显示

现已可以实现将FEC波形数据读出来的同时并且显示出来

- · 学习CUDA的相关内容

- 了解组内相关工作

- 配置实验所需环境

- 协助电子学进行联调

- 完善波形读出的页面布局等问题

- 协助前端电子学的联调

- 着手调研论文准备开题

- 完成其他后续工作

## 感谢各位老师, 请批评指正