## CEPC顶点探测器原型样机的预研制

### 张颖

中国科学院高能物理研究所

On behalf of the CEPC Vertex detector group

中国物理学会高能物理分会第十四届全国粒子物理学术会议 2024年8月13-18日

## 项目背景

- 环形正负电子对撞机(CEPC)物理目标

- ▶ 味物理(b/c夸克喷注,区分b/c衰变顶点)

- 希格斯物理(H-> cc/gg分析)

#### 需要高空间分辨率、低物质量顶点探测器

- 国家重点研发计划项目(CEPC MOST2)目标

- 研制硅顶点探测器原型样机

- ▶ 空间分辨率 < 3~5 µm</p>

- ▶ 抗辐照能力TID > 1MRad

CEPC 项点探测器 CDR (2016)

CEPC MOST2项目 第一款原型样机

## 顶点探测器原型样机的研发

#### ■ 主要技术

- ▶ 高颗粒度像素传感器芯片设计技术 → 高空间分辨率

- 抗辐照设计技术

- ▶ 模块生产和组装技术

# 原型机组装与束流测试

# 像素传感器芯片设计

模块设计与组装

## CMOS单片式像素传感器芯片——TaichuPix

- 设计动机:现有芯片无法同时满足灵敏区面积、空间分辨率和读出速率的需求,需要定制化设计像素探测器芯片

- 主要设计挑战

- ▶ 小像素尺寸→ 高空间分辨率(3-5 μm)

- ▶ 高计数率 → 适应CEPC z pole高亮度运行(最高击中率36 Mbps/cm²)

- ▶ 抗辐照能力: >1 MRad/year

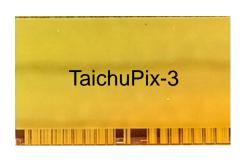

- 完成三轮原型芯片的研发(采用180 nm CMOS 工艺)

- ▶ 小尺寸 (5 mm × 5 mm )芯片: TaichuPix-1和TaichuPix-2,用于可行性和功能验证

- ▶ 全尺寸芯片: TaichuPix-3,全功能芯片,安装至第一款顶点探测器原型样机

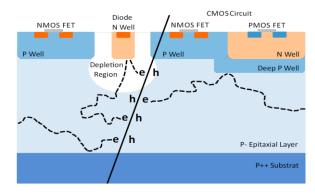

CMOS单片式像素传感器像素截面图

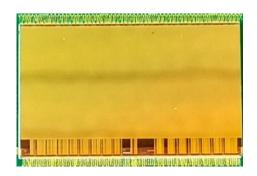

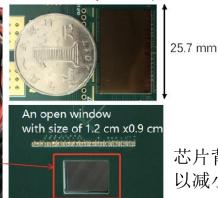

TaichuPix-3  $(15.9 \times 25.7 \text{ mm}^2)$

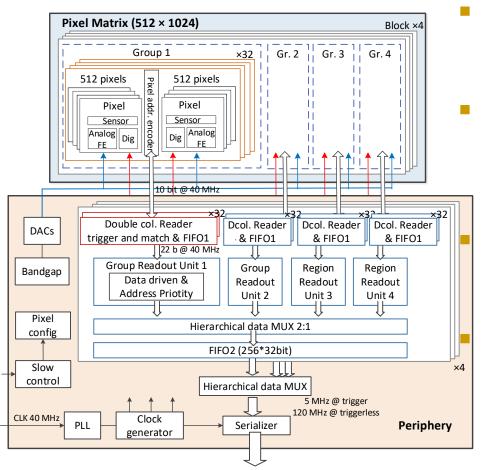

### TaichuPix 芯片读出架构

TaichuPix-3读出架构

#### 像素尺寸25 μm × 25 μm

- 像素内集成连续读出模拟前端电路和甄别器

- ▶ 快速读出数字逻辑,并配有屏蔽及测试功能模块

#### 像素阵列采用双列排布式读出

- ▶ 基于优先逻辑的数据驱动式读出

- > 列端产生每列的时间戳

- ▶ 读出时间: 同列每像素需50 ns,不同列并行读出

#### 两级 FIFO缓存结构

- L1 FIFO: 缓存列端数据

- ▶ L2 FIFO: 匹配读出电路和数据接口速率

#### 兼容触发和非触发数据读出模式

- ▶ 非触发模式:读出所有击中数据,支持3.84 Gbps 数据接口

- 触发模式: 仅输出时间戳与外部触发信号匹配的 数据

#### 片上集成独立工作需要的所有功能模块

▶ 偏置产生, LDO, 慢控,时钟产生器等等

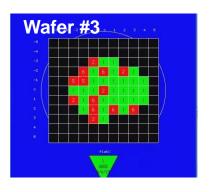

## 全尺寸芯片: TaichuPix-3

- 共生产12片8寸晶圆

- 对晶圆进行了探针台测试、减薄(初步至150微米)和划片

8寸晶圆

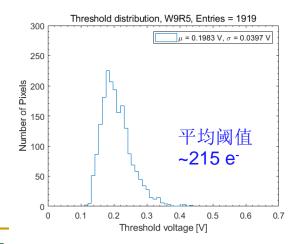

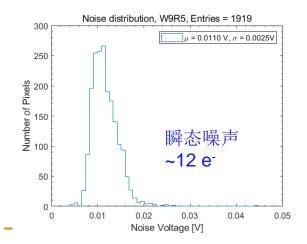

晶圆裸片测试结果 (成品率约~67%)

经减薄和划片后的晶圆

- > 对TaichuPix-3芯片进行了实验室测试

- 功能测试

- 电学性能测试

- 放射源测试

- 辐照测试

## TaichuPix-3 束流望远镜测试

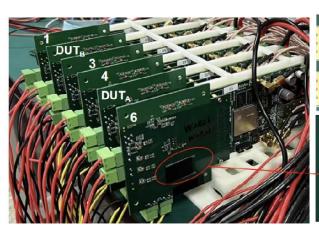

- 研制了基于6层TaichuPix-3芯片的束流望远镜系统

- ▶ 每层包含TaichuPix-3芯片,芯片绑定板、FPGA 读出板

芯片背面PCB开孔,

以减小物质量

6层TaichuPix-3 望远镜

#### ■ 在DESY完成束流测试

- ▶ 束流能量: 4 GeV 电子束

- ▶ 测试了多个被测器件(DUT)

- 分析束流测试数据:空间分辨率、 探测效率

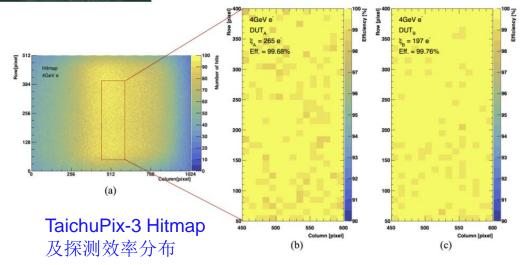

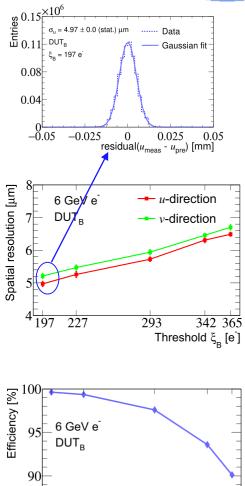

## TaichuPix-3 芯片束流测试结果

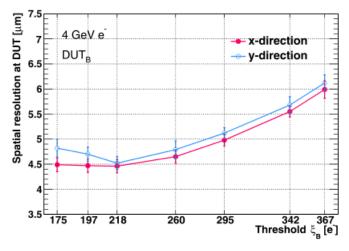

#### ■ 空间分辨率

- ▶ 随像素阈值减低而提高,得益于簇团尺寸变大

- » 可以实现优于5 μm的空间分辨率, 最佳 4.5 μm

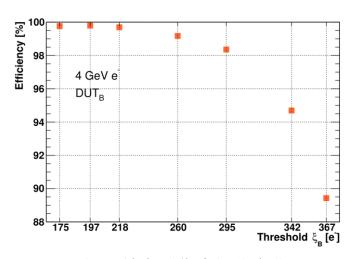

#### ■ 探测效率

- 随阈值增加而降低

- > 空间分辨率为4.5 μm 情况下,探测效率高于99.5%

空间分辨率随像素阈值变化

探测效率随像素阈值变化

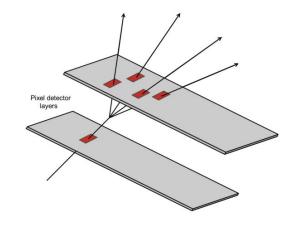

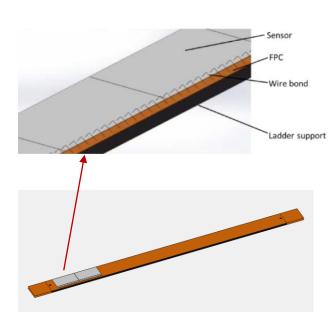

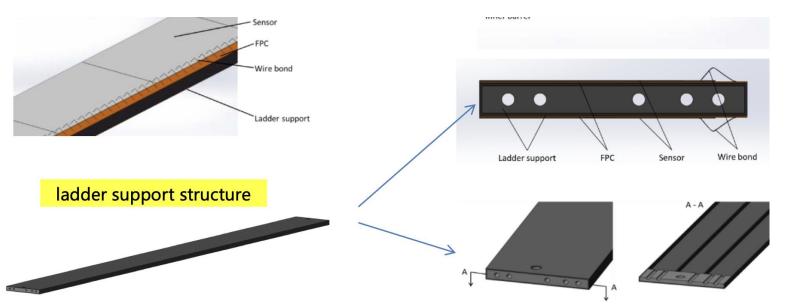

## 探测器样机模块 (Ladder) 设计

- 探测器模块(Ladder)的组成:传感器芯片+柔性电路板(FPC)+碳纤维支撑结构

- » 双面ladder: 支撑结构正反两面均有传感器

- ▶ 10颗TaichuPix-3芯片粘贴并打线至FPC,两条FPC粘贴至支撑结构正反两面上

- ▶ FPC为芯片传输信号、时钟、控制线和电源,在FPC端部由连接器传输至后端读出板

#### ■ 挑战

- ▶ 柔性电路板FPC长度达55 cm,导致电源和高速信号的传输具有设计挑战

- ▶ 物质量低要求金属层数少、电源/地线布线空间有限,引起屏蔽及电压降等问题

- ▶ FPC长度大,厚度小(0.16-0.27 mm),加工难度大、周期长

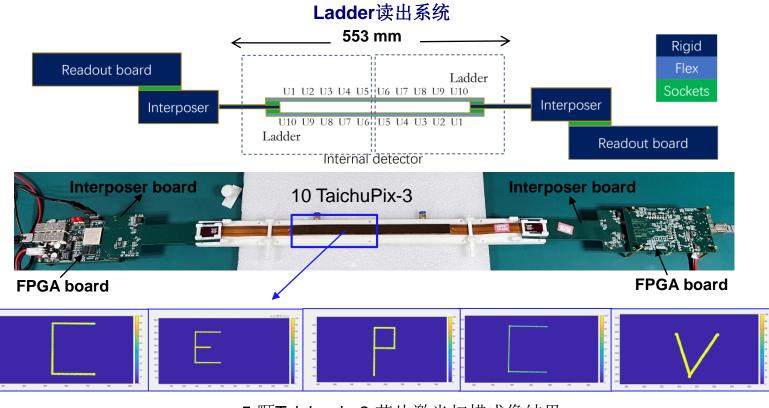

### Ladder读出

- Ladder采用双端读出方式,单面ladder信号由两个基本读出单元处理

- ▶ 一个基本读出单元包括: FPC上5颗芯片+转接板(interposer board)+FPGA读出板

- ▶ Ladder左右两端的正反两面读出单元共用一套转接板和FPGA读出板

- 在实验室验证了装有10颗TaichuPix-3芯片的ladder的基本功能

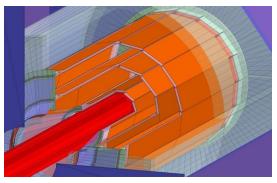

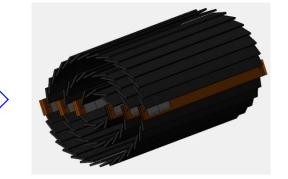

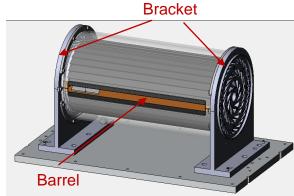

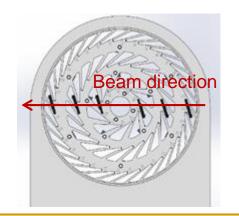

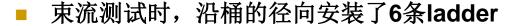

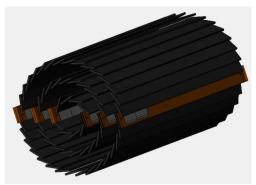

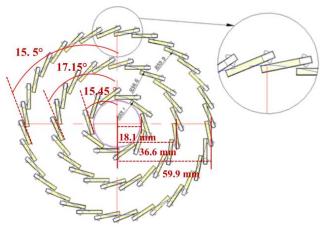

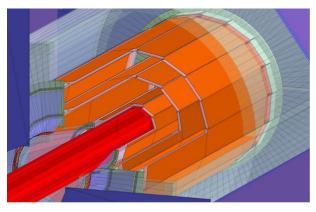

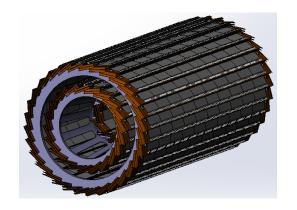

### 原型机的机械结构

- 全尺寸机械结构

- ▶ 三层圆筒,由内到外每层可分别放置10,22,32条ladder

- 三层桶半径,~18.1 mm,36.6 mm,59.9 mm

- ▶ 每条ladder与竖直方向存在一定夹角

- ▶ DESY可提供的最大東斑面积是2.5 cm × 2.5 cm

- ▶ 束流依次穿过6条ladder,包含24颗像素芯片

碳纤维支撑结构

#### Ladder支撑结构 3D 模型

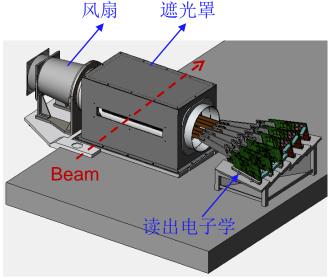

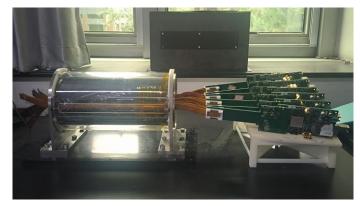

## 原型样机束流测试

- 2023年4月于DESY对原型样机进行了束流测试

- 样机放置于黑色屏盒中,端部有风扇冷却装置

- ▶ 取数期间电子学读出系统和数据获取系统稳定运行

- ▶ 最大数据率 18 Mb/s

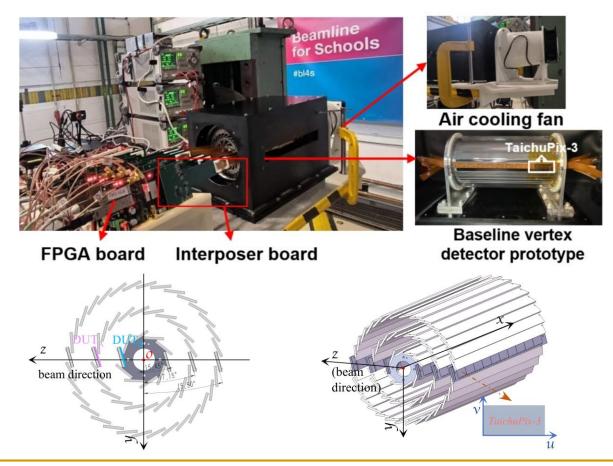

## 原型样机束流测试结果

CEPC

- 12条FPC+24颗芯片安装在束流测试样机中

- ▶ 部分击中图缺少,不影响离线数据的分析

- ▶ 电子束斑 (~2 cm × 2 cm) 清晰可见

- ▶ 最优空间分辨率~4.97 µm, 探测效率> 99%

24颗TaichuPix-3芯片的击中图

Ref: DOI-10.1109/TNS.2024.3395022

227

293

85<sup>1</sup>97

342 365

Threshold  $\xi_{_{\rm B}}$  [e ]

## 总结

- 面向CEPC顶点探测器需求,开展CMOS单片像素传感器芯片研发

- ▶ 经过三次设计迭代,实现了全尺寸全功能芯片(TaichuPix-3)

- ▶ 空间分辨率最好可达4.5 μm,探测效率高于99%

- 基于TaichuPix-3芯片研制了国内第一款顶点探测器原型样机

- 完成三层机械结构的设计与安装

- ▶ 样机经束流测试验证,空间分辨率达到5μm,探测效率优于99%

1<sup>st</sup> Vertex detector prototype (2023)

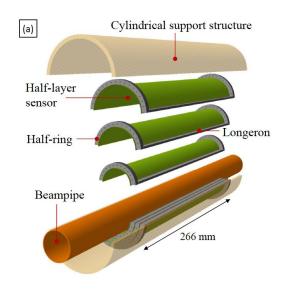

## 展望

- CEPC Ref-TDR的顶点探测器部分正在准备中,面临的主要挑战:

- 東流管半径从16 mm (CDR) 減小至 11 mm (Ref-TDR)

- ▶ 高数据率: 1 Gbps/chip (Z pole)

- ▶ 探测器采用风冷,要求功耗低于 40 mW/cm²

- 基准方案计划采用弯曲的CMOS像素传感器芯片制作桶部

- ▶ 芯片设计采用缝合(stitching)技术(ALICE ITS3采用此技术\*)

- ▶ 基于Ladder结构的探测器作为备选方案

\*ALICE ITS3 TDR: https://cds.cern.ch/record/2890181

**Baseline: curved MAPS**

Alternative: ladder based MAPS

# 谢谢大家!