# Progress of High granularity readout TPC for CEPC TDR

Huirong Qi, Zhi Deng

Yue Chang, Xin She, Jian Zhang, Lingwu Wu, Guang Zhao, Gang Li, Liwen Yu CEPC Track meeting, 2024.03.19

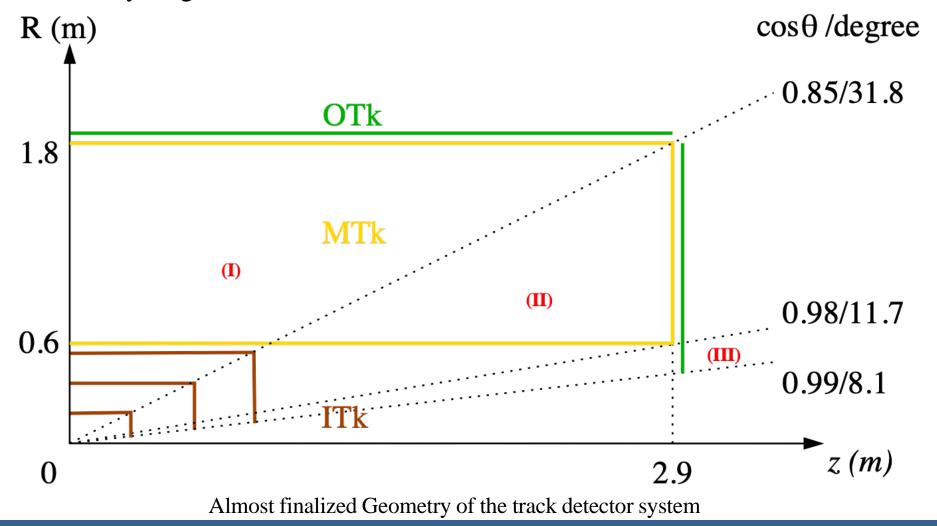

#### Track detector system in CEPC Phy.&Det. TDR

- The track detector system's geometry was finalized.

- Converging geometries as quickly as possible in preparation for physics simulation

- Geometry diagram almost finalized

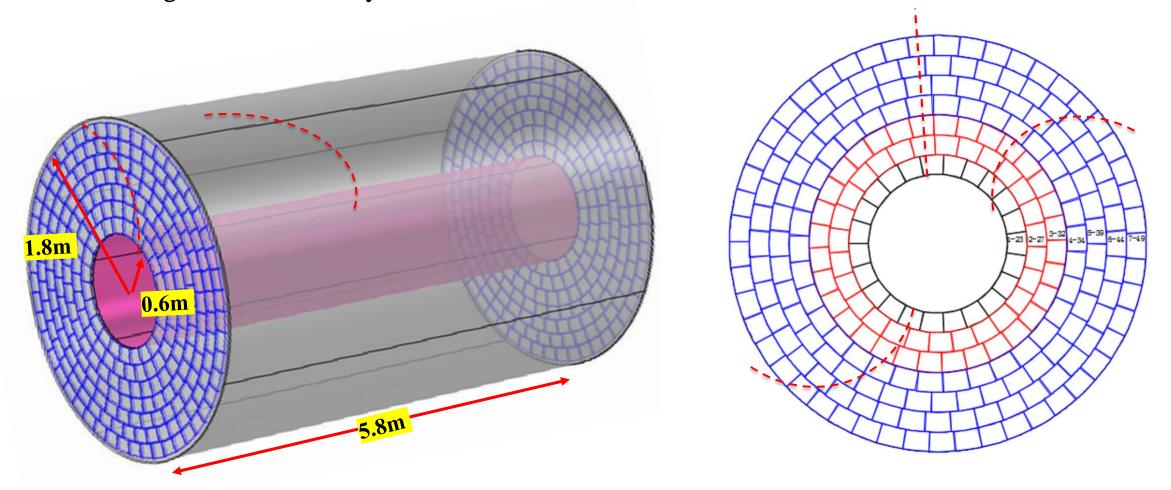

#### **Optimization the endcap of TPC**

- Optimization modules in the endcap

- ILD TPC: Coverage of the sensitivity readout area ~89%

- Coverage of the sensitivity readout area increased from 92% to 96%

### High granularity readout TPC $@\cos\theta \approx 0.98$

| Parameters                              | Higgs run                                             | Z pole run                                            |

|-----------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| B-field                                 | 3.0T                                                  | 2.0T                                                  |

| Pad size (mm)/All channels              | $0.5$ mm $\times 0.5$ mm $/2\times 3\times 10^7$      | $0.5$ mm $\times 0.5$ mm $/2\times 3\times 10^7$      |

| Material budget barrel                  | 0.012 X <sub>0</sub>                                  | 0.012 X <sub>0</sub>                                  |

| Material budget endcap                  | 0.17 X <sub>0</sub>                                   | 0.17 X <sub>0</sub>                                   |

| Points per track in rφ                  | 2300                                                  | 2300                                                  |

| $\sigma_{point}$ in r $\phi$            | 120μm (full drift)                                    | 400μm (full drift)                                    |

| σ <sub>point</sub> in rz                | $\simeq 0.1 - 0.4 \text{ mm}$ (for zero – full drift) | $\simeq 0.2 - 0.8 \text{ mm}$ (for zero – full drift) |

| 2-hit separation in rφ                  | 0.5mm                                                 | 0.5mm                                                 |

| K/π separation power @20GeV             | 3 σ                                                   | 3 σ                                                   |

| dE/dx                                   | 3.2%                                                  | 3.2%                                                  |

| Momentum resolution normalised:         | a = 1.210 e -5                                        | a = 2.69 e -5                                         |

| $\sigma_{1/pT} = \sqrt{a^2 + (b/pT)^2}$ | b = 0.589 e -3                                        | b = 0.90 e -3                                         |

Huirong Oi

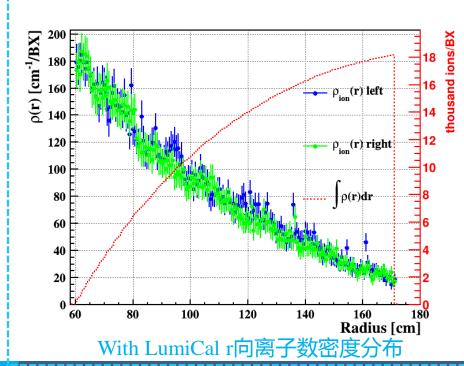

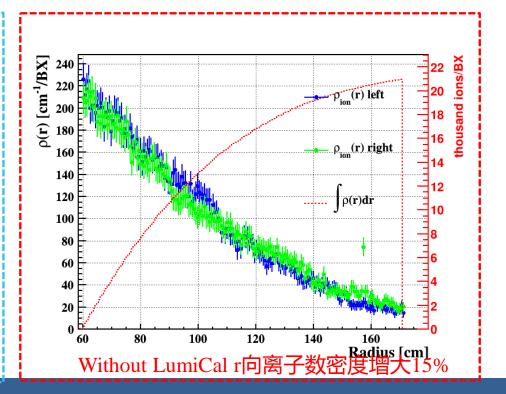

#### Estimation of the LumiCal at the inner of TPC

- With and without the LumiCal in the MDI region

- Optimization of the LumiCal position

| With LumiCal                    | Without LumiCal               |

|---------------------------------|-------------------------------|

| Edep~4.73GeV (10000BX)          | Edep~5.45GeV (10000BX)        |

| 18.20k ions/BX                  | 20.97k ions/BX                |

| Max. $\rho_{sc} = 5.46  nC/m^3$ | Max. $\rho_{sc} = 6.18nC/m^3$ |

#### **Power Consumption – TPC - Validation**

- High granularity readout TPC:  $3 \times 10^7$

- Total power: <10 kW to need the power consumption <100mW/cm<sup>2</sup>

- R&D on pixel TPC readout for CEPC

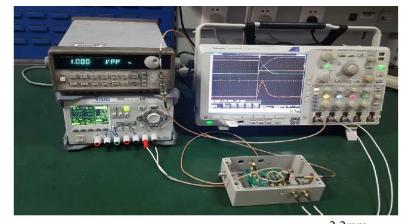

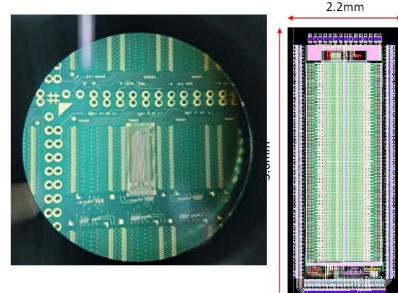

Pixel TPC ASIC chip was started to develop in 2023 and

1st prototype wafer standalone tested in May.

- ✓ Power consumption: <1.1mW/ch (1st prototype)

- √ <400mW/cm² (Test)

</p>

- 2nd prototype wafer design done

- ✓ < 100mW/cm² (Goal and final design)

- The TOA and TOT can be selected as the initiation function in the ASIC chip.

1st readout PCB board and the ASIC layout

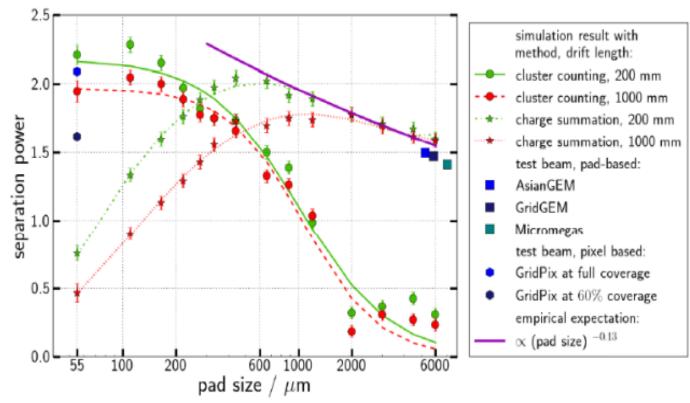

#### **Pad size optimization**

- Pad size optimization ongoing.

- Optimized the pad size to validate the PID performance

dN/dx (and tracking) can be beneficial from smaller pad size

$$\rho_{cl} \approx 30cm^{-1} \Rightarrow Pad\ size \approx 300\mu m$$

(To detect single e<sup>-</sup>)

Need to find out the optimal pad size considering cost/power consumption

#### Simulation with 30 cm track length

https://doi.org/10.1088/1748-0221/17/11/P11027

Huirong Oi

## Many thanks!