# **MAPS development in DRD3**

Eva Vilella [ on behalf of DRD3.1 ] University of Liverpool <u>vilella@hep.ph.liv.ac.uk</u>

# **Overview**

- DRD3 collaboration on solid state detectors

- DRD3.1 monolithic CMOS sensors

- Research proposal document

- DRD3.1 WP projects

- First DRD3 collaboration week

- Zoom meetings for project proposals

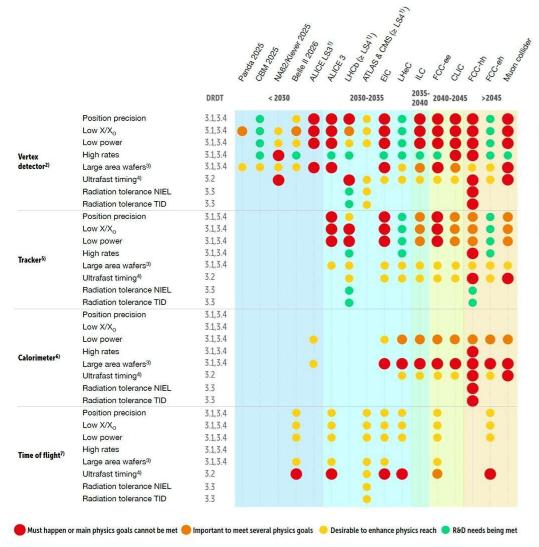

# **ECFA R&D Roadmap and DRD3**

## Solid state detectors chapter 3

Solid

state

| DRDT 3.1 | Achieve full integration of sensing and microelectronics in monolithic CMOS pixel sensors | iu- |

|----------|-------------------------------------------------------------------------------------------|-----|

| DRDT 3.2 | Develop solid state sensors with 4D-capabilities for tracking and calorimetry             | N   |

| DRDT 3.3 | Extend capabilities of solid state sensors to operate at extreme fluences                 | 1.  |

| DRDT 3.4 | Develop full 3D-interconnection technologies for solid state devices in particle physics  | N.  |

|          |                                                                                           |     |

| DRD3 Research topics |                                                                   |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------|--|--|--|--|--|

| WG1                  | Monolithic silicon sensors                                        |  |  |  |  |  |

| WG2                  | Hybrid silicon technologies                                       |  |  |  |  |  |

| WG3                  | Extreme fluence                                                   |  |  |  |  |  |

| WG4                  | Simulation                                                        |  |  |  |  |  |

| WG5                  | Characterisation techniques                                       |  |  |  |  |  |

| WG6                  | Wide bandgap and innovative sensors materials (diamond, SiC, GaN) |  |  |  |  |  |

| WG7                  | Interconnections and device fabrication                           |  |  |  |  |  |

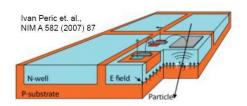

# **DRD3.1 Monolithic silicon sensors**

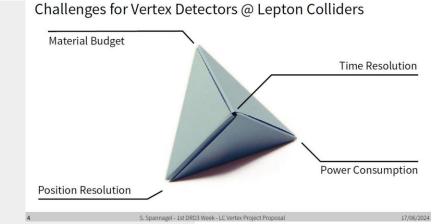

- Aim is to advance the performance of monolithic CMOS, combining sensing and readout elements, tackling the challenges of:

- Very high spatial resolution

- Good timing performance

- High data rate

- High radiation tolerance

- Keeping an affordable cost

- Low mass

- Covering large areas

- Reducing power

- And ultimately combining all these in one single device

## DRD3.1 research goals <2027

- **1.1** Position resolution:  $\leq 3 \mu m$

- **1.2** Timing resolution: towards 20 ps

- 1.3 Readout architectures: towards 100 MHz/cm<sup>2</sup>, 1 GHz/cm<sup>2</sup> with 3D stacked monolithic sensors, and on-chip reconfigurability

- 1.4 Radiation tolerance: towards e16 n<sub>eq</sub>/cm<sup>2</sup>

NIEL and 500 Mrad TID

- **1.5** Low-cost large-area CMOS sensors

# WG1 Programme and technologies

## R&D programme divided into three phases:

- Initial stepping stones developments for ALICE-3, LHCb-2, EIC, Belle-3, ATLAS, CMS and HGCAL (DRD6);

- the subsequent further developments for e+e- colliders;

- and lastly the R&D for MC and FCC-hh.

- Several complementary technology processes with features that are attractive for HEP detectors:

- Accessible to the HEP community;

- Wafer sizes of 200 mm and 300 mm;

- High resistivity bulk (through high resistivity epitaxial and Czochralski substrates of pand n-type);

- Processes with node sizes ranging from 65 nm to 180 nm, and potential to optimise implant designs for charged particle detection;

- Availability of MPWs and/or dedicated engineering run with large reticles (with options for reticle stitching or 3D stacking to logic wafers).

# **WG1 Planning**

## Identified technologies:

- TPSCo 65 nm, LFoundry 110 nm, IHP 130 nm, LFoundry 150 nm, AMS/TSI 180 nm, TJ 180 nm, low-cost large-area CMOS and 3D stacking.

- TSI discontinued its technology in 2023, and efforts focus now on the AMS technology;

- low-cost large-area refers to large-area monolithic CMOS sensors aimed at instrumenting hundreds of m2 in central tracking applications in future collider experiments.

## Submissions:

- The programme foresees several submissions in approximately 18 months cycles (design, submission and evaluation) until 2027.

- Proposed submissions in TPSCo 65 nm will take advantage of the runs currently proposed by CERN to be shared with the community;

- proposed submissions in the other technologies will be as offered by the foundry and/or Europractice.

# **WG1 Planning**

## Technologies and research goals:

- The programme does not exclude any of the identified technologies for any of the research goals initially, but it assumes that some technologies might be more suited to achieve certain research goals.

- As the programme progresses, it is anticipated that perhaps the research focus will shift from all to a sub-set of the identified technologies.

- It will be possible to add WP projects to achieve the combination of multiple research goals in one single device, which is an important challenge that needs to be met for strategic applications, as the collaboration develops

- e.g. to achieve devices with high spatial granularity and fast timing while consuming little power;

- e.g. to achieve devices with fast data rate and high radiation tolerance while consuming little power.

# **Work Package projects**

- Work Package projects proposed by groups of institutes interested in specific questions within the DRD3 research goals.

- Projects will investigate research goals by:

- Designing and simulating the sensor;

- Submitting the design for fabrication;

- Developing specific data acquisition systems (e.g. chip carrier boards, firmware, etc.)

- Characterising the fabricated devices in lab measurements, irradiations, and test beams as appropriate.

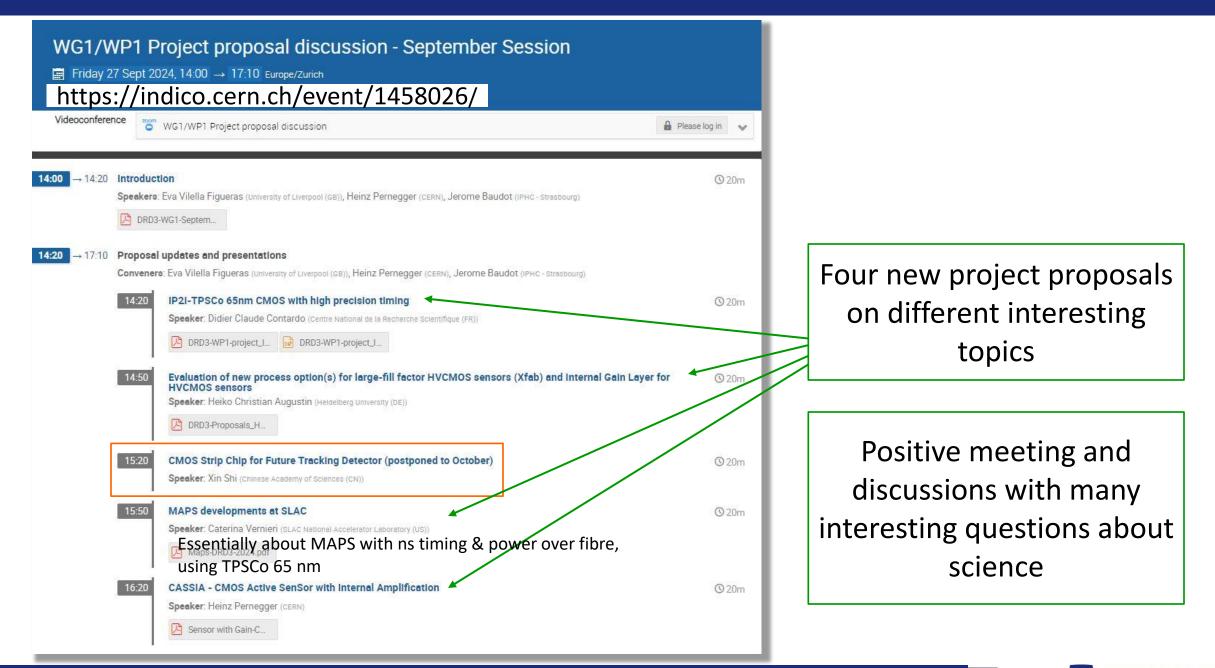

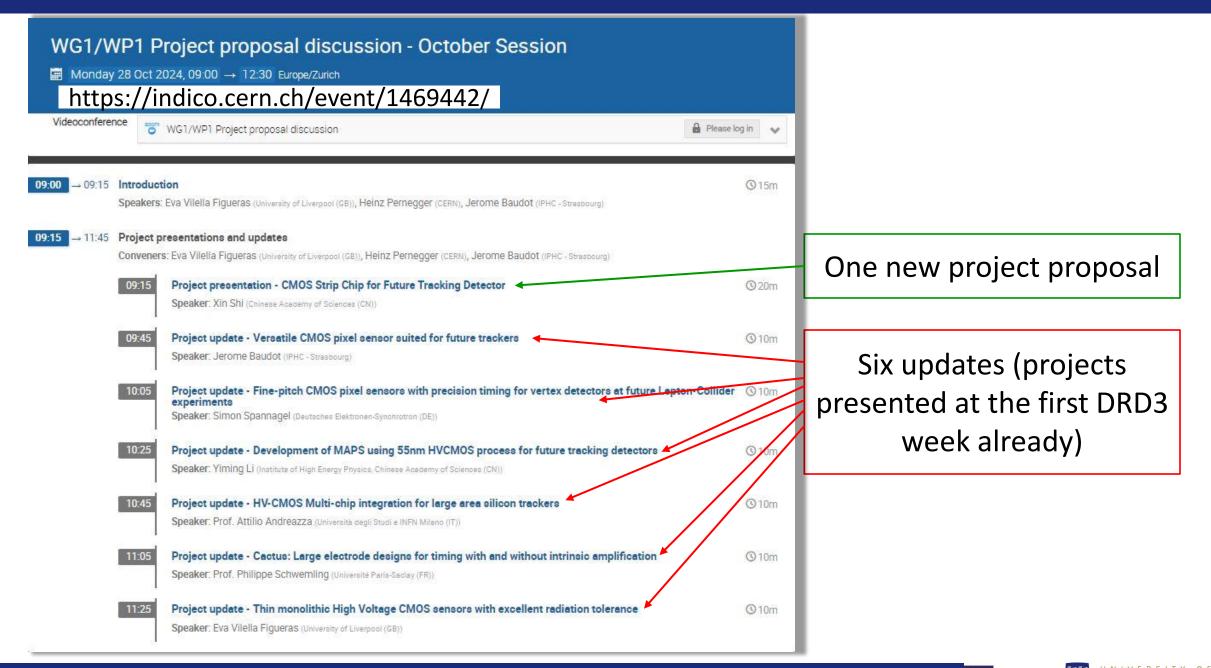

# 1st DRD3 week – WG1/WP1 CMOS technologies session

500/1-001 - Main Auditorium, CERN

500/1-001 - Main Auditorium, CERN Next steps in WG1 (September zoom meeting)

500/1-001 - Main Auditorium, CERN

Monolithic CMOS Strip Sensors for large area detectors

| Mon 17 | /06 Tue 18/06 All days                                                                   | >                                                              | 14:00 |

|--------|------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------|

|        | 📑 Print 🛛 PD                                                                             | PF Full screen Detailed view Filter                            |       |

| 9:00   |                                                                                          |                                                                |       |

|        | Introduction to WG1/WP1 session                                                          | Eva Vilella Figueras et al. 🥝                                  | Ĩ     |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 09:25 - 09:30                                                  |       |

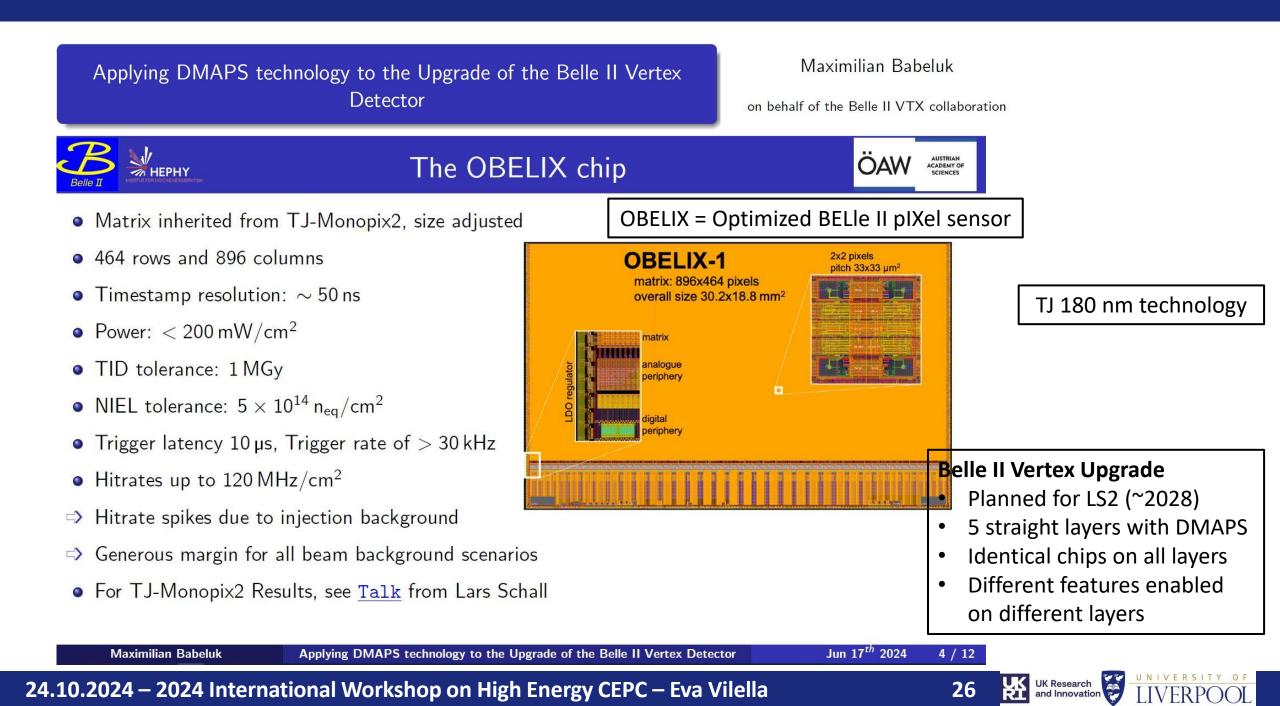

|        | Applying DMAPS technology to the Upgrade of the Belle II                                 | Vertex Detector Maximilian Babeluk 🥝                           | Í     |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 09:30 - 09:45                                                  | 15:00 |

|        | DMAPS for measuring energy depositions and tracks of Ga<br>Haris Lambropoulos            | lactic Cosmic Ray and Solar Energetic Particles                |       |

| 0:00   | R&D of MAPS for the Super Tau-Charm Facility(STCF)                                       | Lailin Xu 🥝                                                    | 1     |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 10:00 - 10:15                                                  |       |

|        | DMAPS development at PSI                                                                 | Hans-Christian Kaestli 🥝                                       |       |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 10:15 - 10:30                                                  | 16:00 |

|        | Coffee Break                                                                             |                                                                |       |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 10:30 - 11:00                                                  |       |

| 1:00   | Research on CMOS MAPS at GSI/FAIR - Status and Next St                                   | ep Michael Deveaux 🥝                                           | 1     |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 11:00 - 11:15                                                  |       |

|        | The ATLASPIX3 CMOS pixel sensor and module performan                                     | ce Prof. Attilio Andreazza et al. 🥝                            | 17:00 |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 11:15 - 11:30                                                  | 11.00 |

|        | Characterization of the RD50-MPW4 HV-CMOS pixel sensor                                   | Bernhard Pilsl 🥝                                               | 1     |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 11:30 - 11:45                                                  |       |

|        | Adaptation and Modularization of MPW4 Firmware for Integ<br>Jorge Jimenez Sanchez et al. | ration into the Caribou Boreal Architecture: A Pilot Project 🥝 | 1     |

| 2:00   | Results and perspectives of the Monopix2 depleted monoli                                 | thic active pixel sensors Lars Philip Schall 🥝                 |       |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 12:00 · 12:15                                                  |       |

|        | Radiation hardness and timing performance of MALTA mon                                   | olithic Pixel sensors in Tower 180 nm 👘 Lucian Fasselt 🥝       |       |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 12:15 - 12:30                                                  | 05    |

|        | Development of MAPS using 55nm HVCMOS process for fu                                     | ture tracking detectors Yiming Li 🥝                            | 1     |

|        | 500/1-001 - Main Auditorium, CERN                                                        | 12:30 - 12:50                                                  |       |

| First measurements on the CASSIA Sensor (CMOS Active SenSor with Internal Amplific                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ation) Heinz Pernegger                                                                                                                                                                      | ٢                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 500/1-001 - Main Auditorium, CERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14:00 · 14:1                                                                                                                                                                                | 15                                                                                                                                         |

| All-silicon ladder concept for CMOS monolithic pixel detectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Marco Vogt                                                                                                                                                                                  | 6                                                                                                                                          |

| 500/1-001 - Main Auditorium, CERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14:15 - 14:3                                                                                                                                                                                | 30                                                                                                                                         |

| Innovations in CMOS Pixel Sensor Technology at IPHC: Projects and Future Prospects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Frederic Morel                                                                                                                                                                              | 6                                                                                                                                          |

| 500/1-001 - Main Auditorium, CERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14:30 - 14:4                                                                                                                                                                                | 45                                                                                                                                         |

| The H2M project: Porting the functionality of a hybrid readout chip into a monolithic 65<br>Philipp Gadow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nm CMOS imaging process                                                                                                                                                                     | Ø                                                                                                                                          |

| Fine-pitch CMOS pixel sensors with precision timing for vertex detectors at future Lepto<br>Simon Spannagel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | on-Collider experiments                                                                                                                                                                     | 6                                                                                                                                          |

| A versatile pixel matrix in TPSCo 65 nm for future trackers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Jerome Baudot                                                                                                                                                                               | C                                                                                                                                          |

| 500/1-001 - Main Auditorium, CERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15:20 · 15:4                                                                                                                                                                                | 40                                                                                                                                         |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15:40 · 16:1<br>xperiments                                                                                                                                                                  |                                                                                                                                            |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                             |                                                                                                                                            |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                             | 6                                                                                                                                          |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance                                                                                                                                                                                                                                                                                                                                                                                        | xperiments                                                                                                                                                                                  | 6                                                                                                                                          |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN                                                                                                                                                                                                                                                                                                                                                   | xperiments<br>Prof. Philippe Schwemling                                                                                                                                                     | @<br>50                                                                                                                                    |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA                                                                                                                                                                                                                                                                                        | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5                                                                                                                                     | 6<br>6<br>50                                                                                                                               |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA<br>500/1-001 - Main Auditorium, CERN                                                                                                                                                                                                                                                   | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5<br>Tomislav Suligoj                                                                                                                 | 6<br>50<br>6<br>10                                                                                                                         |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA<br>500/1-001 - Main Auditorium, CERN<br>DRD7 - Technology Access                                                                                                                                                                                                                       | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5<br>Tomislav Suligoj<br>16:50 - 17:1                                                                                                 | 6<br>50<br>6<br>10                                                                                                                         |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA<br>500/1-001 - Main Auditorium, CERN<br>DRD7 - Technology Access<br>500/1-001 - Main Auditorium, CERN                                                                                                                                                                                  | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5<br>Tomislav Suligoj<br>16:50 - 17:1<br>Walter Snoeys                                                                                | 6<br>50<br>10<br>6<br>30                                                                                                                   |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA<br>500/1-001 - Main Auditorium, CERN<br>DRD7 - Technology Access<br>500/1-001 - Main Auditorium, CERN                                                                                                                                                                                  | xperiments<br>Prof. Philippe Schwennling<br>16:30 - 16:5<br>Tomislav Suligoj<br>16:50 - 17:1<br>Walter Snoeys<br>17:10 - 17:3                                                               | 6<br>50<br>10<br>6<br>30                                                                                                                   |

| 500/1-001 - Main Auditorium, CERN Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e Prof. Attilio Andreazza et al. Large electrode sensors with intrinsic amplification for ultimate timing performance 500/1-001 - Main Auditorium, CERN CMOS Active SenSor with Internal Amplification – CASSIA 500/1-001 - Main Auditorium, CERN DRD7 - Technology Access 500/1-001 - Main Auditorium, CERN An OpenPDKs/OpenSource approach to DRD3 CMOS sensors 500/1-001 - Main Auditorium, CERN Thin monolithic High Voltage CMOS sensors with excellent radiation tolerance | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5<br>Tomislav Suligoj<br>16:50 - 17:1<br>Walter Snoeys<br>17:10 - 17:3<br>Daniel Muenstermann                                         | 6<br>50<br>10<br>30<br>6<br>40                                                                                                             |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA<br>500/1-001 - Main Auditorium, CERN<br>DRD7 - Technology Access<br>500/1-001 - Main Auditorium, CERN<br>An OpenPDKs/OpenSource approach to DRD3 CMOS sensors<br>500/1-001 - Main Auditorium, CERN                                                                                     | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5<br>Tomislav Suligoj<br>16:50 - 17:1<br>Walter Snoeys<br>17:10 - 17:3<br>Daniel Muenstermann<br>17:30 - 17:4                         | 6<br>50<br>10<br>6<br>30<br>40                                                                                                             |

| Large area low-power Monolithic CMOS Tracking Detectors for future particle physics e<br>Prof. Attilio Andreazza et al.<br>Large electrode sensors with intrinsic amplification for ultimate timing performance<br>500/1-001 - Main Auditorium, CERN<br>CMOS Active SenSor with Internal Amplification – CASSIA<br>500/1-001 - Main Auditorium, CERN<br>DRD7 - Technology Access<br>500/1-001 - Main Auditorium, CERN<br>An OpenPDKs/OpenSource approach to DRD3 CMOS sensors<br>500/1-001 - Main Auditorium, CERN<br>Thin monolithic High Voltage CMOS sensors with excellent radiation tolerance     | xperiments<br>Prof. Philippe Schwemling<br>16:30 - 16:5<br>Tomislav Suligoj<br>16:50 - 17:1<br>Walter Snoeys<br>17:10 - 17:3<br>Daniel Muenstermann<br>17:30 - 17:4<br>Eva Vilella Figueras | <ul> <li>6</li> <li>50</li> <li>6</li> <li>10</li> <li>6</li> <li>30</li> <li>6</li> <li>40</li> <li>40</li> <li>40</li> <li>40</li> </ul> |

- 3 reports from experiment-oriented developments

- 12 reports from "generic" R&D

- 8 project proposals (+ further project proposals in zoom meetings)

#### 24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

09:00 - 09:20

09:20 - 09:40

09:40 - 09:42

Jens Weingarten

Eva Vilella Figueras et al.

# **Project proposals**

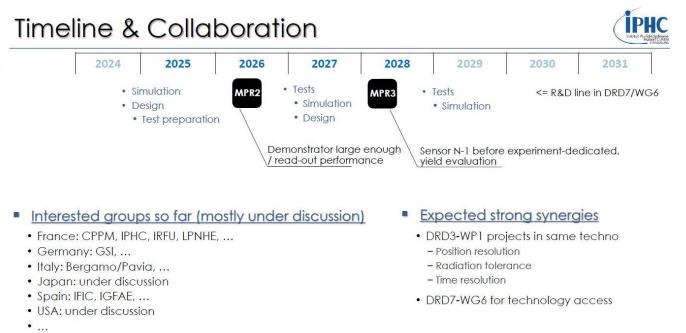

Fine-Pitch CMOS Sensors with Precision Timing for Lepton Collider Experiments

# Project Goals & Scope

- Simulation, development and evaluation of MAPS

- Development in 65nm TPSCo CIS process

- Targeting the vertex-detector requirements of future Lepton Colliders:

- 3 µm single-point resolution

5

- down to 5 ns time resolution (depending on chosen Lepton-Collider technology)

- average power consumption below 50 mW/cm<sup>2</sup>

- thinning to 50 μm, minimal inactive periphery area

- sensor architecture scalable to a large-area detector system

- Development of new high-resolution sensors for beam telescopes as intermediate target Relaxed power-consumption (<500 mW/cm2) and timing requirements (100 ns)</li>

- Staged approach allows further refinement of performance targets after next strategy update

S. Spannagel - 1st DRD3 Week - LC Vertex Project Proposal

17/06/2024

## Project proposal for WP1: A versatile pixel matrix in TPSCo 65 nm for future trackers Jerome Baudot

# Specifications: numbers!

Source: my own mix of LOI, recent talks and private communication

|                                 | ALICE3 OT        | Belle II trk       | CBM <u>trk</u> | LHCb UT            | FCCee trk          |

|---------------------------------|------------------|--------------------|----------------|--------------------|--------------------|

| Position resolution             | ~10 µm           | <15 µm             | ~10 µm         | <10 µm             | <10 µm             |

| Pixel pitch (µm)                | 50               | 50                 | ~30            | 50                 | 5 <b>0</b>         |

| Hit rate (MHz/cm <sup>2</sup> ) | 0.05 to 2        | <1                 | 60/180         | 160                | <10                |

| Data rate (Gb/s)                |                  |                    | 8              | 20                 |                    |

| Time figure (ns)                | 100              | ~1                 | 25             | ~1 (<25)           | 20 to 1000         |

| Triggering                      | no               | yes                | no             | no                 | ?                  |

| Power                           | ~20              | <50                | ~50            | <100               | ~20?               |

| TID (kGy)                       | 50               | 10?                | ~10            | 2400               | 10?                |

| NIEL                            | 10 <sup>14</sup> | 10 <sup>11</sup> ? | few 1014       | 3x10 <sup>15</sup> | 10 <sup>11</sup> ? |

J. Baudot - other projects in TPSCo 65 nm - Vertex detector discussion meeting, 6-7 Mai 2024, DESY

UNIVERSITY

## DRD3-WP1 project proposal

TPSCo 65nm MCMOS with high precision timing

D. Contardo, IP2I

DRD3-WP1 project proposal TPSCo 65nm MCMOS with high precision timing

- Project motivation

- contribute to developments toward full 5D\* tracking with MCMOS sensors

- Targeted applications in several FCC-ee detector concepts

- ToF PID in outer tracking layer(s) of a full Si-tracker or surrounding a LGVD\*\* tracker

- providing both  $\lesssim$  O(10)  $\mu m$  and O( $\lesssim$  50) ps precision timing in a single sensor

- applicable to preshower layers in a sampling calorimeter with embedded electronics (DRD6)

- Major constraints

- high channel density and readout features (real estate) and related power dissipation

- but rates are lower and material budget effect is less (not) constraining at large radii

- Technology choice

- TPSCo 65 nm for high density and low power consumption

- intrincic timing precision may be limited by process (electrode size, epitaxial layer thickness...)

\* 5D = space-point, time & amplitude (ToT amplitude for time walk correction and to complete binary output for space-point resolution in clusters) \*\* Large Gas Volume Detector: Drift Chamber or TPC

### 24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

2

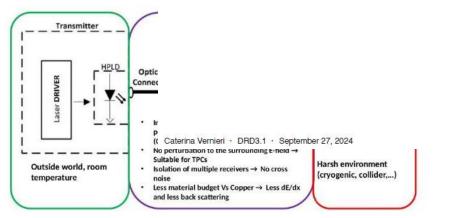

## (towards) Nanosecond timing MAPS & power over fiber

Caterina Vernieri on behalf of Christos Bakalis, James E. Brau (Oregon U), Martin Breidenbach, Sander Breur, Angelo Dragone, Loukas Gouskos (Brown U), Christopher Kenney, Lorenzo Rota, Julie Segal, Mirella Vassilev, Charles Young

#### SLAC

- · Power over Fiber (PoF) offers an innovative solution by delivering power through optical fibers, which are immune to electric and magnetic fields, and boast 1000X lower thermal conductivity compared to coax.

- · We are developing radiation-hardened photonic links that can be used in future e+e- collider environments, where radiation levels can exceed 100 krad.

- · This approach will investigate advanced photovoltaic materials like perovskites and their potential to surpass current GaAs-based photodiodes in power-to-weight ratio and radiation tolerance.

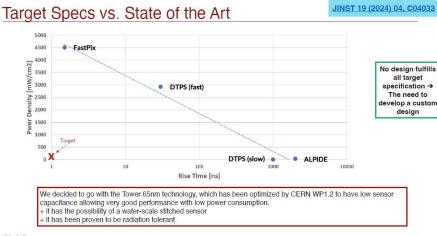

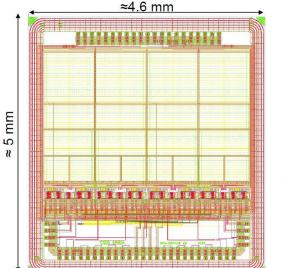

## NAPA\_p1: NAnosecond Pixel for large Area sensors – Prototype 1

#### First prototype in TJ 65nm

- The prototype design submitted with a total area 5 mm x 5 mm and a pixel of 25  $\mu$ m x 25  $\mu$ m, to serve as a baseline for sensor and pixel performance.

- Design motivation → simple architecture with minimum global signals to reduce failure risk in a large area implementation.

- Thanks to CERN WP1.2 effort on sensor optimization in TowerSemi 180 nm and 65 nm technologies

Picture of NAPA-p1 prototype from WP1.2 shared submission

JINST 19 (2024) 04, C04033

ons

## Large area low-power Monolithic CMOS Tracking Detectors for future particle physics experiments

Yanyan Gao – University of Edinburgh Yimin Li – IHEP Attilio Andreazza - Università di Milano and INFN For the ATLASPIX3 Silicon Tracker community

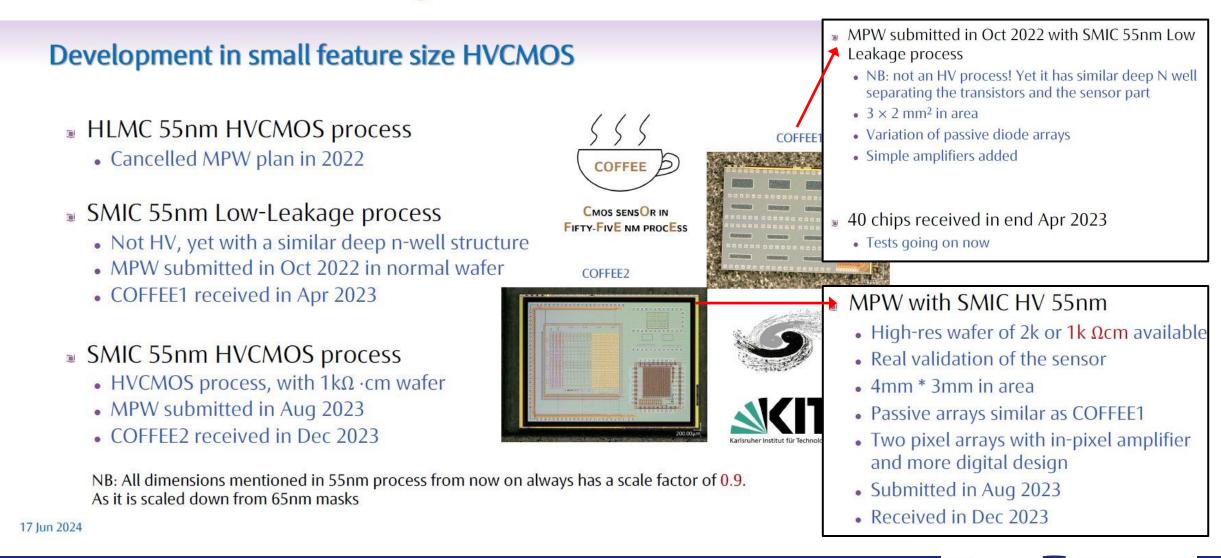

# 55nm High Voltage CMOS Technology

#### Started development in SMIC 55 nm HVCMOS technology

- Smaller technology node with respect to other technologies we are working with

- AMS/TSI 180 nm, LF 150 nm

- comparable to TPSCo 65 nm

- also considering HLMC 55 nm

- The 55nm logic technology combines improved performance and reduced power consumption w increased design possibilities and cost efficiencies.

#### **Project goal**

- New MAPS designs targeting low-power and high granularity, featuring smaller nodes (SMIC foundry 55nm), on-chip solutions allowing for efficient data aggregation (e.g. chip-to-chip communication) and Shunt LDO regulators allowing for serial powering, and multi-chip aggregation via hybrids or on wafer stitching

- 2. development of a large-scale system demonstrator, using state-of-the-art CMOS sensors, that has scalability for large area production as a core element of its design and includes a low-mass mechanical support and efficient cooling strategy. Ultra thin and curved designs will be investigated in the context of vertexing to minimize material budget.

Detailed layout of the project is being developed: scope of this presentation is to trigger a discussion about how it can fit (or be merged) with other WP1 projects

#### ATLASPIX3 does not contains all the features needed for efficient integration

- chip-to-chip data transmission

- 4 input lines

- Some are available as part of engineering runs developing the ATLAPIX4 family or from LHCb Mighty Tracker

- With FCCee feasibility study and CEPC Detector TDR coming in the next months, we consider a demonstration of the integration process of significant value

- Relevant IPs should also be developed in new technologies, like SMIC 55 nm, to facilitate the convergence of sensor developments into full scale system-on-chip, like ATLASPIX3

#### DRD3 Week, 17/06/2024

#### Large-area and low-power monolithic CMOS detectors

## Towards large electrode sensors with intrinsic amplification for ultimate timing performance

CEA/Irfu/DphP and CEA/Irfu/Dedip Yavuz DEGERLI, Fabrice GUILLOUX, Jean-Pierre MEYER, Philippe SCHWEMLING (also Université Paris Cité)

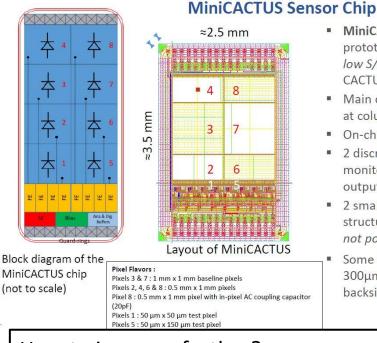

MiniCACTUS is a smaller detector

CACTUS large size demonstrator

*low S/N issue* observed on previous

Main change in MiniCACTUS: FE integrated

On-chip Slow Control, DACs, bias circuitry

2 discriminated digital (LVDS) and 2 analog

structures to study charge collection (FEs

monitoring (slower than CSA output)

Some detectors thinned to 100, 200,

300µm and than post-processed for

backside polarization after fabrication

2 small pixels implemented as test

outputs for 2 columns

not power optimized)

at column level, pixels mostly passive

prototype designed in order to address the

IFAE Barcelona Raimon CASANOVA, Yujing GAN, Sebastian GRINSTEIN University of Liverpool Eva VILELLA

Tomasz HEMPEREK (U. Bonn, now at DECTRIS) MiniCACTUS V2 Sensor Chip

Irfu : Yavuz Degerli, Fabrice Guilloux, Jean-Pierre Meyer, Philippe Schwemling IFAE : Raimon Casanova, Yujin Gan, Sebastian Grinstein

- ~ 2 times larger than MiniCACTUS

- 0.5 mm x 1 mm (baseline), 1 mm x 1 mm and 0.5 mm x 0.5 mm diodes

- 50 μm x 150 μm and 2 50 μm x 50 μm small test diodes

- 3 different preamps

- New multistage discriminator with programmable hysteresis

- Improved layout for better mixed-signal coupling rejection

- CEA-IRFU & IFAE-Barcelona coll.

- Submitted in May 2023, chips came back from post-processing end May 2024

## How to improve further?

- Intrinsic gain allows to:

- Improve S/N  $\rightarrow$  Improve on time resolution

- Reduce FE power consumption

- Reduce pixel pitch

- Ultimate goal is reaching 20 ps resolution (RG 1.2)

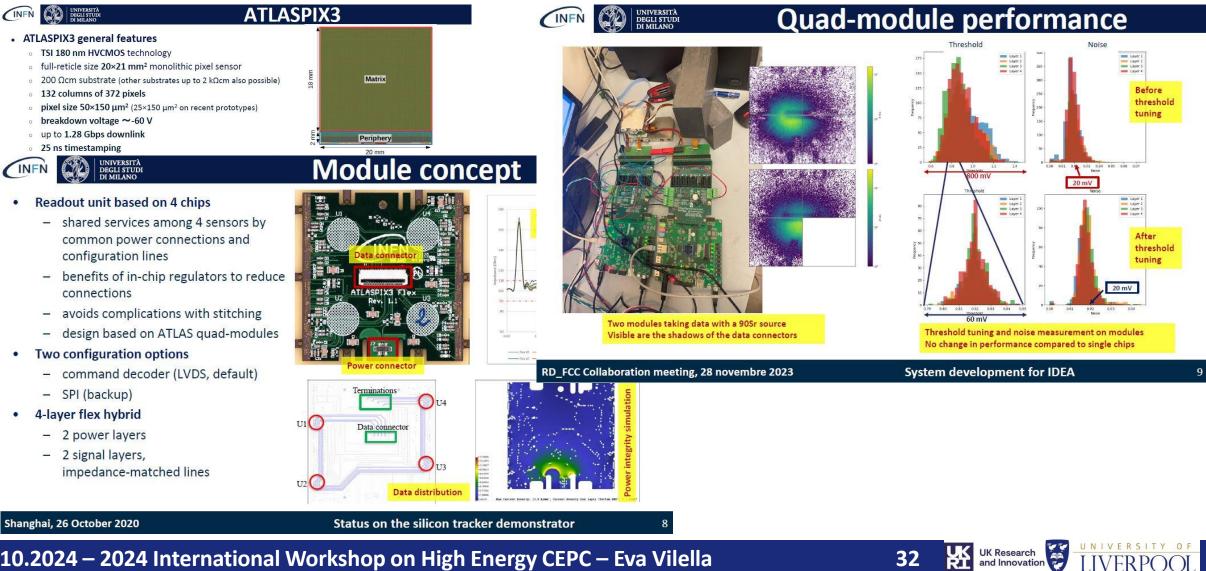

### Thin monolithic High Voltage CMOS sensors with excellent radiation tolerance

University of Liverpool – Jan Hammerich, Sam Powell, Eva Vilella, Ben Wade, Chenfan Zhang, Carleton University – Thomas Koffas, HEPHY – Thomas Bergauer, Christian Irmler, IFIC – Ricardo Marco-Hernández, JSI – Igor Mandic, NIKHEF – Uwe Kraemer, Jory Sonneveld, University of Bern – Silke Moebius, University of Sevilla – Rogelio Palomo

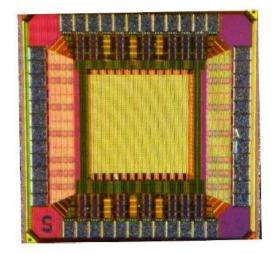

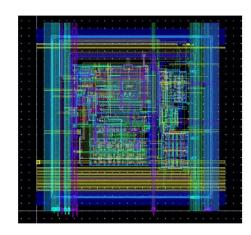

#### RD50-MPW4

#### Significant improvements

- For high breakdown voltage and high radiation tolerance

- Multiple ring structure around the chip edge

- Substrate backside-biasing to high voltage

#### Fabrication details

- 150 nm High Voltage CMOS LFoundry (LF15A)

- P-type substrate with nominal 3 k $\Omega \cdot cm$  high resistivity

- 280 µm thin

- Backside processed via third party (complex wafer loan)

#### Chip contents

- Pixel matrix with FE-I3 style readout

- 64 x 64 pixels

- 62 μm x 62 μm pixels with large collection electrode

- Digital periphery (slow control, hit data transmission)

- Tests structures (e-TCT, DLTS)

#### 17-21 June 2024 – 1st DRD3 week on Solid State Detectors R&D @ CERN – Eva Vilella

#### **Detector community dedicated LF15A submissions**

- What is in the deal with LFoundry?

- Detector community joint submission(s) with several chips in the reticle

- Price advantageous

- Easy access to backside processing (potentially in-house at LFoundry)

- Access to high resistivity wafers

- Large number of fabricated wafers, so many samples for chip evaluation

- Multi-layer mask type submission (MLM 1x3, maximum area is ~ 9 mm x 25 mm)

- Including 6 metal layers and transistors

## This proposal – Boosting the technology parameters

| Parameter              | Current value                                                                                                                                 | Research goals                                                |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| Spatial resolution     | 62 μm x 62 μm<br>(pixel size)                                                                                                                 | 62 μm x 62 μm<br>(pixel size)                                 |  |  |

| Timing resolution      | 10 ns<br>(time-walk)                                                                                                                          | 2 ns<br>(time-walk)                                           |  |  |

| Radiation<br>tolerance | Several 10 <sup>15</sup> n <sub>eq</sub> /cm <sup>2</sup> , maybe 10 <sup>16</sup> n <sub>eq</sub> /cm <sup>2</sup><br>(currently under test) | > 10 <sup>16</sup> n <sub>eq</sub> /cm <sup>2</sup>           |  |  |

| Power consumption      | Several 100 mW/cm <sup>2</sup><br>(currently under test)                                                                                      | A few 100 mW/cm <sup>2</sup>                                  |  |  |

| Fill-factor            | Area hungry digital periphery<br>Area hungry multiring structure                                                                              | Reduced area digital periphery<br>Reduced area ring structure |  |  |

Chip delivered in Q1 2024

**Evaluation is going very well**

See Bernhard Pilsl's

presentation for details

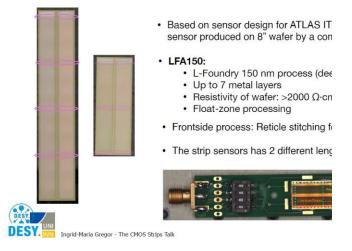

# MONOLITHIC CMOS STRIP SENSORS FOR LARGE AREA DETECTORS

Jan-Hendrik Arling, Marta Baselga, Naomi Davis, Jochen Dingfelder, Ingrid M. Gregor, Marc Hauser, Fabian Hügging, Karl Jakobs, Michael Karagounis, Roland Koppenhöfer, Kevin Kröninger, Fabian Lex, Ulrich Parzefall, Birkan Sari, Simon Spannagel, Dennis Sperlich, Jens Weingarten, Iveta Zatocilova

#### EXISTING CMOS SENSOR STRUCTURE

## NEXT STEPS

- Test monolithic analogue design for the large sensor capacitance of a strip detector

- Foresee to test with different strip lengths by wire bonding long strips to the test chip

- Basic digital functionality (shortness of digital chip design person-power)

#### GOING FULLY MONOLITHIC

- Dream for large area tracking detectors minimise bonds (wire and/or bump bonds)

- Fully monolithic would ease the design significantly while possibly being more cost effective

- Working on the implementation of a front-end on strip level

- Submission spring 2025

#### ATLAS FE-I4 style front-end

Collaborators welcomed in all areas (especially ASICS design)

DRD3 Meeting CMOS Strips

## Project Proposals on large-fill factor HVCMOS sensors

Heiko Augustin for the Heidelberg HV-MAPS group Physikalisches Institut Heidelberg

### Two Proposals

- 1. Evaluation of new process options for large-fill factor HVCMOS sensors

- 2. Internal Gain Layer for HVCMOS sensors

- Evaluation of new process options for large-fill factor HVCMOS sensors

Explore Xfab

- 180nm node HVCMOS process

- $\rightarrow$  Affordable on Institute Level

- Variety of other processes and smaller nodes

- MPW/MLM possible via Europractice

- Internal Gain Layer for HVCMOS sensors

- State-of-the-Art

Prove-of-Principle in picoAD project

Layer gain of 23 achieved

- Potential in HVCMOS

Power consumption

## **Radiation hard read-out architectures**

C. Solans 1st DRD3 week on Solid State Detectors R&D 18 June 2024

Carlos Solans

## Proposal to DRD3 WG1

DRD3 week

## DRD3

UK Research and Innovation

22

ŘŤ

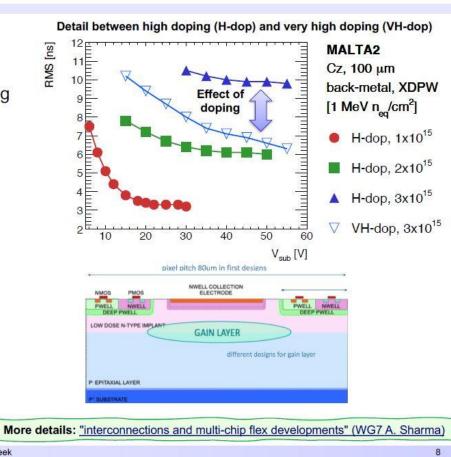

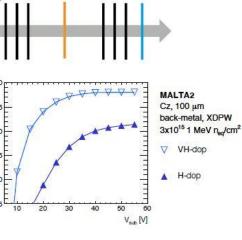

- 4 months: resubmission Mini-MALTA3

- Evaluate ultra-high doping (UH-dop) of n-layer

- Very-high doping (VH-dop) improves wrt high doping (H-dop) after 3e15 n/cm2 <u>Eur. Phys. J. C 83 (2023) 58</u>

- Next 12 months: submission MALTA3

- Demonstrator larger than 2x2 cm2

- Optimized PLL for time tagging below 1 ns

- Reduce the number of serial lines to the chip

- Full command protocol for chip configuration

- Optimize number of bits per hit

- Multiple serial outputs from single chip

- Next 24 months:

- Evaluate alternative pixel designs: CASSIA?

- Evaluate alternative group geometries

- Large area modules: interconnection designs

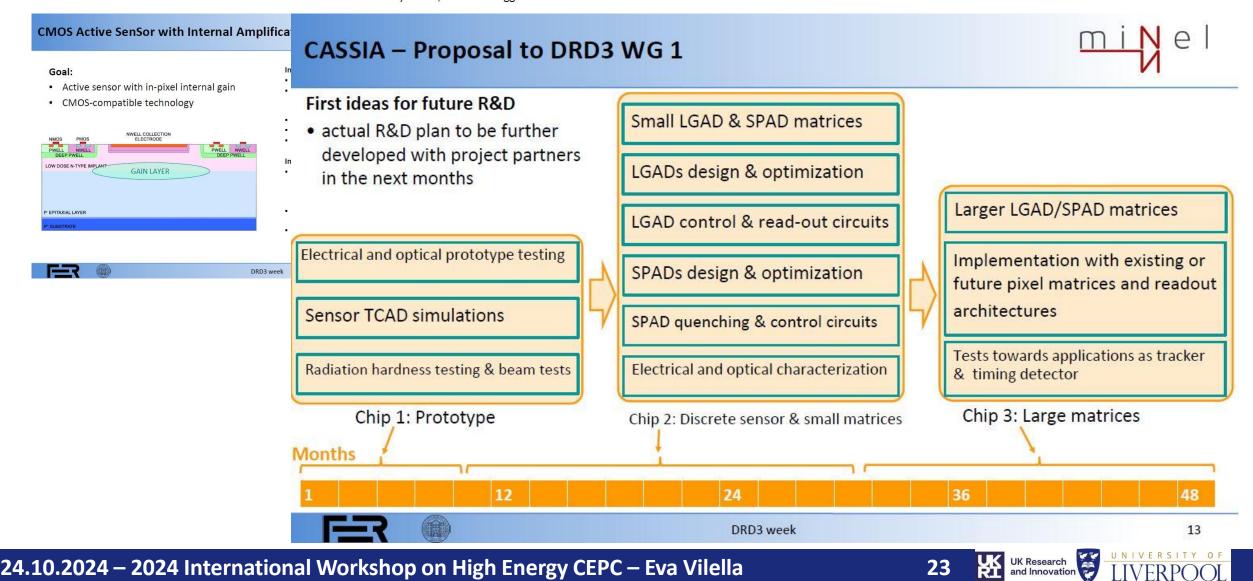

#### **CMOS Active SenSor with Internal Amplification – CASSIA**

Tomislav Suligoj, Ivan Berdalović, Borna Požar

Sebastian Haberl, Anastasia Kotsokechagia, Jenny Lunde, Heinz Pernegger

КĶ

23

# Conclusion

- DRD3 aims to advance the performance of monolithic CMOS, combining sensing and readout elements, tackling several challenges (very high spatial resolution, good timing performance, high data rate, high radiation tolerance, covering large, reducing power, etc.)

- Several Work Package projects proposed within the DRD3 research goals.

- In several technologies.

## DRD3.1 research goals <2027

- Position resolution:  $\leq 3 \mu m$ 1.1

- Timing resolution: towards 20 ps 1.2

- Readout architectures: towards 100 1.3 MHz/cm<sup>2</sup>, 1 GHz/cm<sup>2</sup> with 3D stacked monolithic sensors, and on-chip reconfigurability

- Radiation tolerance: towards e16  $n_{eq}/cm^2$ 1.4 NIEL and 500 Mrad TID

- Low-cost large-area CMOS sensors 1.5

# Reports from experimentoriented developments

DMAPS for measuring energy depositions and tracks of Galactic Cosmic Ray and Solar Energetic Particles

Presenter: Haris Lambropoulos, Professor NKUA, <u>lambrop@uoa.gr</u> HELLENIC REPUBLIC National and Kapodistrian University of Athens EST. 1837

## **DMAPS** Specifications

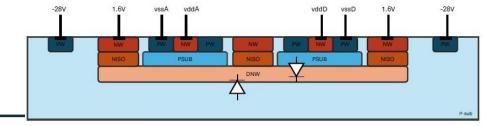

|                           | LOW GAIN PIXEL                            | HIGH GAIN PIXEL                                                       |  |  |

|---------------------------|-------------------------------------------|-----------------------------------------------------------------------|--|--|

| Pixel size                | 200x200 um <sup>2</sup>                   | 100x100 um <sup>2</sup>                                               |  |  |

| Charge range              | 40fC - 9pC                                | 0.5fC -50fC                                                           |  |  |

| Gain                      | 109 mV/pC                                 | 17.5 mV/fC (Q <sub>in</sub> >3fC)<br>120 mV/fC (Q <sub>in</sub> <3fC) |  |  |

| Idle power<br>consumption | 35nA/pixel                                | 7.5uA/pixel                                                           |  |  |

| Noise charge              | 1.5fC                                     | 200aC                                                                 |  |  |

| Digitization              | Embedded SAR ADC 11 bits @ 10 MHz         |                                                                       |  |  |

| Communication             | SPI @ 10 MHz                              |                                                                       |  |  |

| Readout mode              | Only hit pixels/all pixels/specific pixel |                                                                       |  |  |

#### No charge amplifier ! idle power consumption ≈ 35nA @ 1.8 V = 63 nW/pixel For 16 cm<sup>2</sup> covered by 40000 pixels idle power consumption = 2.52 mW A very low power figure !!! idle power consumption ≈ 7.5uA @ 1.8 V = 13.5 µW

/ pixel For 16 cm<sup>2</sup> covered by 160000 pixels Idle power consumption = 2.16 W High power consumption!

## High Gain Pixel

Low gain and High gain sensors combined cover a dynamic range from 0.5fC to 9pC

Common top-level architecture and read-out circuitry for the two sensors

1st DRD3 week on Solid State Detectors R&D, June 17, 2024 @ CERN

vssA = 0V, vddA = 1.8V vssD = 0V, vddD = 1.8V

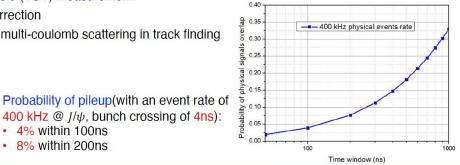

# R&D of a MAPS based Inner Tracker for the STCF

Lailin Xu University of Sci. & Tech. of China On behalf of the STCF MAPS working group

## Design targets

Lailin Xu

- Requirements on the STCF MAPS

- Power consumption:  $\leq 100 mW/cm^2$

- Material budget per layer:  $\leq 0.35\% X_0$

- Spatial resolution:  $\leq 30 \mu m$

- Time resolution:  $\leq 50$  ns (to deal with the pileup issue at high luminosity)

- Time-over-threshold (TOT) measurement:

- Time-walk correction

6/17/24

Correction of multi-coulomb scattering in track finding

4% within 100ns

• 8% within 200ns

STCF = Super Tau Charm Facility

Higher priority on the power consumption than the spatial resolution

## Prototype chips

Lailin Xu

- Designed 4 prototype chips based on the TJ 180nm technology •

- Chip 1: ALPIDE-like small pixels, 0/1 digital readout

- Chip 2: large pixels ( $96\mu m \times 60\mu m$ , Strip-based + Pixel-based) with TOA+TOT readout

- Chip 3: large pixels  $(170\mu m \times 31\mu m, \text{Strip-based} + \text{Pixel-based})$  with TOA+TOT readout

- Chip 4: 3T analog readout (5 types of sensors)

|                       |                                      | Pixel-based                  |                             | Strip-based                  |                             |                |

|-----------------------|--------------------------------------|------------------------------|-----------------------------|------------------------------|-----------------------------|----------------|

|                       | diode<br>In<br>A: pixel<br>30µm×30µm | B: Pixel-based<br>180µm×30µm | C: Pixel-based<br>90µm×60µm | D: Strip-based<br>180µm×30µm | E: Strip-based<br>90µm×60µm |                |

|                       | Chip1                                | Cł                           | nip2                        | Ch                           | ip3                         | Chip4          |

| Pixel size<br>(µm×µm) | 28.1x30.1                            | 96.4x59.6                    |                             | 170.0x31.0                   |                             | Mixed          |

| Sensor                | ALPIDE-like                          | Strip-based                  | Pixel-based                 | Strip-based                  | Pixel-based                 | Mixed          |

| Pixel array           | 16x30                                | 8x12                         | 8x12                        | 60x8                         | 60x7                        | Mixed          |

| Readout               | Token                                | Token<br>√                   |                             | Token                        |                             | Analog readout |

| ToA & ToT             | Х                                    |                              |                             | $\checkmark$                 |                             | X              |

Total area: 5 mm×5 mm Submitted in 2024 Q1

UNIVERSITY

5

24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

14

# **Reports from "generic" R&D**

# Large fill factor DMAPS development at PSI

## May MPW Submission

- Tape out date was May 6 2024

- MPW with 5x5mm<sup>2</sup> area

- 4x5 mm<sup>2</sup> DMAPS chip

- 1x5mm<sup>2</sup> sensor test structures

- 6 metals, deep N-well for charge collection and isolation, deep P-well for isolation

- High res wafers (~3 kOhm cm) supplied by LFoundry

- Post processing:

Sensor

variations

Guard ring

variations

Edge TCT

DMAPS development at PSI

Thinning to 150 um:~12ke- signal (thinner sensors possible, but risk of breaking wafer increases)

17. June 2024

Main DMAPS chip

- backside p+ implant (much more uniform drift field, overdepletion possible→velocity saturation. Good for timing)

- backside metalisation (protection from very sensitive back side)

## Hans-Christian Kästli

## DMAPS chip Panther

- 75μm x 75μm pixel.

- 48 rows, 3x14 columns;

- 3 flavors of preamps, optimized for best timing, lowest power and highest S/N

- No universally best preamp possible. Need to choose/optimize for each specific application

- Pixel has preamp, tunable discriminator, digital logic (kept minimal) and S&H circuit with analog PH readout

- TDC per column

- · Triggered sequential, zero-suppressed readout

- Trigger output •

**DMAPS** development at PSI

- Most digital activity moved to col/row periphery. X-talk is a major issue in this technology!

- · Enormous effort made to shield/decouple signals from extremely sensitive input node  $\rightarrow$  my main concern

17. June 2024

General R&D on DMAPS for future applications in smaller experiments:

- For in-house experiments at PSI

- Also applications outside physics

- Main motivation is low material • budget

- Typical specifications are: relatively low data rates, low radiation tolerance, low-power and timing resolution of O(100-200ps)

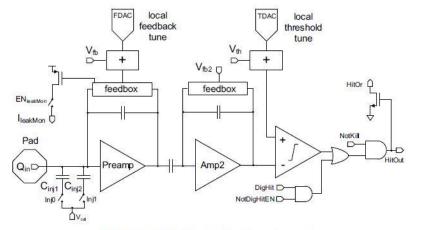

## LF15A pixel cell

digital logic

discriminator

preamp

DMAPS development at PSI

- 3 flavours of preamps •

- Discriminator with global threshold and 3 local trim

- bits, mask bit

- Sample & hold circuit for analog PH readout

- Injection circuit, analog and digital (for timing calibration)

10

Column length: 48 pixel, ~0.36mm

#### 24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

8

17. June 2024

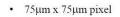

#### **Research on CMOS MAPS at GSI/FAIR – Status and Next Step**

M. Deveaux, GSI

Fair GmbH | GSI GmbH Dr. Michael Deveaux

DRD3 Week CERN 17 June 2024

7

**UK Research**

and Innovation

¥¥

31

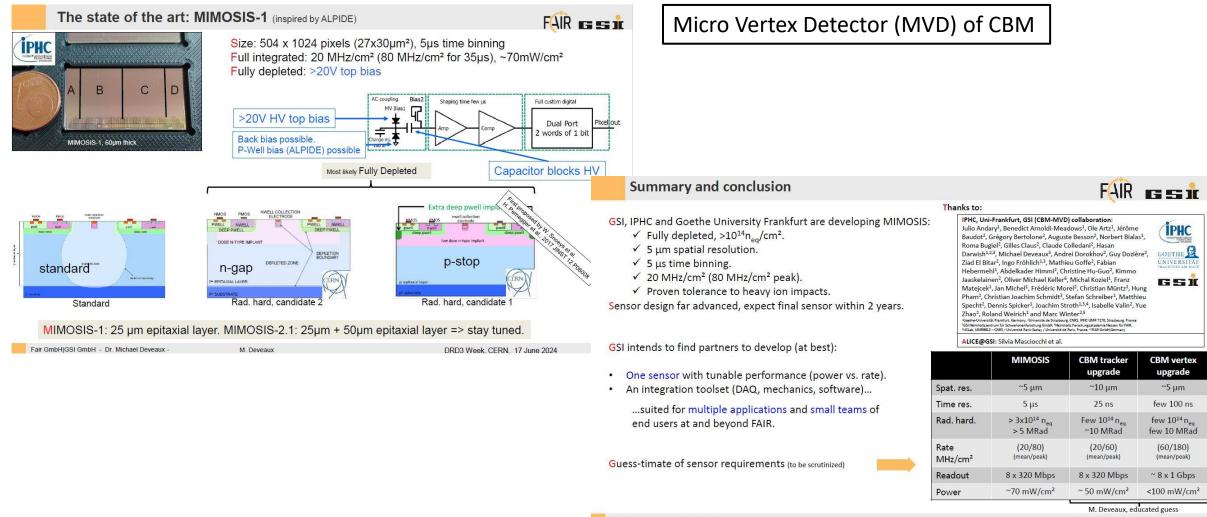

## The ATLASPIX3 CMOS pixel sensor and module performance

Attilio Andreazza - Università di Milano and INFN

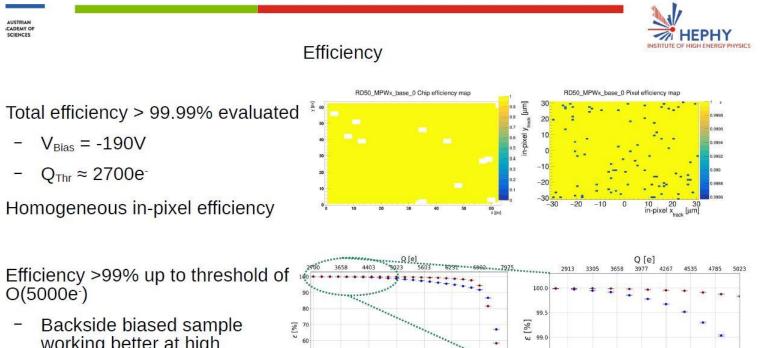

# **Characterization of the RD50-MPW4 HV-CMOS** pixel sensor

- HV-CMOS sensors fabricated in LFoundry 150nm process

- Goals: Evaluation of technology for

- Radiation hardness

- High granularity

- Timing performance

## Bernhard Pilsl (HEPHY), Harald Handerkas (HEPHY)

on behalf of the (former) CERN RD50 CMOS working group

Topside biased

Backside biase

Threshold [mV]

98.5

UK Research and Innovation

350

33

КĚ

Topside biased

Backside biased

140

Threshold [mV]

Efficiency >99% up to threshold of O(5000e<sup>-</sup>)

-

Backside biased sample working better at high thresholds (compared to topside biasing)

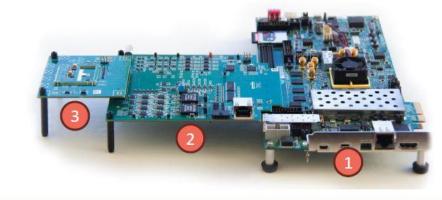

Adaptation and Modularization of MPW4 Firmware for Integration into the Caribou Boreal Architecture: A Pilot project

**Caribou System Architecture**

J. Jiménez-Sánchez<sup>1</sup>, F.R Palomo Pinto<sup>1</sup>,Y- Otarid<sup>2</sup>, J.M. Hinojo-Montero<sup>1</sup>, H.Steininger<sup>3</sup>, B.Pilsl<sup>4</sup>, F. Muñoz-Chavero<sup>1</sup>

**Current Caribou**

Legacy

ZC-706

Propietary

Peary

Propietary

#### 1) System-on-Chip (SoC) board

- ie: Xilinx ZC706 evaluation board

- Embedded CPU runs DAQ and control software

- FPGA runs custom firmware for detector control and readout

#### 2) Control and Readout (CaR) interface board

- Physical interface from SoC to detector

- CaR SoC connection extendable via FMC cable

#### 3) Detector chip board

Custom low-cost PCB

Main goal is to organise into modules and adapt the RD50-MPW4 current firmware to the Caribou's new Boreal firmware architecture

**Boreal Pilot project**

ZCU-102/ZC-706

**Boreal Caribou**

Peary (Boreal adapted)

Propietary (Boreal adapted)

WG1 - https://indico.cern.ch/event/1402825/

4/15

Hardware

**Firmware**

Software

GUI

RESULTS AND PERSPECTIVES OF THE MONOPIX2 DEPLETED MONOLITHIC ACTIVE PIXEL SENSORS

Lars Schall, Marlon Barbero, Pierre Barrillon, Christian Bespin, Patrick Breugnon, Ivan Caicedo, Yavuz Degerli, Jochen Dingfelder, Tomasz Hemperek, Toko Hirono, Fabian Hügging, Hans Krüger, Konstantinos Moustakas, Patrick Pangaud, Heinz Pernegger, Petra Riedler, Piotr Rymaszewski, Philippe Schwemling, Walter Snoeys, Tianyang Wang, Nobert Wermes, and Sinuo Zhang

# Conclusion & Outlook

## LF-Monopix2:

- Excellent radiation hardness without significant performance degradation up to 2 x 10<sup>15</sup> neq/cm<sup>2</sup> NIEL fluence and 100 Mrad TID

- Further irradiation up to 5 x10<sup>15</sup> neq/cm<sup>2</sup> NIEL fluence planned

#### TJ-Monopix2:

- Very low noise and low threshold operation with excellent spatial resolution

- >99 % hit-detection efficiency and very high in-time ratio >99 % within 25 ns

- Fully functional after 100 Mrad TID

- Characterization of irradiated samples up to 1.5 x 10<sup>15</sup> neq/cm<sup>2</sup> NIEL fluence ongoing

#### Perspectives:

New DMAPS based on TJ-Monopix2 under development for Belle II VXD upgrade -<u>talk by M. Babeluk</u>

6/17/24

Lars Schall - lars.schall@uni-bonn.de

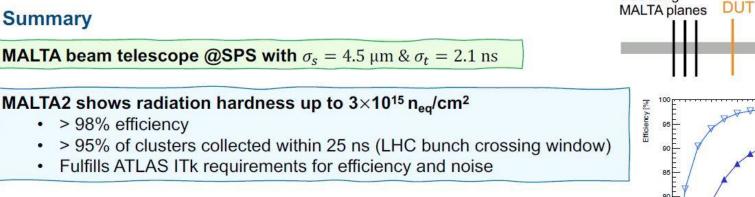

## Radiation hardness and timing performance of MALTA monolithic Pixel sensors in Tower 180 nm

Lucian Fasselt

Scintillator

for timing

17 June 2024

6 tracking

MALTA2 shows radiation hardness up to 3×10<sup>15</sup> n<sub>ed</sub>/cm<sup>2</sup>

- > 98% efficiency

- > 95% of clusters collected within 25 ns (LHC bunch crossing window)

- Fulfills ATLAS ITk requirements for efficiency and noise

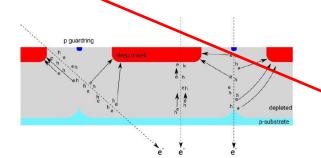

#### **Depletion depth studies:**

- Edge-TCT

- Grazing angle studies

- Amplitude reconstruction from binary hit data

#### MALTA3:

Summary

- Time-stamping logic on chip @ 1.28GHz aiming for sub-nanosecond timing

- Serialised data output in view of future detector integration

#### Future developments:

"Radiation hard read-out architectures" (WG1 C. Solans) Tue 9:00 "Interconnections and multi-chip flex developments" (WG7 A. Sharma) Wed 13:30

DRD3 | MALTA | L. Fasselt | 17 June 2024

### 24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

#### Mini-MALTA3

- $5 \times 4 \text{ mm}^2$  demonstrator with  $64 \times 48$  pixels

- Pixel size  $36.4 \times 36.4 \,\mu\text{m}^2$  (same as MALTA2)

- Same front-end as MALTA2, no clock over the matrix

- Integrate time-stamping and data serialiser on chip in periphery

- Time-stamping logic at 1.28 GHz (for MALTA2 done in FPGA)

- → aiming for sub-nanosecond on-chip timing resolution

- Synchronization memory with 0.78 ns time resolution

- Fast clock generation with STFC PLL from 80 MHz clock

- Serialized high-speed output

12/12

## Development of MAPS using 55nm HVCMOS Process for future tracking detectors

## Yiming Li (IHEP, CAS) On behalf of the COFFEE development team

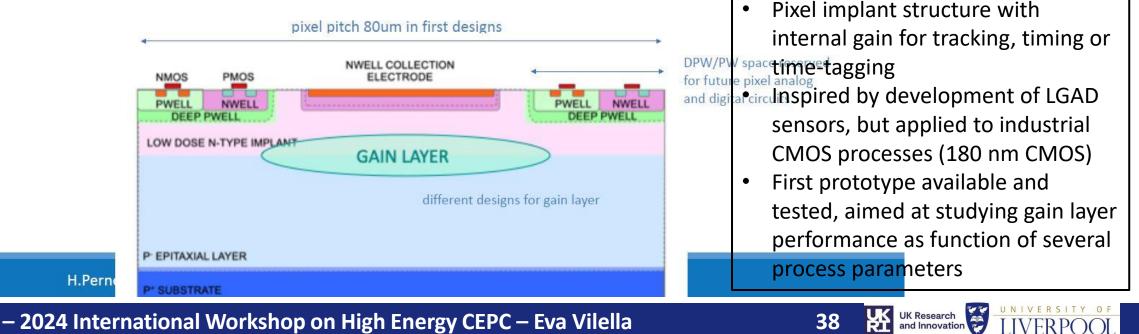

# CMOS Sensors with internal gain

CASSIA CMOS Active SenSor with Internal Amplification

Sebastian Haberl, Anastasia Kotsokechagia, Jenny Lunde, Heinz Pernegger / CERN EP-ADE-TK I. Berdalović, Borna Požar, T. Suligoj / FER University Zagreb

КŁ

38

## Initial design idea for sensor with internal gain

- inspired by development of LGAD sensors but applied to industrial CMOS process (200mm) wafer, 0.18um CMOS process with high production volume)

- "Tracker-like" pixels with 80um pitch (first prototype)

- larger round electrodes (~40um diagonal) but also enlarged area for analog and digital circuit

- DPW for full CMOS electronics in pixel already foreseen now to allow future scaling of results to larger matrix

## 24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

CERN

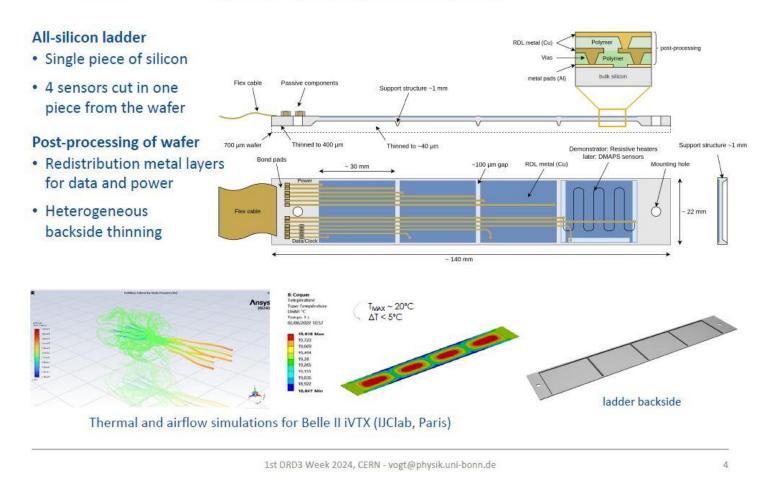

## ALL-SILICON LADDER CONCEPT FOR CMOS MONOLITHIC PIXEL DETECTORS

J. Dingfelder<sup>B</sup>, J. Grosse-Knetter<sup>G</sup>, H. Krüger<sup>B</sup>, C. Lacasta<sup>V</sup>, C. Marinas<sup>V</sup>, A. Quadt<sup>G</sup>, A. Ulm<sup>B</sup>, <u>M. Vogt<sup>B</sup></u> Affiliations: U. Bonn (B), U. Göttingen (G), IFIC Valencia (V)

## ALL-SILICON LADDER CONCEPT

- Motivation is Belle II LS2

- Monolithic active CMOS pixel sensor OBELIX

- Also generic R&D for future colliders (e.g. FCC)

## Innovations in CMOS Pixel Sensor Technology Future P ec:

#### Application-oriented sensor in Tower 180 nm

#### MIMOSIS — CBM-MVD

#### Fully designed at C4Pi

- Collaboration with IKFrankfurt & GSI

- □ 5 µm 5 µs 20 (70) MHz/cm<sup>2</sup> continuous read-out

- Modified process & AC-diode (full or partial depletion)

- □ Series of submission:  $2017 \rightarrow 2025$

- More in M. Deveaux's talk

- OBFLIX Belle II-VTX

- Design within a wide collaboration:

- Uni.Bergamo, Uni.Bonn, CPPMarseille, Tech.Uni.Dortmund, HEPHY-Vienna, IEIC-Valencia, INEN-Pavia, KEK-Tsukuba

- □ 10 µm 50 ns 120 MHz/cm<sup>2</sup> triggered read-out Modified process & DC or AC-diode (full depletion)

- □ Started 2022: 1<sup>st</sup> version in 2024

- More in M. Babeluk's talk

- QUARTPIC submissions

- Multi-project engineer runs organised by C4Pi

12 μm / 10 ns / 100 kHz/cm<sup>2</sup> continuous read-ou

for energy measurement over a wide range

□ Small size prototype (5x7 mm<sup>2</sup>) for ion tracking & identification

- Include internal R&D with small chips

- Mostly focus on DRD7 activities

linear dynamic up to ~800 ke-

Modified process (full depletion)

□ Series of submissions:  $2020 \rightarrow 2024$

Design with: IP2I-Lyon

- □ 1<sup>st</sup> run 2021 (French projects + China)

- 2<sup>nd</sup> run 2024 (French projects + CERN + China)

- □ 3<sup>rd</sup> run under discussion for 2025

- Small prototype (2x2 mm<sup>2</sup>) for new matrix read-out

- Design with: IRFU-Saclay

#### Contribution from CERN-EP R&D & ALICE-ITS3 (DPTS pixel front-end)

- Full asynchronous read-out logic

- Clockless 20 ns time-stamping

- ~10 mW/cm<sup>2</sup> in matrix

## Frédéric Morel on behalf of IPHC teams

#### Focus on two technologies:

- Tower 180 nm is a well-established technology

- Tower 65 nm is where future cuttingedge developments are made

- MOSAIX ALICE-ITS3

Technological R&D in Tower 180

- Wafer scale sensor ASICs with stitiching

- Ultra-thin and bendable: 50 μm

- Tower 65 nm

- $\Box$  5  $\mu$ m 2  $\mu$ s ~6 MHz/cm<sup>2</sup> continuous readout

- □ Series of submission: 2021 → 2025

Contribution in analogue biasing

- Large design team

- □ IPHC design effort:

17/06/2024

frederic.morel@iphc.cnrs.fr - 1st DRD3 week on Solid State Detectors R&E

Responsibility of matrix integration (DoT)

frederic.morel@iphc.cnrs.fr - 1st DRD3 week on Solid State Detectors R&D

UK Research and Innovation **UK Research**

echnological R&D in Tower 65 nm: Charge collection study SPARC Pitch (µm) Spatial Res. (µm) Tel. res. Subtracted (2.1 µm 22.5 ~5.1 18 ~4.1 15 ~3.2 22.5 ~2.4 18 ~1.8

17/06/2024

TIIX

□ 1st submission 2024

40

RI

24.10.2024 – 2024 International Workshop on High Energy CEPC – Eva Vilella

Process Small matrix (2x2 mm<sup>2</sup>) exploring new process

> Process - GAP Pitch - 22.6 um

frederic.morel@iphc.cnrs.fr - 1st DRD3 week on Solid State Detectors R&E

frederic.morel@iphc.cnrs.fr - 1st DRD3 week on Solid State Detectors R&D

GAP

GAP

GAP

STD

STD

STD

15

Only square diode arrangement

~1.3

- Simple architecture:

- Analog output

- Rolling shutter readout

- Variations on:

17/06/202

17/06/202/

CE65 chips

- Process Standard-Modified-Modified with gaps .

- . Diode arrangement (squared or staggered)

- Pitchs 15—18—22.5 µm

- Series of 2 submission 2021 and 2023

- Partners share analysis and measurements

- IPHC CTU Prague UZH Zurich

## The H2M project: Porting the functionality of a hybrid readout chip into a monolithic 65 nm CMOS imaging process

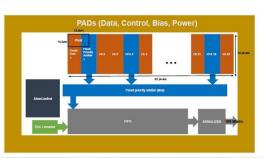

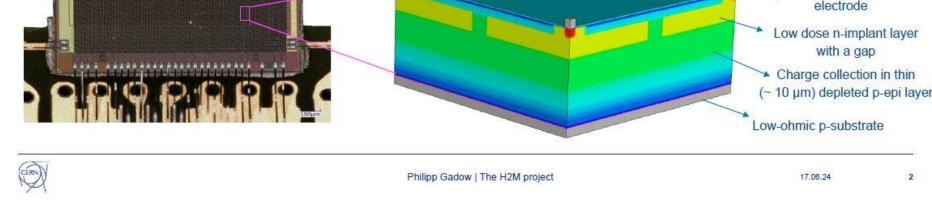

# H2M (Hybrid-to-Monolithic)

Ports a hybrid pixel detector architecture into a monolithic chip.

- Digital-on-top design workflow.

- Manufactured in a TPSCo 65 nm CMOS imaging process.

- 35 µm pixel pitch in 64x16 pixel matrix (total sensitive area: 2.24 × 0.56 mm<sup>2</sup>). Total thickness ~ 50 µm.

- Analog and digital front-end per pixel.

Rafael Ballabriga, Eric Buschmann, Michael Campbell, Raimon Casanova Mohr, Dominik Dannheim, Ana Dorda, Finn Feindt, Philipp Gadow, Ingrid-Maria Gregor, Karsten Hansen, Yajun He, Lennart Huth, Iraklis Kremastiotis, Corentin Lemoine, Stefano Maffessanti, Larissa Mendes, Younes Otarid, Christian Reckleben, Sebastien Rettie, Manuel Alejandro del Rio Viera, Sara Ruiz Daza, Judith Schlaadt, Adriana Simancas, Walter Snoevs, Simon Spannagel, Tomas Vanat, Anastasija Velvka, Gianpiero Vignola, Håkan Wennlöf

(p-epitaxial laver ~ 10 µm)

P-well hosting full

Small n-collection

CMOS circuitry

#### Conclusions

Fully functional digital-on-top sensor in a 65 nm CIS.

Calibration and characterisation of performance with laboratory and test beam measurements.

Fully efficient operation in test beam:

• 27 e- noise, 200 e- minimum threshold, >99.1% efficiency.

Impact of n-wells on charge-collection efficiency observed and qualitatively confirmed by simulations.

Timing performance dominated by sensor effects? >  $\sim$ 30 ns.

Outlook: investigating the possibility of backside-thinning the chips from 50 um to <~30 um, to explore impact of thickness on performance.

2