# CMOS Strip Development for CEPC ITK

#### Xin Shi

On behalf of CEPC Silicon Tracker Team

2024.10.24

2024 CEPC International Workshop

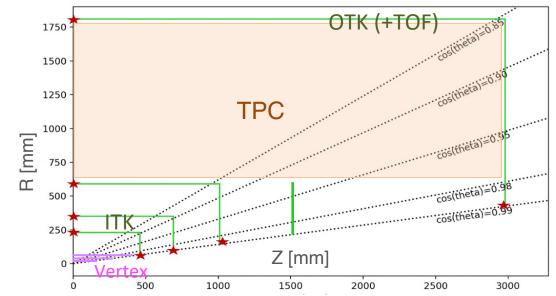

# Why Strips for CEPC Inner Tracker?

- CEPC physics requirements impose technical challenges on silicon tracker

- Spatial resolution  $\sigma_{\phi}$ < 10 µm,  $\sigma_z$ < 50 µm (barrel) and  $\sigma_z$ < 100 µm (endcap)

- Low material budget:  $< 1\% X_0$  per layer

- A few nano-seconds timing resolution to tag 23 ns bunch crossing

- Cost effective area to cover ~20 m<sup>2</sup>

**ATLAS**

(quadrant)

Mark II

CDF

· pixels –

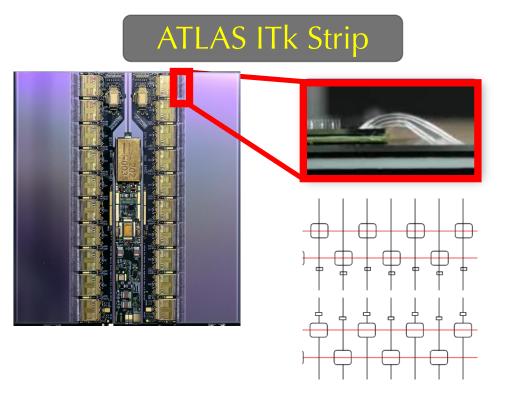

- Silicon strip is mature and widely used in HEP experiments

- HERA, H1, ATLAS, CMS, ALICE, LHCb ...

- Largely used for the HL-LHC upgrade

- ATLAS ITk strip, CMS Outer Tracker ...

- Rich experience on strip detector development at IHEP

- Complete production facility and team members at IHEP

- Experience in sensor, ASIC, strip module construction, and testing

### Why CMOS Strip? (vs Hybrid silicon strip + ASICs)

- High spatial resolution impose challenging pitch size for strip detector design and fabrication

- Less than 30  $\mu m$  pitch to reach <10  $\mu m$  spatial resolution

- Wire bonding will be a nightmare

- ATLAS ITk Strip: 4 layers of wires / chip

- CMOS Strip can combine active detection layer and readout electronics into a single structure

- no wire bonding for each channel

- Industrial standard to reduce cost eventually

- ATLAS ITk strip: all in one company > 3 years production of strip sensors

Complicated bonding structure

- 4 layers of wires / chip

- 5k wire bonds / module

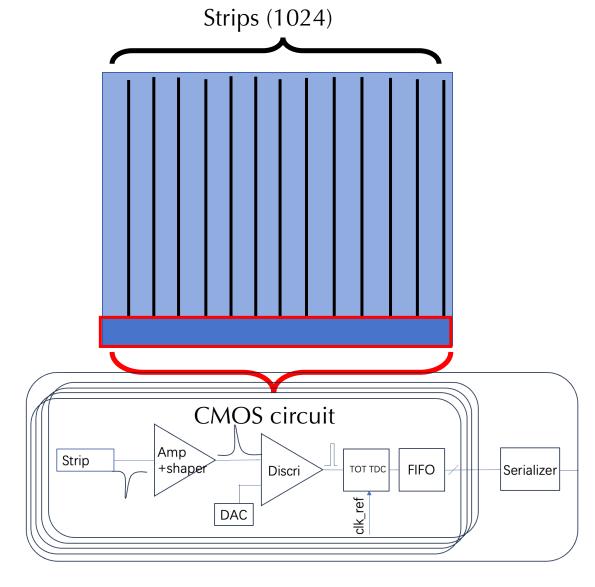

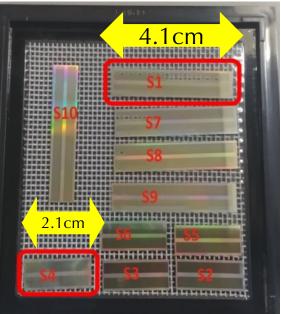

## CMOS Strip Chip - CSC

#### Version 1.3

| CSC Parameters      |                                                            |

|---------------------|------------------------------------------------------------|

| Strip width         | 10 μm                                                      |

| Strip pitch         | 20 μm                                                      |

| Strip number / chip | 1,024                                                      |

| Chip size           | 2.1×2.3 cm <sup>2</sup><br>(active area: 2.05 cm x2.05 cm) |

| Spatial resolution  | σ~5 μm                                                     |

| Time resolution     | ~3 ns                                                      |

| Power consumption   | ~80 mW/cm <sup>2</sup>                                     |

| Data size per hit   | 32 bits (10b BXID, 10b address,<br>6b TOT + other 6 bits)  |

| Event rate / chip   | Maximum ~0.25 Gbps<br>(CEPC Endcap note)                   |

| LV / HV             | 1.8 V / 200 V                                              |

| Wafer resistivity   | $2k \Omega cm$                                             |

| Technology Node     | 180 nm                                                     |

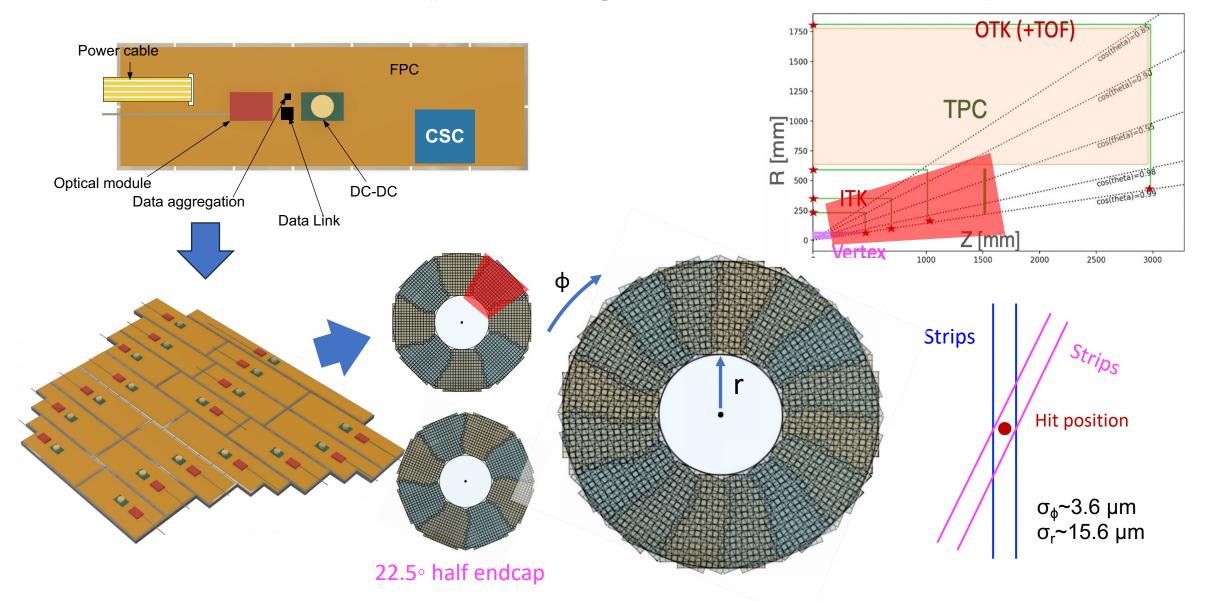

#### CEPC ITK Endcap Design – CMOS Strips

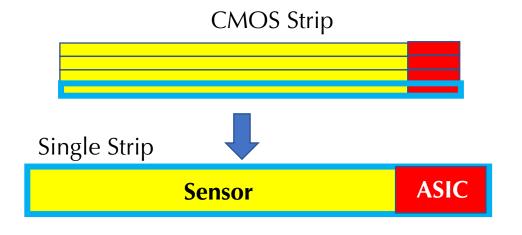

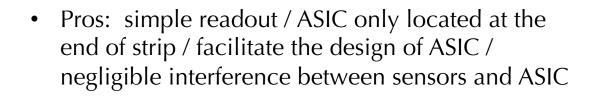

### CMOS Strip Chip – Basic Concept

• CMOS strip is different than CMOS pixel

• Cons: large capacitance of strip sensor

- Pros: small capacitance of sensor

- Cons: ASICs and sensors share same area with interference between sensor and ASIC

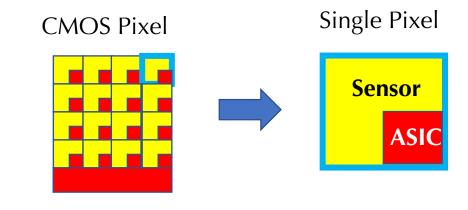

# Existing passive CMOS sensor

Diehl et. al, Characterization of passive CMOS strip sensors, NIMA 1033 (2022) 166671

- First large sized CMOS passive sensor (> 4 cm)

- 75.5µm pitch on 6-inch, 3-5 k $\Omega$  wafer with LFoundary 150 nm

- Successfully tested of strip sensor behavior

- Confirmed feasibility of CMOS strip sensor path

- Passive CMOS without ASIC design, no integrated chip yet

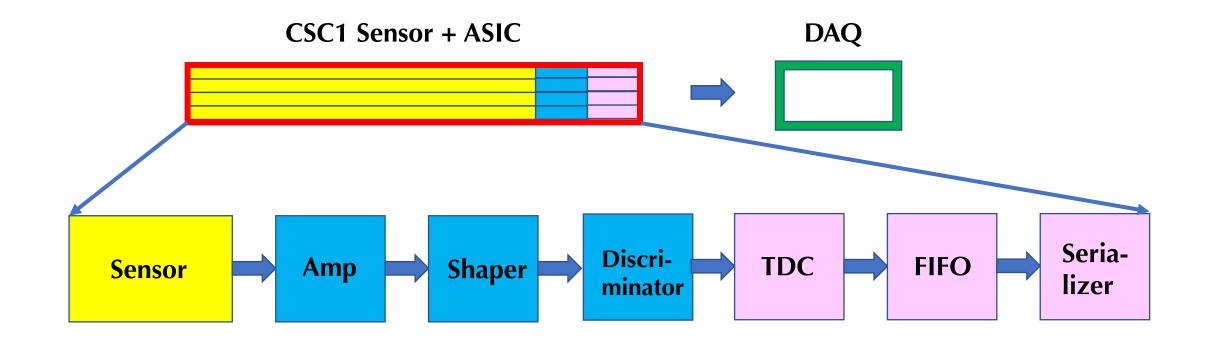

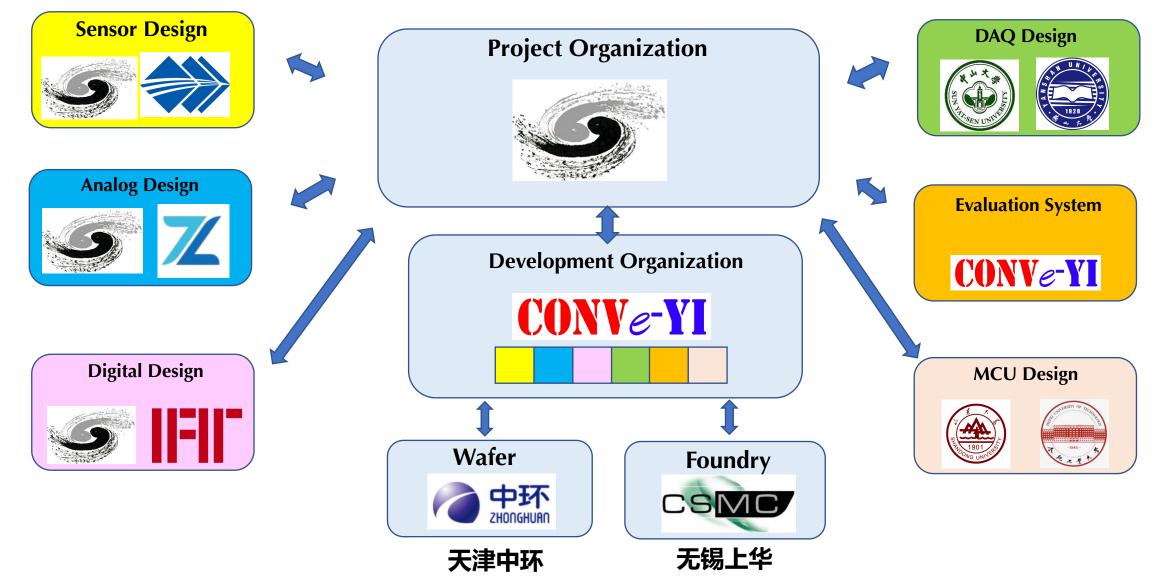

### CSC1 Design Diagram

Evaluation System

#### **CSC** Participating Institutes

北京科维泰信科技有限公司

IFII

#### 山东高等技术研究院 SHANDONG INSTITUTE OF ADVANCED TECHNOLOGY

中国科学院微电子研究所

INSTITUTE OF MICROELECTRONICS OF THE CHINESE ACADEMY OF SCIENCES

• All institutes are members of <u>RASER</u> Team

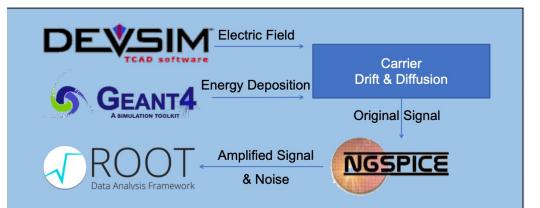

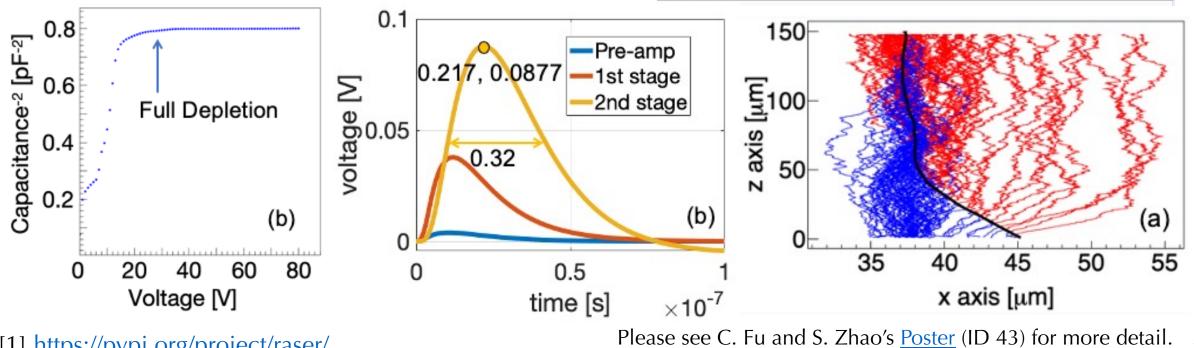

### CSC Simulation with open source RASER

- Simulation based on RASER code <sup>[1]</sup>

- CMOS sensor / electronics / response to laser and MIP

https://pypi.org/project/raser/

#### **CSC** Developer Orgnization

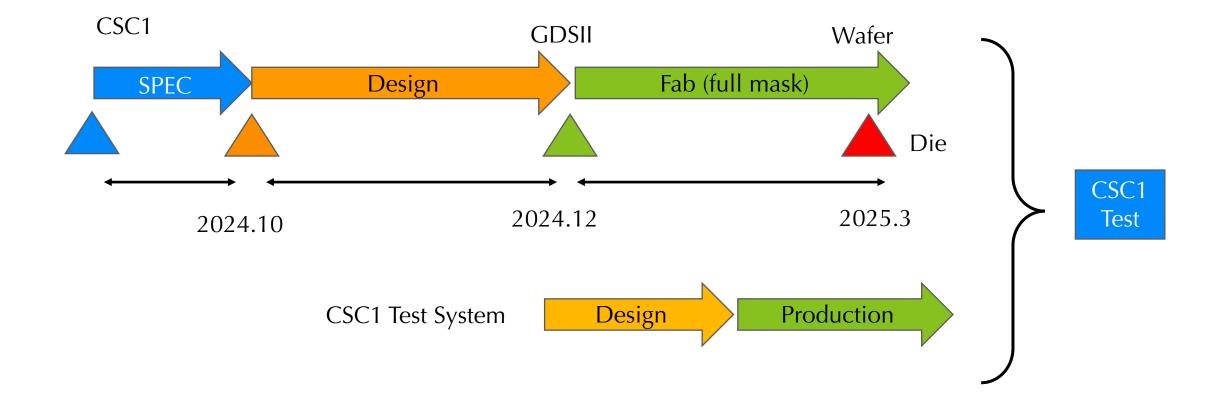

### Timeline for CSC1

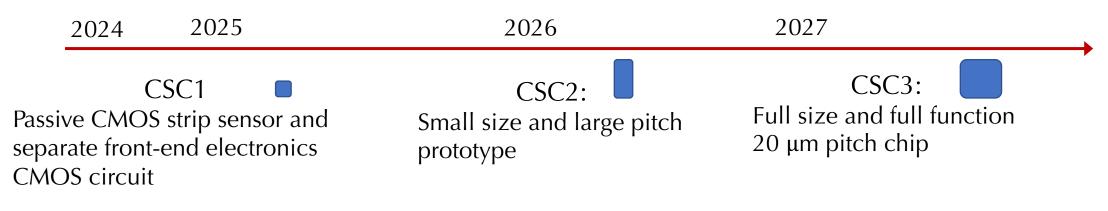

### Summary and Plan

- Hybrid silicon strip is mature and widely used technology in HEP experiment.

- Our target is to develop CMOS strip, which integrates active detection layer and readout electronics into a single chip to achieve ultimate spatial resolution better than **5 μm**.

- CEPC ITK choose CMOS Strip as one baseline for endcap.

- CMOS Strip Chip (CSC) development is steadily progressing.

Welcome to join us!

#### 中國科學院為能物現為完備 Institute of High Energy Physics Chinese Academy of Sciences