### CEPC Electronics System for Ref-TDR Overview, Status & Plan

### Wei Wei

On behalf of the Elec-TDAQ system of the CEPC Ref-TDR

**IHEP, CAS**

2024-10-26 CEPC Workshop 2024, Hangzhou

### **Outline**

- Global Framework of the Elec-TDAQ system

- Main challenges & tasks of the FEE of Sub-Det

- Key blocks & plan of the common electronics

- Summary

### **Requirement from Sub Detectors (@Higgs)**

|                                   | Vertex                                                    | Pix(ITKB)                                              | Strip<br>(ITKE)                                        | ОТКВ                                           | ОТКЕ                                             | ТРС                                   | ECAL-B                                           | ECAL-E                                   | HCAL-B                                                         | HCAL-E                                                         | Muon                                               |

|-----------------------------------|-----------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------------------|------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|

| Channels<br>per chip              | 512*1024<br>Pixelized                                     | 512*128                                                | 1024                                                   | 1:                                             | 28                                               | 128                                   |                                                  |                                          | 8~16<br>@common SiPM A                                         | SIC                                                            |                                                    |

| Ref. Signal processing            | XY addr +<br>BX ID                                        | XY addr +<br>timing                                    | Hit + TOT<br>+ timing                                  | ADC+TDC/TOT+TOA                                |                                                  | ADC + BX<br>ID                        | TOT + TOA/<br>ADC + TDC                          |                                          |                                                                |                                                                |                                                    |

| Data Width<br>/hit                | 32bit                                                     | 42bit                                                  | 32bit                                                  | 40~48bit 48bit                                 |                                                  | 48bit                                 | 48bit                                            |                                          |                                                                |                                                                |                                                    |

| Max Data<br>rate / chip           | 2Gbps/chi<br>p@Trigge<br>rless@Lo<br>w LumiZ<br>Innermost | Avg.<br>3.53Mbps/c<br>hip<br>Max.<br>68.9Mbps/c<br>hip | Avg.<br>21.5Mbps/c<br>hip<br>Max.<br>100.8MHz/<br>chip | Avg:<br>2.9Mbps/chip<br>Max:<br>3.85Mbps/chip  | Avg:<br>38.8Mbps/chip<br>Max:<br>452.7Mbps/chip  | ~70Mbps/<br>module<br>Inmost          | Avg. 0.96Gbps/<br>Max:9.6Gbps/m                  |                                          | Max.<br>144Mbps/modul<br>e-layer                               | Max.<br>350Mbps/modul<br>e-layer                               | Avg: 15.36<br>Mbps/chip<br>Max: 153.6<br>Mbps/chip |

| Data<br>aggregation               | 10~20:1,<br>@2Gbps                                        | 14:1@O(10<br>0Mbps)                                    | 22:1<br>@O(100Mb<br>ps)                                | i. 22:1<br>@O(5Mbps)<br>ii. 7:1<br>@O(100Mbps) | i. 22:1<br>@O(50Mbps)<br>ii. 10:1<br>@O(500Mbps) | 1. 279:1<br>FEE-0<br>2. 4:1<br>Module | i. 4~5:1 side<br>ii. 7*4 / 14*4 ba<br>O(100Mbps) | ck brd @                                 | < 10:1<br>(40cm*40cm<br>PCB –<br>4cm*4cm tile –<br>16chn ASIC) | < 10:1<br>(40cm*40cm<br>PCB –<br>4cm*4cm tile –<br>16chn ASIC) | <=24:1<br>@ O (400 Mbps)                           |

| Detector<br>Channel/m<br>odule    | 1882<br>chips<br>@Stch<br>&Ladder                         | 30,856<br>chips<br>2204<br>modules                     | 23008<br>chips<br>1696<br>modules                      | 83160 chips<br>3780 modules                    | 11520 chips<br>720 modules                       | 492<br>Module                         | 0.96M chn<br>~60000 chips<br>480 modules         | 0.52M chn<br>~32500 chips<br>260 modules | 3.38M chn<br>5536<br>aggregation<br>board                      | 2.24M chn<br>1536<br>Aggregation<br>board                      | 43.2k ch<br>72 Aggregation<br>board                |

| Avg Data<br>Vol before<br>trigger | 474.2Gb<br>ps                                             | 101.7Gbp<br>s                                          | 298.8Gbp<br>s                                          | 249.1Gbps                                      | 27.9Gbps                                         | 34.4Gbps                              | 460Gbps                                          | 250Gbps                                  | 811.2Gbps                                                      | 537.6Gbps                                                      | 24.1 Gbps                                          |

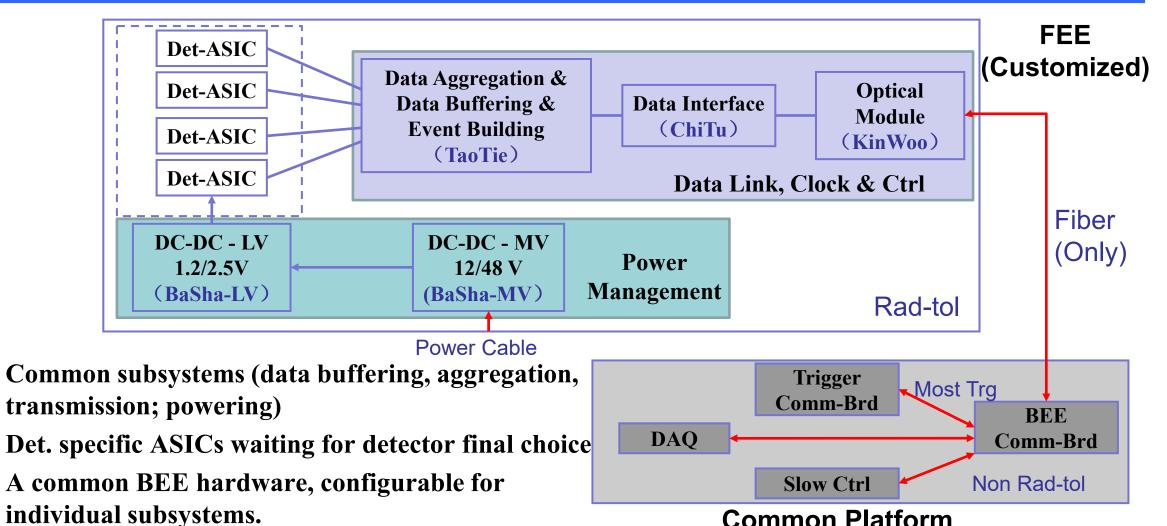

## **Global framework of the CEPC Elec system**

٠

**TDAQ** interface is (probably) only on BEE

**Common Platform**

### Outline

- Global Framework of the Elec-TDAQ system

- Main challenges & tasks of the FEE of Sub-Det

- New technology: Wafer-scale chip design with stitching

- High performance for Q & T

- > Ultra low power & cooling

- Limited space vs advanced PCB & packaging

- Key blocks & plan of the common electronics

- Summary

# **Detector Key Specifications**

| Sub-system         | Key technology                                             | Key Specifications                                                                                                                           |

|--------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Vertex             | 6-layer CMOS SPD                                           | $\sigma_{r\phi} \sim 3 \ \mu m, \ X/X_0 < 0.15\%$ per layer                                                                                  |

| Tracking           | CMOS SPD ITK, AC-LGAD SSD OTK,<br>TPC + Vertex detector    | $\sigma\left(\frac{1}{P_T}\right) \sim 2 \times 10^{-5} \oplus \frac{1 \times 10^{-3}}{P \times \sin^{3/2} \theta} (GeV^{-1})$               |

| Particle ID        | dN/dx measurements by TPC<br>Time of flight by AC-LGAD SSD | Relative uncertainty ~ 3% $\sigma(t)$ ~ 30 ps                                                                                                |

| EM calorimeter     | High granularity crystal bar PFA calorimeter               | EM resolution ~ $3\%/\sqrt{E(GeV)}$<br>Granularity ~ $1 \times 1 \times 2 \text{ cm}^3$                                                      |

| Hadron calorimeter | Scintillation glass PFA hadron calorimeter                 | Support PFA jet reconstruction<br>Single hadron $\sigma_E^{had} \sim 40\% / \sqrt{E(GeV)}$<br>Jet $\sigma_E^{jet} \sim 30\% / \sqrt{E(GeV)}$ |

- Design of the CEPC detector evolves with R&D progressing and better understanding of the physics reach.

- The key specifications continue to be optimized.

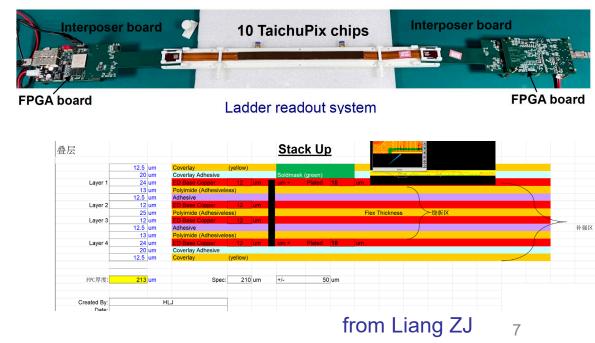

- Baseline: stitching and RDL metal layer on wafer to replace PCB

- Alternative: flexible PCB

- Signal, clock, control, power, ground will be handled by control board through flexible PCB

baseline: ALICE ITS3 like stitching and RDL layer on bent MAPS [1]

[1] ALICE ITS3 TDR: https://cds.cern.ch/record/2890181

#### Alternative: flexible PCB

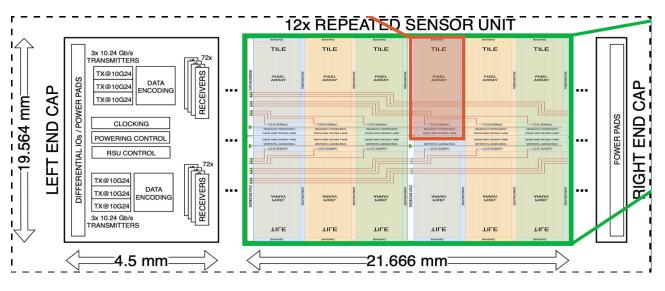

### New technology: wafer-scale chip design with stitching

#### Stitching technology

- Reliability strategy due to the potential risk introduced by bending & thinning

- Redundancy & reliability switches may needed from the top level design

- Conservative design rule needed, routing resources limited

- $\succ$  Chip size from 2.5cm → 25cm

- Long transmission length for both signals and power, parasitics dramatically impact

- Timing sequence for ultra large chip size

#### High rate vs background

- BX Freq @40MHz while power limits to 40mW/cm<sup>2</sup>

- Pixel frontend requires more power to match the BX ID

- FEE-Triggerless readout vs high background

- 1~2Gbps raw data rate for a RSU area @ Low LumiZ

- New process from industrial

- RDL to help the long distance transmission & powering

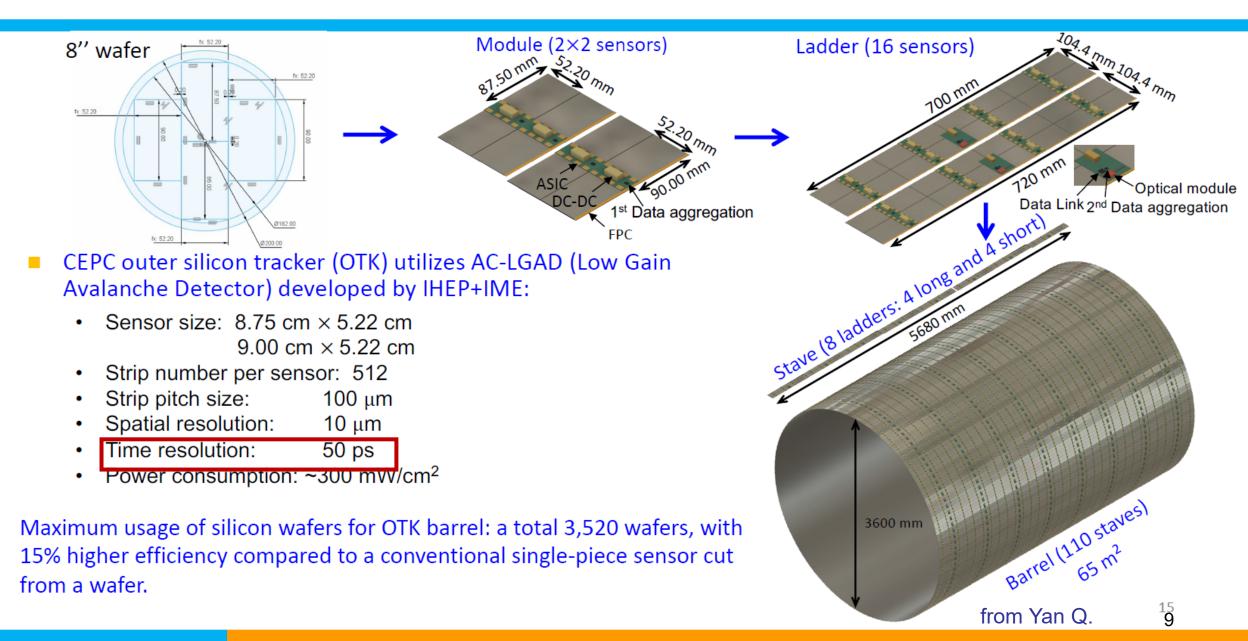

# **CEPC OTK Barrel Design (AC-LGAD Strips)**

# **Crystal ECAL: specifications**

| Key Parameters         | Value                   | Remarks                                              |

|------------------------|-------------------------|------------------------------------------------------|

| MIP light yield        | ~200 p.e./MIP           | Ensure EM resolution $\sim 3\%/\sqrt{E}$             |

| Energy threshold       | 0.1 MIP                 | Balance between S/N and dynamic range                |

| Crystal non-uniformity | < 1%                    | Along the crystal length and between crystals        |

| Dynamic range          | 0.1~3000 MIPs / channel | Maximum energy deposition with 360 GeV Bhabha        |

| Timing resolution      | ~500 ps @ 1 MIP         | Bunch Crossing ID; clustering and hadron performance |

#### Detector requirements

- Moderate MIP light yield

- Good uniformity

- Optimal time resolution

- Large dynamic range

- Moderate S/N ratio

Hardware activities: addressing crucial issues

- SiPM response linearity

- Uniformity of long crystal bar

- Time resolution: different crystal dimensions

- Dynamic range of electronics

- Energy response of crystal module

### Challenges for high performance Q & T vs ultra low power

#### • OTK: 300mW/cm2 vs $\sigma_t \sim 50$ ps

- > Detector Cd: 10pF @CEPC AC-LGAD vs ATLAS HGTD 4pF, while timing is aiming the same

- Power  $\propto$  Cd², estimated 15mW/chn @  $\sigma_t \sim$  30ps

- Optimization of the detector expected, while a smart design of ASIC with low power is also critical

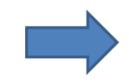

#### TPC: 280µW/chn vs 500µm Pixel

High precision Q & T measurement in very limited power

#### • SiPM ASIC for ECAL, HCAL & Muon, 15mW/chn

- > 0.1~3000 MIPs/chn, requires 2~3 gain channels per input

- $\succ$  0.5ns time resolution at the same time

- > 15mW/chn  $\rightarrow$  120kW of CAL in total, also expects a low power solution

#### Comment & Solution

- Co-optimization with ASIC & Detector: Cd matters a lot

- > Can we be benefit from advanced ASIC technology node? Speed maybe yes, others maybe no

- Can we find a smarter FEE design scheme?

### **Preliminary readout scheme of Pixel TPC**

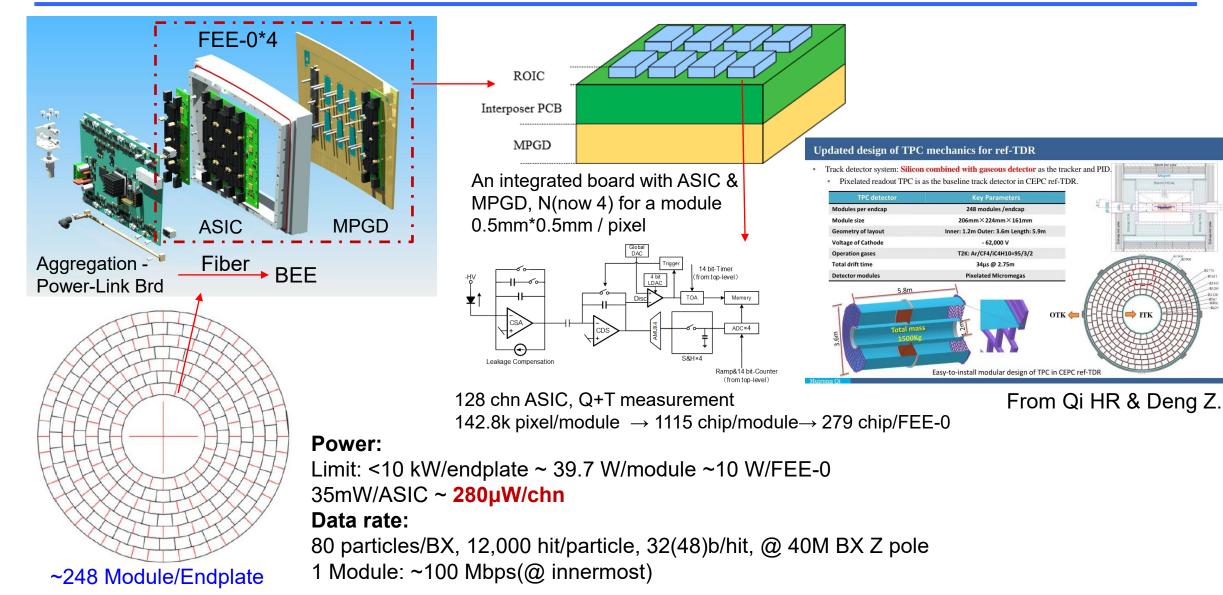

# **Barrel ECAL: module integration**

### Limited space vs advanced PCB & packaging

#### • ECAL module

> A 1cm high & 40cm long narrow PCB, with close touch to SiPM, and density ASICs & routing only on one side

#### HCAL module

- > A thin (1.2mm) but wide (40cm $\times$ 40cm) PCB is allowed, risk of wrapping

- > While no large component is allowed, challenges for the local powering

#### TPC module

- Multiple layers with high density ASICs & sockets for the pixel TPC

- Cooling pipe embedded closely with PCB & module

#### • VTX Flex Cable

- > Low material PCB based on AI is expected, while currently no vendor is available

- A dedicated development may be needed

#### Comment

Co-R&D and collaboration with PCB vendors become critical

### Outline

- Global Framework of the Elec-TDAQ system

- Main challenges & tasks of the FEE of Sub-Det

- Key blocks & plan of the common electronics

- Common data link

- Common powering

- Common BEE

- Wireless communication based scheme

- Summary

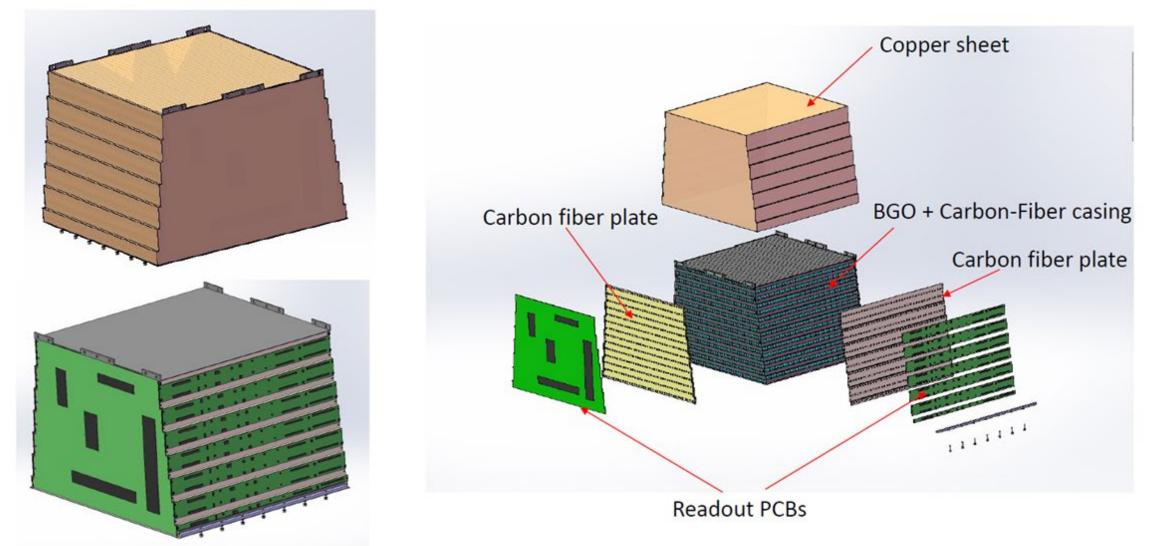

## **Structure of the Data Transmission**

- Pre-Aggregation ASIC (TaoTie): Intend to fit with different front-end detector (different data rates/channels)

- GBTx-like ASIC (ChiTu): Bidirectional serdes ASIC including ser/des, PLL, CDR, code/decode ...

- Array Laser Driver ASIC + TIA ASIC + Customized Optical module (KinWoo)

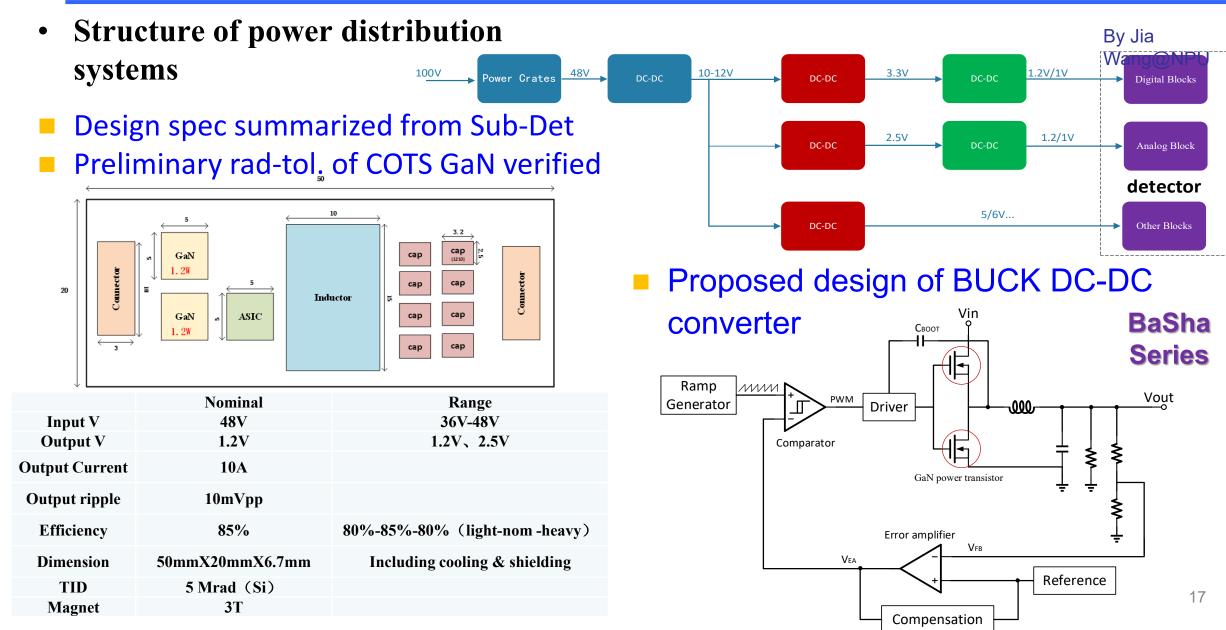

## **Power distribution & DC-DC module**

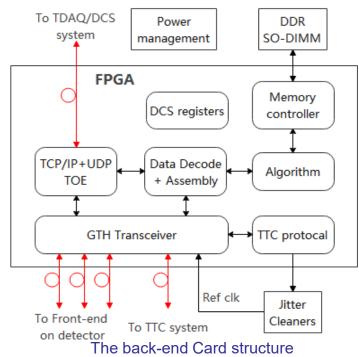

## **Diagram & prototype of common BEE**

Data aggregation and processing board Prototype for Vertex detector

- Routing data between optical link of front-end and the highspeed network of DAQ system.

- Connect to TTC and obtain synchronized clock, global control, and fanout high performance clock for front-end. ٠

- Real-time data processing, such as trigger algorithm and data assembly. ٠

- On-board large data storage for buffering.

- Preference for Xilinx Kintex UltraScale series due to its cost-effectiveness and availability.

|                   |                                          |                                            |                                            | 1                                          |                  |

|-------------------|------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|------------------|

|                   | KC705<br>(XC7K32<br>5T-<br>2FFG90<br>0C) | KCU105<br>(XCKU0<br>40-<br>2FFVA11<br>56E) | VC709<br>(XC7VX<br>690T-<br>2FFG17<br>61C) | VCU108<br>(XCVU0<br>95-<br>2FFVA2<br>104E) | XCKU11<br>5      |

| Logic<br>Cells(k) | 326                                      | 530                                        | 693                                        | 1,176                                      | 1451             |

| DSP<br>Slices     | 840                                      | 1920                                       | 3,600                                      | 768                                        | 5520             |

| Memory<br>(Kbits) | 16,020                                   | 21,100                                     | 52,920                                     | 60,800                                     | 75,900           |

| Transcei<br>vers  | 16(12.5G<br>b/s)                         | 20(16.3<br>Gb/s)                           | 80(13.1G<br>b/s)                           | 32(16.3G<br>b/s) and<br>32(30.5G<br>b/s)   | 64(16.3G<br>b/s) |

| I/O Pins          | 500                                      | 520                                        | 1,000                                      | 832                                        | 832              |

| Cost              | 2748<br>(650)                            | 3882(15<br>00)                             | 8094                                       | 7770                                       |                  |

- A cost-driven device selection: FPGA XC7VX690T

- Interface: SFP+ 10Gbps X12 + QSFP 40Gbps X3 .

- Implement real time FPGA based machine learning for clustering, hit point searching, and tracking algorithms

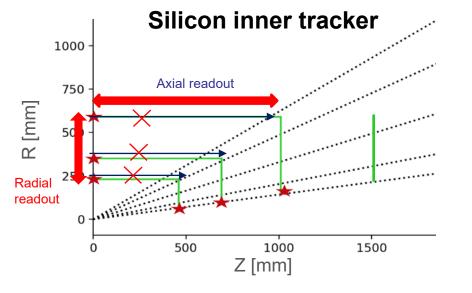

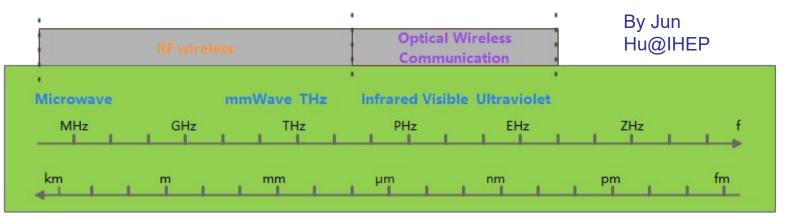

### **Backup scheme based on wireless communication**

- Radial readout with mm-wave

- 12-24 cm transmission distance

- Data rate : < 30Mbps

- Axial readout to endcap

- Only at the outermost layer or dedicated aggregation layer.

- WiFi (2.4GHz, 5GHz)

- large antenna volume, high power consumption, narrow frequency band, and high interference

- Millimeter Wave (24GHz, 45GHz, 60GHz, 77GHz)

- Optical wireless communication (OWC) / Free Space Optical (FSO)

- Wireless communication based readout scheme was proposed to mitigate the cabling problem, as a backup scheme

- Three major solutions were investigated through R&D, two were selected with corresponding schemes

### **Summary**

- Global framework of the electronics system defined for Ref-TDR

- A full ASIC FEE + a common platform BEE proposed for each sub-det, however main challenges should be solved from many aspects

- Recent & long plan

- Prototypes of common platform and common blocks will be demonstrated in ~ 3y

- Stitching VTX, high timing precision OTK ASIC & common SiPM ASIC for ECAL & HCAL & Muon are the major R&D tasks for FEE

> Also expected to be demonstrated in ~3y

• Collaborations, from China & all over the world, are warmly welcome, for both FEE & common projects

## Naming of the common ASICs

ChiTu & Guan Yu

KinWoo in the sun

TaoTie

BaSha carrying a monument

- GBTx-like: ChiTu (赤兔), the most famous horse in Chinese tales, ridden by the Chinese God of War Guan Yu. It is in charge of transportation with ultra fast speed, just as GBTx-like chip is doing.

- VTRx: KinWoo (金乌), the bird who lives in the sun in Chinese tales, an avatar of the sun and in charge of the light, just as the VTRx chip does, to convert electronic signal to/from optical.

- Data aggregation: TaoTie (饕餮), a mythical animal in Chinese tales, who can swallow anything, just as the chip does, to collect all the input data streams.

- DC-DC module: BaSha (霸下), one of the nine sons of the Chinese Loong, who is famous for its strongness and always to bear a monument. Just like the powering system which is the basement and support of all electronics.

### **Choice on global framework**

- We choose FEE-triggerless readout (Backend Trigger) as our baseline global framework, while keep conventional trigger readout as the backup, for the Elec-TDAQ system:

- 1. Keep the max possibility for new physics and future upgrade

- $\succ$  readout all the information w/o pre-assumed trigger condition.

- 2. Speed-up the FEE-ASIC iteration & finalization process

- > w/o the need to consider the undefined trigger algorithm, esp. regarding the potential tight schedule.

- 3. Make it possible for a common platform design for all Sub-Det

- Common BEE Brd, common Trg Brd, common data interface...

- Scalable based on the detector volume

- 4. Sufficient headroom for FEE data transmission based on current MDI background rate

- > 10Gbps per link on FEE (max by  $\times$ 4 links)