師範大學 CENTRAL CHINA NORMAL UNIVERSITY

中國科學院為能物好為統 Institute of High Energy Physics Chinese Academy of Sciences

## A 14bit 100 MS/s Two-Step Split SAR ADC using low-power RA and in-stage redundancy technology

Ping Yang, Zhongwei Chen, Hongda Xu, Xiaoting Li, Zhenhao Meng, Junhui Li, Jingbo Ye

The 2024 International Workshop on the High Energy Circular Electron Positron Collider October 22-27, 2024 Hangzhou Platinum Hanjue Hotel

# Outline

- ✓ 14bit 100 MS/s Two-Step Split SAR ADC

- SAR ADC design

- Residual amplifier design

- Overall analysis

### Summary and Outlook

能物理研究所

Institute of Hi

Chinese Academy of Sciences

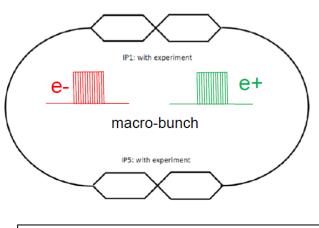

#### Introduction: CEPC and its beam timing

#### Circular e<sup>+</sup>e<sup>-</sup> Higgs (Z) factory

#### Fast readout speed

#### $E_{cm}$ ≈240GeV, luminosity ~2×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, can also run at the Z-pole

Partial Double-ring Scheme

- Crab-waist collision to reduce beam and AC power

- Avoiding pretzel scheme to increase the flexibility and luminosity

- 196ns bunch spacing

- 48 bunches / train

- Duty cycle: 9.4µs/181µs

Reference: CEPC/SppC with ILC (FCC), J. Gao, LCWS 2015, Nov. 2-6, 2015, Whistler, Canada

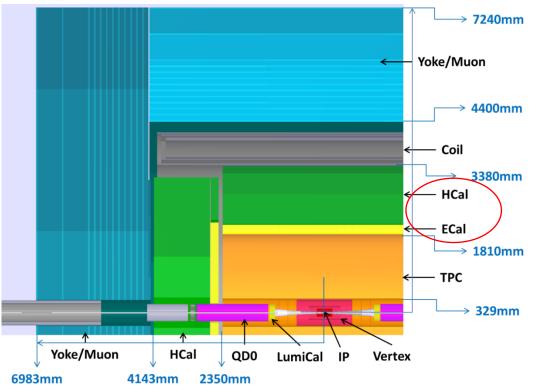

#### Introduction

٠

- Accurate measurement of particle energy requires a Calorimeter system to accurately measure the energy of the jet formed along various directions after particle collision.

- Approximately 72% of jet energy is measured by electromagnetic calorimeter (ECAL) and hadron calorimeter (HCAL).

The Calorimeter requirements:

- The high collision energy high radiation tolerance

- High brightness high energy resolution

- High speed analog-to-digital converter with high radiation tolerance

能物理研究所

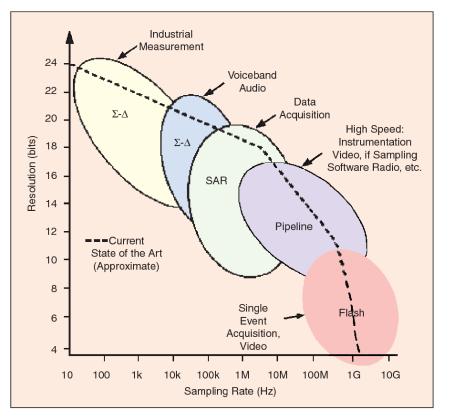

#### **ADC** architectures

ADC architecture, applications, resolution, and sampling rate

Pipelined SAR ADC: Combining the advantages of pipeline ADC and successive approximation ADC, it achieves high speed and accuracy while maintaining low power consumption and small area.

Sigma-Delta ADC: High precision, low power

consumption, but slow speed

- SAR ADC: Low power consumption, slow speed

- Pipeline ADC: High speed, high precision, large

power consumption and area

Flash ADC: high sampling rate, low resolution

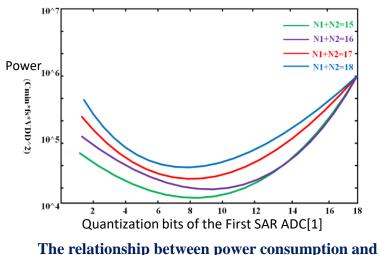

Analyzing the selection of quantization bits for each SAR ADC from the perspectives of linearity and power consumption.

first level quantization bits of Pipelined SAR ADC

#### Two step SAR ADC

The higher the resolution of the first SAR ADC

- The lower requirement for capacitor matching and the smaller the nonlinearity caused.

- The higher the inter stage gain.-> use redundancy

- The nonlinearity of the second SAR ADC will be attenuated more.

- Choose the first stage SAR ADC with an accuracy of 9 bits and the second stage SAR ADC with an accuracy of 7 bits.

[1]Chen K, Duong Q, Alvandpour A. Power analysis for two-stage high resolution pipeline SAR ADC[Z].

Chinese Academy of Sciences

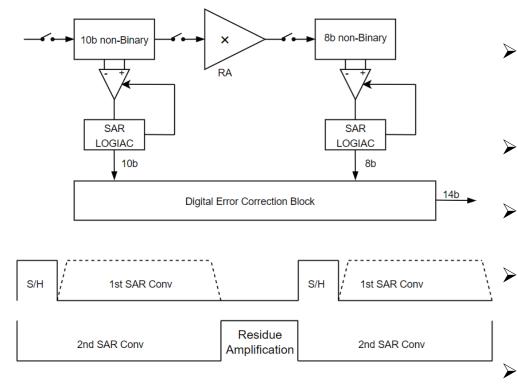

#### **ADC diagram design**

Block diagram of the ADC and its timing diagram

9 bits SAR ADC: Quantify the input signal with 10 bits, including 1-bit internal redundancy.

Institute of High Energy Physics Chinese Academy of Sciences

- RA: Amplify the residual error of the first level quantization.

- 7 bits SAR ADC: Quantify residual signal, including 1-bit internal redundancy.

- Digital Error Correction Block: Delay align the output digital code and perform redundancy calibration.

- Asynchronous switching logic. -> save power consumption.

#### **ADC diagram design**

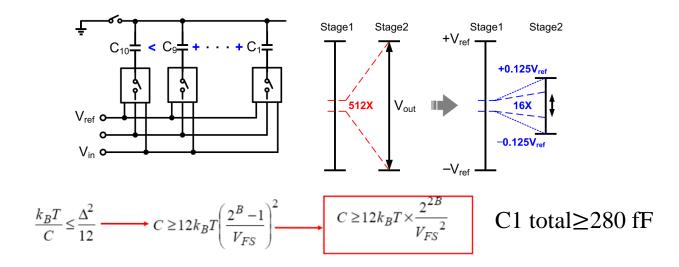

- First stage SAR ADC Ctotal is 511 fF, Vref1 is 1.2V.

- Second stage SAR ADC Ctotal is 63 fF, Vref2 is 150mV.

- Due to inter-stage 2-bit redundancy and the Vref2 is smaller,

The gain of RA is reduced from 512 to 512/4/8=16.

10 bit non binary weight, with 1 bit internal redundancy

| С      | <b>C9</b> | <b>C8</b> | C7 | <b>C6</b> | <b>C5</b> | C4 | <b>C3</b> | <b>C2</b> | <b>C1</b> | <b>C0</b> | Total |

|--------|-----------|-----------|----|-----------|-----------|----|-----------|-----------|-----------|-----------|-------|

| weight | 230       | 130       | 68 | 36        | 20        | 12 | 8         | 4         | 2         | 1         | 511   |

中國科學院為能物招加完備 Institute of High Energy Physics Chinese Academy of Sciences

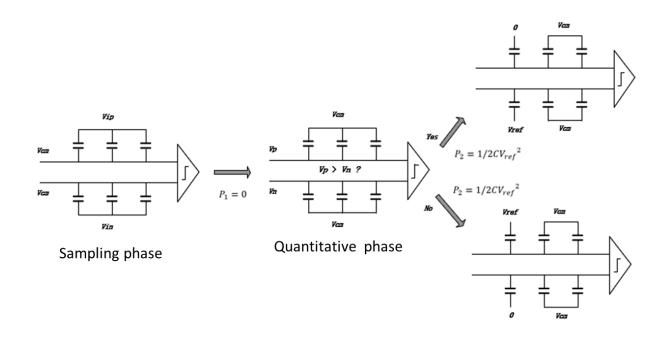

### **SAR ADC Switching strategy**

- Sampling of the lower plate of capacitors.

- Vcm-based switching strategy.

the power consumption is reduced by 87.9%.

> No shift of the common voltage during successive approximation.

中國科學院為能物好納完所 Institute of High Energy Physics Chinese Academy of Sciences

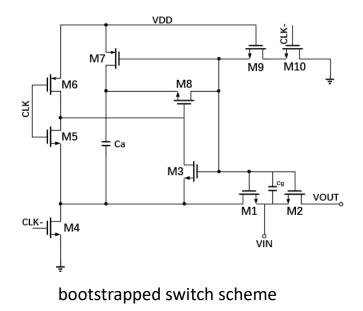

#### bootstrapped switch

- maintain the turn-on resistance and reducing nonlinearity.

- At an input signal frequency of 3M, its SFDR is 99.8dB, SNDR is 99.8dB, SNR is 128.1dB, and ENOB is 16.29bit, all of which are higher than the overall design specifications of the ADC.

中國科學院為能物理研究所 Institute of High Energy Physics Chinese Academy of Sciences

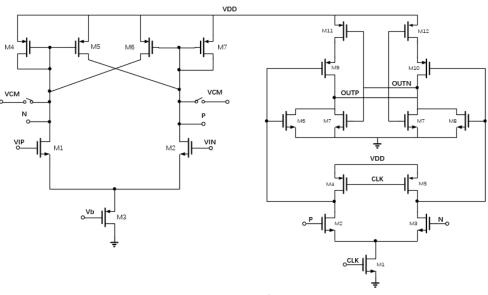

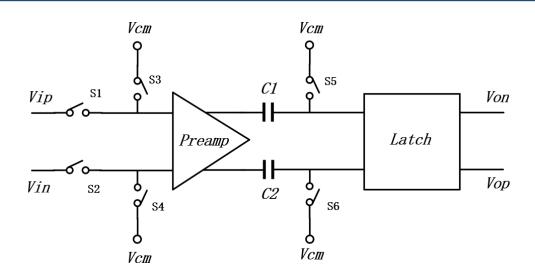

### **Dynamic comparator design**

Block diagram of comparator

- By using a preamplifier and latch structure, the impact of kickback noise on the front-end can be suppressed.

- ➢ Add a reset signal to the output of the preamplifier to improve fault tolerance.

- Positive feedback structure, high resolution, fast speed, and low power consumption.

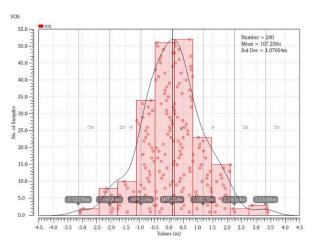

### **Dynamic comparator design**

#### Misalignment self calibration circuit

- Using OOS(Output Offset Storage), the de misalignment technique is divided into a calibration stage and a comparison stage.

- The Monte Carlo simulation results in the left figure show that the equivalent input offset voltage 3 σ is about 3.2mV, which meets the design specifications.

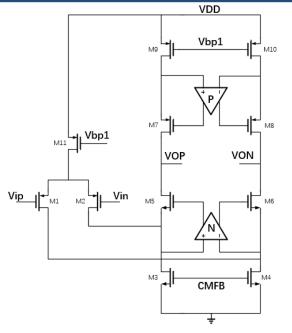

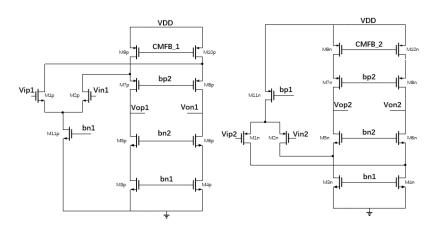

## RA design

Gain enhanced operational amplifier

| corner  | Ao<br>(dB) | GBW<br>(Hz) | PM(°) | POWER<br>(mW) |

|---------|------------|-------------|-------|---------------|

| ss@-40° | 62         | 4.5G        | 62    | 3.8           |

| tt@27°  | 66         | 5.1G        | 63    | 4.5           |

| ff@85°  | 61         | 4.6G        | 77    | 6.2           |

Auxiliary operational amplifiers

- The main operational amplifier adopts a folded cascode structure.

- The auxiliary operational amplifier adopts a folded cascode structure similar to the main operational amplifier.

- Switching capacitor common mode feedback to maintain circuit common mode operating point.

Chinese Academy of Sciences

中國科學院為能物況納完所 Institute of High Energy Physics Chinese Academy of Sciences

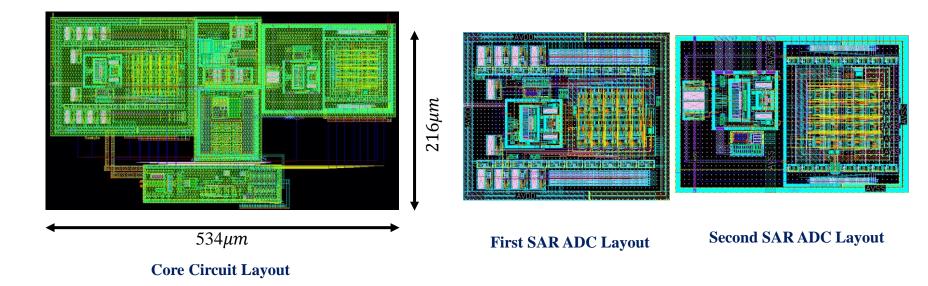

- Separate analog and digital power supplies.

- The capacitor array adopts the same height of the MOM cap and add dummy cap around.

- > The SAR logic connection is the shortest to decrease signal delay.

- > The core circuit area is 534  $\mu m \approx 216 \mu m$ .

-20

-40

-60

-80

-100

-120

0

0.05

0.1

3

5

Power (dB)

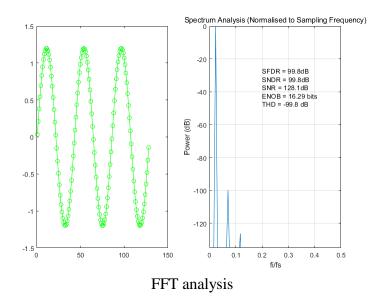

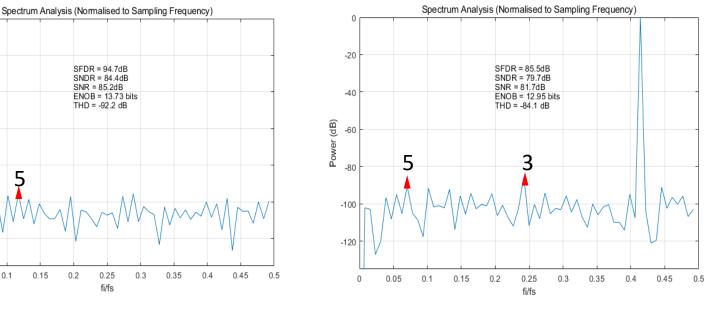

#### Simulation results

FFT analysis results(fin=3M and fs=100M)

FFT analysis results(fin=40M and fs=100M)

- In a typical process corner tt@27°C and an input signal frequency of 3M, the SNR is 85.2dB, SFDR is 94.7dB, and ENOB is 13.73 bit.

- In a typical process corner tt@27°C and an input signal frequency of 40M,  $\geq$ the SNR is 81.7dB, SFDR is 85.5dB, and ENOB is 12.95bit.

然物理研究所

Institute of High Energy Physics Chinese Academy of Sciences

### **Summary and outlook**

#### > Summary

| Supply                  | 1.2V           | SNR  | 76.0dB                       |  |

|-------------------------|----------------|------|------------------------------|--|

| <b>Resolution Ratio</b> | 14 bit         | SFDR | 85.0dB                       |  |

| Input Range             | $0 \sim 2.4 V$ | SNDR | 75.4dB                       |  |

| Sampling Ratio          | 100Msps        | ENOB | 12 <mark>.95 bit@4</mark> 0M |  |

| Power                   | 11.8mW         | Area | 650×380µm²                   |  |

Performance Summary of the Pipelined SAR ADC

#### > Outlook

- Adding on-chip calibration technology to the capacitor array can further reduce the capacitance and to save power.

- Radiation resistance considerations.

- On-chip high speed clock circuit and bias block.

- Multichannel design.

# Thank you for your attention!