# **CEPC TDAQ and Online**

Fei Li, Jingzhou Zhao and Xiaolu Ji On behalf of CEPC TDAQ Group

# Content

- Introduction

- Requirements

- Technology survey and our choices

- Technical challenges

- Previous experience on large facilities

- R&D efforts and results

- Detailed design

- Research team and working plan

- Summary

## Introduction

- This talk is about the design and development of the TDAQ

- This talk relates to the Ref-TDR Ch 12.

- Questions to physics and simulation

- What kind of events need to be saved?

- How to identify these events?

- What level of background?

- Questions to each detectors and electronics

- How many raw data need to readout?

- Whether a hardware trigger is required?

- If hardware trigger, how fast a latency is acceptable?

- What trigger primitive information can be provided

- What level of noise? Signal vs noise occupancy

- What slow control and monitoring requirements?

## Introduction

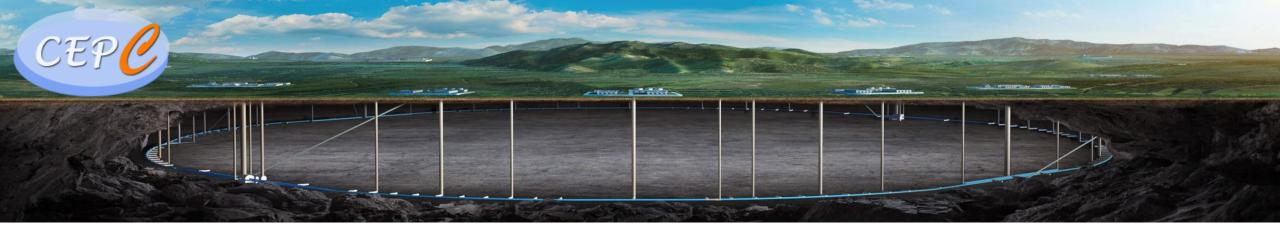

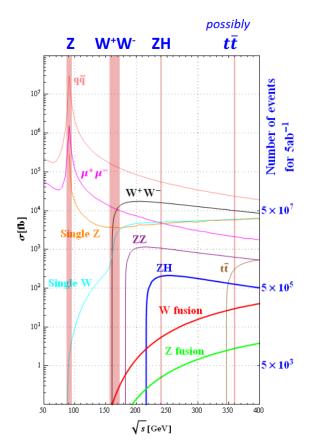

- CEPC beam energy, collision period, luminosity:

- Z(91.2 GeV, 23ns, 115E34), W (160 GeV, 257ns, 16E34) and Higgs (240 GeV, 591ns, 5E34)

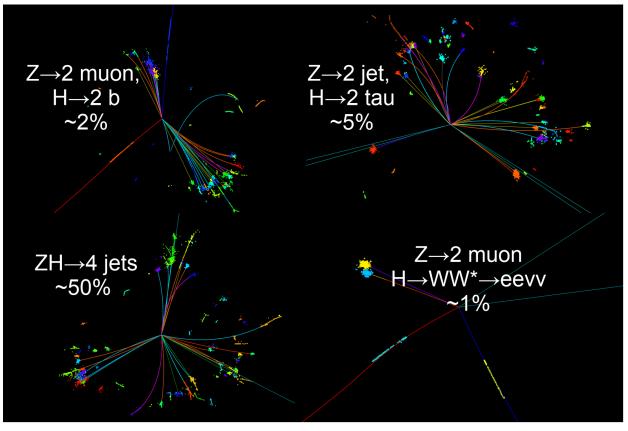

- Requirements for rough selection of the relevant objects (jet, e, muon, tau,v, ...) and combinations.

Ref: CEPC Physics at a glance, Lomonosov Conference 2021, by Manqi Ruan

## **TDR Outline**

- Introduction

- Requirements and design considerations

- Physics requirements for trigger

- Trigger requirements for sub-detectors

- Consideration on readout strategy

- Trigger readout-on-FEE vs. Trigger readout-on-BEE

- Main constraint on FEE triggerless readout vs. CEPC's data rate

- Consideration of the readout-interface for electronics

- Event rate estimation & background rate estimation

- Technology survey and our choices

- Consideration on Backend Trigger strategy (Hardware Trigger vs. Software Trigger)

- Consideration on high level trigger algorithm & resources

- Trigger

- Previous experience on large facilities

- Previous R&Ds

- Common Electronics interface

- Structure of the Trigger for CEPC

- Common Trigger Board

- Resource cost estimation

#### DAQ

- Previous experience on large facilities

- Previous R&Ds

- Platform for DAQ and computing

- Algorithm & architecture

- Resource cost estimation

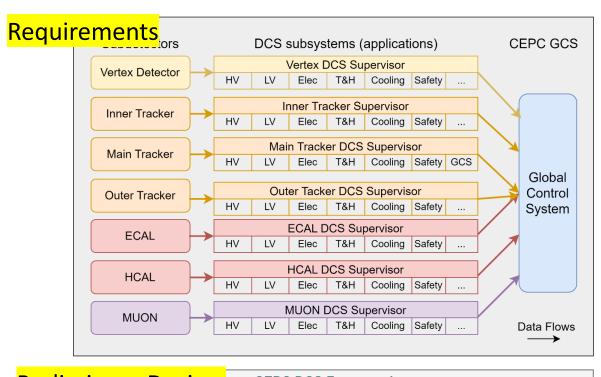

#### Detector Control System

- Requirements on sub-detectors

- On-detector monitoring consideration

- On-detector slow control consideration

- Electronics monitoring and control consideration

#### Experiment Control System

- Requirements

- Network

- Counting room

#### Summary

- Summary on data volume

- Summary on cost

# Requirement

- 7 Sub detectors

- Raw data rate before trigger

- 4.42Tbps, 553GB/s

- @ low Lumi Z

- 22.1Tbps, 2.76TB/s

- @ high Lumi Z

- 5 times increase

- Key issue: FEE readout bandwidth per chip

- Trigger and Online processing

- Good event rate

- <300kHz@Z

- Hardware & software

- Event filter

- Data compression

- Trigger efficiency

- Event purity

|                                | Vertex                                                | Pix<br>(ITKB)                               | Strip (ITKE)                                | TOF (OTK)                                                     | TPC                                   | ECAL                                                          | HCAL                                                        |

|--------------------------------|-------------------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| Channels<br>per chip           | 512*1024<br>Pixelized                                 | 512*128<br>(2cm*2cm@3<br>4um*150um)         | 512                                         | 128                                                           | 128                                   | 8~16                                                          | 8~16                                                        |

| Ref. Signal processing         | XY addr + BX<br>ID                                    | XY addr + timing                            | Hit + TOT +<br>timing                       | ADC+TDC/TOT+TO<br>A                                           | ADC + BX<br>ID                        | TOT + TOA/<br>ADC + TDC                                       | TOT + TOA/<br>ADC + TDC                                     |

| Data<br>Width<br>/hit          | 32bit                                                 | 48bit                                       | 32bit                                       | 40~48bit                                                      | 48bit                                 | 48bit                                                         | 48bit                                                       |

| Data rate<br>/ chip            | 1Gbps/chip<br>@Triggerless<br>@Low LumiZ<br>Innermost | 640Mbps/chip<br>Innermost                   | Avg.<br>1.01MHz/chip<br>Max.<br>100MHz/chip | Avg:<br>26kHz/chip @ z<br>pole<br>Max: 210kHz/chip<br>@z pole | ~70Mbps/<br>modu<br>Inmost            | <4.8Gbps/modul<br>e                                           | <4.8Gbps/modu<br>le                                         |

| Data<br>aggregatio<br>n        | 10~20:1,<br>@1Gbps                                    | 1. 1-2:1<br>@Gbps; 2.<br>10:1@O(10Gb<br>ps) | 1. 10:1<br>@Gbps<br>2. 10:1<br>@O(10Gbps)   | 1. 10:1<br>@1Mbps<br>2. 10:1<br>@O(10Mbps)                    | 1. 279:1<br>FEE-0<br>2. 4:1<br>Module | 1. 4~5:1 side brd<br>2. 7*4 / 14*4<br>back brd @<br>O(10Mbps) | < 10:1<br>(40cm*40cm<br>PCB – 4cm*4cm<br>tile – 16chn ASIC) |

| Detector<br>Channel/<br>module | 2218 chips<br>@long barrel                            | 30,856 chips<br>2204 modules                | 22720 chips<br>1696<br>modules              | 41580 chips<br>1890 modules                                   | 258<br>Module                         | 1.1M chn                                                      | 6.7M chn                                                    |

| Data<br>Volume<br>before Trg   | 2.2Tbps                                               | 2<br>Tbps                                   | 22.4<br>Gbps                                | 1<br>Gbps                                                     | 18Gbps                                | 164.8Gbps                                                     | 14.4Gbps                                                    |

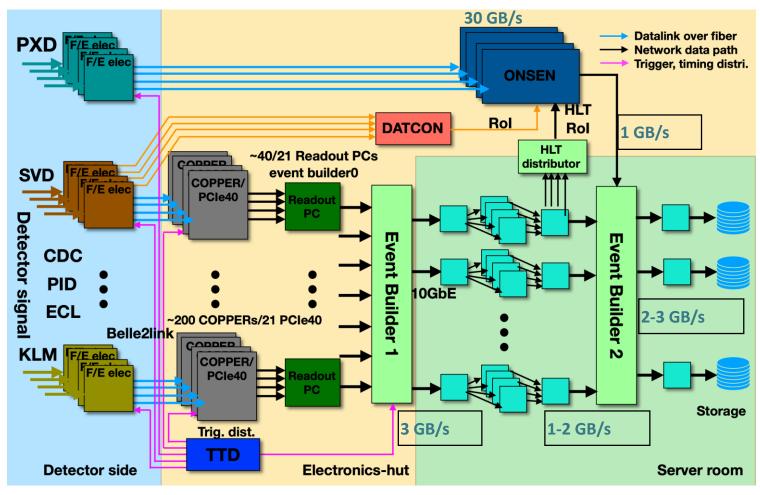

## Belle II TDAQ

- 30 kHz level 1 trigger

- 4.5us L1 latency

- PCIe card readout (except for PXD)

- Buffer PXD data at ONSEN

- Read out by HLT Rol

- Gen. Rol by SVD track

Ref: Belle II DAQ system talk by Qidong Zhou

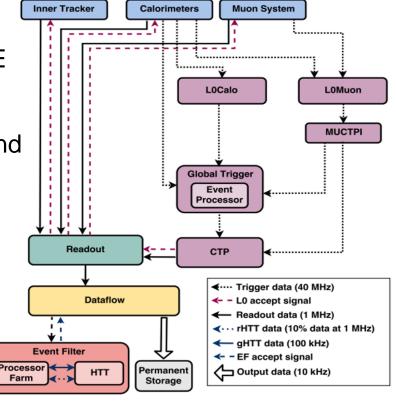

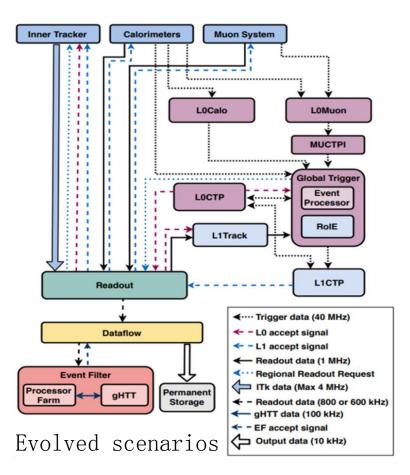

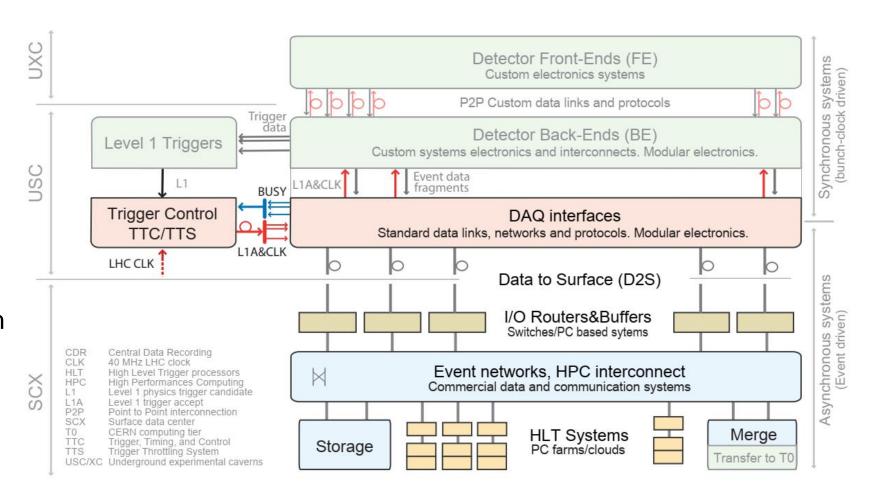

## Atlas TDAQ(Phase II)

- Data rate 4.6 TB/s

- Collect trigger primitive from BEE (Back-End Electronics)

- Fast L0(3us) + L1(10us) + HLT

- HW trigger sent to FEE (Front-End Electronics)

- Common PCI card BEE

- Global HTT(Hardware Track Trigger)

- FPGA based

Baseline

FELIX-155, PCIe gen5x16 482Gb/s, 48 fiber link

Ref: ATLAS Trigger and Data Acquisition Upgrades for the High Luminosity LHC, LeptonPhoton2019

## CMS TDAQ(Phase II)

- Data rate 5.5TB/s

- L1(12.5us) + HLT

- Part FEE trigger less readout

- Common ATCA BEE

- Serenity

- ATCA readout board with Ethernet

- DTH-400Gb/s

- DAQ-800Gb/s

Ref: The Phase-2 Upgrade of the CMS DAQ Interim Technical Design Report

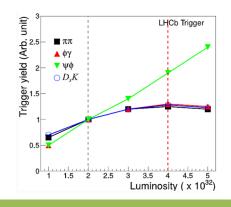

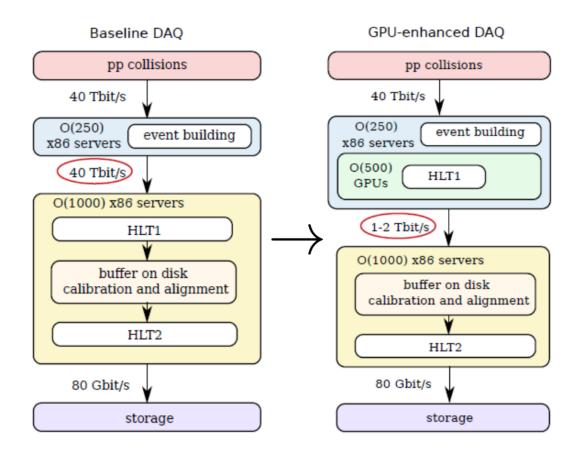

#### LHCb run3

- Run 1–2 trigger: hardware L0 (40→1 MHz)

- Read full event at bunch-crossing rate(4TB/s)

- Cope with higher occupancy.

- Faster/higher precision tracking

- Design characteristic:

- Use disk as a buffer between HLT1 and HLT2.

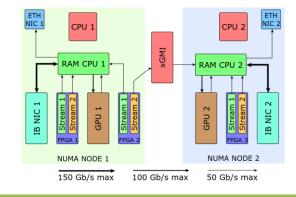

- Compute at HLT1 level using GPUs.

- Event Building using Smart NICs.

Ref: <u>GPU-based software trigger for LHCb experiment</u> talk by <u>Anton Poluektov.</u>

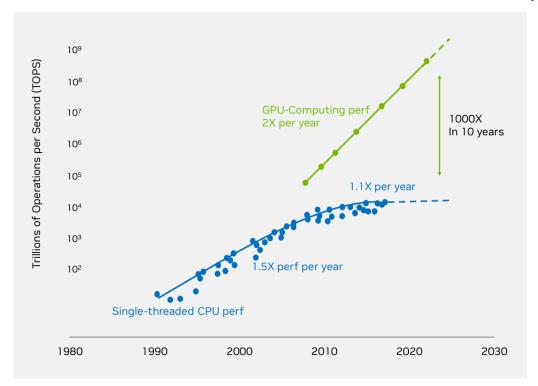

- 800Gbps network is commercially available

- Huang's law: computational power of GPU increase 1000 times in past 10 years

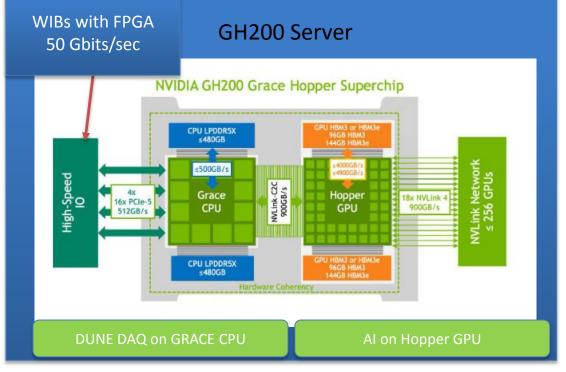

- NVIDIA GH200 server: Arm CPU + GPU, IO > 500GByte/s

Ref: https://www.hangyan.co/charts/3351671202081932642

Ref:DUNE Cold Electronics R&D at ICEBERG, ICHEP-2024, Prague

## **Our choices**

## Trigger solutions

- 1.Full FEE trigger less readout + L1 + HLT

- Baseline option

- Simplified FEE design, extract trigger primitive from BEE

- No high demand for low L1 latency

- 2.Full software trigger

- Preferred option

- Simplified BEE and trigger design

- When L1 compression ratio is low

- 3.Fast L0 + L1 + HLT

- Backup option

- When not enough readout bandwidth for part FEE

- Fast L0 means low trigger latency requirement for part FEE

- Extract L0 trigger primitive from part FEE

# **Main Technical Challenges**

- 1. Full FEE trigger less readout + L1 + HLT

- FPGA algorithm: high data compression ratio

- 2. Full software trigger

- Resource requirement

- High data throughput and online processing efficiency

- 3. Fast L0 + L1 + HLT

- Low L0 latency

- Trigger efficiency

- Synchronize control

- Compression ratio

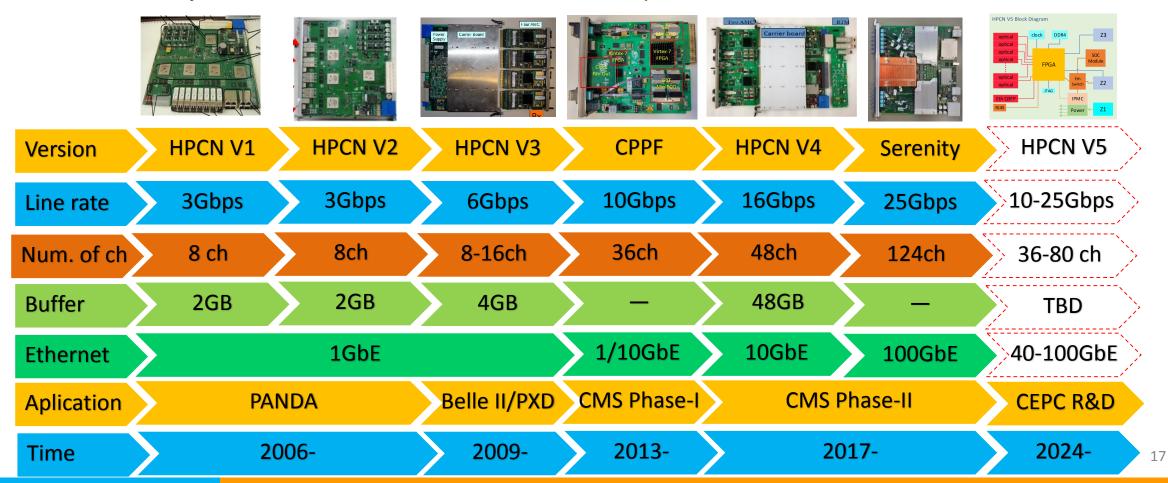

## **Previous experience of TDAQ Hardware**

- Designed BESIII trigger system

- Trigger simulation/hardware design/core trigger firmware development

- Common trigger board design for upgrade

- Share link for data readout, data, fast/slow control and clock transmission

- GSI PANDA TDAQ R&D

- Proposed concept of triggerless readout in TDAQ

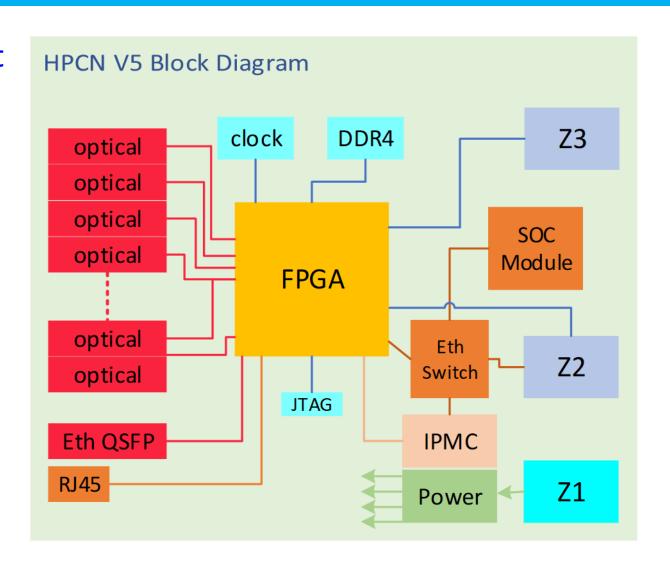

- Designed HPCN board for TDAQ/EMC trigger algorithm development

- Designed Belle2Link and HPCN V3 as ONSEN for Belle II

- Designed CPPF system for CMS Phase-I

- Design MTCA board, Cluster finding and fanout to EMTF/OMTF

- Designing iRPC/RPC Backend/Trigger for CMS Phase-II

- Proposed iRPC Backend system scheme, cluster finding firmware

- ATCA common Backend and trigger board

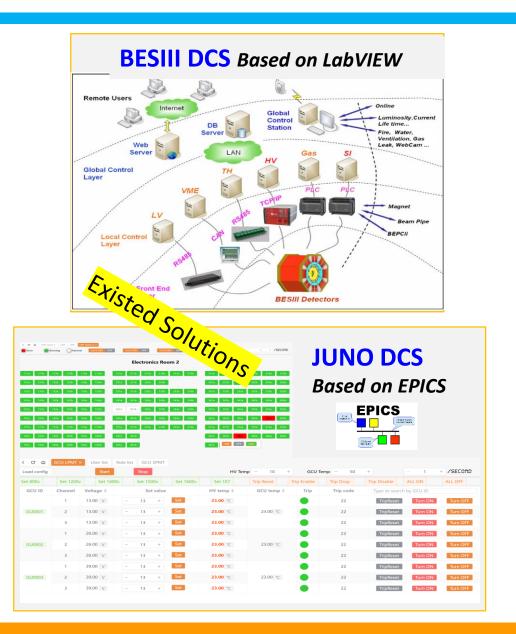

# Previous experience of DAQ&DCS

- BESIII DAQ & DCS

- Running since 2008

- Dayabay experiment DAQ&DCS

- Running from 2011 to 2020

- LHAASO DAQ

- Running since 2019,

- 7k channels, TCP readout

- Full software trigger

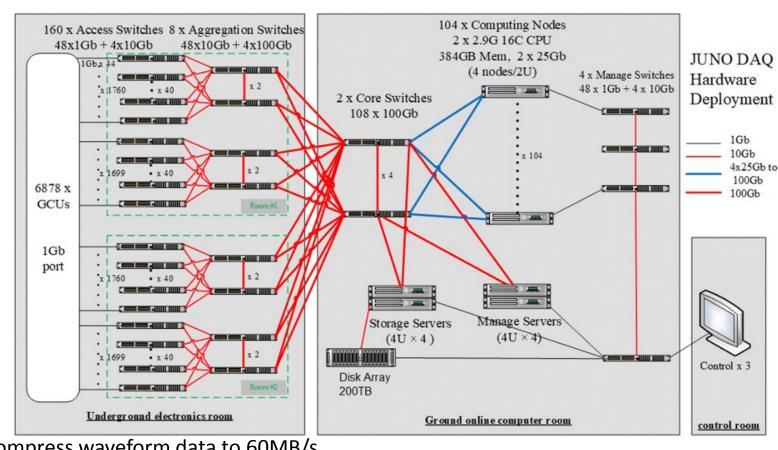

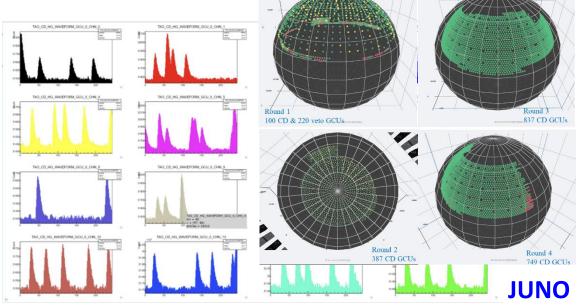

- JUNO DAQ&DCS under developing

- 40GB/s, 45k channels, TCP

- Two type data stream

- HW trigger for waveform

- Software trigger for TQ hits

- Online event classification

- Integrated offline algorithms, compress waveform data to 60MB/s.

Extensive experience in DAQ&DCS development and operation, some in software trigger

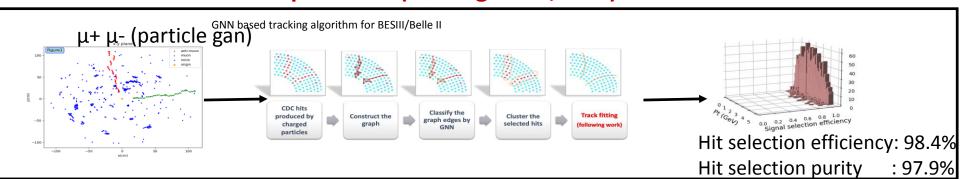

# Previous experience of Advance algorithm

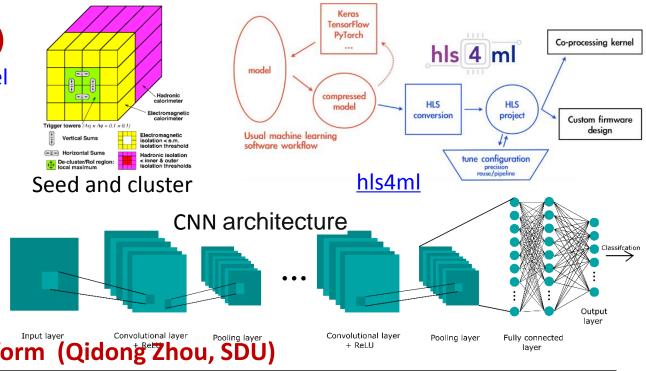

#### Neural network at ATLAS global trigger (Boping Chen)

- Example: tau reconstruction at the hardware trigger level

- Seed with local maximum algorithm

- Cluster around the seed to build region of interest (ROI)

- Train the neural network (NN) with ROI

- To distinguish tau from jet

- Same as image identification: CNN/DNN...

- Use hls4ml to convert NN model to hls project

VCK190 test bench

### HLT Acceleration on FPGA platform (Qidong Zhou, SDU)

## **R&D** efforts and results

- Start to design ATCA TDAQ board for CEPC

- Based on ATCA standard, designed series of ATCA boards

- Already used in PANDA, Belle II and CMS experiment

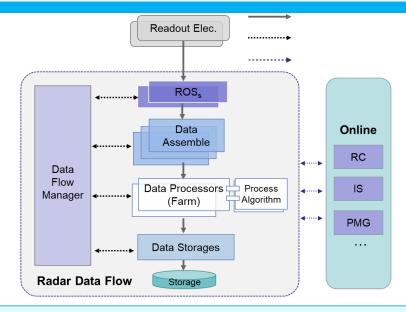

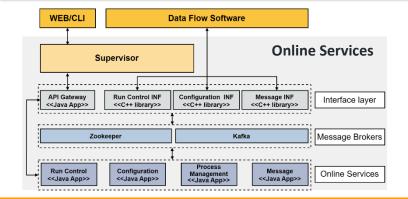

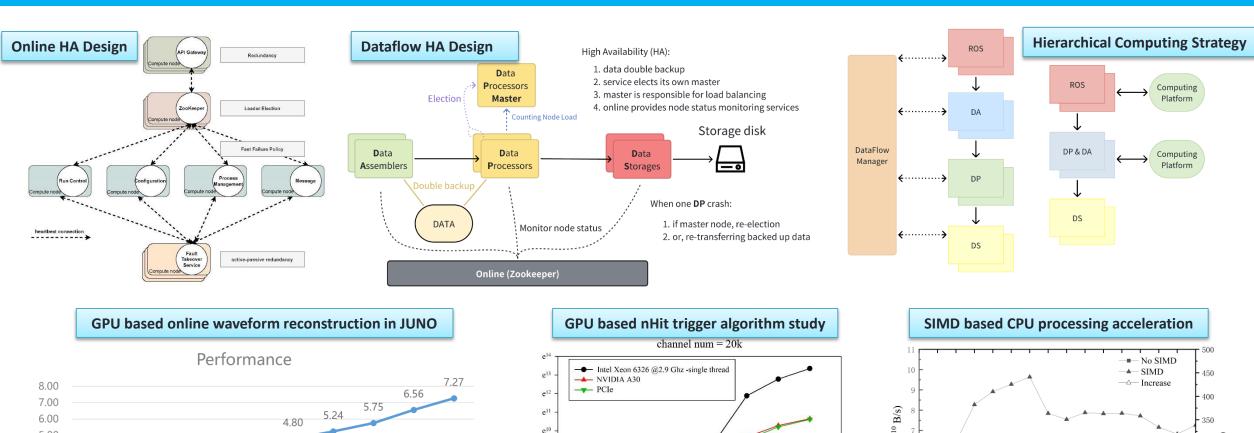

## Streaming Readout Framework - RADAR

heteRogeneous Architecture of Data Acquisition and pRocessing

- **V1:** deployed in LHAASO (3.5 GB/s data rate), software trigger mode

- V2: upgraded for JUNO (40 GB/s data rate), mix trigger mode

- Containerized running

- High availability support

- V3: CEPC-oriented (~ TB/s data rate), under development

- Motivation:

- High-throughput data acquisition and processing

- Current Status:

- Over a decade of work led to significant progress, tested through experiments

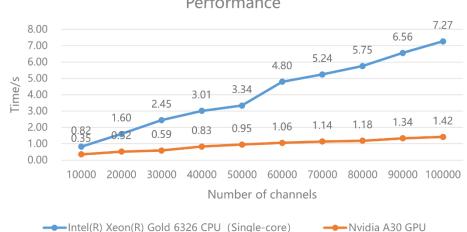

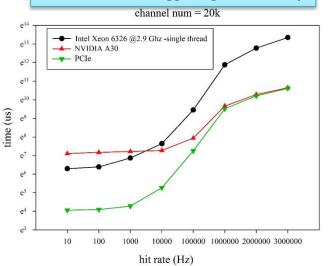

- Recent Focus:

- Heterogeneous online processing platforms with GPU

- Real-time data processing acceleration solutions

- Expansion:

- Application across various domains (DAQ, triggering, control, etc.)

- Integration of Al technologies (ML, NLP, expert systems, etc.)

- General-purpose distributed framework

- Lightweight structure

- Plug-in modules design

- Microservices architecture

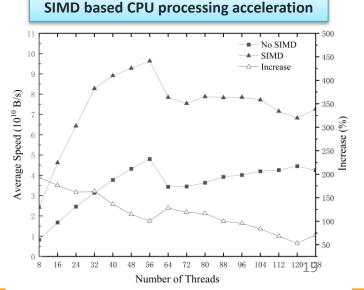

## **R&D** efforts and results

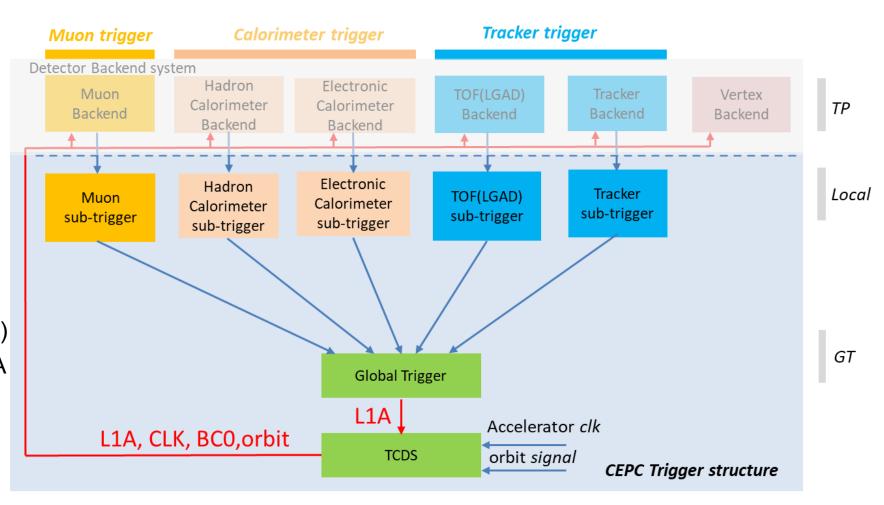

# Preliminary design of hardware trigger

### HW Trigger structure

- Baseline option

- HW trigger sent to BEE

- L1 at back-end

- Backend of each detector generate Trigger

Primitive(TP)

- Sub trigger of generate local detector trigger information(energy, track...)

- Global trigger generate L1A according to physical requirement.

- TCDS distribute clock and fast control signals to BEE.

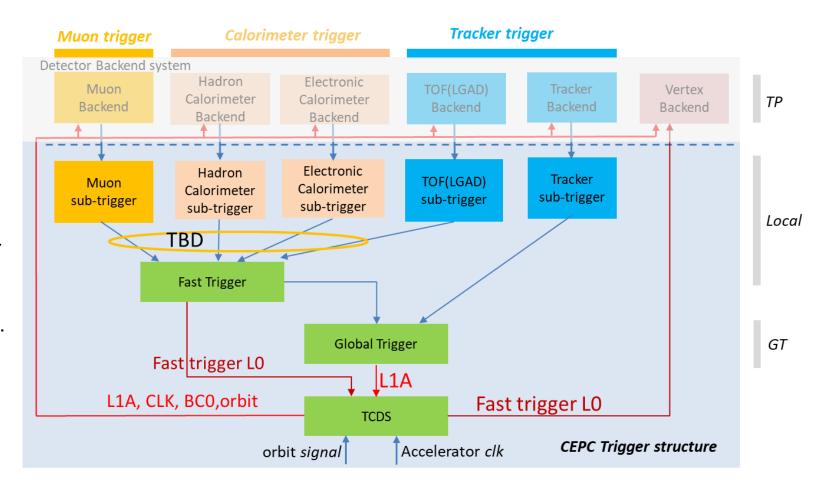

# Preliminary design of hardware trigger

## Trigger structure

- Backup option

- HW trigger sent to FEE

- Fast L0 + L1

- Backend of each detector generate Trigger Primitive(TP)

- Sub trigger of generate local detector trigger information(energy, track...)

- Fast trigger generate local low latency LOA for Vertex to reduce data. Which detectors join this trigger need to be discussed.

- Global trigger generate L1A according to physical requirement.

- TCDS distribute clock and fast control signals to BEE.

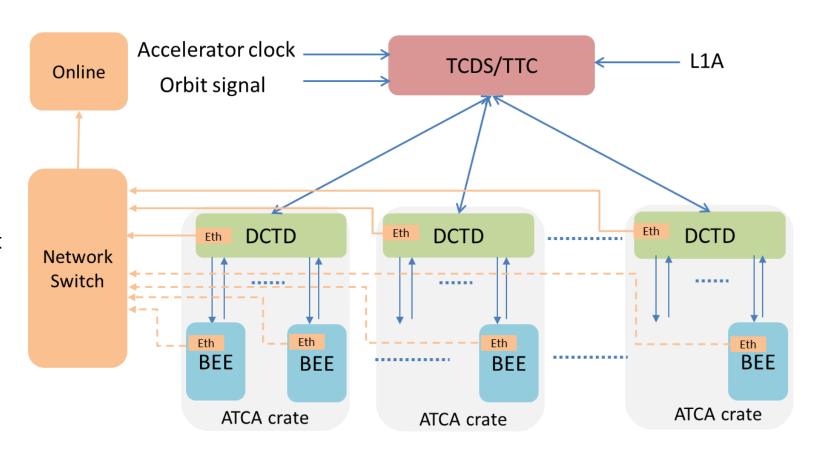

# Preliminary design of TCDS/TTC and readout

## TCDS/TTC

- Clock, BC0, Trigger, orbit start signal distribution

- Full, ERR signal feed back to TCDS/TTC and mask or stop L1A

### DAQ readout

- Option1: BEE Data collected and packaged by DCTD board, and sent to Online via network switch.

- Option2: BEE Data sent to Online via network switch.

- TCDS-Tigger Clock Distribution System

- TTC- Trigger, Timing and Control

- DCTD-Data Concentrator and Timing Distribution

- BEE-Backend board Electronic

## Preliminary design of the common Trigger Board

## Common Trigger board function list

- ATCA standard

- Virtex-7 FPGA

- Optical channel: 10-25 Gbps/ch

- Channel number:36-80 channels

- Optical Ethernet port: 40-100GbE

- DDR4 for mass data buffering

- SoC module for board management

- IPMC module for Power management

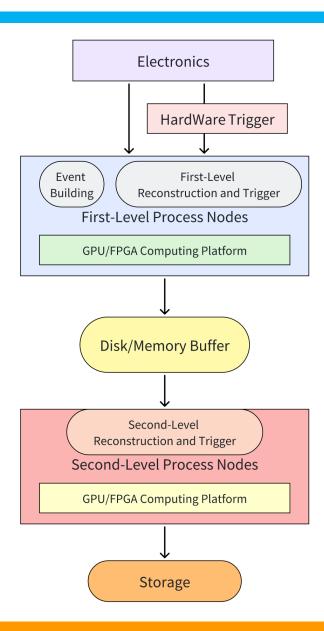

# Preliminary design of DAQ

- Same with or without hardware trigger

- Readout interface and protocol

- Ethernet X\*100Gbps/ TCP or RDMA

- PCIe optional

- GPU acceleration at HLT1 & HLT2

- FPGA optional

- Memory vs disk buffer for HLT2

- Better IO performance but smaller volume size

- RADAR software framework

- Heterogeneous computing cluster

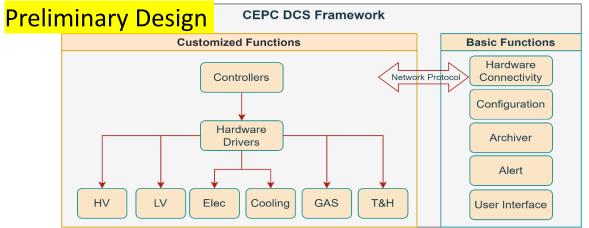

# **Preliminary design of DCS**

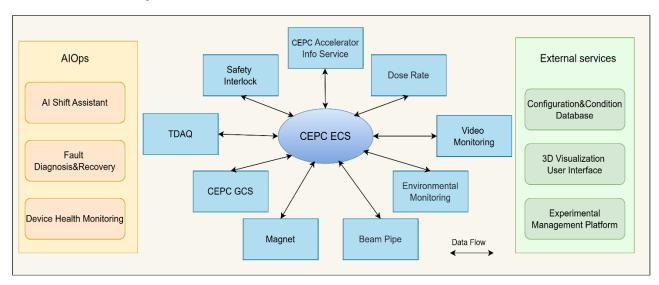

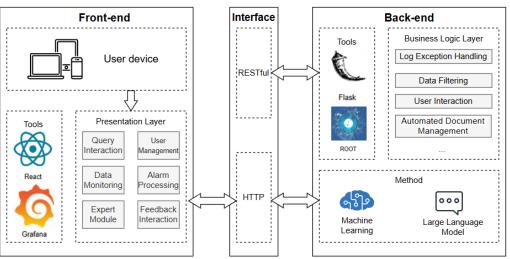

# **Preliminary design of ECS**

## Main components of the ECS

- Existed Solutions:

- 3D Visualization Monitoring

- Al shift assistant research based on LLM+RAG (TAOChat)

- Fault root analysis method based on directed acyclic graph

- A ROOT-based Online Data Visualization System (ROBOT)

- Unified control and monitoring for TDAQ, DCS and others

- Al operation and maintenance

## **Research Team**

- 15 staff of IHEP TDAQ group

- Kejun Zhu (team director)

- DAQ (4 of 6)

- Hongyu Zhang (readout)

- Fei Li (DAQ, team manager)

- Xiaolu Ji (online processing)

- Minhao Gu (software architecture)

- Trigger (4 of 5)

- Zhenan Liu (trigger director)

- Jingzhou Zhao (hardware trigger)

- Boping Chen (simulation/algorithm)

- Sheng Dong (firmware/DCS)

- DCS/ECS (1 of 4)

- Si Ma

| Born in | number |

|---------|--------|

| 1960s   | 3      |

| 1970s   | 4      |

| 1980s   | 4      |

| 1990s   | 4      |

|         |        |

#### Collaborators

Qidong Zhou (HLT, SDU)

| Born in | number |

|---------|--------|

| 1980s   | 2      |

| 1990s   | 1      |

- Yi Liu (HLT, ZZU)

- Junhao Yin(HLT, NKU)

- IHEP Students(20 totally)

- 2 Phd and 4 master

- New member need

- 2 staff next year

- 2 postdoc

- Looking for more collaborators

# **Working plan**

#### TDR related

- Basic Trigger simulation and algorithm study

- Event rate and basic algorithm scheme for each detector

- Hardware trigger and interface design

- Finalize TDAQ design scheme

#### R&D

- Trigger simulation and algorithm

- Hardware trigger, fast control and clock distribution

- ROCE/RDMA readout protocol and smart NIC

- TB/s high throughput software framework(RADAR)

- FPGA/GPU acceleration and heterogeneous computing

- Memory based distributed buffer

- ML/Al algorithm application

- Trigger/data compression/ AI operation and maintenance

# Summary

- Completed preliminary design of TDAQ and online

- Mix hardware and software trigger could be adapted solution currently

- Full software trigger will be best one if no IO and computational power constraints

- No show-stopper found for hardware and software trigger scheme

- But fast L0 trigger algorithm and handling TB/s data at manageable hardware scale remain challenges.

- Much R&D effort still needed from design to implementation

# Thank you for your attention!