### Summary of the recent progress

- Two weeks discussions focused on the cabling & crates, for the electronics rooms requirements

- Thursday meeting indico: <a href="https://indico.ihep.ac.cn/event/23561/">https://indico.ihep.ac.cn/event/23561/</a>, 23622

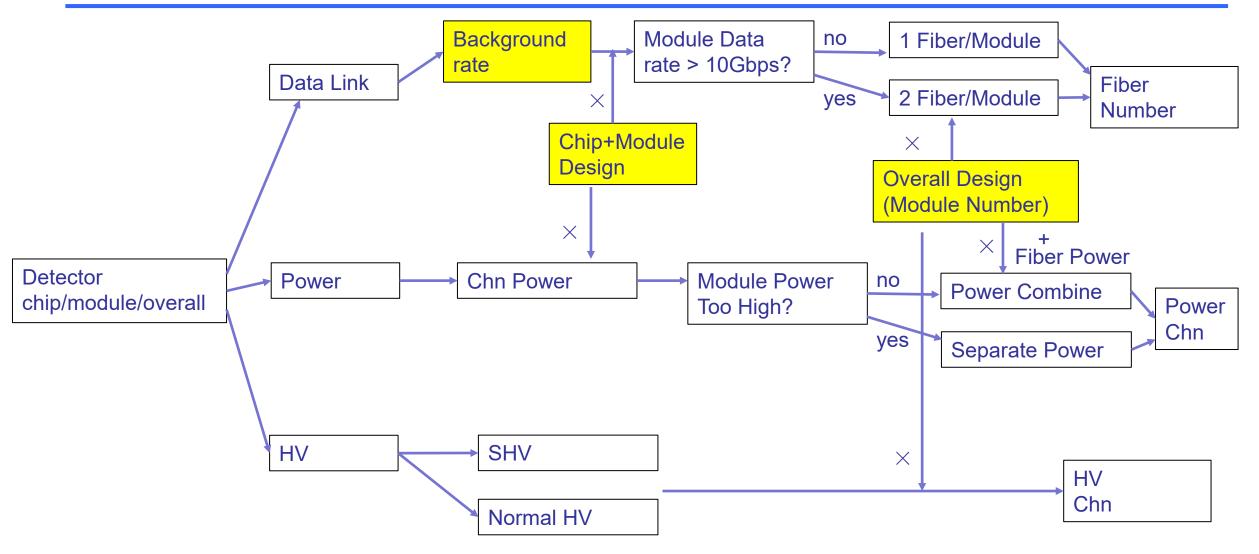

- Collected Background rate, detailed design of the detector, in co-consideration of the FEE scheme, three major items were reviewed: data link, power, HV

- With detailed design of detectors, the rough number of BEE/Power/HV boards, crates, were given

### Consideration according to the detector design

### An example of sub-detector consideration (ECAL)

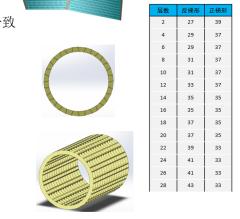

#### ECAL电缆估算

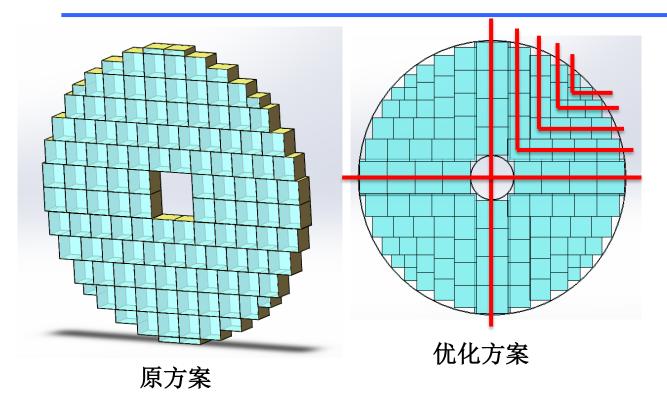

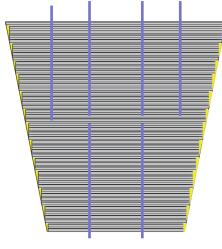

- ECAL桶部,正反梯形排布

- 模块数量: Phi: 32, Z: 15, 共480个模块

- - 1层到28层, 奇数层每层36根, 偶数层晶体数目不一致

- 正梯形晶体数量1000, 反梯形晶体数量992

- 电缆估算: 1根/模块

- AWG15(线径1.45mm,电流:6.5A/7.4A) AWG18(线径1.08mm,电流:3.2A/3.7A)

- 模块功耗估计: 1000\*2\*20mW = 40W

- 光纤估算: 1根/模块

- 模块数据量估算: 待定

- - 高压,低压(正负?),光纤

- 电缆双向走向, 每端240根(平均方案)

- 电缆双向走向, 一端224根, 一端256根

- 未确定电缆: 刻度方案

- The overall detector design: ~480 Module (Dual-trapezium scheme), ~1000 bar/module

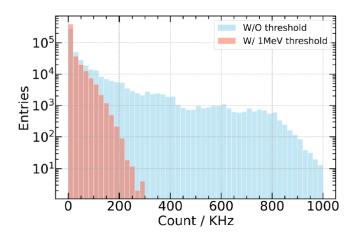

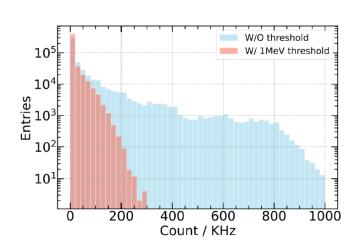

- Current bkgrd estimation: avg. event rate 100kHz / crystal bar w/ threshold; Data width 48bit/event (current ASIC scheme)

- @Dual readout each crystal bar, total data rate:

1000\*100kHz\*48bit\*2ends=9.6Gbps, not possible for 1 fiber for each module, at least 2 fibers for each module

- For max. bkgrd rate@300kHz@Higgs, also needs enough room

- Still waiting for the final bkgrd rate, heard to be even higher (@Z)

### An example of sub-detector consideration (ECAL)

#### Data Link:

- Fibers: 480\*2=960, -> 60 BEE Brds, 6 crates

#### Power:

- ASIC: 15mW/ch, each module 1000\*2\*15mW=30W

- **➤** Within the capability of DC-DC power module

- Data Link + optical Power: 1W each

- Total Power: 31W/0.85\*480=17.5kW

- > Efficiency of the DC-DC: 85%

- Power chn 100W/chn, each module per power cable: 480 power chn -> power crates 10

#### • HV:

- Sch 1: one HV chn for each module, (limitedly) compensated in ASIC

- − HV channels = module number = 480, -> 2 HV crates

- Alt sch2: HV chn for each SiPM? Too many channels & too large control data volume (X)

- Alt sch3: HV chn for sub-region of a module, to compensate the temperature gradient

- ➤ Maybe much optimized than sch1, but rely on the detector simulation

### 小结

- 探测器平均本底、峰值本底均重要

- 峰值本底估算光纤容限

- 平均本底估算总体数据率作为电子学-触发接口

- 探测器详细模块设计是必要的,包括模块上的芯片排布,和探测器整体的模块 排布

- 模块上芯片排布用来评估电子学读出方案(数据汇总、功耗相关),以及模块数据率

- 探测器整体排布评估光纤数以及排布方式

- 按目前考虑,探测器高压基本均要求按模块独立调节

- 与探测器模块排布有关

- 大部分探测器模块维持"一光一电",即电源通道不做汇总,对应到模块级

- 经讨论,探测器端空间有限,电源汇总需要安装额外PCB,机械难以设计

- 少数空间富裕(主要是端盖)且功耗较低的探测器,电源考虑汇总方案(需设计探测器端分配方案)

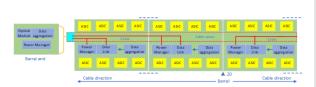

### 电子学间需求计算——边界条件(数据)

- Optical Link

- 特殊限制for VTX: MTX接口的通道数,按照1Rx + 4Tx考虑

- 数据机箱、机柜约束条件

- 后端板for 16道光纤, & @10Gbps/Link, 受接口数&数据率双重约束

- \_ 数据机箱

- > 主要受一个机箱的可插板数量限制,数据率一般不成问题

- > 即需要确定后端电子学机箱标准

- \_ 数据机柜

- > 限制可承受机箱的数量

- "1块后端板接收16通道前端电子学数据,尺寸按mTCA插件设计,安装在mTCA机箱里,以目前买的mTCA机箱计算,考虑到散热(和多要地方),1个mTCA机箱高度按9U,宽度14个单宽插件,机箱控制插件占2位,TTC插件占1位,1位预留,可以按每个机箱插10块后端板计算。1个机柜42U,考虑到散热以及可能DAQ交换机会就近安装到对应机柜,也会占用部分高度,最多安装3个9U机箱,这样一个机柜会安装30个后端板,接出480根光纤。"-by 胡俊

- 机箱@mTCA@9U,每个机箱10块后端板

- 机柜@42U,每个机柜3个机箱,30后端板,480Links

### 电子学间需求计算——边界条件(数据)

- 电源机箱、机柜约束条件

- 电源机箱

- > 主要受机箱功率限制

- ▶探测器模块数——电源电缆数可通过分流来解决

- 电源机柜

- > 限制可承受机箱的数量

- · "电源部分: 2级供电, 380AC-110DC: 一个机箱10路总共60kw~70kw, 6U。 一个机柜可安装5个这样的一级机箱,此机柜在远离辐射区的地方。110DC-48DC 一个机箱48通道(无备份),100W/通道,3U。一个机柜可安装10个这样的二级机箱,此机柜靠近探测器,总共可接出480路电路,每路100W。" by 胡俊

- 高压机箱: 5机箱/机柜, @60~70kW

- 中压机箱: 10机箱/机柜, 48chn/机箱, 100W/ch

### 电子学间需求计算——边界条件(数据)

- 探测器高压机箱约束条件 (by 樊磊)

- 一般高压功率均不高,主要按通道数约束

- (参考HGTD已提供高压机箱)一个机箱8U,14×16=224通道,上下预留2U散热空间

- 一个42U机柜可含约4个高压机箱

- ▶ 如需SHV连接器(如TPC),则机箱高度为10~12U,则一个机柜含3个高压机箱

### 电子学间需求计算——Status

- 前端ASIC数据率由于加速器功率30MW→50MW,本底数据需要进一步更新, 更待MDI统一计算

- 目前暂按之前的估算来考虑

- VTX受此影响最大,按照每芯片2Gbps计算

- ECAL目前受到的挑战也很大

- 探测器模块组织情况

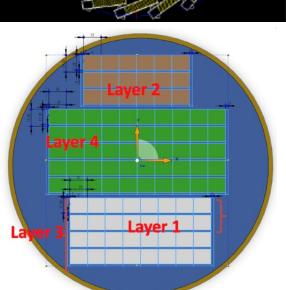

- VTX更新为内四层Stitching, 外层ladder的方式(暂定组织)

- 其他按照目前掌握的探测器设计情况来考虑(大部分探测器模块数量仍未最后确定)

- 探测器功耗情况

- 在探测器级别,也和探测器模块组织方式密切相关

- 在芯片级别,大部分功耗均已明确

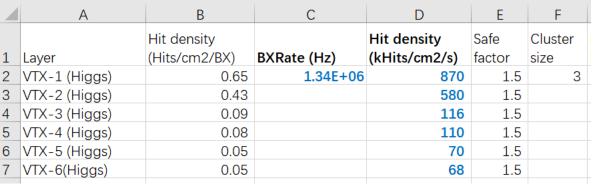

#### **VTX-Data Link**

- · 安全因子1.5,加速器50MW,按内层2Gbps/chip为数据率基准,按 Higgs mode本底比例计算各层,各层芯片数量内四层以RSU为单位, 外两层(double sided)以芯片为单位

- 共需光纤连接88个,等效后端板6块,机箱1个,

| Lay<br>er | Comment          | Data<br>Rate/chip | Chips/<br>Row | Data rate/row | Rows   | Links@10Gbps   |

|-----------|------------------|-------------------|---------------|---------------|--------|----------------|

| 1         | Stitching        | 2Gbps             | 8             | 16G           | 2*2=4  | 2*4=8(两根光纤ch)  |

| 2         | Stitching        | 1.3Gbps           | 12            | 15.6G         | 3*2=6  | 2*6=12(两根光纤ch) |

| 3         | Stitching        | 0.27Gbps          | 16            | 4.3G          | 4*2=8  | 1*8=8          |

| 4         | Stitching        | 0.25Gbps          | 20            | 5G            | 5*2=10 | 1*10=10        |

| 5         | Ladder-<br>side0 | 0.16Gbps          | 29            | 4.64G         | 25     | 1*25=25        |

| 6         | Ladder-<br>side1 | 0.16Gbps          | 29            | 4.64G         | 25     | 1*25=25        |

#### **VTX-Power Link**

| Laye<br>r | Commen t  | Power/chi<br>p | Chips/<br>Row | Power<br>/row | Rows   | Chip Power of Layers | Power consumed of BaSha (18%) | Total Power/Layer<br>(芯片+数据) *1.18 |

|-----------|-----------|----------------|---------------|---------------|--------|----------------------|-------------------------------|------------------------------------|

| 1         | Stitching | 200mW          | 8             | 1.6W          | 2*2=4  | 6.4W                 | 1.152W                        | (6.4+4) *1.18=12.2                 |

| 2         | Stitching | 200mW          | 12            | 2.4W          | 3*2=6  | 14.4W                | 2.592W                        | (14.4+6) *1.18=24                  |

| 3         | Stitching | 200mW          | 16            | 3.2W          | 4*2=8  | 25.6W                | 4.608W                        | (25.6+8) *1.18=39.5                |

| 4         | Stitching | 200mW          | 20            | 4W            | 5*2=10 | 40W                  | 6.8W                          | (40+10) *1.18=58.8                 |

| 5         | Ladder-   | 200mW          | 29            | 5.8W          | 25     | 145W                 |                               |                                    |

|           | side0     |                |               |               |        |                      | 26.1W                         | (145+25) *1.18=200                 |

| 6         | Ladder-   | 200mW          | 29            | 5.8W          | 25     | 145W                 |                               |                                    |

|           | side1     |                |               |               |        |                      | 26.1W                         | (145+25) *1.18=200                 |

- 探测器前提假设一致,每芯片功耗估算为200mW(40mW/cm2 \* 2.6cm\*1.6cm)

- @40MHz (BX=25ns), 如按15ns, 功耗将成倍增加

- 主要功耗贡献:模拟静态功耗+数据接口,不随本底数据率变化,因此不考虑按各层本底的功耗 scaling down

- 设BaSha DC-DC效率为85%,则功耗开销为18%(1÷85%=118%)

- 每行固定功耗: 数据接口1W+数据接口开销0.18W=1.18W

- 总功耗449.8W(可按 $1\sim4$ 层各一个电源通道, $5\sim6$ 每层各两个电源通道@100W/ch考虑,共8个电源通道=1个低压机箱)

#### VTX-HV

- 探测器无实际高压需求

- · 但有一定可能性用到负电压(<-10V)

- 考虑全部探测器仅此处可能用到负电压,专门研发电源模块成本太高,故将此负电压按"高压处理"

- · Stitching部分每片一个高压通道共8个,普通ladder部分每个ladder一个高压通道共50个,共计1个高压机箱可完全覆盖

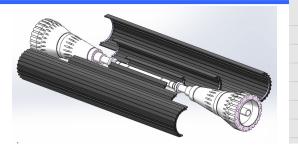

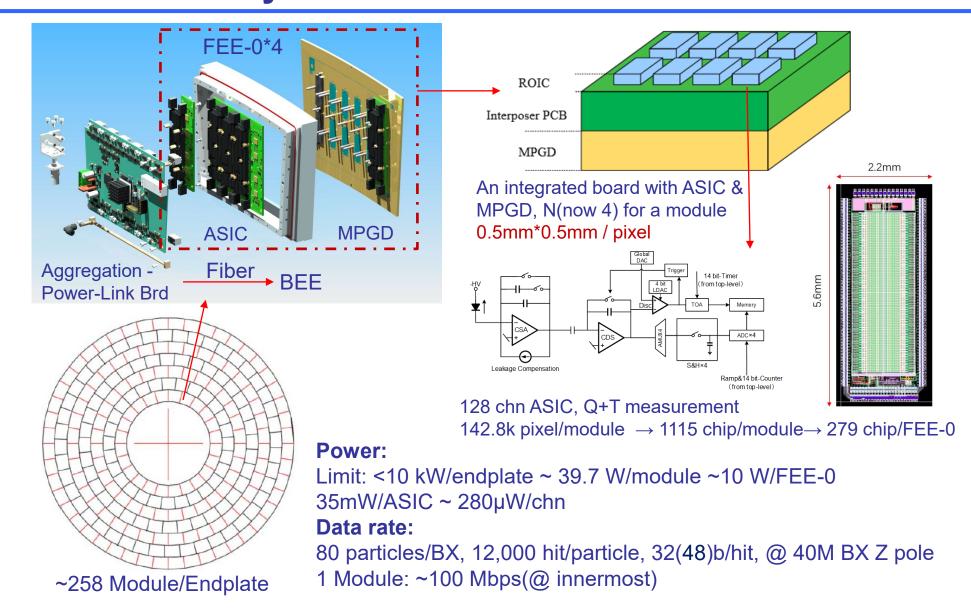

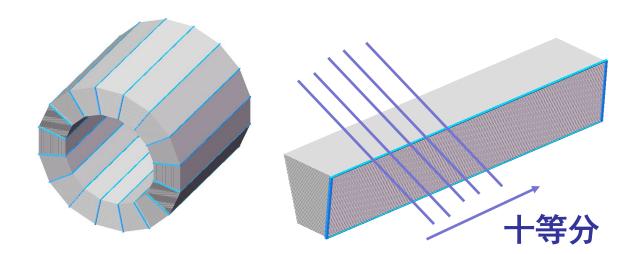

### **Preliminary readout scheme of Pixel TPC**

### TPC—Data Link

- 模块: 258模块\*2端盖=516模块

- · 每模块数据率30Mbps~100Mbps, 平均70Mbps, 远低于光模块传输能力

- 方案一

- 按照每个模块一根光纤,系统可靠性最高,略微增加了光纤和后端电子学数量(成本)

- 方案二

- 由于数据率较低,在TPC端盖上还可做数据汇总,进一步减少光纤和后端板数量(成本)

- 可按16路汇总考虑

| 方案 | 模块数       | Data Rate/module | Module/Fiber | Total Fiber | Total BEE   | <b>Total Crate</b> |

|----|-----------|------------------|--------------|-------------|-------------|--------------------|

| 1  | 258*2=516 | 100Mbps          | 1            | 516         | 258/16*2=34 | 4                  |

| 2  | 258*2=516 | 100Mbps          | 16           | 258/16*2=34 | 3           | 1                  |

• 暂按方案一考虑后端组织,在有限成本增加下获得最高系统可靠性

#### TPC—Power

- · 按照TPC每个端盖10kW功耗

- 258个模块每个功耗38W,加上数据接口开销1.18W,小计不高于40W

- 每路电源机箱通道可提供100W

- · 每侧端盖共需电源通道258个,共516通道,即电源机箱12个(或每侧6个独立考虑)

- 高压通道数同为516通道,每侧两个高压机箱(224通道),共4个

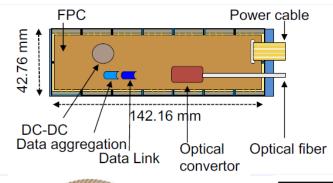

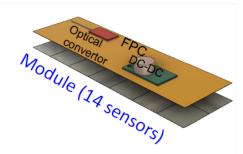

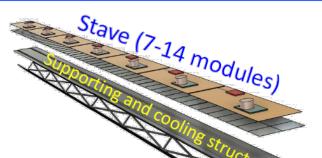

## ITK——探测器排布

· 光纤及DC-DC独立集成 在module上

| Barrels | Modules/Stave | Staves | Modules | Sensors | Sensor area         |

|---------|---------------|--------|---------|---------|---------------------|

| ITKB1   | 7             | 40     | 280     | 3920    | 1.6 m <sup>2</sup>  |

| ITKB2   | 10            | 58     | 580     | 8120    | 3.2 m <sup>2</sup>  |

| ITKB3   | 14            | 96     | 1344    | 18816   | 7.5 m <sup>2</sup>  |

| Total   |               | 194    | 2204    | 30856   | 12.3 m <sup>2</sup> |

| Endcap                  | 1 (per Sector) | 2        | 3         | 4         | Total   |

|-------------------------|----------------|----------|-----------|-----------|---------|

| Ladder Type             | 6              | 8        | 15        | 12        | 18      |

| Ladder Number           | 7              | 10       | 18        | 15        | 1600    |

| Chip Number             | 48             | 98       | 260       | 236       | 20544   |

| Active Area (mm^2)      | 20181.03       | 42796.32 | 116080.28 | 106081.77 | 9.12e6  |

| Module Area (mm^2)      | 23184          | 47334    | 125580    | 113988    | 9.92e6  |

| Power Consumption (W)   | 46.368         | 94.668   | 251.16    | 227.98    | 1.98e4  |

| Avg. Hit Rate (Hz/mm^2) | 3.9e2          | 1.6e3    | 8.9e2     | 2.4e2     | -       |

| Data Rate (Hz)          | 2.89e8         | 2.42e9   | 3.58e9    | 8.75e8    | 2.29e11 |

### ITK——Data Link (桶部)

|                               | HVCMOS Pixels (Barrel)                                               | CMOS Strips (Endcap)                                                 |

|-------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| Pixel Size (Strip Pitch Size) | 34 × 150 μm²                                                         | 20 μm                                                                |

| Chip size                     | $2 \times 2 \text{ cm}^2$ (active area: 1.92x1.74 cm²)               | 2.1×2.3 cm <sup>2</sup><br>(active area: 2.05x2.05 cm <sup>2</sup> ) |

| Array size (Strip number)     | 512 rows × 128 columns                                               | 1,024                                                                |

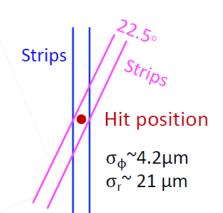

| Spatial resolution            | $\sigma_{\phi}$ ~8 μm (bending), $\sigma_{z}$ ~40 μm                 | $\sigma_{\phi}$ ~4.2 μm (bending), $\sigma_{r}$ ~21 μm               |

| Timing resolution             | ~3-5 ns                                                              | ~3-5 ns                                                              |

| Data size per hit (1 readout) | 42 bit (14b BXID, 7b+9b address,<br>6b TOT, 5b fine TDC, 1 polarity) | 32 bits (10b BXID, 10b address,<br>6b TOT, other 6 bits)             |

| Data rate per chip            | Maximum ~0.1 Gbps*<br>(pair production)                              | Maximum ~0.2 Gbps*<br>(pair production)                              |

| LV / HV                       | 1.2 V / 150 V                                                        | 1.8 V / 150 V                                                        |

|                               | -                                                                    | -                                                                    |

#### Hit Rate Conclusion

|       | Z<br>[mm] | R_in<br>[mm] | R_out<br>[mm] | Average hit rate<br>[10^4 Hz/cm^2] | Max hit rate<br>[10^4 Hz/cm^2] |

|-------|-----------|--------------|---------------|------------------------------------|--------------------------------|

| ITKE1 | 500.5     | 75           | 240           | 3.9                                | 23                             |

| ITKE2 | 715       | 101.9        | 350           | 16                                 | 38                             |

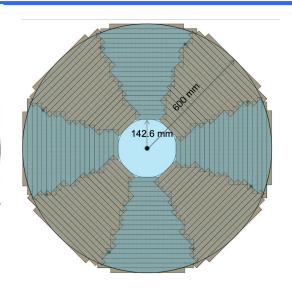

| ITKE3 | 1001      | 142.6        | 600           | 8.9                                | 75                             |

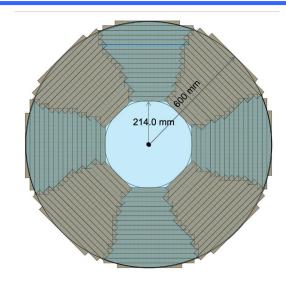

| ITKE4 | 1500      | 213.7        | 600           | 2.4                                | 6.3                            |

| OTKE  | 2903      | 406          | 1810          | 0.3                                | 3.5                            |

|       | te        | el:2903%20406%201 | 810%200.3%203.5                    |                                |

|-------|-----------|-------------------|------------------------------------|--------------------------------|

|       | R<br>[mm] | Half_Z<br>[mm]    | Average hit rate<br>[10^4 Hz/cm^2] | Max hit rate<br>[10^4 Hz/cm^2] |

| ITKB1 | 240       | 500.5             | 1                                  | 4.6                            |

| ITKB2 | 350       | 715               | 2.1                                | 41                             |

| ITKB3 | 600       | 1001              | 2.1                                | 27                             |

| OTKB  | 1800      | 2000              | 0.7                                | 0.9                            |

\* Maximum hit rate: barrel $\sim$ 4.1 $\times$ 10<sup>5</sup>, endcap $\sim$ 7.5 $\times$ 10<sup>5</sup>

| ITKB | 模块<br>数 | 本底平均计数<br>率(Hz/cm²) | 芯片平均数据率<br>Mbps<br>(42bit+4cm²) | 模块平均计数率Mbps(14芯片) | 模块最大计<br>数率Mbps<br>(14芯片) |

|------|---------|---------------------|---------------------------------|-------------------|---------------------------|

| 1    | 280     | 10k                 | 1.68                            | 23.5              | 108.2                     |

| 2    | 580     | 21k                 | 3.53                            | 49.4              | 964.3                     |

| 3    | 1344    | 21k                 | 3.53                            | 49.4              | 635.0                     |

计,数据率整体存疑(偏小?) · 桶部方案相对清楚,端盖 CMOS Strip方案不明

ITK系统无论桶部还是端盖,

均未让电子学系统参与芯片设

- 桶部模块: 2\*7=14 chips

- 总体来看,模块最大数据率距 离10Gbps还有一定裕量,后 端电子学为通道数约束

模块数-光纤共2204,按每层统计后端板 后端电子学板数:18+37+84=139块,机箱14个,

### ITK——Power(桶部)

#### **Technology Survey and our Choice for ITK: Option 1**

- CMOS sensor technology:

- Cost-effective due to widespread use in the semiconductor industry

- Combine the active detection layer and the readout electronics into a single device

- HVCMOS pixels:

- Large depletion depth (full depletion), large signal

- Radiation hard

Pixel size:

- Relatively large capacitance, leading to increased noise and power consumption

- New HVMOS (COFFEE) pixels R&D for CEPC:

- Utilizes 55 nm process instead of the 180 nm used in ATLASPix3 More functionality and less power consumption

Wafer resistivity: 1k-2k Ω·cm  $34 \times 150 \; \mu m^2$

512 rows × 128 columns Array size:

Power consumption: ~200 mW/cm²

#### ATLASPix3

- TSI 180nm HVCMOS on 200 Ωcm substrate

- Pixel size  $50 \times 150 \ \mu m^2$

- 372 rows × 132 columns

- 20.2 × 21 mm<sup>2</sup> reticle size

- Each pixel has 7-bit TOT + 10-bit timestamp

- · Continuous / triggered readout with 8b10b / 64b66b coding

- Power consumption ~160 mW/cm<sup>2</sup>.

| ITKB | 每层<br>模块<br>数 | 每层芯片功<br>耗开销(W) | 每层数据接<br>口总功耗<br>( <b>W</b> ) | 每层总功耗(芯<br>片+数据)/85% |

|------|---------------|-----------------|-------------------------------|----------------------|

| 1    | 280           | 3.14k           | 280                           | 4.02kW               |

| 2    | 580           | 6.50k           | 580                           | 8.32kW               |

| 3    | 1344          | 15.1k           | 1344                          | 19.29kW              |

- 桶部芯片功耗约200mW/cm²,每个模块14芯片,模块总功耗为11.2W

- 每模块固定功耗:数据接口1W+数据接口开销0.18W=1.18W,小计14.4W

- 考虑到组装和布线方便,按照每个模块一个电源通道

- 对应280、580、1344共2204通道电源,对应电源机箱共6+13+28=47个

- 高压约50~200V范围,要求模块独立调节,故高压通道数也为2204,合10个高压机箱

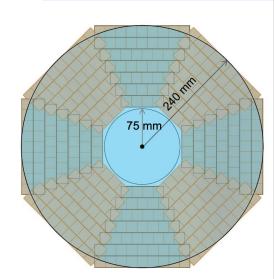

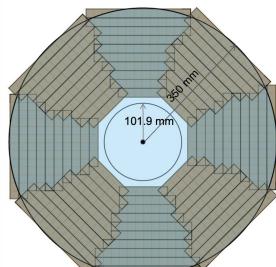

### ITK——探测器排布——端盖

- 每个端盖8个扇区,每层端盖由两个端盖旋转22.5度来重叠

- · 按每个扇区内每条ladder含芯片数来统计

- 第一层: 9+9+8+7+6+5+4=48芯片, 共7条ladder

- 第二层: 13+13+12+11+10+10+9+7+7+6=98芯片, 共10条ladder

- 第三层: 17+22+22+21+20+19+19+18+17+16+16+15+14+13+12+12+10+8+8=299芯片, 共19条ladder

- 第四层: 15+21+22+21+21+19+19+18+17+16+15+14+13+12+11+11+9=274芯片,共17条ladder

### ITK——Data Link (端盖)

#### Hit Rate Conclusion

### 对不上!

|       | Z<br>[mm] | R_in<br>[mm] | R_out<br>[mm] | Average hit rate<br>[10^4 Hz/cm^2] | Max hit rate<br>[10^4 Hz/cm^2] |

|-------|-----------|--------------|---------------|------------------------------------|--------------------------------|

| ITKE1 | 500.5     | 75           | 240           | 3.9                                | 23                             |

| ITKE2 | 715       | 101.9        | 350           | 16                                 | 38                             |

| ITKE3 | 1001      | 142.6        | 600           | 8.9                                | 75                             |

| ITKE4 | 1500      | 213.7        | 600           | 2.4                                | 6.3                            |

| OTKE  | 2903      | 406          | 1810          | 0.3                                | 3.5                            |

|       | te        | el:2903%20406%201 | 810%200.3%203.5                    |                                |

|-------|-----------|-------------------|------------------------------------|--------------------------------|

|       | R<br>[mm] | Half_Z<br>[mm]    | Average hit rate<br>[10^4 Hz/cm^2] | Max hit rate<br>[10^4 Hz/cm^2] |

| ITKB1 | 240       | 500.5             | 1                                  | 4.6                            |

| ITKB2 | 350       | 715               | 2.1                                | 41                             |

| ITKB3 | 600       | 1001              | 2.1                                | 27                             |

| ОТКВ  | 1800      | 2000              | 0.7                                | 0.9                            |

|                |                                                      |                                                                                          |                                                                                                                                                | <b>/</b>                                                                                                                                                                                      |

|----------------|------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 (per Sector) | 2                                                    | 3                                                                                        | 4                                                                                                                                              | Total                                                                                                                                                                                         |

| 6              | 8                                                    | 15                                                                                       | 12                                                                                                                                             | 18                                                                                                                                                                                            |

| 7              | 10                                                   | 18                                                                                       | 15                                                                                                                                             | 1600                                                                                                                                                                                          |

| 48             | 98                                                   | 260                                                                                      | 236                                                                                                                                            | 20544                                                                                                                                                                                         |

| 20181.03       | 42796.32                                             | 116080.28                                                                                | 106081.77                                                                                                                                      | 9.12e6                                                                                                                                                                                        |

| 23184          | 47334                                                | 125580                                                                                   | 113988                                                                                                                                         | 9.92e6                                                                                                                                                                                        |

| 46.368         | 94.668                                               | 251.16                                                                                   | 227.98                                                                                                                                         | 1.98e4                                                                                                                                                                                        |

| 3.9e2          | 1.6e3                                                | 8.9e2                                                                                    | 2.4e2                                                                                                                                          | -                                                                                                                                                                                             |

| 2.89e8         | 2.42e9                                               | 3.58e9                                                                                   | 8.75e8                                                                                                                                         | 2.29e11                                                                                                                                                                                       |

|                | 6<br>7<br>48<br>20181.03<br>23184<br>46.368<br>3.9e2 | 6 8<br>7 10<br>48 98<br>20181.03 42796.32<br>23184 47334<br>46.368 94.668<br>3.9e2 1.6e3 | 6  8  15    7  10  18    48  98  260    20181.03  42796.32  116080.28    23184  47334  125580    46.368  94.668  251.16    3.9e2  1.6e3  8.9e2 | 6  8  15  12    7  10  18  15    48  98  260  236    20181.03  42796.32  116080.28  106081.77    23184  47334  125580  113988    46.368  94.668  251.16  227.98    3.9e2  1.6e3  8.9e2  2.4e2 |

| ITKE | Ladder最<br>大芯片数 | 本底平均计数率<br>(Hz/cm²) | 本底最高计数率<br>(Hz/cm²) | 模块平均计数率<br>Mbps | 模块最大计数率<br>Mbps | 每层模块数(光<br>纤数) |

|------|-----------------|---------------------|---------------------|-----------------|-----------------|----------------|

| 1    | 9               | 39k                 | 230k                | 47.2            | 278.4           | 7*8*2层*2侧=224  |

| 2    | 13              | 160k                | 380k                | 279.7           | 664.3           | 10*32=320      |

| 3    | 22              | 89k                 | 750k                | 263.3           | 2218.9          | 19*32=608      |

| 4    | 22              | 24k                 | 63k                 | 71.0            | 186.4           | 17*32=544      |

- 端盖刚刚完成排布,从作图上看与表格数字不完全对应,暂按照图上数字统计

- 本底计数率也刚刚刷新,模块数据率峰值离光纤能力尚有裕量,按每个模块一根光纤考虑

- 模块总数共: 224+320+608+544=1696, 合后端板106块, 机箱12个(2侧对称)

### ITK——Power(端盖)

#### **Technology Survey and our Choice for ITK: Option 2**

- CMOS sensor technology:

- Cost-effective due to widespread use in the semiconductor industry

- · Combine the active detection layer and the readout electronics into a single device

- CMOS strips compared with CMOS pixels:

- · Less expensive and relatively lower power consumption

- Simpler readout with fewer technical barriers

- · Comparable or even better spatial resolution

- Negligible track ambiguity using specific detector layout design:

For example: the GEPC Trik endcap is designed with strip sensors with a 22.5° cross angle

between 2 half-layers. Drawback: it requires twice number of sensors compared with pixels.

- CMOS Strip Chip (CSC) R&D for CEPC:

- · Utilizes 150 nm process, based on CHESS for ATLAS ITK strip sensor

- Wafer resistivity:

- 2k Ω·cm

- Strip pitch size:

- Strip number per chip: 1024

- Power consumption: ~80 mW/cm²

- · 端盖芯片功耗约 $80 \text{mW/cm}^2$ ,每个芯片336 mW

- · Ladder上功耗最高为7.39W DC-DC额度

- · 每层功耗需结合芯片数(每条ladder变动)和模块数来 统计

- · 功耗共计11.1kW,因模块功耗较低,因此考虑按扇区设计电源汇总分配结构,对应192电源通道,按每侧电源独立考虑,共4个机箱(每侧端盖共用2个机箱)

- 按模块高压独立可调(50~200V), 共1696高压通道, 合8高压机箱

| ITK<br>E | Ladde<br>r最大<br>芯片<br>数 | Ladder<br>最大功耗<br>(W) | 每扇<br>区芯<br>片数 | 每扇区芯<br>片净功耗<br>( <b>W</b> ) | 每扇区数据接口功<br>耗<br>(即每扇区模块数)<br>( <b>W</b> ) | 每扇区总功耗<br>(芯片+数据)<br>÷85%<br>(W) | 每层总功耗<br>(×8×2层<br>×2侧)<br>(W) | 电源通道(按<br>扇区统计) |

|----------|-------------------------|-----------------------|----------------|------------------------------|--------------------------------------------|----------------------------------|--------------------------------|-----------------|

| 1        | 9                       | 3.02                  | 48             | 16.1                         | 7                                          | 27.2                             | 870.6                          | 1 × 32          |

| 2        | 13                      | 4.36                  | 98             | 32.9                         | 10                                         | 50.5                             | 1616.0                         | 1× 32           |

| 3        | 22                      | 7.39                  | 299            | 100.5                        | 18                                         | 139.4                            | 4497.4                         | 2× 32           |

| 4        | 22                      | 7.39                  | 274            | 92.1                         | 15                                         | 126                              | 4105.9                         | 2× 32           |

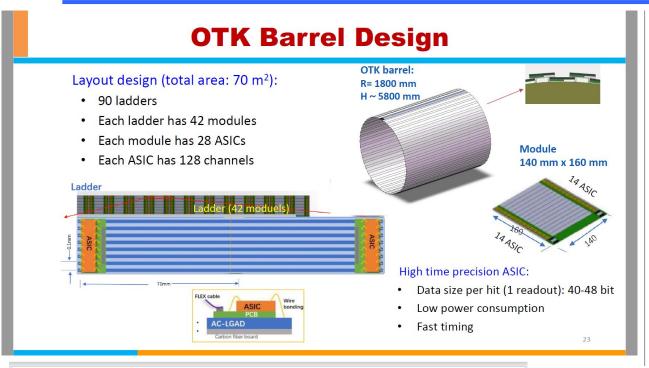

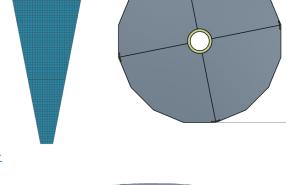

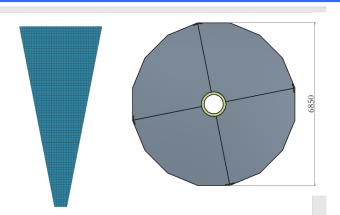

### OTK-探测器排布

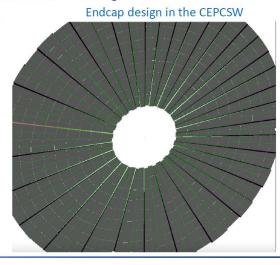

#### Endcap design

- Hit rate estimation: maximum ~35k Hz/cm²

- · Update the sector module design with new HS design

- 400mm 1800mm: 720 modules

- √ 5 inner rows with 1 sector module

- ✓ 5 out rows with 2 sector modules

#### Sector Module

- Overlap to reduce the dead area

- √ 24 petals/layer

- √ 10 rows/petal,

- ✓ 7.5° per petal,

- ✓ Overlap 0.5°/petal

- o140 mm / row at R direction

- 桶部排布相对清楚,散热优化中基本不影响 Ladder设计

- · 端盖方案尚未最终确定,还有梯形、弧形两 种不同方案

#### **OTK-Data Link**

#### Hit Rate Conclusion

|       | Z<br>[mm] | R_in<br>[mm] | R_out<br>[mm] | Average hit rate<br>[10^4 Hz/cm^2] | Max hit rate<br>[10^4 Hz/cm^2] |

|-------|-----------|--------------|---------------|------------------------------------|--------------------------------|

| ITKE1 | 500.5     | 75           | 240           | 3.9                                | 23                             |

| ITKE2 | 715       | 101.9        | 350           | 16                                 | 38                             |

| ITKE3 | 1001      | 142.6        | 600           | 8.9                                | 75                             |

| ITKE4 | 1500      | 213.7        | 600           | 2.4                                | 6.3                            |

| OTKE  | 2903      | 406          | 1810          | 0.3                                | 3.5                            |

|       | R<br>[mm] | Half_Z<br>[mm] | Average hit rate<br>[10^4 Hz/cm^2] | Max hit rate<br>[10^4 Hz/cm^2] |

|-------|-----------|----------------|------------------------------------|--------------------------------|

| ITKB1 | 240       | 500.5          | 1                                  | 4.6                            |

| ITKB2 | 350       | 715            | 2.1                                | 41                             |

| ITKB3 | 600       | 1001           | 2.1                                | 27                             |

| ОТКВ  | 1800      | 2000           | 0.7                                | 0.9                            |

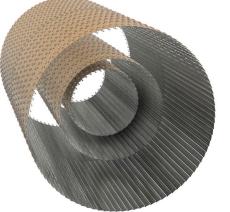

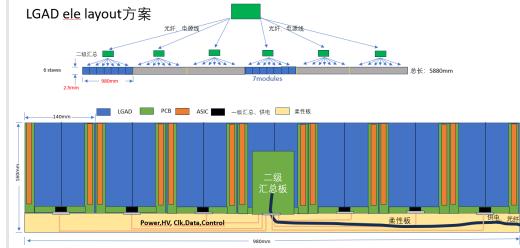

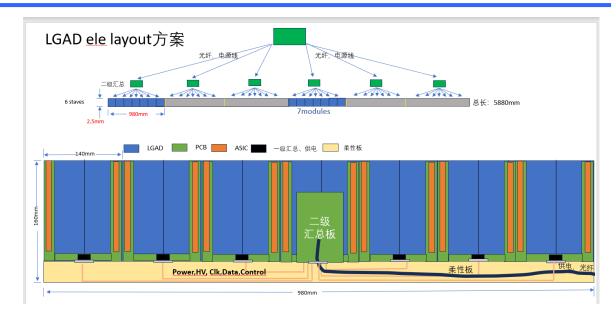

· 芯片数据位宽: 48bit/event

#### • 桶部:

- 光纤接口位于二级汇总版,对应7modules(1 stave),供7\*28=196芯片,模块平均数据率7kHz\*14cm\*14cm\*48bit=65.9Mbps,峰值9kHz→84.7Mbps,对应光纤接口数据率461.3Mbps/1355.2Mbps(平均/峰值),远低于限额

- 一条stave共6 ladder(6光纤),共90条stave,即540光纤,对应34块后端板,4机箱

#### 端盖(弧形方案):

- 两端盖共48Pedal,每Pedal共10圈计15sector(内5圈1个sector,外5圈2个sector);总面积19.4m2,每Pedal面积

4041.7cm²,平均数据率3kHz\*4041.7\*48bit=582Mbps,峰值35kHz→6.79Gbps;如果进一步按照每个Sector来布置光纤,即使端盖内圈计数率显著高于外圈,也可保证数据率限额裕量充足

- 两侧共48pedal计720sector,即720光纤,对应45块后端板,5机箱(每侧端盖独立各两个机箱)

#### **OTK-Power**

- 芯片每通道功耗<mark>20mW/ch</mark>,每芯片128通道,总功耗2.56W

- 桶部:

- 共90条Ladder, 一条Ladder共6 stave, 7module/stave, 22ASIC/mo

- <u>每个模块功耗56.32W(DC-DC设计注意)</u>

- 共90×6×7×22=83,160 ASICs,净功耗212.9kW

- 每个ladder光纤接口净功耗1W, 共540 ladder, 0.54kW

- 考虑DC-DC效率85%, 总功耗251.1kW

- 每个模块对应1个电源通道,对应3780电源通道,共79电源机箱

#### • 端盖

- 弧形方案更新了ASIC的具体排布,每Pedal共240 ASIC

- 两侧端盖共48Pedal, 共11520ASICs, 净功耗29.5kW

- 每个sector光纤净功耗1W, 共0.72kW

- 考虑DC-DC效率85%,总功耗35.6kW

- 每个sector对应1个电源通道,对应720电源通道,共15电源机箱(按两侧端盖独立机箱数为16)

Data rate / petal

| Row (140<br>mm/rwo) | Chip per row | Date rate (HZ) |

|---------------------|--------------|----------------|

| R0 (400-540)        | 11           | 1533882.59     |

| R1: 540-680         | 14           | 335365.01      |

| R2: 680-820         | 17           | 412334.029     |

| R3:                 | 19           | 489303.047     |

| R4                  | 23           | 566272.066     |

| R5                  | 25           | 643241.085     |

| R6                  | 29           | 720210.104     |

| R7                  | 31           | 797179.122     |

| R8                  | 34           | 874148.141     |

| R9: 1660-1800       | 37           | 951117.16      |

|                     |              |                |

#### **OTK-HV**

- · 考虑按照module级别,各模块高压独立可调,150~200V范围

- 桶部

- 90×6×7=3780模块,对应3780高压通道,合17高压机箱

- 端盖

- 共720sector, 每侧360通道, 对应2高压机箱, 共4高压机箱

### ECAL—

#### ECAL电缆估算

- ECAL桶部,正反梯形排布

- 模块数量: Phi: 32, Z: 15, 共480个模块

- - 1层到28层,奇数层每层36根,偶数层晶体数目不一致正梯形晶体数量1000,反梯形晶体数量992

- 电缆估算: 1根/模块

- AWG15(线径1.45mm,电流:6.5A/7.4A) AWG18(线径1.08mm,电流:3.2A/3.7A)

- 模块功耗估计: 1000\*2\*20mW = 40W

- 光纤估算: 1根/模块

- 模块数据量估算: 待定

- 桶部电缆总计

- 类型: 高压, 低压(正负?), 光纤

- 电缆双向走向, 每端240根 (平均方案)

- 电缆双向走向,一端224根,一端256根

- 未确定电缆: 刻度方案

- 按每根晶体本底平均事例率100kHz, 数据位 宽48bit/event

- 每个模块1000晶体总数据率(平均): 1000\*100kHz\*48bit\*2端=9.6Gbps

- 考虑到部分晶体事例率已达300kHz,每个模 块一根光纤基本不可行,<u>每个模块需要至少</u> 两根光纤来维持一定裕量

- 目前根据本底估算,事例率还要进一步提高 -待进一步确认

- 光纤数: 480\*2=960根, 合60块后端板, 6机 箱

- 电源功耗:

- 每通道15mW/ch, 每个模块1000\*2\*15mW=30W

- 光纤接口1W

- 总功耗31W/0.85\*480=17.5kW

- 电源通道每模块一个共480通道。合电源机箱10个

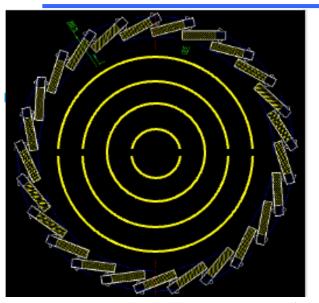

### ECAL——端盖

- · 端盖排布方案还在优化过程中, 目前没有一个确定的基本说法

- · 按照该图,模块数约在122~96个, 初步按照每侧端盖130模块考虑

- · 端盖整体事例率比桶部会更高, 按照每个模块两根光纤初步考虑

- 光纤数:

- 130\*2侧\*2根=520

- 合后端板33块(或34按照两侧独立),机箱4个

#### • 电源:

- 总功耗31W/0.85\*260=9.48kW

- 按模块合电源通道260个,电源机箱6 个

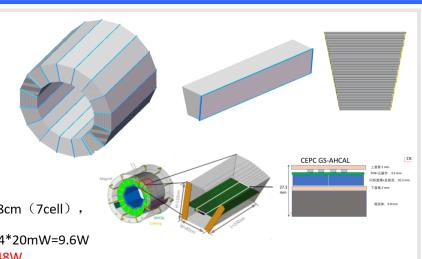

### HCAL-Data Link桶部

#### HCAL电缆估算

- HCAL桶部排布

- 总通道数: 338万

- 分区: 16

- 层数: 48

- Cell尺寸: 4\*4cm

- 电子学板尺寸

- Z向: 60cm(15cell)

- Phi问: 24cm (6cell) , 28cm (7cell) , 32cm (8cell)

- FEE单板最大功耗: 15\*8\*4\*20mW=9.6W

- 汇总板最大功耗: 9.6\*5=48W

- 桶部电缆数量

- 电缆类型: 高压, 低压(正负?), 光纤

- 1/16 分区电缆数量: 19\*3+29\*4=173

- 总电缆数量: 一端173\*16=2768, 总5536

- AWG12(线径2.05mm, 电流: 13.1A/14.9A)

- HCAL数据采用端部汇总方式读出, 单元尺寸、探测器本底计数率、排布 方式等目前均未确定

- 仅能初步按照每个汇总板数据率不超过10Gbps来估计和要求

- 目前估算光纤数量:

- 每1/16分区: 19\*3+29\*4=173

- 总光纤数173\*16\*2=5536

- 一 合后端板346块(两侧独立),共36机箱

1~19层 横向3PCB 20~48层 横向4PCB 汇总板汇总z向一半共5 块PCB, 1光纤出口

### HCAL-Power桶部

- · 最大PCB尺寸——对应闪烁体cell数:

- Z向: 60cm (15cell)

- Phi向: 24cm (6cell), 28cm (7cell), 32cm (8cell)

- · 考虑光收集,每个4cm\*4cm的cell可能需要1~4个SiPM来收集(方案未定)

- 即最大PCB对应SiPM通道数为15\*8\*4=480

- ASIC功耗为15mW/ch, 前端PCB最大功耗为480\*15mW=7.2W, 每个汇总板提供5块PCB的电源, 即DC-DC负载功耗为7.2\*5=36W

- 桶部总功耗为

- ASIC净功耗: 总通道338万\*4SiPM\*15mW=202kW

➤ 细致计算通道数为: 15\*8 (PCBcell) \*173板\*10列\*16扇区=332万cell, 基本一致

- 每根光纤固定功耗为1W, 共5536W

- 按DC-DC的85%效率,总功耗为(202+5.5)/0.85=244.2kW

- 按每模块一个电源通道合电源通道5536个,电源机箱116个

### HCAL-Data Link端盖

#### HCAL电缆估算

- HCAL端盖部排布

- 总通道数: 单端112万, 总共224万

- 分区: 16

- 层数: 48

- Cell尺寸: 4\*4cm

- 端盖电缆数量

- 电缆类型: 高压, 低压(正负?), 光纤

- 每区功耗: 1459\*20mW=30W

- 1/16 分区电缆数量: 48

- 总电缆数量: 一端48\*16=768, 总1536

- AWG12(线径2.05mm,电流: 13.1A/14.9A)

- •未确定电缆:刻度方案

- 总光纤数为48层\*16扇区\*2端盖=1536

- 合后端板96块,10机箱

- HCAL端盖共48层,每层分16 扇区,按照每个扇区一根光纤 进行数据读出

- · 需特别考虑端盖内圈本底计数率(目前尚未明确),但按照径向平均可能问题不严重,暂按照每个扇区数据率可不超过10Gbps考虑

- 按单侧通道数112万,每个扇区共约1458cell,即使按照ECAL数据率100kHz估计,每扇区总数据率也为7.0Gbps,应可在安全范围内(每个cell对应的4个SiPM数据率未按照×4估计)

### HCAL-Power端盖

#### HCAL电缆估算

- HCAL端盖部排布

- 总通道数: 单端112万, 总共224万

- 分区: 16

- 层数: 48

- Cell尺寸: 4\*4cm

- 端盖电缆数量

- 电缆类型: 高压, 低压(正负?), 光纤

- 每区功耗: 1459\*20mW=30W

- 1/16 分区电缆数量: 48

- 总电缆数量: 一端48\*16=768, 总1536

- AWG12(线径2.05mm,电流: 13.1A/14.9A)

- •未确定电缆:刻度方案

- · 按单侧通道数112万,每个扇区共约 1458cell,每个cell对应4SiPM,则每 个扇区5832电子学通道

- 每个扇区功耗87W –或需要两个DC-DC模块供电

- ASIC净功耗为224万 \*4SiPM\*15mW/ch=134.4kW

- · 每根光纤固定功耗1W, 共1536W

- · 总功耗为(134.4k+1536) /0.85=159.9kW

- 按每层分扇区一个电源通道考虑,合 电源通道1536个,电源机箱32个(两 侧独立)

### 量能器——高压方案

- · ECAL、HCAL的高压方案暂不明确

- 按模块统一提供,局部补偿——模块之间因温度梯度导致的不一致性可能较大

- 按每个SiPM独立可调——复杂度太高,控制数据量太大

- 分区域提供高压——强烈依赖探测器和散热仿真结果

- 目前仅能统一按模块级统一提供高压来考虑

- ECAL桶部: 480模块, 共480高压通道, 合2高压机箱

- ECAL端盖: 260模块, 共260高压通道, 合2高压机箱

- HCAL桶部: 5536汇总板, 共5536高压通道, 合26高压机箱(汇总板分布在两侧端部)

- HCAL端盖: 1536扇区层, 共1536高压通道, 合32高压机箱

### Muon (更新)

| Muon             | Module | Channel/Module | Readout<br>Channel | Hit rate/Hz<br>(worst case) | Data format                                    | Raw data rate /<br>Gbps |

|------------------|--------|----------------|--------------------|-----------------------------|------------------------------------------------|-------------------------|

| Barrel           | 192    | 169.5          | 32544              | 10 k                        | 48bit                                          | 15.63                   |

| Inner<br>endcaps | 64     | 144            | 9216               | 10k~100 k,<br>Average 20 k  | (8b BX+ 10b<br>ADC + 2b range<br>+ 9b TOT + 7b | 8.85                    |

| Outer<br>endcaps | 64     | 256            | 16384              | 10 k                        | TOA+ 4b chn ID<br>+ 8b chip ID)                | 7.87                    |

| Total            |        |                | ~58.2 k            |                             |                                                | ~32.4                   |

- · Muon未提供探测器具体排布,仅提供了参考Belle2的类比探测器规模

- · 按每个Module—根光纤考虑:

- 桶部192光纤,12机箱;端盖128光纤,8机箱

- 功耗的考虑缺少探测器排布,情况不明。考虑前端ASIC理应兼容到ECAL的 SiPM读出,但因通道数多,可能导致模块功耗较大。因此按照HCAL相同量 级来提供电源机箱、做上限考虑、即:

- 桶部51电源机箱、端盖34电源机箱

# 汇总

| 探测器             | 光纤最高<br>数据率 | 每模块光<br>纤数量      | 光纤数量        | 后端板数<br>量        | 数据机箱<br>数 | 模块最大<br>功耗 ( <b>W</b> ) | 总功耗<br>(kW)      | 电源通道<br>数       | 电源机箱<br>数      | 是否需要高<br>压 | 高压通<br>道数 | 高压机箱<br>数        | 触发板数 | 触发机箱<br>数 | Comme<br>nt |

|-----------------|-------------|------------------|-------------|------------------|-----------|-------------------------|------------------|-----------------|----------------|------------|-----------|------------------|------|-----------|-------------|

| VTX             | (Gbps)      | <mark>1~2</mark> | 88          | 6                | 1         | 25                      | 0.45             | 8               | 1              | ~-10V      | 58        | 1                |      |           |             |

| TPC             | 0.1         | 1                | 516         | 34               | 4         | -                       | 20               | 516             | 12             | SHV        | 516       | 4                |      |           |             |

| ITK-<br>Barrel  | 0.96        | 1                | 2204        | 139              | 14        | 11.2                    | 31.59            | 2204            | 47             | 50~200V    | 2204      | 10               |      |           |             |

| ITK-<br>EndCap  | 2.2         | 1                | 1696        | 106              | 12        | 7.4                     | 11.1             | 192             | 4              | 50~200V    | 1696      | 8                |      |           |             |

| OTK-<br>Barrel  | 1.4         | 1                | 540         | 34               | 4         | <b>56.3</b>             | <b>251.1</b>     | 3780            | 79             | 150~200V   | 3780      | 17               |      |           |             |

| OTK-<br>EndCap  | 0.7         | 1                | 720         | 45               | 5         | <b>58.9</b>             | 35.6             | 720             | 15             | 150~200V   | 720       | 4                |      |           | 排布待明 确      |

| ECAL-<br>Barrel | 4.8         | 2                | 960         | 60               | 6         | 30                      | 17.5             | 480             | 10             | 40~60V     | 480       | 2                |      |           |             |

| ECAL-<br>EndCap | ?           | 2                | 520         | 34               | 4         | ?                       | 9.5              | 260             | 6              | 40~60V     | 260       | 2                |      |           | 排布、本 底待明确   |

| HCAL-<br>Barrel | ?           | 1                | <b>5536</b> | <mark>346</mark> | 36        | 36                      | 244.2            | <b>5536</b>     | 116            | 40~60V     | 5536      | 26               |      |           | 排布、本 底待明确   |

| HCAL-<br>EndCap | ?           | 1                | 1536        | 96               | 10        | <mark>87</mark>         | 159.9            | 1536            | 32             | 40~60V     | 1536      | 32               |      |           | 排布、本 底待明确   |

| Muon-<br>Barrel | ?           | 1                | 192         | 12               | 2         | ?                       | 244.2<br>(按HCAL) | 5536<br>(按HCAL) | 116<br>(按HCAL) | ?          | 5536      | 26               |      |           | 探测器方案?      |

| Muon-<br>EndCap | ?           | 1                | 128         | 8                | 2         | ?                       | 159.9<br>(按HCAL) | 1536<br>(按HCAL) | 32<br>(按HCAL)  | ?          | 1536      | 32               |      |           | 探测器方案?      |

| 总计              |             |                  | 14636       | 920              | 100       |                         | 1185.04          | 22304           | 470            |            | 23858     | <mark>164</mark> |      |           |             |

### 触发初步考虑

- 触发方案有待进一步明确

- 物理目标对触发方案的需求

- 参与触发的子探测器需进一步讨论,及探测器可提取的触发特征信息

- 进一步明确触发的算法,考虑其算法复杂度来规划资源

- 触发延迟需求需进一步明确:

- 电子学: 后端板依靠板载大RAM, 触发延迟可按照兼容硬件触发/软件触发来考虑

- ▶ 参考指标: 如缓存8GB, 通用后端板16通道满数据率160Gbps, 则缓存时间长度可达 8G×8/160=0.4s

- 探测器:探测器响应目前不明确,一些慢速探测器将影响触发延迟的长短

- · 按目前情况初步估计,触发系统约需160个触发板,20个ATCA机箱,10个机柜。

#### • 问题:

- Z pole模式目前本底情况过高(例如特别是ECAL)且未来优化情况不明,必须考虑未来 升级——电子学间空间设计时已固定,需要为未来探测器升级留出空间

- 部分系统目前本底仍基于30MW功率考虑,需统一按照50MW,给出平均计数率和峰值计数率

https://cds.cern.ch/record/1027431/files/p165.pdf <u>Ø2200</u> UXC55 Ø 13500<sub>5</sub> 0 0 UXC55 Wall (7 m) USC55 USC55 USC55 PIX tank Underground **Counting Room** gure 4: Point 5 Underground Area; The experimental cavern Experimental CC55 with the adjacent, albeit a 7 meter thick concrete wall, Hall derground counting room USC55, consisting of two floors. Hole between USXCoo et USCOO **FAR SIDE** ➤ USC55尺寸: 长19m宽17m总长85m\* ▶洞室内部用钢结构建成了一个4层的机 SS2 tank X3 ▶洞室中的机柜区域集中放置(对应下表 PS tanks X2 X1 **NEAR SIDE**

CMS机房USC55的结构图

\*: https://doi.org/10.1007/978-3-031-12851-6\_49

### CMS机柜组织

| + <b>Z</b> |           |              | Upp         |               |               | (Zone S2)   |                 |            |           | - <b>Z</b> |

|------------|-----------|--------------|-------------|---------------|---------------|-------------|-----------------|------------|-----------|------------|

|            | A         | В            | C           | D             | E             |             | F               | G          | Н         |            |

| 01         |           |              |             | ECAL spare    | Cal Reg       |             | HCAL HTR        |            |           |            |

| 02         | TOTEM     | TOTEM        | DAQ         | ECAL ULR      | Cal Reg       |             | HCAL HTR        | DAQ        | x         |            |

| 03         | TOTEM     | TOTEM        | CASTOR HV   | ECAL ULR      | %Cal Reg      |             | HCAL HTR        | EBE DCS    | x         |            |

| 04         | TOTEM     | TOTEM        | CASTOR HV   | ECAL ULR      | Cal Reg       |             | HCAL HTR        | EBE DCS    | x         |            |

| 05         | TOTEM     | DAQ          | UX DCS      | ECAL SRP/TST  | %Cal Res      |             | %HCAL HTR       | Presh. HV  | X         |            |

| 06         | RAMSES    | EB HV        | HCAL DCS    | ECAL ULR      | Cal Reg       |             | HCAL HTR        | EB HV      | x         |            |

| 07         | Access    | EB HV        | HCAL DCS    | ECAL ULR      | Cal Reg       |             | HCAL HTR        | EB HV      | x         |            |

| *08        | ASSM      | EB HV        | HCAL SrcDrv | ECAL ULR      | Cal Reg       |             | HCAL HTR        | EB HV      | x         |            |

| *09        | ASSM      | EE HV        | HPD HV      | DAQ           | Cal Reg       |             | HCAL HTR        | EE HV      | x         |            |

| 10         | ASSM      | Presh. DCS   | HPD HV      | FRL PC        | Cal Reg       |             | DAQ             | Presh. DCS | x         |            |

| 11         | ASSM      | ECAL LV      | HPD HV      | X             | TOTEM         | Trig        | EBE Lt Mn       | ECAL Cool  | DSS       |            |

| 12         | ASSM      | ECAL LV      | HPD HV      | x             | CASTOR        |             | EBE Lt Mn       | ECAL Cool  | DSS       |            |

| 13         | ASSM      | Presh. LV    | HPD HV      | Presh. Misc   | ZDO           |             | EBE Lt Mn       | ECAL Cool  | DSS       |            |

| 14         | ASSM      | Rack Pwr     | PMT HV      | Presh. Misc   | DAQ I         | PP          | EB Misc         | EE Misc    | DSS       |            |

| 15         | ASSM      | Rack Pwr     | DSS         | DSS           | DSS           | \$          | DSS             | DSS        | DSS       |            |

|            |           |              |             |               | < Passageway> |             |                 |            |           |            |

| 16         | Fire Det. | TTC PCs      | DAQ PC      | DAQ Switch    | Netw          | k           | DCS PCs         | Spare PCs  | UPS PCs   |            |

| *17        | Fire Det. | TK PCs       | DAQ PC      | DAQ Switch    | Netw          | k           | HCAL PCs        | Trig PCs   | UPS PCs   |            |

| *18        | Fire Det. | TK/Pixel PCs | DAQ PC      | DAQ Switch    | Netwk         |             | ECAL DCS/ES PCs | Muon PCs   | UPS PCs   |            |

| 19         | Fire Det. | TOTEM PCs    | DAQ PC      | DAQ Switch    | Netwk         |             | ECAL FED PCs    | Align PCs  | UPS PCs   |            |

| +Z         |           |              |             | Lower         | Floor         | (Zone S1)   |                 |            |           | -Z         |

| +L         | A         | R            |             | C             | D             | (Zone S1)   | F               | G          | н         | -L         |

| 00         | **        | <i>u</i>     |             | Presh. ULR    | Presh. ULR    | TK. FEC     | TK. FEC         | DT/RO/SC   |           |            |

| 01         |           |              |             | DAQ           | DT TrkFnd     | Opt.Cpl.    | RPC Trig        | Pixel FEC  |           |            |

| 02         | TK. Ctrl  | DAQ          |             | DAQ           | DT TrkFnd     | TTC         | RPC Trig        | Pixel Ctrl | RPC B HV  |            |

| 03         | TK. Ctrl  | TK. FED TIB+ | -TID        | TK. FED TOB   | DT TrkFnd     | %TTC        | RPC Trig        | Pixel FED  | RPC B HV  |            |

| 04         | TK. Ctrl  | TK. FED TIB+ |             | TK. FED TOB   | CSC TrkFnd    | Global      | RPC Trig        | Pixel FED  | RPC B HV  |            |

| 05         | TK. Ctrl  | TK. FED TIB+ |             | TK. FED TOB   | CSC TrkFnd    | %Cal Global | %RPC Trig       | DAQ        | RPC B HV  |            |

| 06         | TK. Ctrl  | DAQ          |             | DAQ           | FRL PC        | TTS         | DAQ             | CSC FED    | RPC B HV  |            |

| 07         | TK. Ctrl  | DAQ          |             | DAQ           | DT HV         | TTS         | x               | CSC FED    | RPC B HV  |            |

| *08        | TK. Ctrl  | TK. FED TE   | C-          | TK. FED TEC+# | DT HV         | BPTX        | BRM#            | CSC FED    | RPC E+ HV |            |

| *09        | TK. Ctrl  | TK. FED TE   |             | TK. FED TEC+# | DT HV         | LHC         | DAQ#            | DAO PP     | RPC E+ HV |            |

| 10         | TK LV Mon | TK. FED TE   |             | TK. FED TEC+  | DT HV         | BPM         | DSS             | ME1/1 HV   | RPC E- HV |            |

| 11         | CSC HV    | DAQ          |             | DAQ           | DT HV         | DSS         | DSS             | DSS        | RPC E- HV |            |

| 12         | CSC HV    | TK. Ctrl     |             | Work Area     | DAQ PC        | Work Area   | Work Area       | Work Area  | Work Area |            |

| 13         | CSC HV    | TK. Ctrl     |             | Work Area     | Work Area     | Work Area   | Work Area       | Work Area  | Work Area |            |

| 14         | BCAM      | TK. Ctrl     |             | Work Area     | Work Area     | Work Area   | Work Area       | Work Area  | Work Area |            |

| 15         | Rack Pwr  | TK. Ctrl     |             | Work Area     | Work Area     | Work Area   | Work Area       | Work Area  | Work Area |            |

|            |           |              |             |               | < Passageway> |             |                 |            |           |            |

|            |           |              |             |               |               |             |                 |            |           |            |

- · 仅计算电子学、触发、高压机柜时,约30行7列共210个机柜,不同种类机柜在 其中混排

- · DAQ、慢控机柜集中在4行7列不到28个机柜

### CMS机柜组织与探测器排布

### Rack Layout in USC55 (version 5.6)

# 机柜需考虑探测器排布,光纤长度敏感的机柜通常与触发。完时相关

Both floors are shown. Racks are installed out to #11, 15 on S1,2. Row A is closest to the shaft. Racks 0 (S1) and 1 (S2) are closest to the interaction hall (UXC55). Rack rows are spaced 1.5 m front face to front face (B-C,D-E,F-G,H-J)) and 1.0 m rear face to rear face (A-B,C-D,E-F,G-H,J-K). \*There is a 30 cm optional gap between racks 8 & 9 (and 17 & 18 on S1) to improve access over an underfloor structural beam. #There is a 30 cm gap between racks S1C08 and S1C09 and also between S1F08 and S1F09 for a vertical structural column. %There are holes between the floors located at E05 and F05. RED RACKS HAVE CRITICAL LENGTH FIBERS TO THE DETECTOR. GREEN RACKS HAVE NON-CRITICAL PATH FIBERS TO THE DETECTOR. DAQ RACKS ARE BLUE. GREY RACKS ARE RESERVATIONS. Definition of abbreviations. Information about racks. Rack Wizard (rack entry tool).

| + <b>Z</b> |              |                 | Lower         | Floor       | (Zone S1)    |              |              | -Z        |

|------------|--------------|-----------------|---------------|-------------|--------------|--------------|--------------|-----------|

|            | $\mathbf{A}$ | В               | C             | D           | $\mathbf{E}$ | $\mathbf{F}$ | $\mathbf{G}$ | H         |

| 00         |              |                 | Presh. ULR    | Presh. ULR  | TK. FEC      | TK. FEC      | DT/RO/SC     |           |

| 01         |              |                 | DAQ           | DT TrkFnd   | Opt.Cpl.     | RPC Trig     | Pixel FEC    |           |

| 02         | TK. Ctrl     | DAQ             | DAQ           | DT TrkFnd   | TTC          | RPC Trig     | Pixel Ctrl   | RPC B HV  |

| 03         | TK. Ctrl     | TK. FED TIB+TID | TK. FED TOB   | DT TrkFnd   | %TTC         | RPC Trig     | Pixel FED    | RPC B HV  |

| 04         | TK. Ctrl     | TK. FED TIB+TID | TK. FED TOB   | CSC TrkFnd  | Global       | RPC Trig     | Pixel FED    | RPC B HV  |

| 05         | TK. Ctrl     | TK. FED TIB+TID | TK. FED TOB   | CSC TrkFnd  | %Cal Global  | %RPC Trig    | DAQ          | RPC B HV  |

| 06         | TK. Ctrl     | DAQ             | DAQ           | FRL PC      | TTS          | DAQ          | CSC FED      | RPC B HV  |

| 07         | TK. Ctrl     | DAQ             | DAQ           | DT HV       | TTS          | X            | CSC FED      | RPC B HV  |

| *08        | TK. Ctrl     | TK. FED TEC-    | TK. FED TEC+# | DT HV       | BPTX         | BRM#         | CSC FED      | RPC E+ HV |

| *09        | TK. Ctrl     | TK. FED TEC-    | TK. FED TEC+# | DT HV       | LHC          | DAQ#         | DAQ PP       | RPC E+ HV |

| 10         | TK LV Mon    | TK. FED TEC-    | TK. FED TEC+  | DT HV       | BPM          | DSS          | ME1/1 HV     | RPC E- HV |

| 11         | CSC HV       | DAQ             | DAQ           | DT HV       | DSS          | DSS          | DSS          | RPC E- HV |

| 12         | CSC HV       | TK. Ctrl        | Work Area     | DAQ PC      | Work Area    | Work Area    | Work Area    | Work Area |

| 13         | CSC HV       | TK. Ctrl        | Work Area     | Work Area   | Work Area    | Work Area    | Work Area    | Work Area |

| 14         | BCAM         | TK. Ctrl        | Work Area     | Work Area   | Work Area    | Work Area    | Work Area    | Work Area |

| 15         | Rack Pwr     | TK. Ctrl        | Work Area     | Work Area   | Work Area    | Work Area    | Work Area    | Work Area |

|            |              |                 | <             | Passageway> |              |              |              |           |

|            |              |                 |               |             |              |              |              |           |

### CMS各种板数量

Table 1.2: CMS Phase-2 detector projected data links, ATCA back-end configuration and event size summary. Data are obtained from the technical design reports wherever possible. Average throughput estimated from event size assuming 750 kHz Level-1-accept rate.

| Subdetector        | Front-end                | Sub-event | Back-end | Back-end | Average           | Notes         |

|--------------------|--------------------------|-----------|----------|----------|-------------------|---------------|

|                    | lpGBT links <sup>a</sup> | size (MB) | boards   | crates   | throughput (Tb/s) |               |

| Outer Tracker      | 13 000                   | 1.15      | 216      | 18       | 6.90              | (b)           |

| Track Trigger      |                          | 0.01      |          | 18       | 0.06              |               |

| Inner Tracker      | 1 260                    | 1.44      | 24       | 4        | 8.64              | (°)           |

| MIP Timing Det BTL | 1 000                    | 0.02      | 11       | 1        | 0.14              |               |

| MIP Timing Det ETL | 438                      | 0.04      | 5        | 1        | 0.22              |               |

| ECAL Barrel        | 10 000                   | 1.58      | 108      | 12       | 9.49              |               |

| HCAL Barrel        | other                    | 0.24      | 18       | 2        | 1.45              |               |

| HCAL - HO          | legacy                   | 0.03      | -        | 1        | 0.18              | $\binom{d}{}$ |

| HCAL - HF          | other                    | 0.06      | -        | 1        | 0.36              | (d)           |

| Endcap CALO        | 8 000                    | 2.00      | 108      | 9        | 12.00             |               |

| Endcap CALO TPG    | 9 000                    | 0.20      | 144      | 12       | 1.50              |               |

| muon DT            | 3840                     | 0.13      | 84       | 8        | 0.78              |               |

| muon CSC           | other                    | 0.20      | -        | 2        | 1.20              | (d)           |

| muon GEM - GE1/1   | other                    | 0.002     | -        | 1        | 0.01              | (d)           |

| muon GEM - GE2/1   | 144                      | 0.001     | 8        | 1        | 0.01              |               |

| muon GEM - ME0     | 216                      | 0.12      | 12       | 1        | 0.71              |               |

| muon RPC           | other                    | -         | -        | -        | -                 | (e)           |

| Level1             |                          | 0.15      | 120      | 14       | 0.90              | (f)           |

| Total              |                          | 7.4       | >858     | >106     | 44                |               |

• 不同的文献来源对比, 机箱总数和目前估计也在相似数量

### 说明

- · 本PPT所有的计算都没有加安全因子

- 共计数据机箱约100个,每个机柜3个机箱,共约34个数据机柜;

- 共计低压电源机箱约534个,每个机柜10个机箱,共约54个电源机柜

- Muon系统给电源机箱统计带来很大不确定性

- 共计探测器高压机箱164个,每个机柜3/4个机箱,共约42高压电源机柜

- · 每个低压机柜对应1个AC-DC电源机箱,约为130个,占26个机柜

- · 以上数值未考虑备份、未来升级空间以及其他探测器方案变动带来的不确定性,特别是触发算法可能进一步要求机箱分配与探测器排布相映射,将降低机箱插件占用率。如果按照最小值×1.5的裕量来考虑,共需数据机柜51个,低压电源机柜81个,探测器高压机柜63个,AC电源机机柜39个,触发机柜15个(共约249机柜),整体规模即同CMS的不到210机柜规模相当,考虑机柜之间散热后(彼此间隔1.5m,考虑机箱厚度按pitch 2m),电子学间的空间整体也应在相同规模(粗略估计10行16列2层容量320机柜,20m×32m×2层)

# • backup

### **Requirement from Sub-Detector**

|                            | Vertex                                                | Pix(ITKB)                                                          | Strip (ITKE)                                              | TOF (OTK)                                                          | TPC                                                                     | ECAL                                                                                    | HCAL                                                                                    |

|----------------------------|-------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Channels per chip          | 512*1024<br>Pixelized                                 | 512*128<br>(2cm*2cm@34u<br>m*150um)                                | 512                                                       | 128                                                                | 128                                                                     | 8~16                                                                                    | 8~16                                                                                    |

| Ref. Signal processing     | XY addr + BX<br>ID                                    | XY addr + timing                                                   | Hit + TOT + timing                                        | ADC+TDC/TOT+TOA                                                    | ADC + BX ID                                                             | TOT + TOA/<br>ADC + TDC                                                                 | TOT + TOA/<br>ADC + TDC                                                                 |

| Data Width<br>/hit         | 32bit<br>(10b X+ 9b Y<br>+ 8b BX + 5b<br>chip ID)     | 48bit<br>(9b X+7b Y<br>+14b BX + 6b<br>TOT + 5TOA +<br>4b chip ID) | 32bit<br>(10b chn ID +<br>8b BX + 6b TOT<br>+ 5b chip ID) | 40~48bit<br>(7b chn ID + 8b BX<br>+ 9b TOT + 7b<br>TOA+5b chip ID) | 48bit<br>(7b chn ID + 8b<br>BX + 11b chip<br>ID + 12b ADC<br>+ 10b TOA) | 48bit<br>(8b BX+ 10b ADC<br>+ 2b range + 9b<br>TOT + 7b TOA+ 4b<br>chn ID + 8b chip ID) | 48bit<br>(8b BX+ 10b ADC +<br>2b range + 9b TOT +<br>7b TOA+ 4b chn ID +<br>8b chip ID) |

| Data rate / chip           | 1Gbps/chip@<br>Triggerless@<br>Low LumiZ<br>Innermost | 640Mbps/chip<br>Innermost                                          | Avg.<br>1.01MHz/chip<br>Max.<br>100MHz/chip               | Avg:<br>26kHz/chip @ z pole<br>Max: 210kHz/chip<br>@z pole         | ~70Mbps/modu<br>le<br>Inmost                                            | <4.8Gbps/module                                                                         | <4.8Gbps/module                                                                         |

| Data<br>aggregation        | 10~20:1,<br>@1Gbps                                    | 1. 1-2:1 @Gbps;<br>2.<br>10:1@O(10Gbp<br>s)                        | 1. 10:1<br>@Gbps<br>2. 10:1<br>@O(10Gbps)                 | 1. 10:1<br>@1Mbps<br>2. 10:1<br>@O(10Mbps)                         | 1. 279:1<br>FEE-0<br>2. 4:1<br>Module                                   | 1. 4~5:1 side brd<br>2. 7*4 / 14*4 back<br>brd @ O(10Mbps)                              | < 10:1<br>(40cm*40cm PCB –<br>4cm*4cm tile – 16chn<br>ASIC)                             |

| Detector<br>Channel/module | 2218 chips<br>@long barrel                            | 30,856 chips<br>2204 modules                                       | 22720 chips<br>1696<br>modules                            | 41580 chips<br>1890 modules                                        | 258 Module                                                              | 1.1M chn                                                                                | 6.7M chn                                                                                |

| Data Volume before trigger | 2.2Tbps                                               | 2Tbps                                                              | 22.4Gbps                                                  | 1Gbps                                                              | 18Gbps                                                                  | 164.8Gbps                                                                               | 14.4Gbps                                                                                |

## A summary of FEE power

|                      | Vertex                                  | Pix Tracker                          | TOF                         | Si Strip                         | TPC                   | DC                           | ECAL                           | HCAL                           |

|----------------------|-----------------------------------------|--------------------------------------|-----------------------------|----------------------------------|-----------------------|------------------------------|--------------------------------|--------------------------------|

| Detector for readout | CMOS<br>Sensor                          | HVCMOS                               | Strip-<br>LGAD              | Si Strip                         | Pixel<br>PAD          | Drift<br>Chamber             | SiPM                           | SiPM                           |

| Main Func<br>for FEE | X+Y                                     | XY + nsT                             | X +<br>50psT                | X                                | E + nsT               | Analog<br>Samp.              | E + 400psT                     | E + 400psT                     |

| Channels<br>per chip | 512*1024<br>Pixelized                   | 768*128<br>(2cm*2cm@2<br>5um*150um)  | 128                         | 128                              | 128                   | -                            | 16                             | 16                             |

| Voltage@c<br>hip     | 1.8V@180n<br>m<br>(1.2V@65nm<br>future) | 1.2V@55nm<br>(HVCMOS<br>Pixel)       | 1.2V@55<br>nm (TDC)         | 1.2V@13<br>0nm (电<br>压统一、<br>便宜) | 1.2V@65<br>nm         | ±3.3V商用<br>→1.2V@G<br>aAs?   | 1.2V@55nm<br>(TDC)             | 1.2V@55nm<br>(TDC)             |

| Power@ch<br>ip       | <200mW/cm<br>2<br><0.8W/chip            | <200mW/cm<br>2<br><0.8W/chip<br>尚无设计 | <40mW/c<br>h<br><5W/chip    | 5mW/ch<br>640mW/c<br>hip         | 35mW/ch<br>ip         | ?                            | 20mW/chn<br>160~320mW<br>/chip | 20mW/chn<br>160~320mW<br>/chip |

| chips@mo<br>dule     | 10~20:1                                 | <10:1<br>尚无设计                        | 10:1                        | 10:1                             | 279:4:1               | 需FPGA、<br>ADC供电,<br>可统一1.2V? | 112~280:1<br>侧板无DCDC<br>仅电容    | ~10:1                          |

| Power@m<br>odule     | 8~16W<br>@1.8V<br>4.4~8.9A              | 8~16W<br>@1.8V<br>4.4~8.9A           | 50W (???)<br>@1.2V<br>41.7A | 6.4W<br>@1.2V<br>0.53A           | 40W<br>@1.2V<br>33.3A |                              | 44.8W<br>@1.2V<br>37.3A        | 3.2W<br>@1.2V 2.6A             |

| Other                | 辐照TID<br>7.3Mrad/y @<br>HLumi Z         |                                      | 需进一步<br>优化                  |                                  |                       | On FPGA                      | 可能SiPM可<br>共用60V中压<br>电源       | 可能SiPM可<br>共用60V中压<br>电源       |