## 2024年度考核报告

严雄波

电子学组

2024.11.22

### 岗位职责

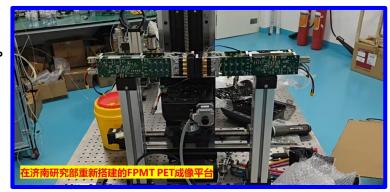

- FPMT PET成像平台读出电子学研究

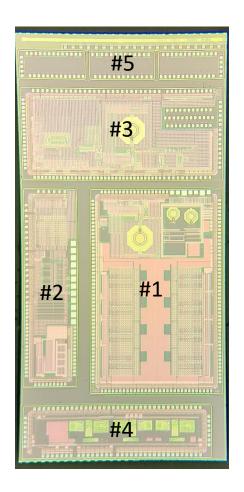

- · ASIC设计(4家合作单位)

- #1: 8通道高精度TDC (10ps)

- # 2: 单通道TDC模块验证

- #3: TDC延迟单元(5ps)

- #4: 14 bit Pipelined-SAR ADC

- #5: 55nm工艺抗辐照研究

- 芯片测试系统设计

- CEPC 径迹探测器 TDR- elec

### 项目1-FPMT PET成像平台读出电子学研究

(宁哲,严雄波,胡俊,梁泽洪,江晓山)

- 项目目标:用FPMT实现切伦科夫光TOF-PET,系统SPE信号时间分辨~50ps,电子学采用"放大甄别+FPGATDC"方案,时间分辨好于10ps。

- 本人贡献:完成放大甄别ASIC改进版设计测试,实现FPGA TDC原理性方案验证,解决和优化模拟前端的问题。

- 已成功实现模体成像

#### 提升成像平台性能路径总结

- □ 进一步提高MCP-PMT的TTS<sub>SPE</sub>至30ps(FWHM): <50ps

- ▶ 优化结构、实现PbF₂窗

- □ 将MCP-PMT的TTS<sub>SPE</sub>由~50ps提升至<30ps(sigma): ~100ps (主峰) <sub>24.5</sub>

- ✓ 中心阳极已经实现TTS<sub>SPE</sub> <30ps(sigma) <sub>23.11</sub>

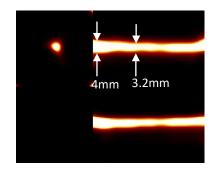

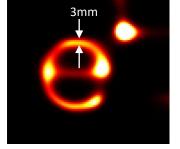

- ✓ 利用MCP-PMT实现对于结构模体的初步成像 24 10

- > 解决射线与MCP作用占比高问题: 实现系统时间谱直接分辨 <100ps

- □ 提高FPMT一致性+电子学优化 (阈值+基线): ~150ps

- ✓ 已实现逐通道基线标定+阈值调节 23.11

- □ 加入幅度判选, ~280ps→~200ps (已实现中心阳极~150ps) <sub>23.8</sub>

- □ 解决多板时钟同步问题,~500ps→~280ps (已实现217ps) 23.4

平台双通道时间分辨~500ps (最初)

读出电子学系统

68Ge棒源成像

模体成像

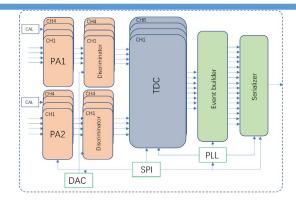

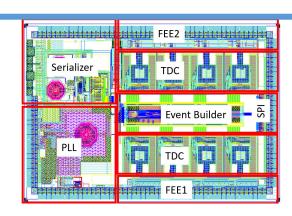

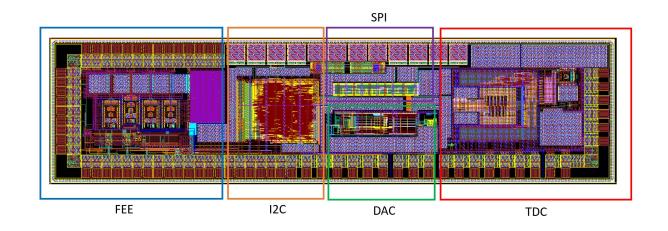

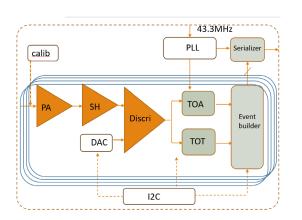

#### 项目2 Chip1-FPMROC\_VO芯片

()

(严雄波,李筱婷,叶竞波,合作单位)

- 项目目标:实现多通道TDC ASIC集成,时间分辨好于10ps。

- 芯片流片已完成,测试准备中

- 通道数: 8

- 2种前放方案

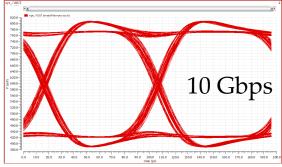

- 5.12 GHz 时钟,10 Gbps 串行器

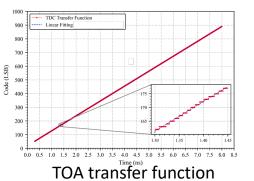

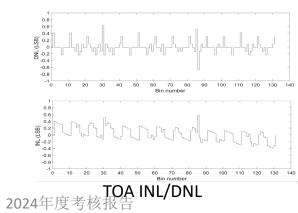

| Parameter              | FPMROC Simulation |  |

|------------------------|-------------------|--|

| FEE                    | < 5 ps            |  |

| TOA/TOT LSB            | 13.0 ps           |  |

| TOA range              | 0.7ns-24.3ns      |  |

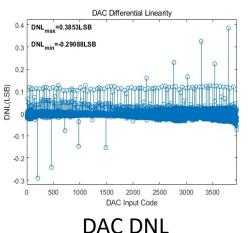

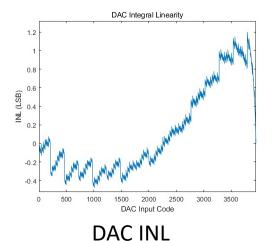

| TOA INL                | <0.7LSB           |  |

| TOA DNL                | <0.6LSB           |  |

| TOT range              | 200ps~3.25ns      |  |

| Core Power Consumption | 40mW/ch           |  |

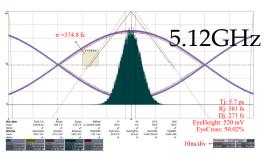

PLL jitter<460fs

Serializer eye diagram

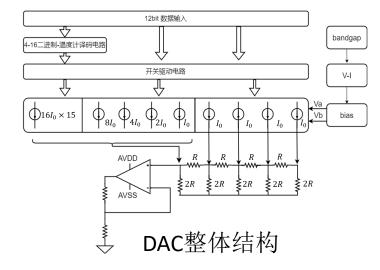

### Chip2-单元模块测试芯片

(严雄波,李筱婷,叶竞波,合作单位)

- 含CEPC 单元模块功能测试和验证

- Preamp, Discriminator--LGAD前端模拟电路

- I2C Slave--CEPC ASIC configuration

- 12 bit DAC--Channel threshold and In-chip Calibration

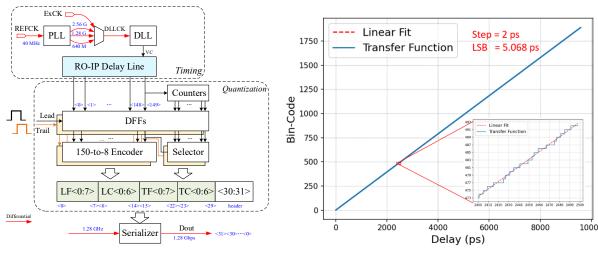

#### Chip 3-TDC ASIC方案2-DLL-Base TDC Core

(李筱婷,严雄波,王传烨,叶竞波)

#### ▶实现更高精度TDC核心模块

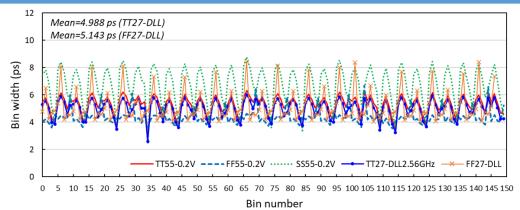

- DLL提供控制结合内插实现最小分辨~5.2ps

- ▶开展高精度/多通道低功耗TDC芯片的研究

- ▶高精度---游标型: 目标 2ps

- ➤低功耗---事例驱动型: 128通道, 30ps

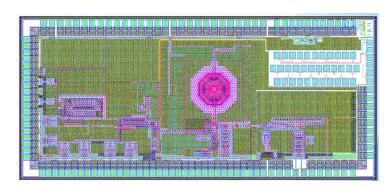

layout

#### 仿真bin size

DLL-Based TDC core scheme

转换曲线(0-10ns)

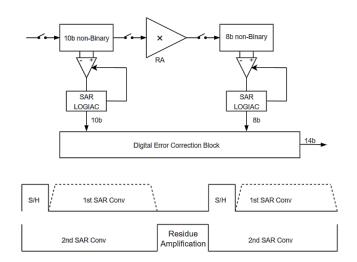

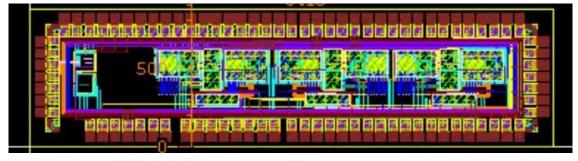

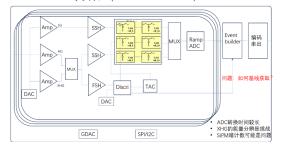

#### Chip4-Pipelined SAR ADC

(杨苹,严雄波,李筱婷,叶竞波)

ADC原理框图和时序

FFT analysis results(fin=40M and fs=100M)

- ▶ 适用于多通道集成,为CEPC SiPM读出芯片数字化提供解决方案

- ▶ 低功耗ADC设计,异步时钟节省功耗

| Supply           | 1.2V    | SNR  | 76.0dB                   |

|------------------|---------|------|--------------------------|

| Resolution Ratio | 14 bit  | SFDR | 85.0dB                   |

| Input Range      | 0∼2.4V  | SNDR | 75.4dB                   |

| Sampling Ratio   | 100Msps | ENOB | 12.23bit                 |

| Power            | 11.8mW  | Area | $650 \times 380 \mu m^2$ |

ADC芯片版图

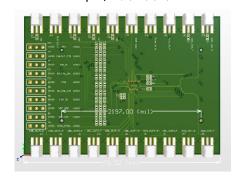

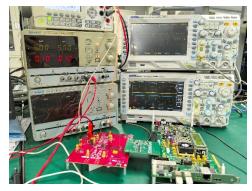

### ASIC测试系统设计 (严雄波, 李筱婷, 朱秋生, 汪鑫, 梁泽洪, 梅文, 叶竞波)

- 制定测试方案

- 组织测试系统设计团队

- 完成5种芯片测试系统设计,正在打线

- 测试系统采用子母板形式,调试完成

- 母板: 提供通用测试功能

- 电压转换、数字电平转换、ADC、DAC、 FPGA数据接口

- 测试固件和软件基本完成

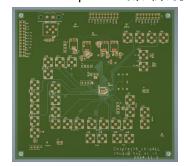

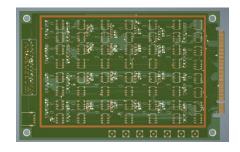

Chip 1,2 测试系统

Chip 1 测试板

Chip 2 测试板

Chip4 ADC 测试系统

Chip 3 测试板

Chip 5 测试板

#### 项目3-CEPC 径迹探测器TDR方案研究和撰写

严雄波,魏微,叶竞波,常劲帆,胡俊,赵梅,李筱婷,张颖,李怀申,其他tracker项目组成员

#### ▶ 径迹探测器电子学系统负责人

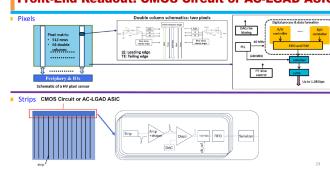

- ▶ 负责LGAD、CMOS Pixel、CMOS Strip前端电子学方案

- ▶ 参与径迹系统讨论例会,明确电子学系统主要读出框架, 前端参数汇总

- ▶ 参加各子探测器例会,推动各子探测器分析并组织收集 电子学系统关键接口,供电,数据,排布

- ▶ 参与电子学组例会,讨论确定子探测器前端电子学读出 方案及ASIC初步方案

- ▶ 联系所外合作单位,扩大合作规模

#### ▶量能器 SiPM读出ASIC、外径迹LGAD ASIC负责人

- ▶ 参与探测器方案讨论,收集量探测器信息

- ▶ 研究制定方案,组织研究队伍,制定计划

- ▶ 定期开展组会

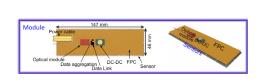

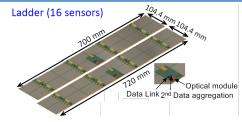

LGAD readout Chip

SiPM ASIC方案 (0.1~3000MIPs)

OTK ladder

#### Front-End Readout: CMOS Circuit or AC-LGAD ASIC

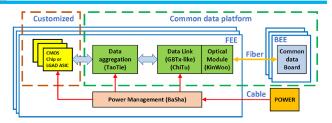

#### **Silicon Tracker Common Electronics**

#### 学术交流及经费情况

- 学术交流

- 江门合作组会及workshop,微电子学年会,核电子学年会,TWEPP,CEPC workshop

- 文章(已发表2篇)

- Reliability studies of the custom-designed front-end and ADC chips used for JUNO large photomultipliers electronics, 通讯, 2024.1

- A 5.12-Gbps serializer circuit for front-end fast readout electronics of silicon pixelated detectors, 合作, 2024.6

- 文章 (审稿中, 4篇)

- A ring-oscillator-based 5.2-ps bin-size integrated circuit for time measurements,通讯, JINST审稿中

- An ASIC for ToF-PET application with MCP-PMTs, 通讯, JINST审稿中

- A 64-Channel Precision Time-to-Digital Converter with Average 4.77 ps RMS Implemented in a 28 nm FPGA,通讯,TNS审稿中

- A 14-bit 100 MS/s Two-Step Split SAR ADC using low-power high-linearity RA without any internal phase compensation and in-stage redundancy technology, 合作, JINST审稿中

- 专利

- 一种水下探测设备的包装结构,第3发明人,已公开

- 一种延迟链型定时核心电路,第2发明人,审查中

- 项目

- 在研其他项目

- 面向FPGA的USB3.2芯片的关键技术研究,52万,主要人员

- 中科院科研仪器设备研制项目-基于非像素晶体的三维位置分辨伽马探测系统研制,272万,主要人员

- 科技部重大仪器-紫外光电子谱分析仪研制与应用,360万,主要人员

- 2023年申请

- 重点项目--申请1项,未获批

- 指导博后/研究生:

- 1名博后, 1名博士研究生, 2名硕士研究生, 2名联合培养硕士

### 公共服务

- 总支组织委员/第二支部书记

- 党员党费收缴,活动经费管理

- 党员组织关系维护,党员信息更新,关系转入转出

- 制定支部计划

- 配合党委组织人员参与选举、竞赛、学习、演出等活动

- 参加党委组织的研讨会,贯彻落实相关精神、文件

- 带领青年理论学习小组定期参与党委举办相关活动

- 组织党员学习,每月一次"主题党日"

- •参与期刊审稿和毕业论文评审、答辩

### 存在问题

- · ASIC研发任务多,时间紧,设计人员不足

- 系统级人员设计经验不足

- 复杂芯片的设计方法有待提高

- 经费争取欠佳

2024年度考核报告

12

### 下一步计划

- ➤CEPC TDR撰写

- ▶CEPC SiPM读出芯片设计,2025年底完成原型验证

- ➤TDC ASIC研究:

- ▶ CEPC LGAD应用 -多通道、低功耗

- ▶TOF-PET应用-高精度<10ps,多通道扩展

- ▶前瞻性研究: <2ps

- ▶5款芯片的测试与改进

# 谢谢!