中國科學院為能物招加完所 Institute of High Energy Physics Chinese Academy of Sciences

# Preliminary consideration of the electronics room requirement with current detector design

#### Wei Wei

#### On behalf of the Elec-TDAQ system of the CEPC Ref-TDR team

#### IHEP, CAS

2024-09-27 CEPC Day

#### Outline

- Motivation

- Considerations on data link / power / HV according to the current

- Key parameters to calculate the cabling and crates

- Detailed calculation for each sub-detector

- Summary of the cabling and crates

- Comparison with the CMS counting room

- Rough estimation of the electronics-TDAQ room

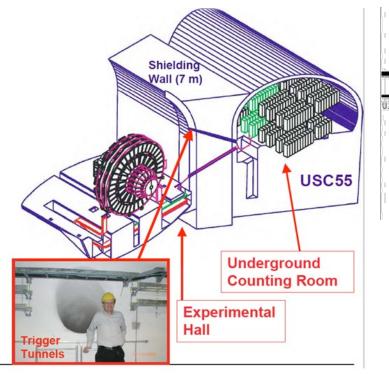

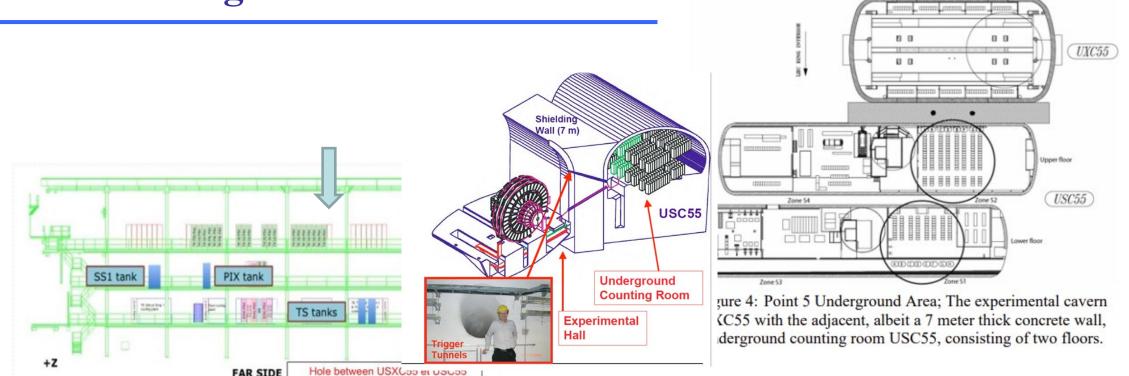

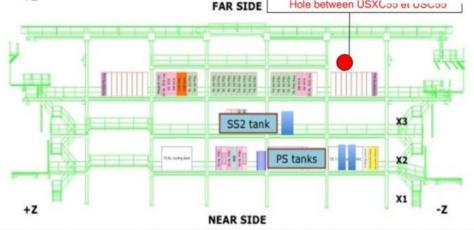

#### **Motivation – an example from CMS**

+Z

- For the floorplan of the detector hall, to estimate the space requirement, and location preference

- Also connected to the installation strategy

X1

NEAR SIDE

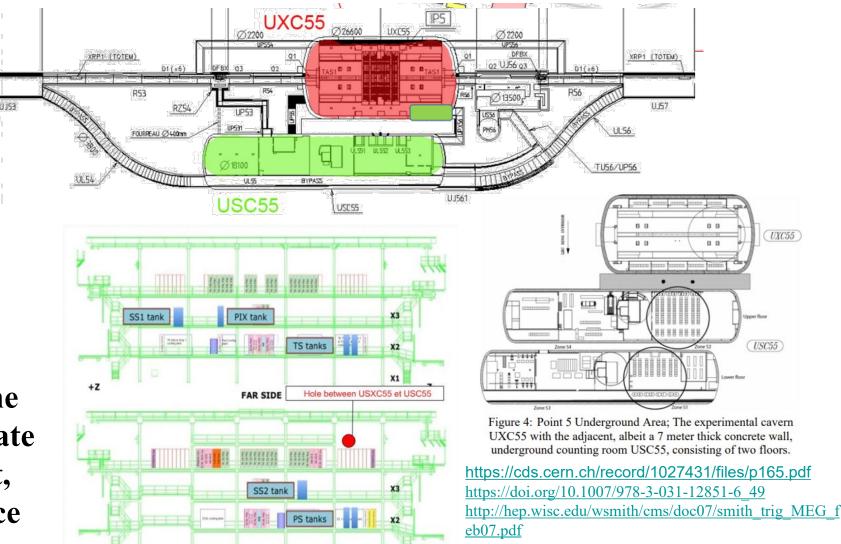

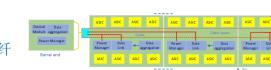

#### **Global framework of the Elec-TDAQ system**

**Common platform**

- Common subsystems (data buffering, aggregation, ٠ transmission; powering)

- Det. specific ASICs waiting for detector final choices. ٠

- A common BEE hardware, configurable for individual ٠ subsystems.

- TDAQ interface is (probably) only on BEE ٠

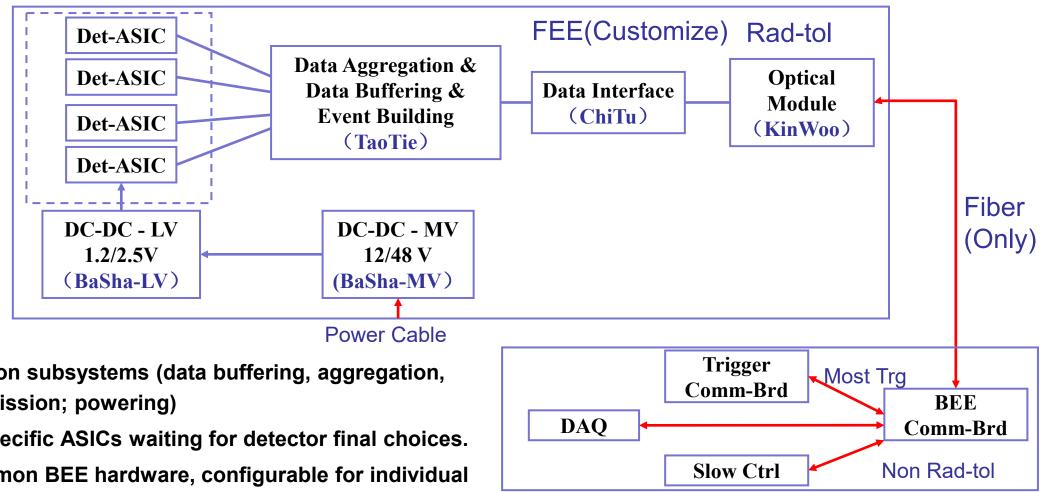

#### **Consideration according to the detector design**

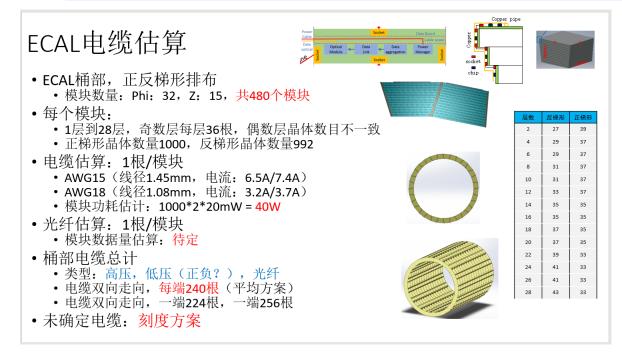

## An example of sub-detector consideration (ECAL)

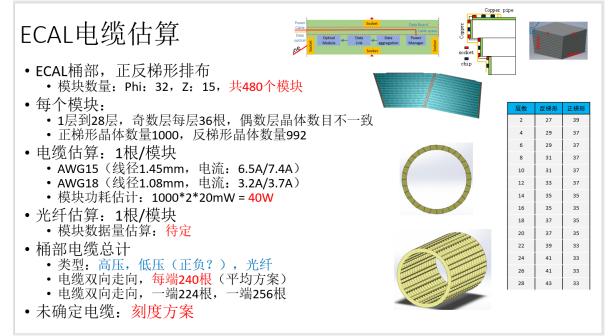

- The overall detector design: ~480 Module (Dual-trapezium scheme), ~1000 bar/module

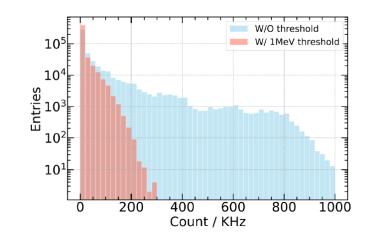

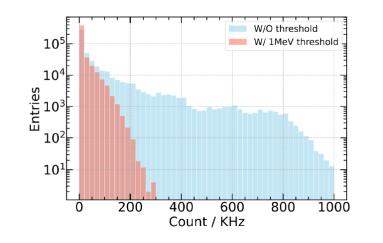

- Current bkgrd estimation: avg. event rate 100kHz / crystal bar w/ threshold; Data width 48bit/event (current ASIC scheme)

- @Dual readout each crystal bar, total data rate:

1000\*100kHz\*48bit\*2ends=9.6Gbps, not possible for 1 fiber for each module, <u>at least 2 fibers for each module</u>

- For max. bkgrd rate@300kHz@Higgs, also needs enough room

- For Z pole, bkgrd will be much higher, also needs extra room

## An example of sub-detector consideration (ECAL)

- Data Link:

- Fibers: 480\*2=960, -> 60 BEE Brds, 6 crates

- Power:

- ASIC: 15mW/ch, each module 1000\*2\*15mW=30W

- > Within the capability of DC-DC power module

- Data Link + Optical Power: 1W each

- Total Power: 31W/0.85\*480=17.5kW

- **Efficiency of the DC-DC: 85%**

- Power chn 100W/chn, each module per power cable: 480 power chn -> power crates 10

- HV:

- Sch 1: one HV chn for each module, (limitedly) compensated for each SiPM in ASICs

- HV channels = module number = 480, -> 2 HV crates

- Alt sch2: HV chn for each SiPM? Too many channels & too large control data volume (×)

- Alt sch3: HV chn for sub-region of a module, to compensate the temperature gradient

- > Maybe much optimized than sch1, but rely on the detector simulation

#### Note for the calculation

- Avg. & Max background rate both are important

- Max bkgrd rate to calculate the room for the data rate

- Avg bkgrd rate to calculate the total data rate for the electronics –TDAQ interface

- Detailed detector design, including the module vs. chip, is necessary for the electronics cabling, powering and HV scheme

- Chip on module to evaluate electronics readout scheme (data link, power, aggregation)

- Overall detector design to evaluate the cabling, HV and crate channels

- According to the current electronics design, most detector module following the "1 fiber + 1 Power" manner

- Most module data rate at the level of Gbps, a fiber channels @10Gbps level is proper

- Although the room for a power channel at the module level is large, current scheme not consider power channel merge

- Otherwise needs extra power aggregation board on detector, means extra room and increasing difficulty for Mechanics

- Several detector with enough space (esp. endcaps) with very low power, power channel merge can still be considered

9

#### Main parameters for the room calculation – Data Crates

S

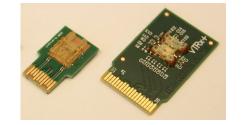

- Optical Link

- By using MTX interface for fibers, multiple fiber channels can be integrated in small unit

- ➤ Can be 1Rx + 4Tx as a normal design

- Each Tx channel at 10Gbps rate, with 8b10b protocol, and the max valid data rate to be 8Gbps

- Major constraint for the detector module

- If module data rate too high (>8Gbps valid data), multiple Tx fiber channels should be used, while the size of the optical module unchanged

- Crates for data

- The common BEE Board considered with 16 optical channels, each @10Gbps/Link

- BEE Board to be designed following the  $\mu TCA$  standard

- μTCA crate height 9U, total room for 14 cards

- > 2 Ctrl cards for each crate, 1 TTC card (clocking), 1 reserved card

- > 10 valid slots for BEE boards in each data crate

- Racks for data

- Height of a rack 42U

- Height for the heat dissipation 2U each

- Reserve some room for the possible Switch to DAQ

- Max 3 crates in each Data Rack (= 30 BEE Boards = 480 optical channel)

VTRx+ 4Tx + 1Rx Array Optical Module

#### Main parameters for the room calculation – Power Crates

- MV(110V DC to 48V DC) Power Crate & Racks:

- In the electronics room, near the Data Racks

- A crate with a height 3U

- **>** Type1: 48 channels, with the capability of 100W output for each channel

- **>** Type2: 96 channels, with the capability of 40W output for each channel

- Concerning the room for heat dissipation, a 42U Power Rack for 10 Power Crates is proper

- Pwr-HV (380V AC to 110 DC) Power Crate & Racks:

- Power for the MV Power Racks, may be on the ground or far from radiation

- A crate with a height 6U & total power of 60kW~70kW for a total 10 channels

- A rack for 5 power crates (6U + 2U cooling)

#### Main parameters for the room calculation – Det-HV Crates

- Detector HV crates & racks

- Usually the power of the detector HV source is low, channel density is the major constraint

- (Ref. from the Det-HV crates provided for ATLAS-HGTD) a crate with a height 8U with 14×16=224 channels, independent tuning for each channel

- 2U height for heat dissipation for each crate

- A 42U Det-HV Rack can hold 4 Det-HV Crates

- If SHV is needed (as for TPC), SHV-connector is larger, height of the crate -> 10~12U, and a Det-SHV Rack will be for 3 Det-SHV crates

#### **VTX-Data Link**

From Zhijun

| _ |    |

|---|----|

| 1 | La |

| 2 | VT |

| 3 | VT |

| 4 | VT |

| 5 | VT |

| 6 | VT |

| 7 | VT |

|   |    |

- В С D Α Hit density Hit density Safe Cluster (Hits/cm2/BX) (kHits/cm2/s) factor size BXRate (Hz) ayer 1.34E+061.5 TX-1 (Higgs) 0.65 870 3 1.5 TX-2 (Higgs) 0.43 580 1.5 TX-3 (Higgs) 0.09 116 TX-4 (Higgs) 0.08 110 1.5 TX-5 (Higgs) 0.05 70 1.5 1.5 TX-6(Higgs) 0.05 68

- VTX scheme: Inner 4 layers stitching, with 1 typical double-sided ladder (layer 5&6)

- Bkgrd rate @50MW @Higgs with safety factor 1.5

- Assume RSU@stitching = ladder chip = 1024\*512 matrix, then data rate for the innermost layer for a "chip" is 2Gbps, other layers according the bkgrd ratio

- **Inner 2 layers needs 2 fiber chns for <u>each row</u>, due to the high data rate**

- possible to merge into less optical MTX interfaces

• In total 88 fibers = 6 BEE Brd = 1 Data Crate

| Layer | Comment      | Data Rate/chip | Chips/Row | Data rate/row | Rows   | Links@10Gbps          |

|-------|--------------|----------------|-----------|---------------|--------|-----------------------|

| 1     | Stitching    | 2Gbps          | 8         | 16G           | 2*2=4  | 2*4=8 (2 fiber chns)  |

| 2     | Stitching    | 1.3Gbps        | 12        | 15.6G         | 3*2=6  | 2*6=12 (2 fiber chns) |

| 3     | Stitching    | 0.27Gbps       | 16        | 4.3G          | 4*2=8  | 1*8=8                 |

| 4     | Stitching    | 0.25Gbps       | 20        | 5G            | 5*2=10 | 1*10=10               |

| 5     | Ladder-side0 | 0.16Gbps       | 29        | 4.64G         | 25     | 1*25=25               |

| 6     | Ladder-side1 | 0.16Gbps       | 29        | 4.64G         | 25     | 1*25=25               |

#### **VTX-Power**

| Layer | Comment      | Power/chip | Chips/Row | Power<br>/row | Rows   | Chip Power of<br>Layers | Total Power/Layer<br>(Chip+Link) *1.18 |

|-------|--------------|------------|-----------|---------------|--------|-------------------------|----------------------------------------|

| 1     | Stitching    | 200mW      | 8         | 1.6W          | 2*2=4  | 6.4W                    | (6.4+4) *1.18=12.2                     |

| 2     | Stitching    | 200mW      | 12        | 2.4W          | 3*2=6  | 14.4W                   | (14.4+6) *1.18=24                      |

| 3     | Stitching    | 200mW      | 16        | 3.2W          | 4*2=8  | 25.6W                   | (25.6+8) *1.18=39.5                    |

| 4     | Stitching    | 200mW      | 20        | 4W            | 5*2=10 | 40W                     | (40+10) *1.18=58.8                     |

| 5     | Ladder-side0 | 200mW      | 29        | 5.8W          | 25     | 145W                    | (145+25) *1.18=200                     |

| 6     | Ladder-side1 | 200mW      | 29        | 5.8W          | 25     | 145W                    | (145+25) *1.18=200                     |

- For simplicity, assume the power of Unit(RSU/Chip) is the same 200mW(40mW/cm2 \* 2.6cm\*1.6cm)

- Main contribution of power: analog static power + data link, not varying with bkgrd rate

- Extra cost by using optical: fixed 1W each set

- 0.75W for Data Interface & 0.25W for 1 Rx+4Tx VTRx

- Efficiency of BaSha DC-DC is 85% = extra efficiency cost of DC-DC 18% (1÷85%=118%)

- Total power: 449.8W

- 16 power channels each layer for 1~4, each chn for a semi-; 2 chn for each ladder in 5/6 layer, 50 chn in all

- Power will be provided from both ends for long barrel

- 66 power channels = 2 power crate

- Very likely to be merged due to the limited room for VTX

#### **VTX-Det-HV**

- There is no actual need for "High Voltage"

- However, may be the only detector to use negative voltage for sensors

- Depend on R&D, ranges < -10V</p>

- Not cost-effective to developed a dedicated power module for VTX

- Can be treat as a "Det-HV"

- Det-HV Crates (similar to VTX Power Crates):

- 16 HV channels each layer for 1~4, each chn for a semi-; 2 chn for each ladder in 5/6 layer, 50 chn in all

- HV will be provided from both ends for long barrel

- 66 HV channels = 1 Det-HV crate

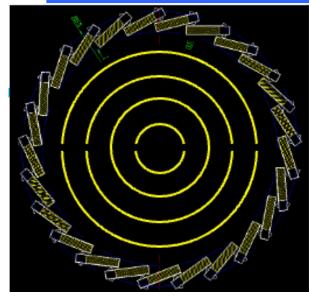

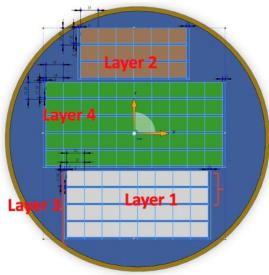

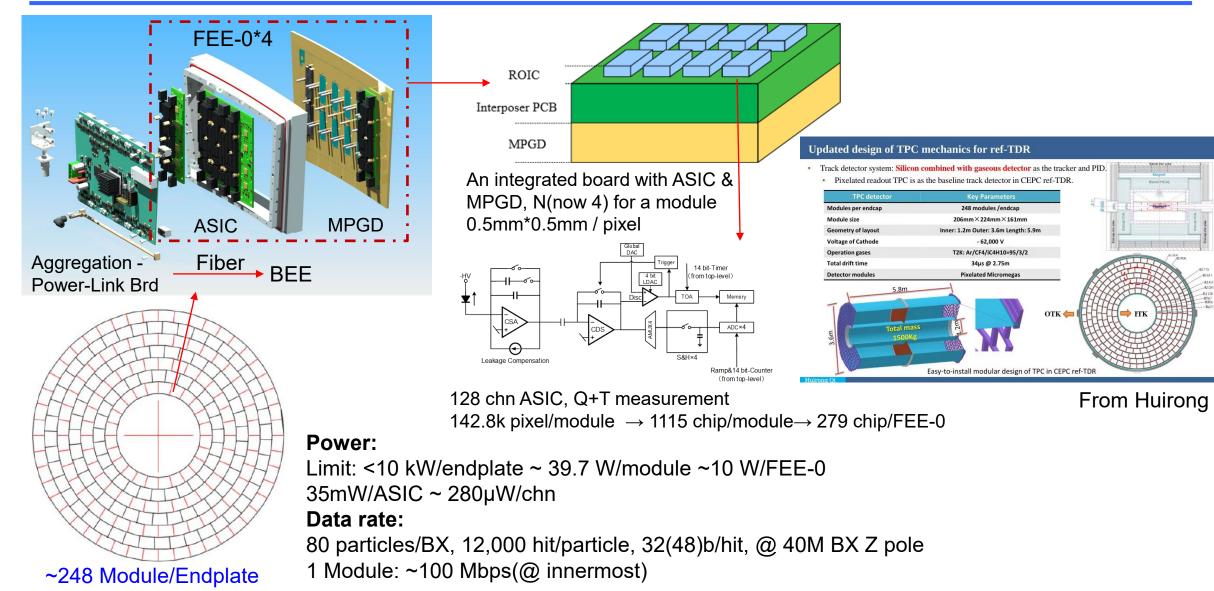

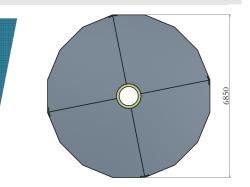

#### **Preliminary readout scheme of Pixel TPC**

#### **TPC—Data Link**

16

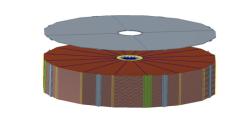

- Module number: 248 \* 2 endcap=496 modules ullet

- **Data rate concerning bkgrd rate:** ۲

- 30Mbps~100Mbps per module, avg. @ 70Mbps, much less than the max capability of optical

- **Data Link:** ullet

- Each module per fiber link, w/o inter-module data aggregation, to maximize the reliability

- Not too much cost variation for the BEE

- The alternative scheme by data aggregation is also listed below

| Sch. | Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data Rate/module                                                                                                                                                                                 | Module/Fiber | Total Fiber         | Total BEE                              | Total crate                                                                       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|----------------------------------------|-----------------------------------------------------------------------------------|

| 1    | 248*2=496                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100Mbps                                                                                                                                                                                          | 1            | 496                 | 248/16*2=32                            | 4                                                                                 |

| 2    | 248*2=496                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100Mbps                                                                                                                                                                                          | 16           | 246/16*2=32         | 3                                      | 1                                                                                 |

|      | E<br>150<br>100<br>50<br>-100<br>-150<br>-200<br>-150<br>-100<br>-50<br>0<br>50<br>-100<br>-50<br>0<br>-150<br>-100<br>-50<br>0<br>50<br>100<br>-150<br>-100<br>-50<br>0<br>50<br>100<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>-150<br>- | 10 <sup>4</sup> mm bins 3000<br>10 <sup>4</sup> mm bins 3000<br>10 <sup>3</sup> 2000<br>10 <sup>2</sup> 1000<br>10 <sup>2</sup> 1000<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | http<br>http | os://doi.org/10.108 | cord/1543486/files<br>8/1748-0221/12/0 | / <mark>LCD-Note-2013-005.pdf</mark><br>7/P07005<br>article/pii/S0168900216305381 |

y [cm]

#### TPC—Power & HV

- The power spec for each endcap of TPC is 10kW

- Avg. power for each module is 40.3W

- Concerning the cost of data link 1W, total power per module ~42W

- Suitable to provide power for each module with an independent power channel

- Max. the flexibility for installation and reliability; min. the complexity in case that the power has to be distributed between modules

- Power crates

- In total 496 module = 496 channels = Power Crates 6

- > Assuming independent distribution for the two endcaps

- Det-HV crates

- Requirement for independent tuning for each module, has to be 1 chn for each module

- In total 496 module = 496 channels = Power Crates 4

- > Assuming independent distribution for the two endcaps

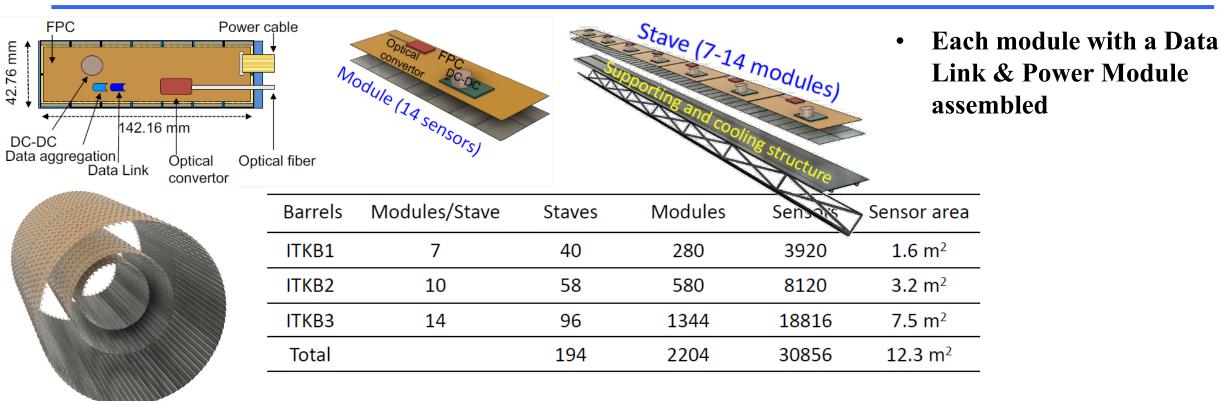

#### **ITK——Detector, stave & module**

42.76 mm

| Endcap                  | 1 (per Sector) | 2        | 3         | 4         | Total   |

|-------------------------|----------------|----------|-----------|-----------|---------|

| Ladder Type             | 6              | 8        | 15        | 12        | 18      |

| Ladder Number           | 7              | 10       | 18        | 15        | 1600    |

| Chip Number             | 48             | 98       | 260       | 236       | 20544   |

| Active Area (mm^2)      | 20181.03       | 42796.32 | 116080.28 | 106081.77 | 9.12e6  |

| Module Area (mm^2)      | 23184          | 47334    | 125580    | 113988    | 9.92e6  |

| Power Consumption (W)   | 46.368         | 94.668   | 251.16    | 227.98    | 1.98e4  |

| Avg. Hit Rate (Hz/mm^2) | 3.9e2          | 1.6e3    | 8.9e2     | 2.4e2     | -       |

| Data Rate (Hz)          | 2.89e8         | 2.42e9   | 3.58e9    | 8.75e8    | 2.29e11 |

#### ITK——Data Link (Barrel)

|                               | HVCMOS Pixels (Barrel)                                                 | CMOS Strips (Endcap)                                                       |  |  |

|-------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| Pixel Size (Strip Pitch Size) | $34 	imes 150 \ \mu m^2$                                               | 20 µm                                                                      |  |  |

| Chip size                     | $2 \times 2 \text{ cm}^2$<br>(active area: 1.92x1.74 cm <sup>2</sup> ) | 2.1×2.3 cm <sup>2</sup><br>(active area: 2.05x2.05 cm <sup>2</sup> )       |  |  |

| Array size (Strip number)     | 512 rows $	imes$ 128 columns                                           | 1,024                                                                      |  |  |

| Spatial resolution            | $\sigma_{\phi}$ ~8 μm (bending), $\sigma_{z}$ ~40 μm                   | $\sigma_{\phi}{}^{\sim}4.2~\mu m$ (bending), $\sigma_{r}{}^{\sim}21~\mu m$ |  |  |

| Timing resolution             | ~3-5 ns                                                                | ~3-5 ns                                                                    |  |  |

| Data size per hit (1 readout) | 42 bit (14b BXID, 7b+9b address,<br>6b TOT, 5b fine TDC, 1 polarity)   | 32 bits (10b BXID, 10b address,<br>6b TOT, other 6 bits)                   |  |  |

| Data rate per chip            | Maximum ~0.1 Gbps*<br>(pair production)                                | Maximum ~0.2 Gbps*<br>(pair production)                                    |  |  |

| LV / HV                       | 1.2 V / 150 V                                                          | 1.8 V / 150 V                                                              |  |  |

\* Maximum hit rate: barrel~ $4.1 \times 10^5$ , endcap~ $7.5 \times 10^5$

| IT<br>KB | Modul<br>es/lay<br>er | Avg bkgrd<br>rate<br>(Hz/cm <sup>2</sup> ) | Avg Chip<br>Data rate<br>(Mbps)<br>(42bit & 4cm <sup>2</sup> ) | Avg Module<br>Data rate<br>(Mbps)<br>(14 chips) | Max bkgrd<br>rate<br>(Hz/cm <sup>2</sup> ) | Max Module<br>Data rate (Mbps)<br>(14 chips) |

|----------|-----------------------|--------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|--------------------------------------------|----------------------------------------------|

| 1        | 280                   | 10k                                        | 1.68                                                           | 23.5                                            | 46k                                        | 108.2                                        |

| 2        | 580                   | 21k                                        | 3.53                                                           | 49.4                                            | 410k                                       | 964.3                                        |

| 3        | 1344                  | 21k                                        | 3.53                                                           | 49.4                                            | 270k                                       | 635.0                                        |

In total 2204 Modules = 2204 fibers, each layer is independent with other layers on BEE

#### BEE Boards: 18+37+84=139, -> 14 Data Crates

| Hit | Rate | Conc | lusion |

|-----|------|------|--------|

|     |      |      |        |

|       | Z<br>[mm] | R_in<br>[mm]   | R_out<br>[mm]                            | Average hit rate<br>[10^4 Hz/cm^2] |   | Max hit rate<br>[10^4 Hz/cm^2] |  |

|-------|-----------|----------------|------------------------------------------|------------------------------------|---|--------------------------------|--|

| ITKE1 | 500.5     | 75             | 240                                      | 3.                                 | 9 | 23                             |  |

| ITKE2 | 715       | 101.9          | 350                                      | 10                                 | 6 | 38                             |  |

| ITKE3 | 1001      | 142.6          | 600                                      | 8.                                 | 9 | 75                             |  |

| ITKE4 | 1500      | 213.7          | 600                                      | 2.                                 | 4 | 6.3                            |  |

| OTKE  | 2903      | 406            | 1810 0.3                                 |                                    | 3 | 3.5                            |  |

|       | R<br>[mm] | Half_Z<br>[mm] | 0%200.3%203.5<br>Average h<br>[10^4 Hz/0 |                                    |   | ax hit rate<br>4 Hz/cm^2]      |  |

| ITKB1 | 240       | 500.5          | 1                                        |                                    |   | 4.6                            |  |

| ITKB2 | 350       | 715            | 2.1                                      |                                    |   | 41                             |  |

| ITKB3 | 600       | 1001           | 2.1                                      |                                    |   | 27                             |  |

| ОТКВ  | 1800      | 2000           | 0.7                                      |                                    |   | 0.9                            |  |

- Data width~42bit/event

- Barrel Module: 2\*7=14 chips

- Max Data rate per module ~1Gbps

- Enough room left for a fiber channel, 1 fiber for 1 module

#### **ITK—Power (Barrel)**

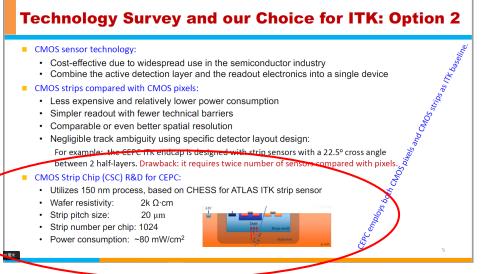

#### **Technology Survey and our Choice for ITK: Option 1**

- CMOS sensor technology:

- Cost-effective due to widespread use in the semiconductor industry

- Combine the active detection layer and the readout electronics into a single device

- HVCMOS pixels:

- Large depletion depth (full depletion), large signal

- Radiation hard

- Relatively large capacitance, leading to increased noise and power consumption

- New HVMOS (COFFEE) pixels R&D for CEPC:

- Utilizes 55 nm process instead of the 180 nm used in ATLASPix3 More functionality and less power consumption

- Wafer resistivity: 1k-2k Ω·cm

- $34 \times 150 \ \mu m^2$  Pixel size: 512 rows  $\times$  128 columns

- Array size:

- Power consumption: ~200 mW/cm<sup>2</sup>

- ATLASPix3

- TSI 180nm HVCMOS on 200 Ωcm substrate

- Pixel size 50 × 150 μm<sup>2</sup>

- 372 rows × 132 columns

- 20.2 × 21 mm<sup>2</sup> reticle size

- Each pixel has 7-bit TOT + 10-bit timestamp

- Continuous / triggered readout with 8b10b / 64b66b coding

- Power consumption ~160 mW/cm<sup>2</sup>.

| ITKB | Modu<br>les/la<br>yer | Layer<br>power (W) | Data Link<br>Power (W) | Total<br>Power(chip+da<br>ta)/85% |

|------|-----------------------|--------------------|------------------------|-----------------------------------|

| 1    | 280                   | 3.14k              | 280                    | 4.02kW                            |

| 2    | 580                   | 6.50k              | 580                    | 8.32kW                            |

| 3    | 1344                  | 15.1k              | 1344                   | 19.29kW                           |

- Estimated chip power 200mW/cm<sup>2</sup>, 14 chips per module, Module power 11.2W

- Extra power: Data Link 1W per module ۲

p-substrate

- **1** Power channel for each module for reliability & installation simplicity ۲

- **Power channels:** 280 + 580 +1344=2204, -> **Power Crates** 3+12+14=29, each layer independent ٠

- HV range 50~200V (normal HV), independent tuning for each module ۲

- Det-HV channels also 2204, -> Det-HV Crates 10

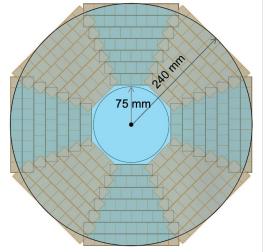

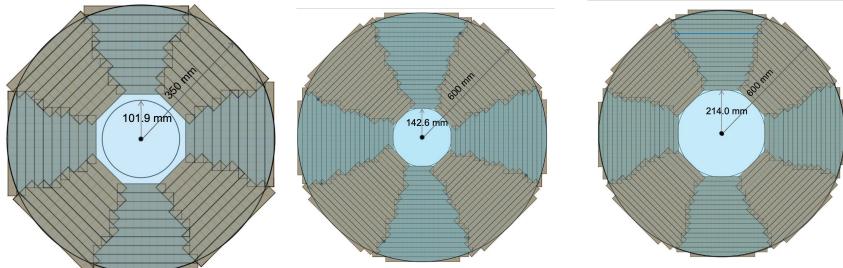

#### **ITK——Detector Design Endcap**

Hit position

σ<sub>φ</sub>~4.2μm σ<sub>r</sub>~ 21 μm

Strips

- 8 sectors for each endcap layer; each endcap by two layers overlapped @22.5°

- **Different size of module at different radius & different layers**

- Assume 1 fiber + 1 power for each module, chip number matters for data rate & power

- 1<sup>st</sup> Endcap: 9+9+8+7+6+5+4=48 chips, 7 ladders

- 2<sup>nd</sup> Endcap : 13+13+12+11+10+10+9+7+7+6=98 chips, 10 ladders

- 3<sup>rd</sup> Endcap : 17+22+22+21+20+19+19+18+17+16+16+15+14+13+12+12+10+8+8=299 chips, 19 ladders

- $4^{\text{th}}$  Endcap : 15+21+22+21+21+19+19+18+17+16+15+14+13+12+11+11+9=274 chips, **17 ladders**

#### ITK——Data Link (Endcap)

#### Hit Rate Conclusion

|      |       | Z<br>[mm]    | R_in<br>[mm]       | R_out<br>[mm]          | Average hit<br>[10^4 Hz/cn |                                |                                                |                                   | Endcap              | 1 (per Secto                     | vr) 2    | 3                      | 4                       | Total   |

|------|-------|--------------|--------------------|------------------------|----------------------------|--------------------------------|------------------------------------------------|-----------------------------------|---------------------|----------------------------------|----------|------------------------|-------------------------|---------|

|      | ITKE1 | 500.5        | 75                 | 240                    | 3.9                        | 23                             | -                                              |                                   | Ladder Type         | 6                                | 8        | 15                     | 12                      | 18      |

|      | ITKE2 | 715          | 101.9              | 350                    | 16                         | 38                             |                                                | Ladder Number                     |                     | 7                                | 10       | 18                     | 15                      | 1600    |

|      | ITKE3 | 1001         | 142.6              | 600                    | 8.9                        | 75                             |                                                | Chip Number<br>Active Area (mm^2) |                     | 48                               | 98       | 260                    | 236                     | 20544   |

|      | ITKE4 | 1500<br>2903 | 213.7<br>406       | 600<br>1810            | 2.4<br>0.3                 | 6.3<br>3.5                     | L                                              |                                   |                     | 20181.03                         | 42796.32 | 116080.28              | 106081.77               | 9.12e6  |

|      | OTKE  | 2905         | :2903%20406%201810 | %200.3%203.5           |                            |                                |                                                | Module Area (mm^2)                |                     | 23184                            | 47334    | 125580                 | 113988                  | 9.92e6  |

|      |       | R<br>[mm]    | Half_Z<br>[mm]     | Average h<br>[10^4 Hz/ |                            | Max hit rate<br>[10^4 Hz/cm^2] |                                                |                                   | ver Consumption (W) | 46.368                           | 94.668   | 251.16                 | 227.98                  | 1.98e4  |

|      | ITKB1 | 240          | 500.5              | 1                      |                            | 4.6                            |                                                | ,                                 |                     | 3.9e2                            | 1.6e3    | 8.9e2                  | 2.4e2                   |         |

|      | ITKB2 |              | 715                | 2.1                    |                            | 41                             |                                                | Avg. Hit Rate (Hz/mm^2)           |                     |                                  |          |                        |                         | -       |

|      | ITKB3 | 600          | 1001               | 2.1                    |                            | 27                             |                                                |                                   | Data Rate (Hz)      | 2.89e8                           | 2.42e9   | 3.58e9                 | 8.75e8                  | 2.29e11 |

|      | OTKB  | 1800         | 2000               | 0.7                    |                            | 0.9                            |                                                |                                   |                     |                                  |          | _                      |                         |         |

| ITKE |       | Lado<br>Max  | der<br>chips       | •                      | bkgrd<br>cm²)              | rate                           | Max bkgrd rateAvg Module Da(Hz/cm²)rate (Mbps) |                                   |                     | a Max Module Data<br>rate (Mbps) |          | Modules/Ladders(Fibers |                         |         |

| 1    |       | 9            |                    | 39k                    |                            |                                | 230k                                           |                                   | 47.2                | 278.4                            |          |                        | 7*8*2layer*2Endcap =224 |         |

| 2    |       | 13           |                    | 160                    | k                          |                                | 380k                                           |                                   | 279.7               |                                  | 664.3    |                        | 10*32=320               |         |

| 3    |       | 22           |                    | 89k                    |                            |                                | 750k                                           |                                   | 263.3               |                                  | 2218.9   |                        | 19*32=608               |         |

| 4    |       | 22           |                    | 24k                    |                            |                                | 63k                                            |                                   | 71.0                |                                  | 186.4    |                        | 17*32=544               |         |

- Max module data rate 2.2Gbps, enough room left by using 1 fiber for each ladder

- Ladders in total: 224+320+608+544=1696, =106 BEE, =12 Data Crates (symmetry from two side)

#### ITK—Power (Endcap)

23

- Power density 80mW/cm<sup>2</sup>, Chip Power 336mW

- Max Ladder Power 7.39W for DC-DC consideration

- Total Power 11.1kW,

- Ladder power is relatively low, consideration to merge for the power channel at the sector level

- In total 192 power channels, 2 power crates

- Inner 2 endcaps, 1 power chn for each sector

- Outer 2 endcaps, 2 power chns for each sector

- Det-HV ind. tuning for 50~200V, 1 chn for each ladder, in total 1696 Det-HV channels, = 8 Det-HV crates

| ITKE | Ladder<br>Max<br>chips | Ladder<br>Max<br>Power(W) | Chip<br>per<br>sector | Sector<br>Chip<br>Power(W) | Sector Data<br>Link Power<br>(W) | Sector<br>Power(Chip+Link)<br>÷85% (W) | Layer Power<br>(×8×2layer×2<br>endcap) (W) | Power Chn (1<br>Chn per sector) |

|------|------------------------|---------------------------|-----------------------|----------------------------|----------------------------------|----------------------------------------|--------------------------------------------|---------------------------------|

| 1    | 9                      | 3.02                      | 48                    | 16.1                       | 7                                | 27.2                                   | 870.6                                      | 1 × 32                          |

| 2    | 13                     | 4.36                      | 98                    | 32.9                       | 10                               | 50.5                                   | 1616.0                                     | 1× 32                           |

| 3    | 22                     | 7.39                      | 299                   | 100.5                      | 18                               | 139.4                                  | 4497.4                                     | 2× 32                           |

| 4    | 22                     | 7.39                      | 274                   | 92.1                       | 15                               | 126                                    | 4105.9                                     | 2× 32                           |

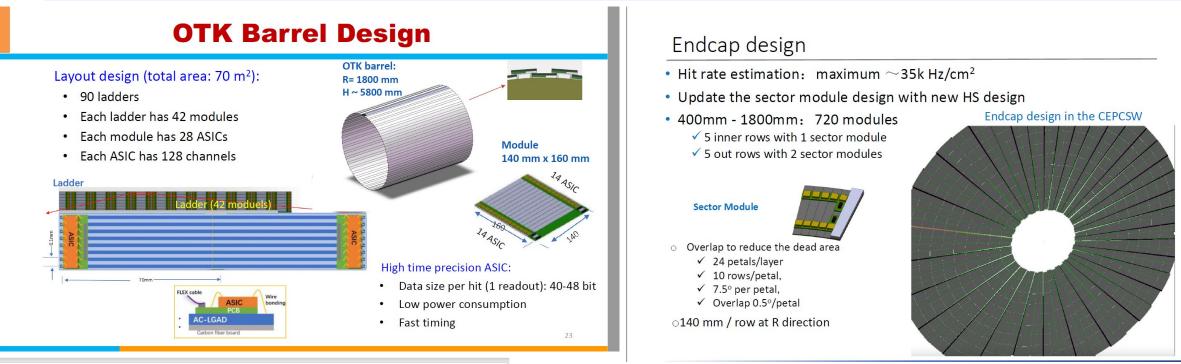

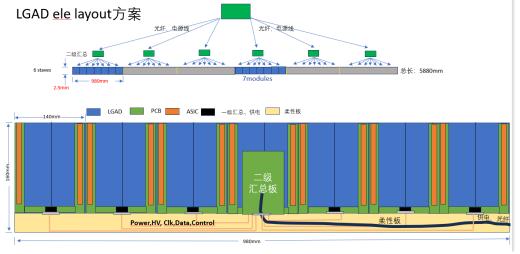

#### **OTK - detector design**

- Propose to use a unique ASIC for both barrel and endcaps

- Data width 48bit/event

#### **OTK-Data Link**

#### Hit Rate Conclusion Average hit rate [10^4 Hz/cm^2] Max hit rate R\_out R\_in [10^4 Hz/cm^2] [mm] [mm] [mm] ITKE1 500.5 75 240 3.9 23 ITKE2 715 101.9 350 16 38 ITKE3 1001 142.6 600 8.9 75 1500 213.7 600 2.4 6.3 ITKE4 0.3 3.5 OTKE 2903 406 1810 0 3%203 5 Average hit rate Max hit rate Half\_Z [10^4 Hz/cm^2] [10^4 Hz/cm^2] [mm] [mm] 240 500.5 1 4.6 ITKB1 715 2.1 ITKB2 350 41 ITKB3 600 1001 2.1 27

0.7

#### • Barrel:

OTKB 1800

2000

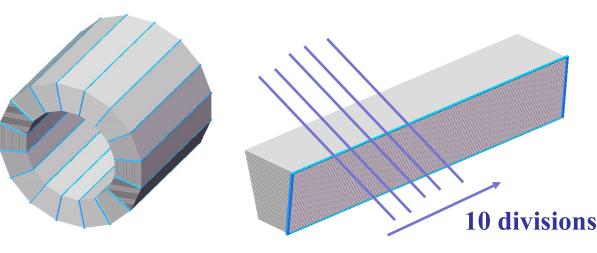

- Data link proposed to locate at the 2<sup>nd</sup> level aggregation board, for 7 modules (1 ladder), each module 22 ASICs

- Avg module rate 7kHz\*14cm\*14cm\*48bit=65.9Mbps, Max 9kHz→84.7Mbps

0.9

- For the optical data rate of 7 modules (1 ladder), avg/max to be 461.3Mbps/1355.2Mbps, with large room for the data link

- A full 6m Stave with 6 Ladders (6 fibers), barrel in total 90 ladders, =540 fibers = 34 BEE = 4 Data Crates

- Endcap:

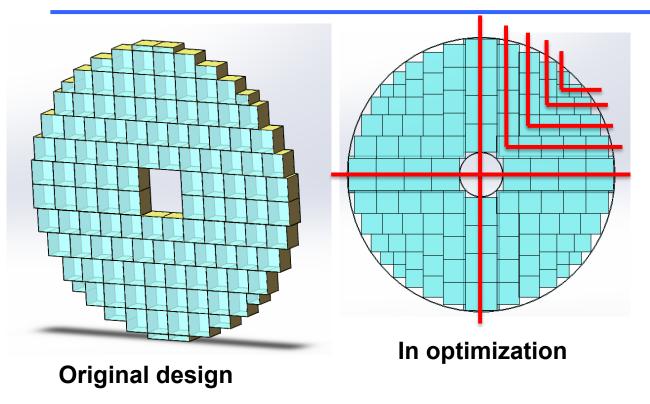

- 48 Pedals for 2 endcaps, 10 rings each Pedal with 15 sectors (Inner 5 rings 1 sector, Outer 5 rings 2 sectors)

- Total area 19.4m<sup>2</sup>, =4041.7cm<sup>2</sup> for each Pedal, avg. Pedal data rate= 3kHz\*4041.7\*48bit=582Mbps, Max 35kHz→6.79Gbps

- > Consideration 1 fiber for each sector, even concerning the higher data rate for inner sectors, enough room left for the fiber

- 48 Pedals with 720 sectors in total, =720 fibers = 45 BEE = 6 Data Crates (each endcap independent)

#### **OTK-Power**

- Chip power 20mW/ch @ 7pF Cd for 30ps

- 128 channels for each ASIC, 2.56W/chip

- Barrel:

- 90 staves, 6 ladders per stave, 7 modules per ladder, 22 ASIC per module

- Module power 56.32W (should be noticed for DC-DC design)

- In total  $90 \times 6 \times 7 \times 22 = 83,160$  ASICs, chip power 212.9kW

- Data Link power 1W for each ladder, 540 fibers in total, 0.54kW

- For DC-DC efficiency 85%, total power 251.1kW

- To provide 1 chn for each <u>module (not enough for 1 chn per ladder)</u>

- ➤ = 3780 power channel = 79 Power Crates

- Endcap:

- According to the detail detector design, 240 ASICs for each Pedal

- Max 23 chips for a sector, sector power 58.9W, needs a independent power channel

- 48 Pedals for 2 endcaps = 11520 ASICs, with chip power 29.5kW

- Data Link power 1W for each sector, 0.72kW in total

- For DC-DC efficiency 85%, total power 35.6kW

- 1 power chn for each sector: 720 power chns = 16 power crates (independent endcaps)

| Row(140<br>mm/rwo) | Chip per row | Date rate (HZ) |

|--------------------|--------------|----------------|

| R0 (400-540)       | 11           | 1533882.59     |

| R1: 540-680        | 14           | 335365.01      |

| R2: 680-820        | 17           | 412334.029     |

| R3:                | 19           | 489303.047     |

| R4                 | 23           | 566272.066     |

| R5                 | 25           | 643241.085     |

| R6                 | 29           | 720210.104     |

| R7                 | 31           | 797179.122     |

| R8                 | 34           | 874148.141     |

| R9: 1660-1800      | 37           | 951117.16      |

#### **OTK- Det-HV**

- Det-HV independently tuning for 150~200V

- 1 chn for each module/sector

- Barrel:

- $90 \times 6 \times 7=3780$  module, =3780 Det-HV chns =17 Det-HV crates

- Endcap:

- 720 sectors, 360 Det-HV chns for each endcap by 2 Det-HV crates, in total 4 Det-HV crates

## ECAL – Data Link(skip)

- The overall detector design: ~480 Module (Dual-trapezium scheme), ~1000 bar/module

- Current bkgrd estimation: avg. event rate 100kHz / crystal bar w/ threshold; Data width 48bit/event (current ASIC scheme)

- @Dual readout each crystal bar, total data rate:

1000\*100kHz\*48bit\*2ends=9.6Gbps, not possible for 1 fiber for each module, <u>at least 2 fibers for each module</u>

- For max. bkgrd rate@300kHz@Higgs, also needs enough room

- For Z pole, bkgrd will be much higher, also needs extra room

#### ECAL – crates (skip)

#### • Data Link:

- Fibers: 480\*2=960, -> 60 BEE Brds, 6 crates

- Power:

- ASIC: 15mW/ch, each module 1000\*2\*15mW=30W

- > Within the capability of DC-DC power module

- Data Link + Optical Power: 1W each

- Total Power: 31W/0.85\*480=17.5kW

- Efficiency of the DC-DC: 85%

- Power chn 40W/chn, each module per power cable: 480 power chn -> power crates 5

- Det-HV:

- Sch 1: one HV chn for each module, (limitedly) compensated for each SiPM in ASICs

- HV channels = module number = 480, -> 2 HV crates

- Alt sch2: HV chn for each SiPM? Too many channels & too large control data volume (×)

- Alt sch3: HV chn for sub-region of a module, to compensate the temperature gradient

- > Maybe much optimized than sch1, but rely on the detector simulation

#### ECAL – endcap

- Waiting for the final design of ECAL endcap

- According to the current design, module number 122~96, calculated by 130 modules

- Expect higher bkgrd rate than barrel, keep the scheme of 2 fibers per module

- Fibers:

- 130module\*2endcap\*2 fiber=520

- 34 BEE = 4 Data Crates (from 2 sides)

- Power:

- Total power: 31W/0.85\*260=9.48kW

- 260 Power channels = 4 power crates

### HCAL-Data Link(barrel)

#### HCAL电缆估算

- HCAL桶部排布

- 总通道数: 338万

- 分区: 16

- 层数: 48

- Cell尺寸: 4\*4cm

- 电子学板尺寸

- Z戶: 60cm(15cell)

- Phi向: 24cm(6cell), 28cm(7cell), 32cm(8cell)

- FEE单板最大功耗: 15\*8\*4\*20mW=9.6W

- 汇总板最大功耗: 9.6\*5=48W

- 桶部电缆数量

- 电缆类型: 高压, 低压(正负?), 光纤

- 1/16 分区电缆数量: 19\*3+29\*4=173

- 总电缆数量: 一端173\*16=2768, 总5536

- AWG12(线径2.05mm,电流: 13.1A/14.9A)

- Currently, HCAL is not finalized, especially for the module design, e.g. cell size and channel number

- Data have to be aggregated at the end of barrel for each layer, also the DC-DC

- By rough estimation, the bkgrd will be low, the aggregated data rate for each layer board should not exceed 8Gbps (10Gbps for the fiber)

- Then 1 fiber for each aggregation board is reasonable

- Fibers:

550速+反射器 10.2 m

- Aggr. board number every 1/16 sector: 19\*3+29\*4=173

- 1 fiber per aggregation board: 173\*16\*2=5536 fibers

- =346 BEE = 36 Data Crates

1~19layer 3PCBs width 20~48layer 4PCBs width Aggr Brd for 5 PCBs along z from both ends, with 1 fiber

#### **HCAL-Power (barrel)**

- Max PCB size corresponding to GS cells:

- Z direction: 60cm (15cell)

- Phi direction: 24cm (6cell), 28cm (7cell), 32cm (8cell)

- Concerning the light collection, every 4cm\*4cm GS cell may use 1~4 SiPMs

- Max SiPM channels for the largest PCB: 15\*8\*(1~4)=120~480

- ASIC Power 15mW/ch, Power for the max PCB: (120~480)\*15mW=1.8W~7.2W

- Every Aggregation board provides power for 5 PCBs: (1.8~7.2)\*5=9~36W

- Power for Barrel:

- ASIC power: total channel 3.38M \* 15mW/chn\*(1~4)=50.7kW~202kW

- > Match with the calculation: 15\*8 (PCB cells) \*173 Brds \* 10 div \*16 sections = 3.32M cells

- Data Link power 1W for 5536 fibers = 5536W

- For DC-DC efficiency 85%, total power [(50.7~202)+5.5]/0.85=66.1~244.2kW

- 1 power channel for each aggregation board for installation simplicity:

> 5536 power channels = 116 power crates

## **HCAL-Data Link (Endcap)**

#### HCAL电缆估算

- HCAL端盖部排布

- •总通道数:单端112万,总共224万

- 分区: 16

- 层数: 48

- Cell尺寸: 4\*4cm

- 端盖电缆数量

- 电缆类型: 高压, 低压(正负?), 光纤

- 每区功耗: 1459\*20mW=30W

- 1/16 分区电缆数量: 48

- 总电缆数量: 一端48\*16=768, 总1536

- AWG12(线径2.05mm,电流: 13.1A/14.9A)

- •未确定电缆:刻度方案

- Fibers

- 1 fiber for each sector at each layer

- 48layer\*16sector\*2endcap=1536

- =96BEE = 10 Data Crates

- Current design for HCAL:

- 48 layers with 16 sectors

- Needs input of the bkgrd rate, assuming 1 fiber is enough (data rate < 8Gbps) for each sector at each layer

- Rough calculation:

- each endcap 1.12M channels -> 1458 GS cells for each sector

- Even if the bkgrd is at the level of ECAL of 100kHz avg., total data rate of each sector per layer is 7.0Gbps, within the safety region for using 1 fiber

## **HCAL-Power (Endcap)**

#### HCAL电缆估算

- HCAL端盖部排布

- •总通道数:单端112万,总共224万

- 分区: 16

- 层数: 48

- Cell尺寸: 4\*4cm

- 端盖电缆数量

- 电缆类型: 高压, 低压(正负?), 光纤

- •每区功耗: 1459\*20mW=30W

- 1/16 分区电缆数量: 48

- 总电缆数量: 一端48\*16=768, 总1536

- AWG12(线径2.05mm,电流: 13.1A/14.9A)

- •未确定电缆:刻度方案

- each endcap 1.12M channels -> 1458 GS cells for each sector

- If each GS cell with 1~4 SiPM channels, each sector 1458~5832 ASIC channels

- Common SiPM ASIC as ECAL, 15mW/chn max

- Each sector 21.9~87.5W (<u>should be noticed</u> <u>for DC-DC design</u>)

- Chip power 2.24M\*15mW/ch \* (1~4) = 33.6~134.4kW

- Data link power : 1536W for 1536 fibers

- Total power: (33.6~134.4k+1536)/0.85=41.3~159.9kW

- 1 power chn for each sector at each layer: 1536 power chns = 16 power crates

#### CAL—Det-HV

- SiPM HV 40~60V depends on device type

- Currently not clear for ECAL & HCAL detector HV scheme

- Scheme 1: HV for each module, compensate SiPM in ASIC

- > Limited compensation range by ASIC, may see large gradient by temperature

- Alt sch2: HV chn for each SiPM? Too many channels & too large control data volume (×)

- Alt sch3: HV chn for sub-region of a module, to compensate the temperature gradient

- Maybe much optimized than sch1, but strongly rely on the detector simulation and careful design future work

- Currently only simply considering Det-HV for each module

- ECAL barrel: 480 modules, 480 Det-HV chns, 2 Det-HV crates

- ECAL endcap: 260 modules, 260 Det-HV chns, 2 Det-HV crates

- HCAL barrel: 5536 aggregation boards, 5536 Det-HV chns, 26 Det-HV crates

- HCAL endcap: 1536 sector layer, 1536 Det-HV chns, 32 Det-HV crates

#### Muon

| Muon             | Module | Channel/Module | Readout<br>Channel | Hit rate/Hz<br>(worst case) | Data format                                             | Raw data rate /<br>Gbps |

|------------------|--------|----------------|--------------------|-----------------------------|---------------------------------------------------------|-------------------------|

| Barrel           | 192    | 169.5          | 32544              | 10 k                        | 48bit<br>(8b BX+ 10b<br>ADC + 2b range<br>+ 9b TOT + 7b | 15.63                   |

| Inner<br>endcaps | 64     | 144            | 9216               | 10k~100 k,<br>Average 20 k  |                                                         | 8.85                    |

| Outer<br>endcaps | 64     | 256            | 16384              | 10 k                        | TOA+ 4b chn ID<br>+ 8b chip ID)                         | 7.87                    |

| Total            |        |                | ~58.2 k            |                             |                                                         | ~32.4                   |

- Needs detailed design of the overall detector, only provides a estimation from BELLE2

- Assuming bkgrd not high, 1 fiber for each module:

- Barrel 192 fibers = 12 Data crates; Endcap 128 fibers, 8 Data crates

- Power: Assuming common ASIC for SiPM as CAL with a 15mW/chn, the max module power is 3.84W, a low power crate is enough with 96chn/crate

- Barrel 2, inner endcap 2, outer endcap 2 power crates

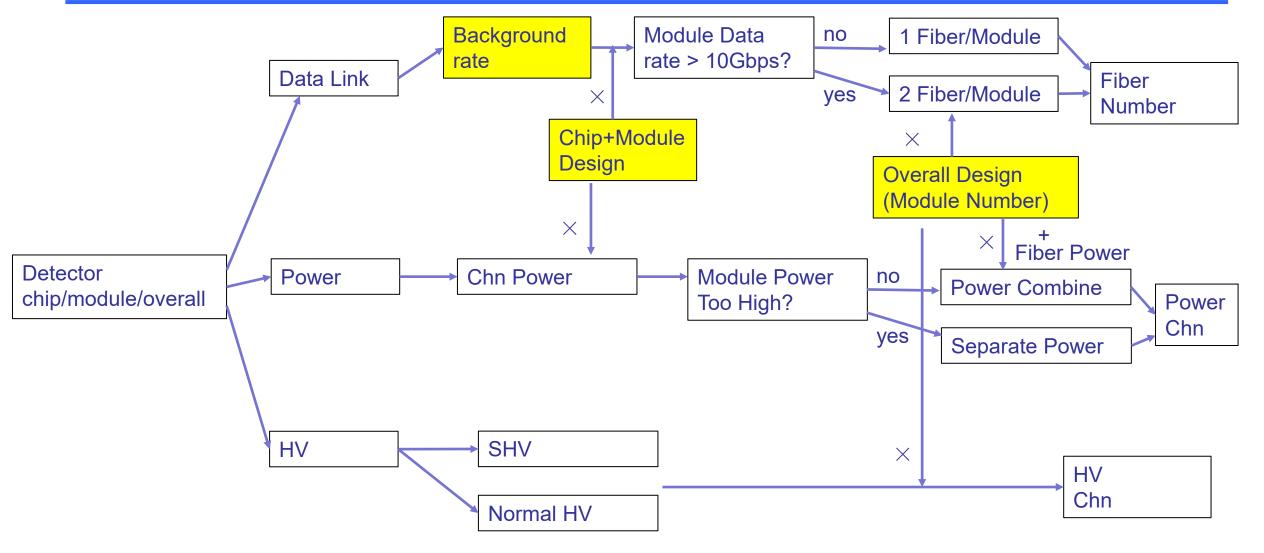

## Summary table

| Detector         | Max<br>data rate<br>per fiber<br>(Gbps) | Fibers<br>per<br>module | Fiber<br>sum       | BEE<br>sum       | Data<br>crate<br>sum | Module<br>Max<br>Power<br>(W) | Total<br>Power<br>(kW) | Power<br>channels  | Power<br>crate<br>sum | HV<br>require<br>ments | HV<br>chann<br>els<br>sum | HV<br>crates<br>sum | Trg<br>boards<br>sum | Trg<br>crates<br>sum | Comme<br>nt      |

|------------------|-----------------------------------------|-------------------------|--------------------|------------------|----------------------|-------------------------------|------------------------|--------------------|-----------------------|------------------------|---------------------------|---------------------|----------------------|----------------------|------------------|

| ντχ              | 8                                       | <mark>1~2</mark>        | 88                 | 6                | 1                    | 25                            | 0.45                   | 66                 | 2                     | ~-10V                  | 66                        | 1                   |                      |                      |                  |

| ТРС              | 0.1                                     | 1                       | 496                | 32               | 4                    | 42                            | 20                     | 496                | 6                     | SHV                    | 496                       | 4                   |                      |                      |                  |

| ITK-<br>Barrel   | 0.96                                    | 1                       | 2204               | 139              | 14                   | 11.2                          | 31.59                  | 2204               | 29                    | 50~200<br>V            | 2204                      | 10                  |                      |                      |                  |

| ITK-<br>EndCap   | 2.2                                     | 1                       | 1696               | 106              | 12                   | 7.4                           | 11.1                   | 192                | 2                     | 50~200<br>V            | 1696                      | 8                   |                      |                      |                  |

| OTK-<br>Barrel   | 1.4                                     | 1                       | 540                | 34               | 4                    | <mark>56.3</mark>             | 251.1                  | 3780               | 79                    | 150~200<br>V           | 3780                      | 17                  |                      |                      |                  |

| OTK-<br>EndCap   | 0.7                                     | 1                       | 720                | 45               | 6                    | <mark>58.9</mark>             | 35.6                   | 720                | 16                    | 150~200<br>V           | 720                       | 4                   |                      |                      | Not<br>finalized |

| ECAL-<br>Barrel  | 4.8                                     | 2                       | 960                | 60               | 6                    | 30                            | 17.5                   | 480                | 5                     | 40~60V                 | 480                       | 2                   |                      |                      |                  |

| ECAL-<br>EndCap  | ?                                       | 2                       | 520                | 34               | 4                    | 30                            | 9.5                    | 260                | 4                     | 40~60V                 | 260                       | 2                   |                      |                      | Not<br>finalized |

| HCAL-<br>Barrel  | ?                                       | 1                       | <mark>5536</mark>  | <mark>346</mark> | 36                   | 9                             | 66.1                   | <mark>5536</mark>  | 58                    | 40~60V                 | 5536                      | 26                  |                      |                      | Not<br>finalized |

| HCAL-<br>EndCap  | ?                                       | 1                       | 1536               | 96               | 10                   | 21.9                          | 41.3                   | <mark>1536</mark>  | 16                    | 40~60V                 | 1536                      | 32                  |                      |                      | Not<br>finalized |

| Muon-<br>Barrel  | ?                                       | 1                       | 192                | 12               | 2                    | 2.54                          | 0.49                   | 192                | 2                     | 40~60V                 | 192                       | 1                   |                      |                      | No Det<br>scheme |

| Muon-<br>EndCap  | ?                                       | 1                       | 128                | 8                | 2                    | 3.84                          | 0.38                   | 128                | 4                     | 40~60V                 | 128                       | 2                   |                      |                      | No Det<br>scheme |

| <mark>Sum</mark> |                                         |                         | <mark>14616</mark> | <mark>918</mark> | <mark>101</mark>     |                               | <mark>485.11</mark>    | <mark>15590</mark> | 223                   |                        | <mark>17094</mark>        | <mark>109</mark>    |                      |                      |                  |

#### **Requirement from Sub-Detector for FEE Data – updated**

|                                   | Vertex                                                    | Pix(ITKB)                                                              | Strip<br>(ITKE)                                               | ОТКВ                                           | ΟΤΚΕ                                             | TPC                                                                           | ECAL-B                                                      | ECAL-E                               | HCAL-B                                                         | HCAL-E                                    | Muon                                 |  |

|-----------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|-------------------------------------------|--------------------------------------|--|

| Channels<br>per chip              | 512*1024<br>Pixelized                                     | 512*128                                                                | 1024                                                          | 128                                            |                                                  | 128                                                                           | 8~16<br>@common SiPM ASIC                                   |                                      |                                                                |                                           |                                      |  |

| Ref. Signal processing            | XY addr +<br>BX ID                                        | XY addr +<br>timing                                                    | Hit + TOT<br>+ timing                                         | ADC+TDC                                        | TOT+TOA                                          | ADC + BX<br>ID                                                                | TOT + TOA/<br>ADC + TDC                                     |                                      |                                                                |                                           |                                      |  |

| Data Width<br>/hit                | 32bit<br>(10b X+<br>9b Y + 8b<br>BX + 5b<br>chip ID)      | 42bit<br>(9b X+7b<br>Y +14b BX<br>+ 6b TOT +<br>5TDC + 1b<br>polarity) | 32bit<br>(10b chn ID<br>+ 10b BX +<br>6b TOT +<br>5b chip ID) | 40~4<br>(7b chn ID + 8t<br>7b TOA+5            | BX + 9b TOT +                                    | 48bit<br>(7b chn ID<br>+ 8b BX +<br>11b chip<br>ID + 12b<br>ADC + 10b<br>TOA) |                                                             |                                      |                                                                |                                           |                                      |  |

| Max Data<br>rate / chip           | 2Gbps/chi<br>p@Trigge<br>rless@Lo<br>w LumiZ<br>Innermost | Avg.<br>3.53Mbps/c<br>hip<br>Max.<br>68.9Mbps/c<br>hip                 | Avg.<br>21.5Mbps/c<br>hip<br>Max.<br>100.8MHz/<br>chip        | Avg:<br>2.9Mbps/chip<br>Max:<br>3.85Mbps/chip  | Avg:<br>38.8Mbps/chip<br>Max:<br>452.7Mbps/chip  | ~70Mbps/<br>module<br>Inmost                                                  | ~9.6Gbps/mo<br>dule<br>@dual-end<br>readout                 | Needs bkgrd<br>rate                  | Needs bkgrd<br>rate                                            | Needs bkgrd<br>rate                       | Needs bkgrd<br>rate                  |  |

| Data<br>aggregation               | 10~20:1,<br>@2Gbps                                        | 14:1@O(10<br>0Mbps)                                                    | 22:1<br>@O(100Mb<br>ps)                                       | i. 22:1<br>@O(5Mbps)<br>ii. 7:1<br>@O(100Mbps) | i. 22:1<br>@O(50Mbps)<br>ii. 10:1<br>@O(500Mbps) | 1. 279:1<br>FEE-0<br>2. 4:1<br>Module                                         | i. 4~5:1 side<br>ii. 7*4 / 14*4<br>back brd @<br>O(100Mbps) | Needs<br>detector<br>finalization    | < 10:1<br>(40cm*40cm<br>PCB –<br>4cm*4cm tile –<br>16chn ASIC) | Needs detector finalization               | Needs detector finalization          |  |

| Detector<br>Channel/m<br>odule    | 1882<br>chips<br>@Stch<br>&Ladder                         | 30,856<br>chips<br>2204<br>modules                                     | 23008<br>chips<br>1696<br>modules                             | 83160 chips<br>3780 modules                    | 11520 chips<br>720 modules                       | 492<br>Module                                                                 | 0.96M chn<br>~60000 chips<br>480 modules                    | Needs<br>detector<br>finalization    | 3.38M chn<br>5536<br>aggregation<br>board                      | 2.24M chn<br>1536<br>Aggregation<br>board | Needs detector finalization          |  |

| Avg Data<br>Vol before<br>trigger | 474.2Gb<br>ps                                             | 101.7Gbp<br>s                                                          | 298.8Gbp<br>s                                                 | 249.1Gbps                                      | 27.9Gbps                                         | 34.4Gbps                                                                      | 4.6Tbps<br>(needs<br>finalization)                          | Needs det &<br>bkgrd<br>finalization | Needs det &<br>bkgrd<br>finalization                           | Needs det &<br>bkgrd<br>finalization      | Needs det &<br>bkgrd<br>finalization |  |

#### A summary of FEE power – updated

|                                               | Vertex                             | Pix(ITKB)                           | Strip (ITKE)                        | ОТКВ | ΟΤΚΕ               | TPC                    | ECAL-B                    | ECAL-E                            | HCAL-B | HCAL-E | Muon                        |

|-----------------------------------------------|------------------------------------|-------------------------------------|-------------------------------------|------|--------------------|------------------------|---------------------------|-----------------------------------|--------|--------|-----------------------------|

| Channels per<br>chip                          | 512*1024<br>Pixelized              | 512*128                             | 1024                                |      | 128                | 128                    | 8~16<br>@common SiPM ASIC |                                   |        |        |                             |

| Technology                                    | 65nm CIS                           | 55nm<br>HVCMOS                      | 55nm<br>HVCMOS                      | 55n  | m CMOS             | 65 CMOS                | 55nm CMOS (or 180 CMOS?)  |                                   |        |        |                             |

| Power<br>Supply<br>Voltage (for<br>DC-DC) (V) | 1.2                                | 1.2                                 | 1.2                                 |      | 1.2                | 1.2                    | 1.2 (or 1.8?)             |                                   |        |        |                             |

| Power@chip                                    | 40mW/cm <sup>2</sup><br>200mW/chip | 200mW/cm <sup>2</sup><br>800mW/chip | 200mW/cm <sup>2</sup><br>336mW/chip |      | mW/chn<br>56W/chip | 280µW/chn<br>35mW/chip | 15mW/chn<br>240mW/chip    |                                   |        |        |                             |

| Max<br>chips@modu<br>le                       | 29                                 | 14                                  | 22                                  | 22   | 3                  | 1115                   | 64                        | Needs<br>detector<br>finalization | 8      | 92     | Needs detector finalization |

| Power@mod<br>ule (W)                          | 5.8                                | 11.2                                | 7.39                                | 56.3 | 58.9               | 39.7                   | 30                        | Needs<br>detector<br>finalization | 9      | 21.9   | Needs detector finalization |

#### **Preliminary consideration for the TDAQ**

- Very early stage for the trigger scheme, many aspects not clear

- Physics goal for the trigger scheme

- Needs further discussion on sub detectors that participate in the trigger decision, and information that can be attracted from detectors

- Trigger algorithm vs related resources depend on complexity

- Needs to define the requirement for the trigger latency

- From electronics: can rely on big RAM, then the restore capability can be enough

- Ref parameters: 8GB ram on BEE, a 16-chn BEE with max data rate of 160Gbps, can hold a buffer length to be 8G×8/160=0.4s

- From detector: response speed of many detectors not finalized, some slow detectors will affect the trigger latency

- Current rough estimation: Trigger system needs 160 Trg boards = 20 ATCA crates = 10 Racks

- Note:

- Z pole bkgrd is too high at current stage (esp. ECAL), not clear for the future optimization.

- However future upgrade is necessary, and reserved room should be pre-allocated.

Table 1.2: CMS Phase-2 detector projected data links, ATCA back-end configuration and event size summary. Data are obtained from the technical design reports wherever possible. Average throughput estimated from event size assuming 750 kHz Level-1-accept rate.

| Subdetector        | Front-end                | Sub-event | Back-end | Back-end | Average           | Notes            |

|--------------------|--------------------------|-----------|----------|----------|-------------------|------------------|

|                    | lpGBT links <sup>a</sup> | size (MB) | boards   | crates   | throughput (Tb/s) |                  |

| Outer Tracker      | 13 000                   | 1.15      | 216      | 18       | 6.90              | ( <sup>b</sup> ) |

| Track Trigger      |                          | 0.01      |          | 18       | 0.06              |                  |

| Inner Tracker      | 1 2 6 0                  | 1.44      | 24       | 4        | 8.64              | ( <sup>c</sup> ) |

| MIP Timing Det BTL | 1 000                    | 0.02      | 11       | 1        | 0.14              |                  |

| MIP Timing Det ETL | 438                      | 0.04      | 5        | 1        | 0.22              |                  |

| ECAL Barrel        | 10000                    | 1.58      | 108      | 12       | 9.49              |                  |

| HCAL Barrel        | other                    | 0.24      | 18       | 2        | 1.45              |                  |

| HCAL - HO          | legacy                   | 0.03      | -        | 1        | 0.18              | ( <sup>d</sup> ) |

| HCAL - HF          | other                    | 0.06      | -        | 1        | 0.36              | (d)              |

| Endcap CALO        | 8 000                    | 2.00      | 108      | 9        | 12.00             |                  |

| Endcap CALO TPG    | 9 000                    | 0.20      | 144      | 12       | 1.50              |                  |

| muon DT            | 3840                     | 0.13      | 84       | 8        | 0.78              |                  |

| muon CSC           | other                    | 0.20      | -        | 2        | 1.20              | ( <sup>d</sup> ) |

| muon GEM - GE1/1   | other                    | 0.002     | -        | 1        | 0.01              | (d)              |

| muon GEM - GE2/1   | 144                      | 0.001     | 8        | 1        | 0.01              |                  |

| muon GEM - ME0     | 216                      | 0.12      | 12       | 1        | 0.71              |                  |

| muon RPC           | other                    | -         | -        | -        | -                 | ( <sup>e</sup> ) |

| Level1             |                          | 0.15      | 120      | 14       | 0.90              | (*)              |

| Total              |                          | 7.4       | >858     | >106     | 44                |                  |

• The total number of data crates of CMS matches with our calculation for CEPC

• Why choose CMS for a comparison? Similar detector scale, similar trigger framework (both are backend trigger)

#### https://cds.cern.ch/record/1027431/files/p165.pdf

#### **CMS counting room**

# USC55 size: 19m×17m × 85m\* Racks located centralizedly (see table below)

\*: https://doi.org/10.1007/978-3-031-12851-6\_49

#### **CMS USC55 counting room**

#### **CMS racks organization**

| 19 |   |          |

|----|---|----------|

|    | 6 | - second |

|    |   | g.       |

|    |   |          |

| +Z        |                |                | Up                  |                          |               | (Zone S2)   |                       |                      | -Z        |

|-----------|----------------|----------------|---------------------|--------------------------|---------------|-------------|-----------------------|----------------------|-----------|

|           | Α              | В              | С                   | D                        | E             |             | F                     | G                    | н         |

| 01        |                |                |                     | ECAL spare               | Cal Reg       |             | HCAL HTR              |                      |           |

| 02        | TOTEM          | TOTEM          | DAQ                 | ECAL ULR                 | Cal Reg       |             | HCAL HTR              | DAQ                  | x         |

| 03<br>04  | TOTEM          | TOTEM          | CASTOR HV           | ECAL ULR                 | %Cal Re       |             | HCAL HTR              | EBE DCS              | x         |

| 04<br>05  | TOTEM<br>TOTEM | TOTEM<br>DAQ   | CASTOR HV<br>UX DCS | ECAL ULR<br>ECAL SRP/TST | Cal Reg       |             | HCAL HTR<br>%HCAL HTR | EBE DCS<br>Presh. HV | x         |

|           | RAMSES         |                |                     |                          | %Cal Re       |             |                       |                      | х         |

| 06        |                | EB HV          | HCAL DCS            | ECAL ULR                 | Cal Reg       |             | HCAL HTR              | EB HV                | х         |

| 07        | Access         | EB HV          | HCAL DCS            | ECAL ULR                 | Cal Reg       |             | HCAL HTR              | EB HV                | х         |