### COFFEE2 Circuit Test with Caribou Board

Dexing Miao, Leyi Li, Yiming Li, Weiguo Lu, Zhiyu Xiang, Zijun Xu, Yang Zhou

October 15, 2024

Zhiyu Xiang October 15, 2024 1/17

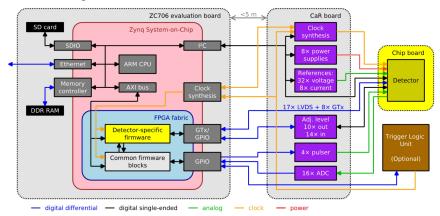

#### ZC706 evaluation board

#### Xilinx ZC706 evaluation board

Zyng-7000 XC7Z045-2FFG900C SoC

#### **Processing System (PS)**

2 x ARM Cortex-A9 MPCore CPUs Yocto-based Linux Network/ssh control interface Caribou DAQ software (Peary)

https://www.xilinx.com/products/boards-and-kits/ek-z7-zc706-g.html

#### Programmable Logic (PL)

Kintex-7 FPGA AXI control interface Caribou firmware

Zhiyu Xiang October 15, 2024 2 / 17

#### CaR board

## Control and Readout (CaR) board

| Feature                           | Description                                  |  |  |  |

|-----------------------------------|----------------------------------------------|--|--|--|

| Adjustable Power Supplies         | 8 units, 0.8 – 3.6 V, 3 A                    |  |  |  |

| Adjustable Voltage References     | 32 units, 0 – 4 V                            |  |  |  |

| Adjustable Current References     | 8 units, 0 – 1 mA                            |  |  |  |

| Voltage Inputs to Slow ADC        | 8 channels, 50 kSPS, 12-bit, 0 - 4 V         |  |  |  |

| Analog Inputs to Fast ADC         | 16 channels, 65 MSPS, 14-bit, 0 - 1 V        |  |  |  |

| Programmable Injection Pulsers    | 4 units                                      |  |  |  |

| Full-Duplex High-Speed GTx Links  | 8 links, <12 Gbps                            |  |  |  |

| LVDS Links                        | 17 bidirectional links                       |  |  |  |

| Input/Output Links                | 10 output links, 14 input links, 0.8 - 3.6 V |  |  |  |

| Programmable Clock Generator      | Included                                     |  |  |  |

| External TLU Clock Reference      | Included                                     |  |  |  |

| External High-Voltage (HV) Input  | Included                                     |  |  |  |

| FEAST Module Compatibility        | Supported                                    |  |  |  |

| FMC Interface to FPGA             | Included                                     |  |  |  |

| SEARAY Interface to Detector Chip | 320-pin connector                            |  |  |  |

**20 CaR boards v1.4** produced and distributed within RD50 common project

https://gitlab.cern.ch/Caribou/hardware/carboard

3 / 17

Zhiyu Xiang October 15, 2024

## **Caribou system architecture**

Zhiyu Xiang October 15, 2024 4 / 17

## Setup: Tested Bias PIN

| -                    |         |        |              |          |           |        |  |

|----------------------|---------|--------|--------------|----------|-----------|--------|--|

| PIN                  | VDDD    | BL     | $TH_{L}left$ | COM_BIAS | CLAMP     | VDDA   |  |

| $V_{set}[V]$         | 1.2     | 0.55   | 0.8          | 8.0      | 1.2       | 1.2    |  |

| $V_{out}[V]$         | 1.23    | 0.55   | 8.0          | 8.0      | 1.2       | 1.2    |  |

| PIN                  | VB2_FB  | VB1_FB | IBN          | IBFOLL   | $VCAS_rt$ | IBP    |  |

| $V_{set}[V]$         | 0       | 0.475  | 0.6          | 0.5      | 1.5       | 0.76   |  |

| $V_{out}[V]$         | 0       | 0.474  | 0.6          | 0.5      | 1.5       | 0.76   |  |

| PIN                  | VDD_grd | IOUT   | VDDA_rt      | VB1      | TH_rt     | VBO    |  |

| $V_{set}[V]$         | 1.2     | 1.2    | 0.65         | 0.7      | 0.6       | 1.5    |  |

| $V_{out}[V]$         | 1.23    | 1.2    | 0.68         | 0.7      | 0.6       | 1.5    |  |

| PIN                  | BL      | VNFOLL | VCAS_lt      | VN       | VP        | VB2_SB |  |

| V <sub>set</sub> [V] | 0.55    | 0.4    | 0.72         | 0.535    | 0.73      | 0      |  |

| $V_{out}[V]$         | 0.55    | 0.4    | 0.72         | 0.536    | 0.73      | 0      |  |

| PIN                  | P_WELL  | VB1_SB | VDDA_left    |          |           |        |  |

| $V_{\text{set}}[V]$  | 0       | 0.29   | 0.8          |          |           |        |  |

| $V_{out}[V]$         | 0       | 0.29   | 0.844        |          |           |        |  |

Other bias pins default connect to HV, PWR\_OUT or GND

Zhiyu Xiang October 15, 2024 5 / 17

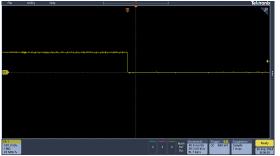

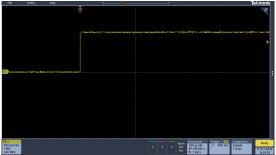

## Setup: Tested pulse configuration

Pulse rise/fall time about  $4\mu s/20ns$ . Q: require  $\sim ns?$  - 20ns fall time works in simulation.

- INJ\_BIAS (voltage) + INJ\_CTRL (analog switch) = pulse

- INJ\_BIAS: I2C protocol among SoC and CaR, DAQ system integrated, easy to control

- INJ\_CTRL: Hardware manager or AXI protocol among FPGA and CaR. Need build firmware, configured by Zijun with former method

Zhiyu Xiang October 15, 2024 6 / 17

## Setup: Configurable PIN

BIAS: current source, i/o  $5\mu A$  configured

VBG/VDAC: BG output/DAC output. getADC  $\longrightarrow$  0.6V

VOUT\_1COL: Analog output  $\stackrel{FMC}{\longrightarrow}$  CaR pin(ADC\_IN\_G2) $\stackrel{ADC}{\longrightarrow}$  Diff. digital signal  $\stackrel{FMC}{\longrightarrow}$  ZC706 FPGA pin: [T24 T25]

$Sel_{row} < 0...4 >: row selector. Digital input, FPGA pin: [W25 W26], [V28 V29], [R28 T28], [T30 U30], [R25 R26]$

Row\_sel < 0 >: Digital output for validate Sel\_ < 0 >, FPGA pin [N26 N27]

VCAL: external pulse injection. CaR(INJ\_CTRL\_1), FPGA pin:[T24 T25]

D\_out\_1stcol, D\_out\_234cols: Digital output. H-level if pixel triggered in 1 or 234 (in total) colum. FPGA pin: [P23 P24], [P21 R21]

Zhiyu Xiang October 15, 2024 7 / 17

## Setup: Problem PIN - FPGA pin NOT connected to FMC

Few pins of FPGA could not connected for ZC706 due to factory design

Col\_sel< 19 >: Digital output. H-level if colum 19 selected

A\_out\_1stcol, A\_out\_234cols: Analog output for colum0 or colum 123 (in total)

$Sel\_col < 0...4 >: colum selector. Digital input, FPGA pin: [P30 R30], [1 break], [T29 U29], [3 break], [P25 P26]$

COM\_ROW: Digital pulse output after buffer for row 32

COM\_PIXEL: 1 pixel comparator output after buffer

CSA\_OUT\_COL: CSA output after buffer for colum 1

CSA\_OUT\_PIXEL: CSA output after buffer for 1 pixel

VOUT\_1COL, VOUT\_7COL, VOUT\_SP: Analog output for colum 4, 5-11 or outside 4 signal pixels

COL\_CON: Test input from external signal

Zhiyu Xiang October 15, 2024

8 / 17

## Digital switch test

Switch Sel\_row[4,0] to 0 or !0, Row\_sel[0] gives 1 or 0, En\_row also works

Zhiyu Xiang October 15, 2024 9 / 17

## Modifying wire-bonding for colum selector

Row-Colum mask: foalting pin convert to 0/1 or random code?

| row bit index | 4 | 3 | 2 | 1 | 0 | col bit index | 4 | 3 | 2 | 1 | 0 |

|---------------|---|---|---|---|---|---------------|---|---|---|---|---|

| CaR pin index | 1 | 2 | 4 | 5 | 7 | CaR pin index | 6 | Ø | 3 | 8 | 0 |

Modifying the wire-bonding for foalting pin (connect bit 3/1 to neighbor) to ensure the certain 0 or 1 level

• case1:  $1 \Leftrightarrow 0$ ,  $3 \Leftrightarrow 2$ , enable colum 0,3,12,15,16,19

• case2:  $1 \Leftrightarrow 2$ ,  $3 \Leftrightarrow 4$ , enable colum 0,1,6,7

Zhiyu Xiang October 15, 2024 10 / 17

### Colum selector validation

Switch  $Sel\_col[4,0]$  to 10011,  $Col\_sel[19]$  gives 1

Zhiyu Xiang October 15, 2024 11 / 17

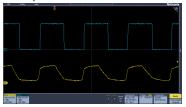

## CSA analog out test

- i.e. Switch Sel\_row[4,0] and Sel\_col[4,0] to ALL 0 (pixel 0, other rows also tried)

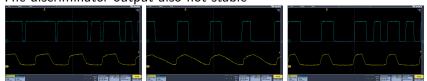

- The abnormal CSA baseline analog output after buffer (A\_out\_1st\_col) and digital output after discriminator (D\_out\_1stcol).

Pulse injection doesn't affect the output

- Similar for other colums (tried 3,6,7 and last 8 colums)

• The discriminator output also not stable

Zhiyu Xiang October 15, 2024

12 / 17

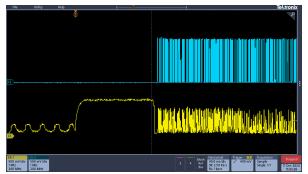

# What happen at the very beginning?

• At the time scale of power on. Not sure if there is self-oscillation

Zhiyu Xiang October 15, 2024 13 / 17

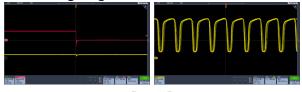

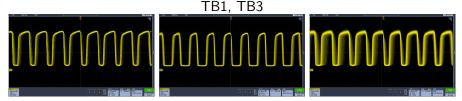

### Check a CSA baseline for all TBs

2 (modifying wire-bonding) + 3 (from Weiguo) = 5 TBs in total. CSA\_OUT\_PIXEL, analog output of a single pixel after buffer, independent of the row and column gating.

TB4, TB5, TB6

Adjust reference voltage did not affect to much.

Zhiyu Xiang October 15, 2024 14 / 17

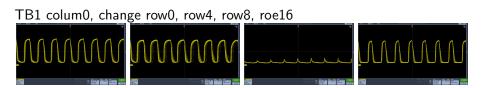

## Check CSA in same colum, i.e. TB1

Zhiyu Xiang October 15, 2024 15 / 17

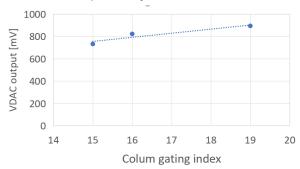

#### **VDAC** test

- VDAC controlled by 6 bit input from colum < 19 14 >, should proportion to colum gating. i.e. TB1 allows colum 15,16,19

- Not a perfect linear dependency

Zhiyu Xiang October 15, 2024 16 / 17

#### Conclusion

- Caribou system prepared, bias voltage and pulse function verified

- 5 chips tested with (modified) designed board

- Not seen expected CSA analog output

- Row-Colum digital gating works well

- Discriminator seems work

- VDAC changed with colum selection

- What can we try:

- 1. Try FIB to modify the connection among diode and CSA to avoid the X-talk

- 2. Investigate the CSA analog output with the simulation

- 3. Re-do the test with the new externally adjustable board to avoid any potential X-talk from CaR system

Zhiyu Xiang October 15, 2024 17 / 17