## Development of DNN trigger for Belle II experiment

Shuangshuang Zhang, Qi-Dong Zhou

Institute of frontier and interdisciplinary science, Shandong University

12 Dec. 2024

CEPC TDAQ meeting

## Outline

- Motivation

- Deep Neural Network (DNN) model

- Development of DNN model with python

- High Level Synthesi (HLS) with Vitis

- Testing IP cores in Vivado

## Motivation

- Study the CDC DNN trigger and master the implementation process of DNN in FPGA

- Optimize the model and observe changes in performance

- PLAN: Investigating the possiblity of using more input variables in DNN

models, such as ADC signals and momentum

PLAN: Development of DNN model to Versal ACAP

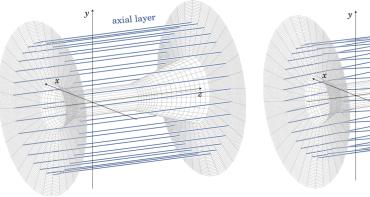

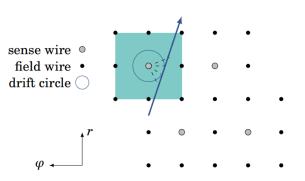

## Central drift chamber

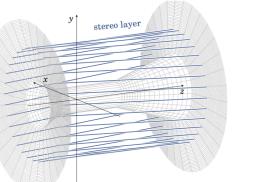

A drift cell of the CDC is formed of one sense

wire and eight field wires

- A hit on an axial wire provides coordinates in the transverse plane(2D)(Φ,r)

- By combining axial and stereo hits, a three dimensional track can be reconstructed(3D)

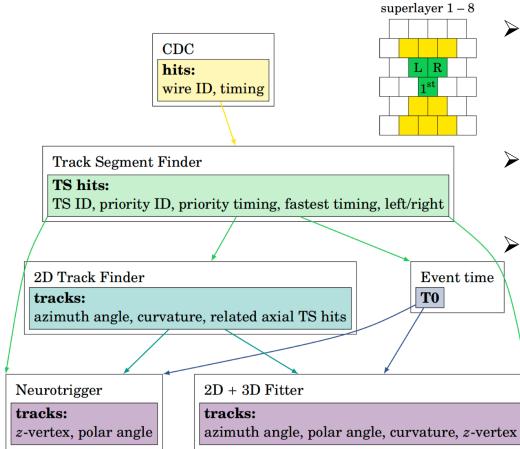

## The CDC track trigger

- The Belle II trigger consists of two

levels: the first level trigger(hardware)

and the high level trigger(software)

- CDC track trigger provides charged track information

- The track finding for the trigger is based

on track segments("TS")

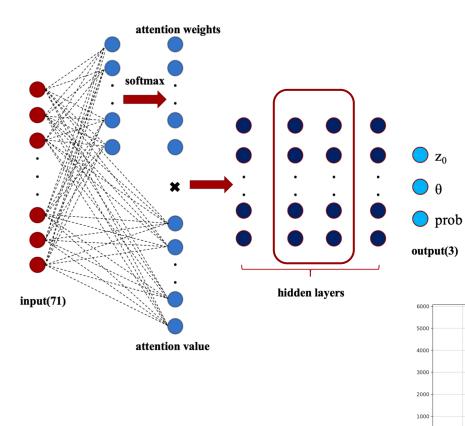

## Deep Neural Network (DNN) model

• Extract a track segment from each

super layer

• Every track segment (TS) contains a set of  $\alpha$ ,t<sub>drift</sub> and  $\Phi$

- DNN trigger : 2D track candidates+ Drift time for all other wires in the stereo wire

- Input : α,t<sub>drift</sub>, phi of priority wire, t<sub>drift</sub> of all other 10 wires for every TS(3\*9+11\*4=71)

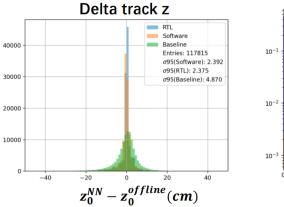

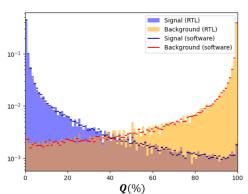

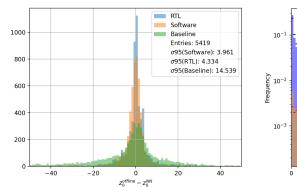

- Output :  $z_0, \theta_0$ , classifier output (Q)

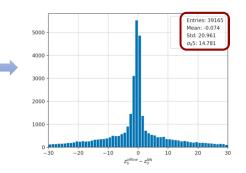

## Development of DNN model with python

• Using pytorch lib for model

building and training

- Add two hidden layers

- Modify learning rates

Entries: 391

Mean: -0.450

Std: 20.490

σ<sub>9</sub>5: 14.121

20

30

10

-30

-20

-10

$z_0^{offline} - z_0^N$

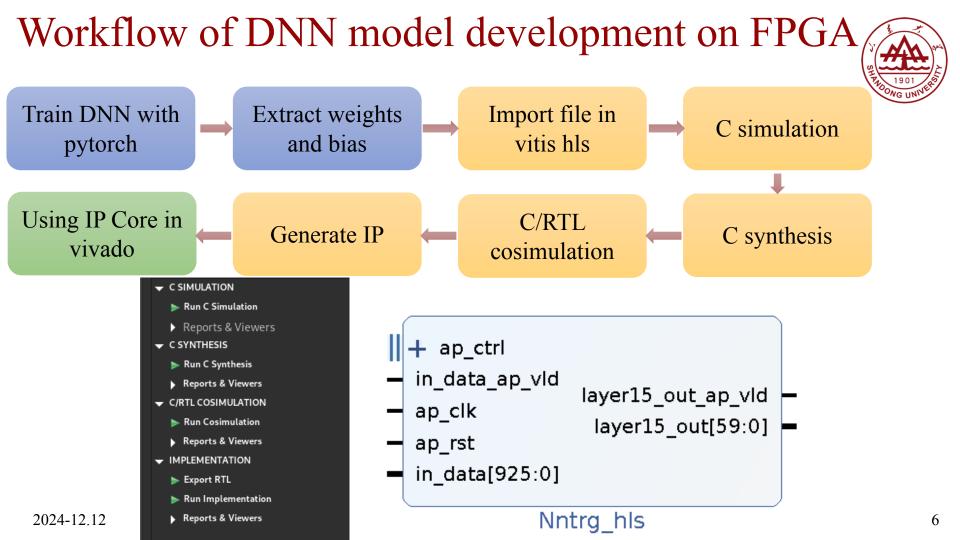

## Development flow with Vitis HLS

A typical flow using HLS has the following steps:

- Convert python based model to C/C++ model with hls4ml (Optional)

- Write the algorithm using C/C++ with a target architecture in mind

- Verify the functionality at the behavioral level

- Generate the RTL based model

- Verify the functionality of the generated RTL model

Optimizing performance: "#pragma HLS"

#### #pragma HLS array\_partition variable = w2 complete dim = 0

- Generate multiple small memories

- Increases the amount of read and write ports for the storage

#### 2024-12.12

## Performance

| Criteria                                                  | Guideline | Actual | Status |

|-----------------------------------------------------------|-----------|--------|--------|

| LUT                                                       | 70%       | 44.22% | ОК     |

| FD                                                        | 50%       | 8.00%  | ок     |

| LUTRAM+SRL                                                | 25%       | 2.02%  | ОК     |

| CARRY8                                                    | 25%       | 25.59% | REVIEW |

| MUXF7                                                     | 15%       | 0.00%  | ОК     |

| DSP                                                       | 80%       | 25.58% | ОК     |

| RAMB/FIFO                                                 | 80%       | 0.26%  | ОК     |

| DSP+RAMB+URAM (Avg)                                       | 70%       | 12.92% | ок     |

| BUFGCE* + BUFGCTRL                                        | 24        | 0      | ОК     |

| DONT_TOUCH (cells/nets)                                   | 0         | 0      | ОК     |

| MARK_DEBUG (nets)                                         | 0         | 0      | ок     |

| Control Sets                                              | 17370     | 83     | ОК     |

| Average Fanout for modules > 100k cells                   | 4         | 2.83   | ОК     |

| Max Average Fanout for modules > 100k cells               | 4         | 3.09   | ок     |

| Non-FD high fanout nets > 10k loads                       | 0         | 2      | REVIEW |

| TIMING-6 (No common primary clock between related clocks) | 0         | 0      | ОК     |

| TIMING-7 (No common node between related clocks)          | 0         | 0      | ОК     |

| TIMING-8 (No common period between related clocks)        | 0         | 0      | ок     |

| TIMING-14 (LUT on the clock tree)                         | 0         | 0      | ок     |

| TIMING-35 (No common node in paths with the same clock)   | 0         | 0      | ок     |

| Number of paths above max LUT budgeting (0.425ns)         | 0         | 0      | ок     |

| Number of paths above max Net budgeting (0.298ns)         | 0         | 0      | ок     |

#### Virtex Ultra XCVU160

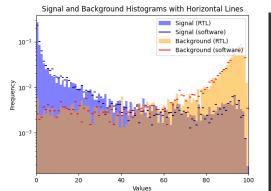

| <pre>baseline(NN)/software(DNN)/RTL(HLS)</pre> |

|------------------------------------------------|

|------------------------------------------------|

| +                                                                                              |           |        |              |   |

|------------------------------------------------------------------------------------------------|-----------|--------|--------------|---|

| Design Summary                                                                                 |           |        |              |   |

| impl_1<br>  xcvc1902-vsva2197-1 P-e-S                                                          |           |        |              |   |

| +                                                                                              | +         |        |              |   |

| Criteria                                                                                       | Guideline | Actual | Status       |   |

| ·                                                                                              |           |        |              |   |

| LUT                                                                                            | 70%       | 87.69% | REVIEW       |   |

| FD                                                                                             | 50%       | 14.26% | 0K           |   |

| LUTRAM+SRL                                                                                     | 25%       | 4.08%  | 0K           |   |

| LOOKAHEAD8                                                                                     | 25%       | 21.99% | 0K           |   |

| LUT Combining                                                                                  | 20%       | 2.23%  | 0K           |   |

| DSP                                                                                            | 80%       | 4.07%  | 0K           |   |

| RAMB                                                                                           | 80%       | 0.88%  | 0K           |   |

| URAM                                                                                           | 80%       | 0.00%  | 0K           |   |

| DSP+RAMB+URAM (Avg)                                                                            | 70%       | 2.48%  | 0K           |   |

| BUFGCE* + BUFGCTRL                                                                             | 24        |        | 0K           |   |

| DONT_TOUCH (cells/nets)                                                                        | 0         | Θ      | ОК           |   |

| MARK_DEBUG (nets)                                                                              | 0         | 0      | 0K           |   |

| Control Sets                                                                                   | 16872     | 491    | 0K           | 4 |

| Average Fanout for modules > 100k cells                                                        | 4         | 2.75   | 0K           |   |

| Max Average Fanout for modules > 100k cells                                                    | 4         | 3.31   | 0K           |   |

| Non-FD high fanout nets > 10k loads                                                            | 0         | 3      | REVIEW       |   |

|                                                                                                | +         |        | ++<br>       |   |

| TIMING-6 (No common primary clock between related clocks)                                      | 0         | 0      | 0K  <br> 0K  |   |

| TIMING-7 (No common node between related clocks)                                               |           | 0      |              |   |

| TIMING-8 (No common period between related clocks)<br>  TIMING-14 (LUT on the clock tree)      | 0<br>  0  | 0      | UK  <br>  OK |   |

| TIMING-14 (LOT on the clock tree)<br>  TIMING-35 (No common node in paths with the same clock) | 10        | 0      |              |   |

| TIMING-55 (NO COMMON HOUSE IN PACHS WITH THE SAME CLOCK)                                       |           |        |              |   |

| Number of paths above max LUT budgeting (0.449ns)                                              | 1 0       |        | REVIEW       |   |

| Number of paths above max Net budgeting (0.302ns)                                              | İŏ        | 23     | REVIEW       |   |

| +                                                                                              | +         |        |              |   |

|                                                                                                |           |        |              |   |

#### Versal AI Core XCVC1902

#### 2024-12.12

## Latency(testbench)

|                                 |                                         | 110.000 ns 850.000 ns                                                                                     | THE ISONG UNIVERSI   |

|---------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------|

| Name                            | Value 0.000 ns 1                        | 00.000 ns 1200.000 ns 1800.000 ns 1400.000 ns 1500.000 ns 1600.000 ns 1700.000 ns 1800.000 ns 1800.000 ns | ONG UNIVE            |

| lap_clk                         | 1                                       |                                                                                                           |                      |

| l⊌ ap_rst                       | 0                                       |                                                                                                           |                      |

| ¼ ap_start<br>> ♥ indata[925:0] | 1                                       |                                                                                                           |                      |

| > Indata[925:0]                 | 000000000000000000000000000000000000000 | <u>∞∞∞∞∞</u>                                                                                              |                      |

| la ap_idle                      |                                         |                                                                                                           |                      |

| lap_ready                       |                                         |                                                                                                           | initial:             |

| layer11_out_ap_vld              | 1                                       |                                                                                                           | IIIItiai.            |

| > 10 layer11_out[59:0]          | 83800c5a0                               | xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                    |                      |

| > 😻 fd0[31:0]                   | fffble0 XXXXXXXX                        | ffffble0                                                                                                  | 74clock              |

| > 😻 index[31:0]                 | 0000004a 00000000                       |                                                                                                           | X                    |

| > 😻 status0[31:0]               | 00000001 XXXXXXXX                       | 0000001                                                                                                   |                      |

| ¼ float_data                    | -0.1420898 0.0                          | ━>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>                                                                    | XX                   |

| > 😻 PERIOD[31:0]                | 0000000a                                | 0000003                                                                                                   |                      |

|                                 |                                         |                                                                                                           |                      |

|                                 |                                         | 920.000                                                                                                   | 15 .                 |

| Name                            | Value                                   | 110.000 ns                                                                                                | 15                   |

|                                 | value                                   | 0.000 ns   200.000 ns   400.000 ns   600.000 ns   800.000 ns   100.000 ns                                 |                      |

| 🖁 ap_clk                        | 1                                       |                                                                                                           |                      |

| 👃 ap_rst                        | 0                                       |                                                                                                           |                      |

| 😼 ap_start                      | 1                                       |                                                                                                           |                      |

| > 😻 indata[925:0]               | 000000000000000000000000000000000000000 |                                                                                                           |                      |

| 🐻 layer15_out_ap_vld            | 1                                       |                                                                                                           | optimize:            |

| lap_done                        | 1                                       |                                                                                                           | opullin              |

| ap_ready                        | 0                                       |                                                                                                           | optimize:<br>81clock |

| ap idle                         | 0                                       |                                                                                                           | OTCIOCK              |

|                                 | 44200d3e00f8000                         | XXX00XXX00XXX00 X44200d.                                                                                  |                      |

| > 1 layer15_out[59:0]           |                                         |                                                                                                           |                      |

| > 😻 fd0[31:0]                   | ffffble0                                |                                                                                                           |                      |

| > 😻 index[31:0]                 | 00000047                                |                                                                                                           |                      |

| > 😻 status0[31:0]               | 00000001                                | 00000001                                                                                                  |                      |

| 🕌 float_data                    | 0.166015625                             | 0.0 0.1ee015e25                                                                                           |                      |

|                                 |                                         |                                                                                                           |                      |

| > 😻 PERIOD[31:0]                | 0000000a                                | €0000000                                                                                                  |                      |

9

## Next plan

- Further optimize the model and perform pruning

- Investigating the possibility of using more input variables in DNN models, such as ADC signals and momentum(Hope to receive more suggestions)

- Check the size of the model scale(Utilization, latency)

- Predicting the use of the next generation UT5 board

- Deploy the neutral networks to Versal ACAP

- First step: deploy the DNN model into Versal AI engine

- Further plan: deploy the NN model on Versal DPU

# Thanks for your listening

## Back up

## Virtex UltraScale XCVU160

| Design Summary<br>  impl_1<br>  xcvul60_CIV-flgc2104-2-e                                                                                                                                                                                                                                                                             |                                                                                                                                                                         |                                                                                                                                             |                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| +<br>  Criteria                                                                                                                                                                                                                                                                                                                      | +<br>  Guideline                                                                                                                                                        | Actual                                                                                                                                      | Status                                                                          |

| LUT<br>FD<br>LUTRAM+SRL<br>[CARRY8<br>MUXF7<br>LUT Combining<br>DSP<br>RAMB/FIF0<br>DSP+RAMB+URAM (Avg)<br>BUFGCE* BUFGCE* BUFGCE*<br>DONT TOUCH (cells/nets)<br>MARK_DEBUG (nets)<br>[Control Sets<br>Average Fanout for modules > 100k cells<br>Max Average Fanout for modules > 100k cells<br>Non-FD high fanout nets > 10k loads | 70%<br>  50%<br>  25%<br>  15%<br>  25%<br>  25%<br>  25%<br>  25%<br>  25%<br>  25%<br>  25%<br>  26%<br>  26%<br>  70%<br>  24<br>  0<br>  0<br>  17370<br>  4<br>  0 | 50.79%  <br>10.22%  <br>29.50%  <br>0.00%  <br>11.29%  <br>68.33%  <br>0.26%  <br>34.30%  <br>0<br>0<br>0<br>266  <br>2.44  <br>3.67  <br>4 | 0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0K<br>0 |

| TIMING-6 (No common primary clock between related clocks)<br>TIMING-7 (No common node between related clocks)<br>TIMING-8 (No common period between related clocks)<br>TIMING-14 (LUT on the clock tree)<br>TIMING-35 (No common node in paths with the same clock)<br>Number of paths above max LUT budgeting (0.425ns)             | 0<br>  0<br>  0<br>  0<br>  0                                                                                                                                           | 0<br>  0<br>  0<br>  0<br>  0                                                                                                               | ОК<br>  ОК<br>  ОК<br>  ОК<br>  ОК                                              |

| Number of paths above max Lor budgeting (0.425hs)<br>  Number of paths above max Net budgeting (0.298hs)<br>+                                                                                                                                                                                                                        | 0<br>  0<br>+                                                                                                                                                           | 1                                                                                                                                           | REVIEW                                                                          |

|                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                         |                                                                                                                                             |                                                                                 |

| Implementation  | tool:   |         | Vivac  | lo v.202 | 3.2   |      |

|-----------------|---------|---------|--------|----------|-------|------|

| Project:        |         | DNN_1   |        |          |       |      |

| Solution:       |         | soluti  |        |          |       |      |

| Device target:  |         |         |        |          |       |      |

| Report date:    |         | Sat De  | c 07 0 | 01:58:02 | CST : | 2024 |

|                 |         |         |        |          |       |      |

| #=== Post-Imple |         | tion Re | source | e usage  | ===   |      |

| SLICE:          | 0       |         |        |          |       |      |

|                 | 0542    |         |        |          |       |      |

| FF: 18          | 9296    |         |        |          |       |      |

| DSP:            | 1066    |         |        |          |       |      |

| BRAM:           | 17      |         |        |          |       |      |

| URAM:           | 0       |         |        |          |       |      |

| LATCH:          | 0       |         |        |          |       |      |

| SRL: 1          | 7550    |         |        |          |       |      |

| CLB: 7          | 3455    |         |        |          |       |      |

|                 |         |         |        |          |       |      |

| #=== Final timi | .ng === | =       |        |          |       |      |

| CP required:    |         |         |        | 4.000    |       |      |

| CP achieved pos | t-synt  | thesis: |        | 4.410    |       |      |

| CP achieved pos | t-impl  | lementa | tion:  | 7.624    |       |      |

| Timing not met  |         |         |        |          |       |      |

|                 |         |         |        |          |       |      |

|          | +<br>  Design Summary<br>  impll<br>  xcvu160-flgb2104-2-e                                                                                                                                                                                                                                                                                 |                                                                                                            |                                                                                                                      |                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

|          | Criteria                                                                                                                                                                                                                                                                                                                                   | Guideline                                                                                                  | Actual                                                                                                               | Status                                                     |

| optimize | LUT<br>FD<br>LUTRAM+SRL<br>LUTRAM+SRL<br>CARRY8<br>MUXF7<br>LUT Combining<br>DSP<br>RAMB/FIF0<br>DSP-RAWB-URAM (Avg)<br>BUFGCF + BUFGCTRL<br>DONT TOUCH (cells/nets)<br>MARK_DEBUG (nets)<br>Control Sets<br>Average Fanout for modules > 100k cells<br>Max Average Fanout for modules > 100k cells<br>Non-FD high fanout nets > 10k loads | 70%<br>50%<br>25%<br>25%<br>25%<br>28%<br>80%<br>80%<br>80%<br>70%<br>24<br>0<br>0<br>17370<br>4<br>4<br>4 | 64.08%<br>12.59%<br>8.13%<br>9.00%<br>12.84%<br>96.03%<br>0.26%<br>48.15%<br>2<br>0<br>0<br>255<br>2.57<br>3.59<br>6 | 0K  <br>0K  <br>0K  <br>0K  <br>0K  <br>0K  <br>0K  <br>0K |

|          | TIMING-6 (No common primary clock between related clocks)<br>  TIMING-7 (No common node between related clocks)<br>  TIMING-8 (No common period between related clocks)<br>  TIMING-14 (LUT on the clock tree)<br>  TIMING-15 (No common node in paths with the same clock)                                                                | 0<br>  0<br>  0<br>  0                                                                                     | 0<br>0<br>0<br>0<br>0                                                                                                | 0K  <br>0K  <br>0K  <br>0K  <br>0K                         |

|          | Number of paths above max LUT budgeting (0.425ns)<br>  Number of paths above max Net budgeting (0.298ns)<br>+                                                                                                                                                                                                                              | 0<br>  0                                                                                                   | 0                                                                                                                    | ок  <br>  ок  <br>  ок                                     |

| Project<br>Solutio | on:<br>target: |         | new_<br>solu<br>xcvu | _hide<br>ution<br>u160- | elaye<br>1<br>flgb | er<br>02104- |        | 2024 |

|--------------------|----------------|---------|----------------------|-------------------------|--------------------|--------------|--------|------|

| #=== Pc            | ost-Imple      | menta   | tion                 | Reso                    | ource              | usad         | ie === |      |

| SLICE:             |                | 0       |                      |                         |                    | -            |        |      |

| LUT:               | 59             | 3640    |                      |                         |                    |              |        |      |

| FF:                | 23             | 3306    |                      |                         |                    |              |        |      |

| DSP:               |                | 1498    |                      |                         |                    |              |        |      |

| BRAM:              |                | 17      |                      |                         |                    |              |        |      |

| URAM:              |                | Θ       |                      |                         |                    |              |        |      |

| LATCH:             |                | 0       |                      |                         |                    |              |        |      |

| SRL:               |                | 7871    |                      |                         |                    |              |        |      |

| CLB:               | 8              | 9668    |                      |                         |                    |              |        |      |

|                    |                |         |                      |                         |                    |              |        |      |

|                    | lnal timi      | .ng === | =                    |                         |                    |              |        |      |

| CP requ            |                |         |                      |                         |                    | 4.000        |        |      |

|                    | leved pos      |         |                      |                         |                    | 4.324        |        |      |

|                    | leved pos      | t-impl  | lemer                | ntati                   | .on:               | 9.196        |        |      |

| Timing             | not met        |         |                      |                         |                    |              |        |      |

#### initial

## Some questions

| Modules & Loops                                                       | lssue Type             | Violation Type | Distance | Slack | Latency(cycles) | Latency(ns) | Iteration Latency | Interval | Trip Count Pipelir |

|-----------------------------------------------------------------------|------------------------|----------------|----------|-------|-----------------|-------------|-------------------|----------|--------------------|

| ■ NNTRG_hls                                                           | 💧 Timing Violation     |                |          |       | 85              | 340.000     |                   | 4        |                    |

| custom_dense_hybrid_ap_fixed_13_1_5_3_0_ap_fixed_16_6_5_3_0_config2_s |                        |                |          |       | 37              | 148.000     |                   | 4        |                    |

| leaky_relu_ap_fixed_ap_fixed_16_6_5_3_0_LeakyReLU_config3_s           |                        |                |          |       | 0               | 0.0         |                   |          |                    |

| custom_dense_hybrid_ap_fixed_16_6_5_3_0_ap_fixed_16_6_5_3_0_config4_s | 🔼 Timing Violation     |                |          |       | 4               | 16.000      |                   | 4        |                    |

| softmax_stable_ap_fixed_ap_fixed_16_6_5_3_0_Softmax_config5_s         |                        |                |          |       | 16              | 64.000      |                   |          |                    |

| custom_dense_hybrid_ap_fixed_16_6_5_3_0_ap_fixed_16_6_5_3_0_config6_s | 🔼 Timing Violation     |                |          |       | 4               | 16.000      |                   | 4        |                    |

| multiply_ap_fixed_ap_fixed_16_6_5_3_0_ap_fixed_16_6_5_3_0_config7_s   |                        |                |          |       | 1               | 4.000       |                   |          |                    |

| custom_dense_hybrid_ap_fixed_16_6_5_3_0_ap_fixed_16_6_5_3_0_config8_s | 💧 Timing Violation     |                |          |       | 4               | 16.000      |                   | 4        |                    |

| leaky_relu_ap_fixed_ap_fixed_16_6_5_3_0_LeakyReLU_config9_s           |                        |                |          |       | 0               | 0.0         |                   |          |                    |

| custom_dense_hybrid_ap_fixed_ap_fixed_16_6_5_3_0_config10_s           | \land Timing Violation |                |          |       | 4               | 16.000      |                   | 4        |                    |

| leaky_relu_ap_fixed_ap_fixed_16_6_5_3_0_LeakyReLU_config11_s          |                        |                |          |       | 0               | 0.0         |                   |          |                    |

| custom_dense_hybrid_ap_fixed_ap_fixed_16_6_5_3_0_config12_s           | \land Timing Violation |                |          |       | 4               | 16.000      |                   | 4        |                    |

| leaky_relu_ap_fixed_ap_fixed_16_6_5_3_0_LeakyReLU_config13_s          |                        |                |          |       | 0               | 0.0         |                   |          |                    |

| custom_dense_hybrid_ap_fixed_ap_fixed_16_6_5_3_0_config14_s           | 🔔 Timing Violation     |                |          |       | 3               | 12.000      |                   | 4        |                    |

| ◎ tanh ap fixed 16 6 5 3 0 ap fixed 20 1 5 3 0 Tanh config15 s        |                        |                |          |       | 3               | 12.000      |                   | 1        |                    |

|                       |                                         |           | 110.00 | 0 nc |        |         |       |       |         | _        |       | 0 ns<br>10 ns |       |       |       |      |      |     |       |        |         |           |     |

|-----------------------|-----------------------------------------|-----------|--------|------|--------|---------|-------|-------|---------|----------|-------|---------------|-------|-------|-------|------|------|-----|-------|--------|---------|-----------|-----|

| Name                  | Value                                   | 0.000 ns  | 110.00 |      | 200.00 | 00 ns   |       |       | 400.000 |          |       |               |       | 600.0 | 00 ns | . 1  |      |     | 800   | . 000  | ns      |           |     |

| ¼ ap_clk              | 1                                       |           |        |      |        |         | ninni |       | Innin   |          |       |               |       | nnnn  | nnn   |      | uuuu |     |       |        |         |           | ΠΠ  |

| 😼 ap_rst              | 0                                       |           |        |      |        |         |       |       |         |          |       |               |       |       |       |      |      |     |       |        |         |           |     |

| 😼 ap_start            | 1                                       |           |        |      |        |         |       |       |         |          |       |               |       |       |       |      |      |     |       |        |         |           |     |

| > 😻 indata (925:0)    | 000000000000000000000000000000000000000 | 000000000 | XXXX   | XXXX | 00     | XXX     | X     |       | XXXX    | (X)C     | 00000 | 00000         | 00000 | χ     | X     | XXXX | зХ   | 0)  | (XXX  | XXO    | $\odot$ | 00000000  | 0)  |

| 🔓 ap_done             | 1                                       |           |        |      |        |         |       |       |         |          |       |               | Π     |       |       | Л    |      |     |       | $\Box$ |         |           |     |

| 🔓 ap_idle             | 0                                       |           |        |      |        |         |       |       |         |          |       |               |       |       |       |      |      |     |       |        |         |           |     |

| 🔓 ap_ready            | 0                                       |           | Л      |      | П      |         | ПШП   |       |         |          |       | Π             | Π     |       |       |      |      |     | П     |        |         |           |     |

| 🔓 layer15_out_ap_vld  | 1                                       |           |        |      |        |         |       |       |         |          |       |               |       |       |       |      |      |     |       |        |         |           |     |

| > 😻 layer15_out[59:0] | 44200d3e00f8000                         |           |        | XX   | XOOXXX | 00XXX00 | 0     |       |         | 4        | Х     | 4             | 4420  | 0d    | XXXO  | 0X   | 4    | XXX | boxxo | (00)X  | (44     | 200d3e00f |     |

| > 😻 fd0[31:0]         | ffffble0                                | XXXXXXXXX |        |      |        |         |       |       |         |          |       | ffffl         | leO   |       |       |      |      |     |       |        |         |           |     |

| > 😻 index[31:0]       | 00000025                                | 00000000  | XXXX   | XXXX | XXXX   | XXXX    |       | XXXXX | XXXXX   | $\infty$ | XXX   | XXX           | XXX   | XXX   | XXXX  | XXXX | XXXX | XXX | скхх  | XXX    | XXX     | XXXXXX    | XXX |

| > 😻 status0[31:0]     | 0000001                                 | XXXXXXXXX |        |      |        |         |       |       |         |          |       | 00000         | 0001  |       |       |      |      |     |       |        |         |           |     |

| 🐌 float_data          | 0.0                                     | 0.0       | XXXX   | XXXX | XXXX   | XXX     | XX    | XXXXX | ÷XXXXX  | (X)C     |       | 0.0           | )     |       | XŌX   | XXXX | -1.0 | XXX | скхх  | XXX    | 0XX)    | 0.0       |     |

| > 😻 PERIOD[31:0]      | 0000000a                                |           |        |      |        |         |       |       |         | 0 00     | 0000  | а             |       |       |       |      |      |     |       |        |         |           |     |

|                       |                                         |           |        |      |        |         |       |       |         |          |       |               |       |       |       |      |      |     |       |        |         |           |     |