## **CEPC Silicon Tracker Progress Report (12)**

Qi Yan on behalf of the Silicon Tracker Group Nov 19, 2024, IHEP

## **Upcoming MPW Submission Plan for HVCMOS Pixels**

- Submission plan update for 2025:

- Two MPW windows in the first half of 2025: January and April

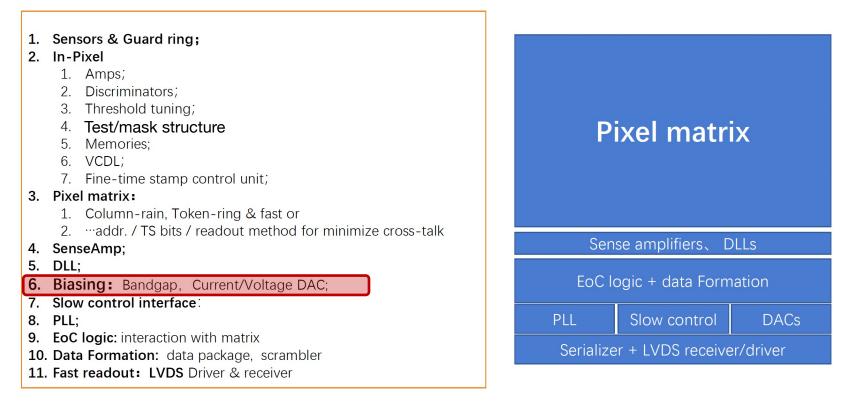

- Initial plan: 1 MPW to implement all periphery functions

- To demonstrate part of key performance by ref-TDR release (June 2025?):

- 1st submission in January: all basic functions except DAC

- 2nd submission in April or later 2025: DAC included, all other modules optimized

## Preparation Towards Next Submission (COFFEE3 ...)

- 15 active designers:

- preparation for some modules started right after COFFEE2

- A few modules already in the layout phase

- However, it remains an extremely challenging task

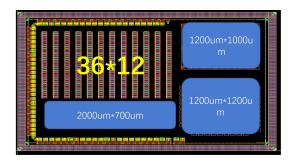

General layout planning Pixel size: 34 μm×144 μm MPW size: 3 mm×4 mm

Staff and students from IHEP, NWPU, DMU, SDU, NJU, ...