# Progress of CEPC ref-TDR TDAQ

$Fei\ Li$  On behalf of CEPC TDAQ Group

#### **Progress of TDAQ**

#### ■ TDR draft v0.2

- First draft: Intro/requirements

- Partial draft: overview/simulation/trigger/DAQ

- Elec. & TDAQ meeting

- Nov. 14<sup>th</sup> (Thu. morning)

- Discussed trigger and clock distribution schema

- TDAQ meeting

- Nov. 14<sup>th</sup> (Thu. afternoon)

- https://indico.ihep.ac.cn/event/24194/

- Trigger rate discussion

- New physics trigger requirements(single photon)

- Trigger simulation progress

- TDAQ overview architecture discussion

| Chapter 12 Trigger and Data Acquisition                     | 1 |

|-------------------------------------------------------------|---|

| 12.1 Introduction                                           | 1 |

| 12.2 Requirements                                           | i |

| 12.2.1 Requirements                                         | 1 |

| 12.2.2 Event rate & background rate estimation              | 1 |

| 12.3 Overview Design                                        | 1 |

| 12.3.1 Design consideration                                 | 1 |

| 12.3.1 Design consideration  12.3.2 TDAQ design structure   | 1 |

|                                                             | 1 |

| 12.4 Trigger Simulation and Algorithms                      | 2 |

| 12.4.1 Physics Signatures and primitives with sub-detectors | 2 |

| 12.4.2 Sub-detectors trigger algorithms                     |   |

| 12.4.3 Global trigger algorithms                            | 4 |

| 12.5 Hardware Trigger                                       | 5 |

| 12.5.1 Previous experience on large facilities              | 5 |

| 12.5.2 System architecture                                  | 5 |

| 12.5.3 Common Trigger Board                                 | 5 |

| 12.5.4 Trigger Control and Distribution                     | 5 |

| 12.5.5 Resource cost estimation                             | 5 |

| 12.6 Software and High Level Trigger                        | 5 |

| 12.6.1 Previous experience on large facilities              | 5 |

| 12.6.2 HLT software                                         | 5 |

| 12.6.3 Study of GPU usage in the HLT                        | 5 |

| 12.6.4 Study of FPGA usage in the HLT                       | 5 |

| 12.6.5 Model for CPU estimation                             | 5 |

| 12.7 Data Acquisition System                                | 5 |

| 12.7.1 Previous experience on large facilities              | 5 |

| 12.7.2 Overview of System Functionality                     | 5 |

| 12.7.3 Detector Readout                                     | 5 |

| 12.7.4 Dataflow                                             | 5 |

| 12.7.5 Online Software                                      | 5 |

| 12.7.6 Hardware Deployment                                  | 5 |

| 12.8 Detector Control System                                | 5 |

| 12.8.1 Control and monitoring requirements                  | 5 |

| 12.8.2 Experience in detector control system                | 5 |

| 12.8.3 Detector control system software architecture design | 5 |

| 12.9 Experiment Control System                              | 5 |

| 12.9.1 Requirements                                         | 5 |

| 12.9.2 Experience in experiment control system              | 5 |

| 12.9.3 Software framework design                            | 5 |

| 12.9.4 Online Data Center                                   | 5 |

| 12.9.5 Infrastructure and services                          | 5 |

| 12.10Summary                                                | 5 |

| 12.105ummary                                                |   |

#### **TCDS-Trigger Clock Distribution System**

#### TCDS/TTC

- Clock, BC0, Trigger, orbit start signal distribution

- Full, ERR signal feed back to TCDS/TTC and mask or stop L1A

- TCDS-Trigger Clock Distribution System

- TTC- Trigger, Timing and Control

- DCTD-Data Concentrator and Timing Distribution

- BEE-Backend board Electronic

TDAQ are only responsible for system-level distribution, each system is then responsible for its own internal distribution.

#### **Trigger & Data Rate**

- Compress background -> 1% @ L1

- Compress background -> 0.1% @ HLT

- Data size per bunch cross

- 300Kbytes @ Higgs

- Unknown @Z

- Event size < 2 Mbyte</p>

- Occupancy and read out window

- L1 trigger rate

- 13~120 kHz @ Higgs&low lum. Z

- DAQ data rate

- Read out: 26~240 GB/s

- @ Higgs & low lum. Z

- Storage: 0.3~7.5 GB/s

|                                         | Higgs | Z(10MW) | Z(50MW) | W     | tt     |

|-----------------------------------------|-------|---------|---------|-------|--------|

| Luminosity(10E34/cm2/s)                 | 8.3   | 38      | 192     | 26.7  | 0.8    |

| Bunch space(ns)                         | 346.2 | 69.3    | 23.1    | 253.8 | 4523.1 |

| Bunch cross rate(MHz)                   | 1.34  | 12      | 39.4    | 6.5   | 0.18   |

| Raw data rate before trigger (TBytes/s) | 0.4   | 3.6     | 11.82   | 1.95  | 0.048  |

| Physical event rate(kHz)                | 0.008 | 13.2    | 66      | 0.1   | 0.002  |

| L1 trigger rate(kHz)                    | 13    | 120     | 400     | 65    | 2      |

| DAQ readout rate(Gbyte/s)               | 26    | 240     | 800     | 130   | 4      |

| High level trigger rate(kHz)            | 1     | 25      | 100     | 6     | 1      |

| DAQ storage rate(Gbytes/s)              | 0.3   | 7.5     | 30      | 1.8   | 0.3    |

## Backup

## **Working Plan for TDR**

- 先根据河南技术方案修改一个版本,一周。后面三周扩充内容。

- 模拟:

- 第一周:事例率 (Cal+Muon), muon tracking

- 双gamma光子应对策略

- 第二周:L1算法(Cal+Muon)算法, TDR editing

- 第三周: TPC、OTK tracking, low lum. Z background.

- 第四周: Global trigger start, TDR draft 0.1

- 12月, TDR draft 1.0

- HLT algorithm 结果

- Global trigger

- trigger efficiency

| Ch      | apter | 12 TDA    | Q and online                            |

|---------|-------|-----------|-----------------------------------------|

|         | 12.1  | Introduct | tion                                    |

|         | 12.2  | Requiren  | nents and Design Considerations         |

|         |       | 12.2.1 F  | Requirements                            |

|         |       | 12.2.2 I  | Event rate & background rate estimation |

|         |       | 12.2.3    | Technology survey                       |

|         |       | 12.2.4    | ΓDAQ policy consideration               |

|         |       | 12.2.5    | TDAQ Interface with electronics         |

|         | 12.3  | Trigger S | Simulation and Algorithms               |

|         | 12.4  | Hardwar   | e Trigger                               |

|         |       | 12.4.1 F  | Previous experience on large facilities |

| d       |       | 12.4.2    | System architecture                     |

| <u></u> |       | 12.4.3    | Common Trigger Board                    |

|         |       | 12.4.4    | Trigger Control and Distribution        |

|         |       | 12.4.5 H  | Resource cost estimation                |

|         | 12.5  | Software  | and High Level Trigger                  |

|         | 12.6  | Data Acc  | quisition System                        |

|         |       | 12.6.1 I  | Previous experience on large facilities |

|         |       | 12.6.2    | Overview of System Functionality        |

|         |       | 12.6.3 I  | Detector Readout                        |

|         |       | 12.6.4 I  | Dataflow                                |

|         |       | 12.6.5 N  | Network                                 |

|         |       | 12.6.6    | Online Software                         |

|         | 12.7  | Detector  | Control System                          |

|         |       |           | ent Control System                      |

|         | 12.9  | Summar    | y                                       |

## **Working Plan for TDR**

#### ■ 硬件触发

- 11月

- Hardware trigger structure design for TDR

- trigger board/ TTC detailing

- BEE interface

- basic trigger primitives

- 12月:

- trigger primitives for each L1 detectors

- common trigger board structure finalize

- L1 algorithm deploment design, boards num

### **Working Plan for TDR**

#### HLT

- 11月

- 编辑一页的FPGA加速

- GPU,概念性描述

- 离线软件状况

#### DAQ

- 11月

- system architecture

- software layer data flow

- RDMA/GPU/FPGA/Mem buffer

- 12月

- Network/hardware

- Online software

#### DCS

- 11月

- DCS requirement from each detectors

- framework design

- ECS

- 11月

- framework design

- control network

- 12月

- IT infrastructure

- hardware

- control/computing room

- monitoring

## Findings--revised

- The baseline plan is to transmit the full raw data to the front-end electronics and connect the trigger to the back-end electronics.

- Transmit the full raw data from front-end electronics(on-detector) to backend electronics(off-detector)

- A hierarchical trigger scheme is foreseen to bring event data rates down from ~3MHz to ~1kHz in ZH running and ~40MHz to ~100kHz at the Z pole.

- The bunch cross rate in ZH running is about 1.34 MHz when bunch space is 346.2 ns (2.9 MHz) and there is 54% bunch train gap.

#### Comments

- The detailed (bottom-up) design of the TDAQ must await further details on the sub detector design.

- We will closely follow the design of each sub detector. Especially background study and data rate estimation from each sub detectors.

- Work on the trigger primitives is needed to bring the rate down to an acceptable input for the second-level trigger, and to inform further planning for the processing farms in the DAQ design. Should it be needed, a track trigger could provide a powerful additional primitive.

- More simulation works on trigger primitive and more discussion with physics and detector experts are needed. Track trigger simulation will be next main work.

- High-level triggering will also need to weigh the physics-versus-bandwidth tradeoff for lower-energy events, e.g. from gamma-gamma collisions.

- We need more study for low-energy events of beam induced background. And few gamma-gamma collisions are included in the available background sample data.

#### Recommendations

- A simple simulation of sub detector-based trigger inputs using simple, robust algorithms should be prioritized to allow more detailed specification of the requirements for TDAQ hardware and identify areas that need further attention. This should include an appropriate safety factor for beam-related backgrounds.

- Basic trigger simulation study for each sub detectors are in progress.

- And the safety factor needs to be discussed carefully.

- Further work should include an evaluation of benefits of implementing a track trigger as a complement to the calorimeter and muon primitives, and to clarify the bandwidth foreseen for gamma-gamma events.

- We will move forward this after finish simple trigger simulation.

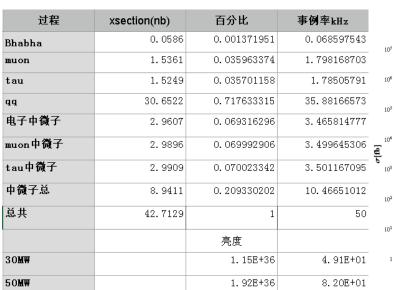

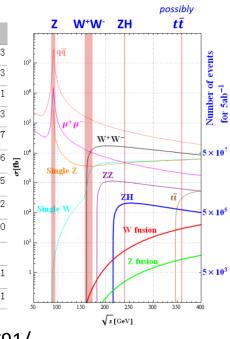

## **Physical Event Rate**

- Higgs 240GeV(30MW/50MW)

- BX rate: 0.8(1.74)/1.34(2.9) MHz

- Physical event rate: 5Hz/8Hz (Higgs: 0.02Hz)

- Z pole 91GeV(10MW/50MW)

- BX rate: 12(14.5)/39.4(43.3) MHz

- Physical event rate: 13.2kHz/66kHz

|                                                                        | Higgs       | 7        | Z        | W          | tť           |

|------------------------------------------------------------------------|-------------|----------|----------|------------|--------------|

| SR power per beam (MW)                                                 | 30          | 30       | 10       | 30         | 30           |

| Bunch number                                                           | 268         | 11934    | 3978     | 1297       | 35           |

| Bunch spacing (ns)                                                     | 576.9 (×25) | 23.1(×1) | 69.2(×3) | 253.8(×11) | 4523.1(×196) |

| Train gap (%)                                                          | 54          | 17       | 17       | 1          | 53           |

| Luminosity per IP (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 5.0         | 115      | 38       | 16         | 0.5          |

|                                                                        | Higgs | Z     | W     | tť     |  |  |  |  |

|------------------------------------------------------------------------|-------|-------|-------|--------|--|--|--|--|

| SR power per beam (MW)                                                 | 50    |       |       |        |  |  |  |  |

| Bunch number                                                           | 446   | 13104 | 2162  | 58     |  |  |  |  |

| Damah anasina (na)                                                     | 346.2 | 23.1  | 138.5 | 2700.0 |  |  |  |  |

| Bunch spacing (ns)                                                     | (×15) | (×1)  | (×6)  | (×117) |  |  |  |  |

| Train gap (%)                                                          | 54    | 9     | 10    | 53     |  |  |  |  |

| Luminosity per IP (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 8.3   | 192   | 26.7  | 0.8    |  |  |  |  |

Z pole, ref: MC /cefs/data/stdhep/CEPC91/ 2fermions/wi\_ISR\_20220618\_50M/2fermions/

#### **Raw Data Rate**

- Data rate before trigger

- <1 TB/s @ Higgs</p>

- Several TB/s @ Z

- L1 trigger rate

- O(1k) Hz @ Higgs

- O(100k) Hz @ Z

- Event size < 2 MB</p>

- Related to occupancy and read out window

- Storage rate after HLT

- <100 Hz(200 MB/s)</li>@ Higgs

- 100 kHz (200 GB/s)@ Z

|                                | Vertex                                     | Pix(ITKB)                          | Strip<br>(ITKE)                   | ОТКВ                                  | ОТКЕ                                 | ТРС                              | ECAL-B                                      | ECAL-E        | HCAL-B                                    | HCAL-E                                    | Muon                             |

|--------------------------------|--------------------------------------------|------------------------------------|-----------------------------------|---------------------------------------|--------------------------------------|----------------------------------|---------------------------------------------|---------------|-------------------------------------------|-------------------------------------------|----------------------------------|

| Channels per chip              | 512*102<br>4                               | 512*128                            | 1024                              | 128 128                               |                                      |                                  | 8~16                                        |               |                                           |                                           |                                  |

| Data Width<br>/hit             | 32bit                                      | 42bit                              | 32bit                             | 48                                    | Bbit                                 | 48bit                            | 48bit                                       |               |                                           |                                           |                                  |

| Avg. data rate<br>/ chip       | 0.18Gbp<br>s/chip,<br>1Gbps/c<br>hip inner | 3.53Mb<br>ps/chip                  | 21.5Mbp<br>s/chip                 | 2.9Mbp<br>s/chip                      | 38.8Mb<br>ps/chip                    | ~70Mb<br>ps/mod<br>ule<br>Inmost | 10kHz/ch                                    | 10kHz/ch      | 5kHz/chann<br>el                          | 5kHz/chann<br>el                          | 10kHz/c<br>hannel                |

| Detector<br>Channel/modu<br>le | 1882<br>chips<br>@Stch<br>&Ladder          | 30,856<br>chips<br>2204<br>modules | 23008<br>chips<br>1696<br>modules | 83160<br>chips<br>3780<br>module<br>s | 11520<br>chips<br>720<br>module<br>s | 492<br>Module                    | 0.96M chn<br>~60000<br>chips 480<br>modules | 0.39 M<br>chn | 3.38M chn<br>5536<br>aggregation<br>board | 2.24M chn<br>1536<br>Aggregation<br>board | 43,176<br>chn,<br>288<br>modules |

| Avg Data Vol<br>before trigger | 474.2<br>Gbps                              | 101.7<br>Gbps                      | 298.8<br>Gbps                     | 249.1<br>Gbps                         | 27.9<br>Gbps                         | 34.4<br>Gbps                     | 460.8<br>Gbps                               | 187 Gbps      | 811.2<br>Gbps                             | 537.6<br>Gbps                             | 24 Gbps                          |

| Occupancy(%)                   | 0.022                                      | 0.025                              | (Strip)                           | 0.35(                                 | (Strip)                              | 0.0028                           | 0.58 0.002                                  |               |                                           | 002                                       | 0.038                            |

| Sum                            |                                            | 3.2 Tbps = 400GB/s                 |                                   |                                       |                                      |                                  |                                             |               |                                           |                                           |                                  |

Collected from each detectors @Higgs

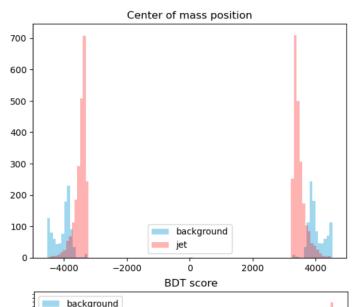

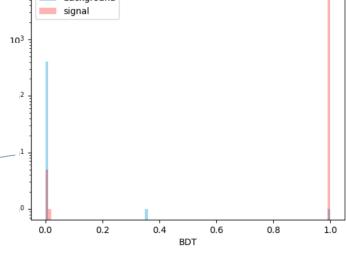

## **Trigger simulation**

- Trigger simulation study

- BDT: energy + Centre of gravity for Ecal&Hcal

- Higgs: 1.34MHz->3.4kHz

- Trigger efficiency 95%->99.9%, background 5%->0.25%

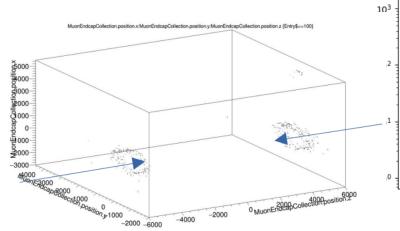

- Tracking @ Muon detector

- gamma-gamma collisions