Jie Zhang on behalf of the electronics team Institute of High Energy Physics, CAS

<sup>\*</sup>Institute of High Energy Physics Chinese Academy of Sciences

## CONSIDERATION

- Up to thousands of channels

- Custom front-end electronics

- Custom pre-amplifier

- Single p.e. to ?

- or TOT

- ADC or TDC or ADC+TDC

- Compatible with ASIC scheme or discrete device scheme

- ADC >=12 bits (SNR, range)

- TDC <= 20 ps

- Adjustable multi-channel bias voltage (<200V)</li>

- Universal back-end FPGA readout system

- White-Rabbit clock synchronization and timing

- External trigger input for beam or cosmic-ray test

- Universal cable between front-end and back-end

- Analog or digital signals

- LV and HV power supply

# DISCRETE DEVICE SCHEME

Commercial pre-amplifier, ADC or TDC

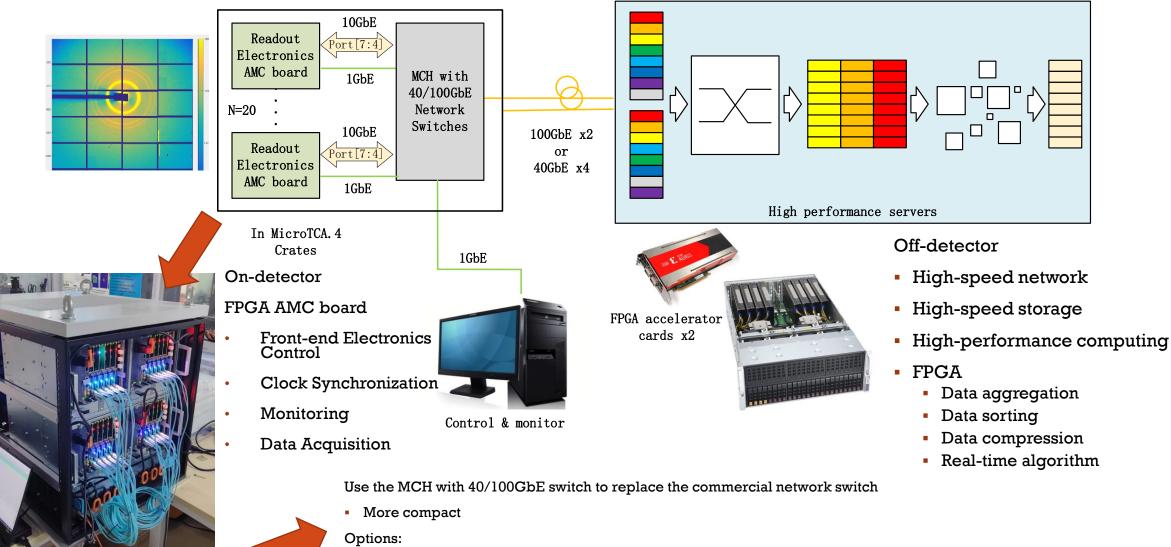

### EXAMPLE: JUNO TAO READOUT ELECTRONICS

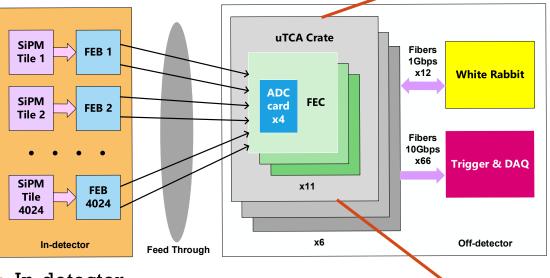

- In-detector

- Discrete readout: 2 channels/SiPM tile

- 8064 ch

- Off-detector

- 6 uTCA.4 crates

- Each crate has 12 slots and will be mounted with **11 FEC boards**

- 9 FEC boards with 4 ADC FMC cards

- Each ADC FMC card supports 32 channels

- 2 FEC board with 3 ADC FMC cards and 1 WR FMC card

- l spare slot is reserved for redundancy/debugging

- 80 FEC under mass-production

- 66 for CD, 3 for TVT, 11 for spares (13.75%)

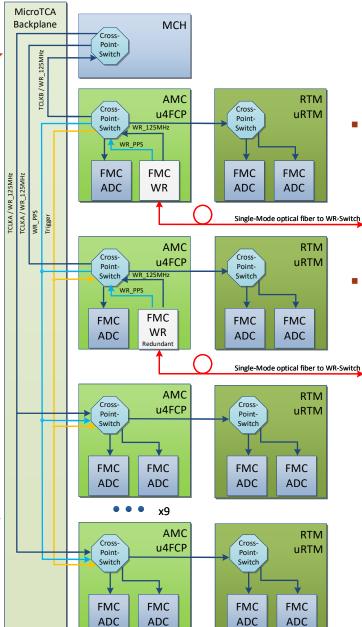

Block diagram of clock distribution in uTCA crate

- High reliability consideration in uTCA crate

- Redundant crate power supplies

- Redundant WR nodes

- Interface to trigger & DAQ system

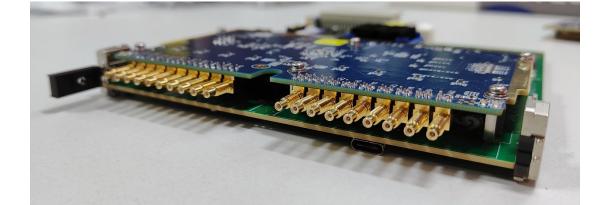

Photo of uTCA with FPGA cards <sup>4</sup>

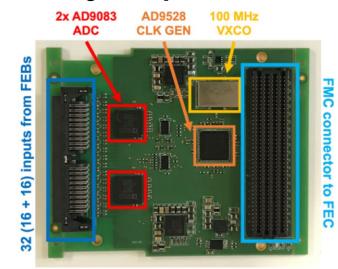

## HIGH-DENSITY READOUT

- Samtec high-density connection

- Up to 128 ch ADC per FPGA board

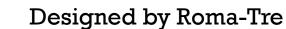

- ADC card designed and produced by Roma-Tre

- Status

- Hardware completed the small system test (60 ch)

- u4FCP, uRTM, Mini-WR and ADC card

- Passed PRR, under mass-production

- Firmware

- Complete the framework and basic functions, upgrade to 128-channel readout

- ADC JESD204B interface

- Q/T calculation

- Data format

- Aurora 64b/66b

- WR timestamp decode

- Scripts

- Online configuration through UDP

2x ADC BOARD (rear) FEC BOARD (max 128 channels) 2x ADC BOARD (front)

5

## LOW-DENSITY READOUT

Jie Zhang @ IHEP

- Easy to debug or test

- Coaxial inputs

- I6 ch or 32 ch per FPGA board

ADC FMC board

- 16 single-end channels

- 125 MHz analog bandwidth

- DC coupled analog input

- 12/16-bit Σ-Δ ADC

- Raw sample rate up to 2 GSps

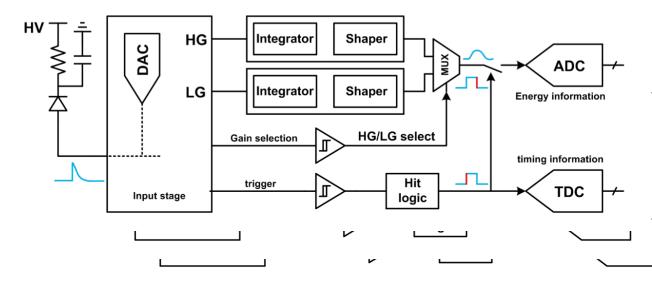

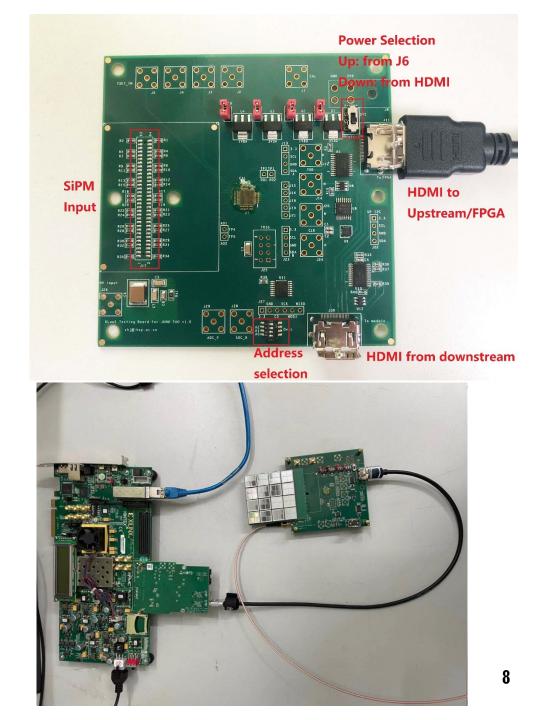

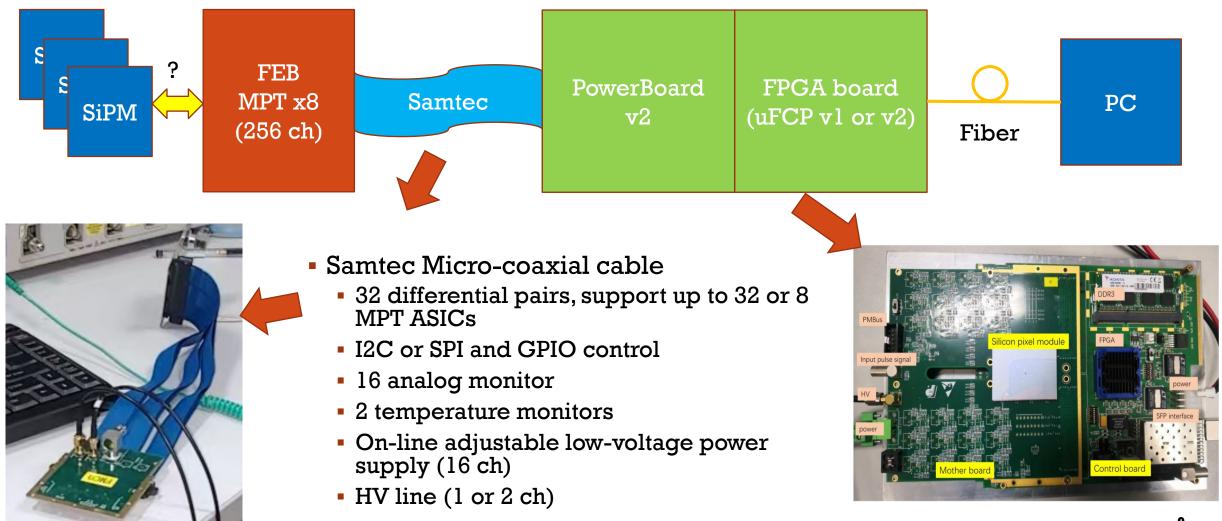

# ASIC SCHEME

Put ASIC close to SiPM

Jie Zhang @ IHEP

### ASIC SCHEME

### Prototype

- MPT or KLauS

- Multi-ch inputs

- ADC+TDC

x 36

### ASIC SCHEME (PLAN)

# BACK-END READOUT SYSTEM

FPGA, MicroTCA, WR, Trigger

Jie Zhang @ IHEP

### UNIVERSAL BACK-END FPGA READOUT SYSTEM

### MicroTCA or stand-alone on desktop

| Name      | Form factor  | Controller                                                   | <b>Power Supply</b>                                                              | JTAG                                           | AMC                                                    | RTM                                           |

|-----------|--------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|-----------------------------------------------|

| NATIVE-R9 | 9U, 19"      | 2 double full-<br>size NAT-<br>MCH with<br>1 NAT-MCH-<br>RTM | 6 double full-<br>size <b>NAT-PM</b> ,<br>two of them as<br>Rear Power<br>Module | NAT-JSM                                        | 12 double mid-<br>size                                 | 12 double mid-<br>size                        |

| NATIVE-C8 | 8U, 19"      | 2 double full-<br>size <b>NAT-MCH</b>                        | 3 double full-<br>size <b>NAT-PM</b>                                             | 1 double<br>compact-<br>size <u>JSM</u> module | 10 single mid-<br>size <b>or</b> 12 double<br>mid-size | None                                          |

| NATIVE-R5 | 5U, 0.5x 19" | 1 double full-<br>size NAT-<br>MCH with NAT-<br>MCH-RTM      | 1 double full-<br>size <b>NAT-PM</b>                                             | None                                           | 6 double mid-<br>size + 1 double<br>full-size          | 6 double mid-<br>size + 1 double<br>full-size |

| NATIVE-C5 | 5U, 0.5x 19" | 1 double full-<br>size <b>NAT-MCH</b>                        | 1 double full-<br>size <b>NAT-PM</b>                                             | None                                           | 6 double mid-<br>size + 1 double<br>full-size AMCs     | None                                          |

| NATIVE-R2 | 2U, 19"      | 1 double full-<br>size NAT-<br>MCH with NAT-<br>MCH-RTM      | 1 double full-<br>size <b>NAT-PM</b>                                             | 1 single mid-<br>size <b>NAT-JSM</b>           | 5 double mid-<br>size + 1 double<br>full-size          | 5 double mid-<br>size                         |

**R5**

R9

**R5**

| and all the second seco |                                          |                          |                                                                        |                                                                                                 |                               |                                                                                                                                          |                                                |                                                                            | Plan                                                                                                                  | )    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|

| uF(<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • 840 DSP<br>PCIe2.0 x4<br>8GB DDR3 8001 | on System Logic          | <ul> <li>0.65</li> <li>2928</li> <li>4*PCIe</li> <li>2*16GE</li> </ul> | Jltrascale+ 16nn<br>Million System L<br>DSP<br>4.0 x4 + PCIe4.<br>DDR4 1200MH<br>100G High-Spee | .ogic<br>0 x8<br>Iz SDRAM ECC | u4FCP v2<br>• Kintex Ultrascale+<br>• 1.14 Million Syst<br>• 1968 DSP<br>• SAMTEC Firefly x3<br>• 2* 16GB DDR4 120<br>• 8*40G/100G High- | tem Logic<br>3 + PCIe4.0 x8<br>00MHz SDRAM ECC | <ul> <li>3.78 M</li> <li>12288</li> <li>SAMTEC</li> <li>2* 16GB</li> </ul> | trascale+ 14 nm/16 n<br>/illion System Logic<br>DSP<br>C Firefly x3 + PCIe4.0<br>DDR4 SDRAM ECC<br>100G High-Speed Se | ) x8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Name                                     | Instance Specs<br>Status |                                                                        | FPGA                                                                                            | Memory                        | FMC                                                                                                                                      | NVMe                                           | PCIe BW                                                                    | Network                                                                                                               |      |

| Name    | Instance Specs        |        |        |                                        |               |         |           |

|---------|-----------------------|--------|--------|----------------------------------------|---------------|---------|-----------|

|         | Status                | FPGA   | Memory | FMC                                    | NVMe          | PCIe BW | Network   |

| uFC v2  | Ready                 | 7K325T | 8GB    | HPC x2                                 | -             | 2 GB/s  | 10GbE     |

| uFCP v1 | Ready                 | KU11P  | 2*16GB | HPC x4                                 | 4*(up to 4TB) | 8 GB/s  | 40/100GbE |

| uFCP v2 | Under Mass-production | KU15P  | 2*16GB | HPC x4                                 | -             | 8 GB/s  | 40/100GbE |

| uFCT    | Plan                  | VU13P  | 2*16GB | HPC x2 ( <mark>FMC+</mark> )<br>HPC x2 | -             | 8 GB/s  | 40/100GbE |

**uFC Series Board**

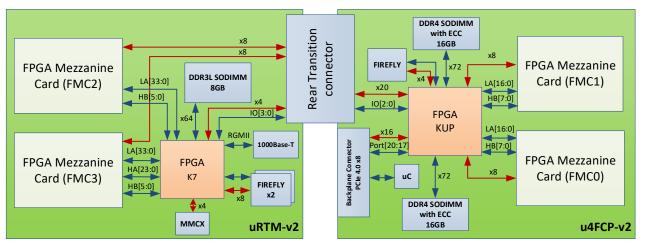

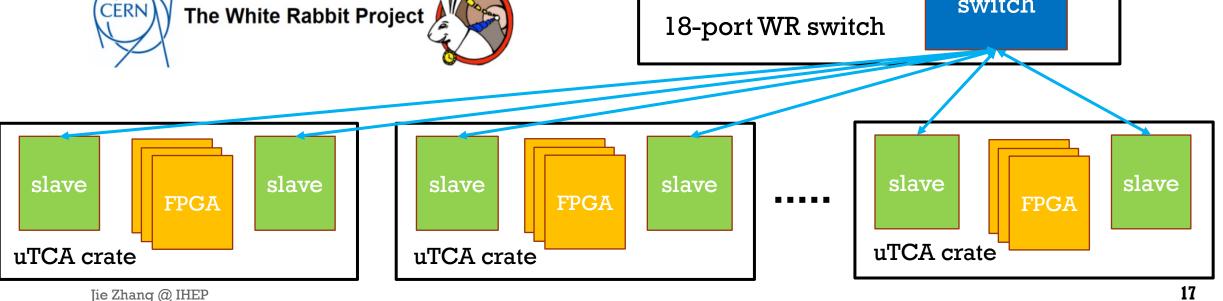

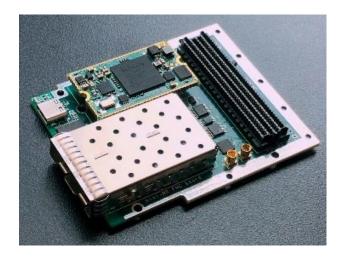

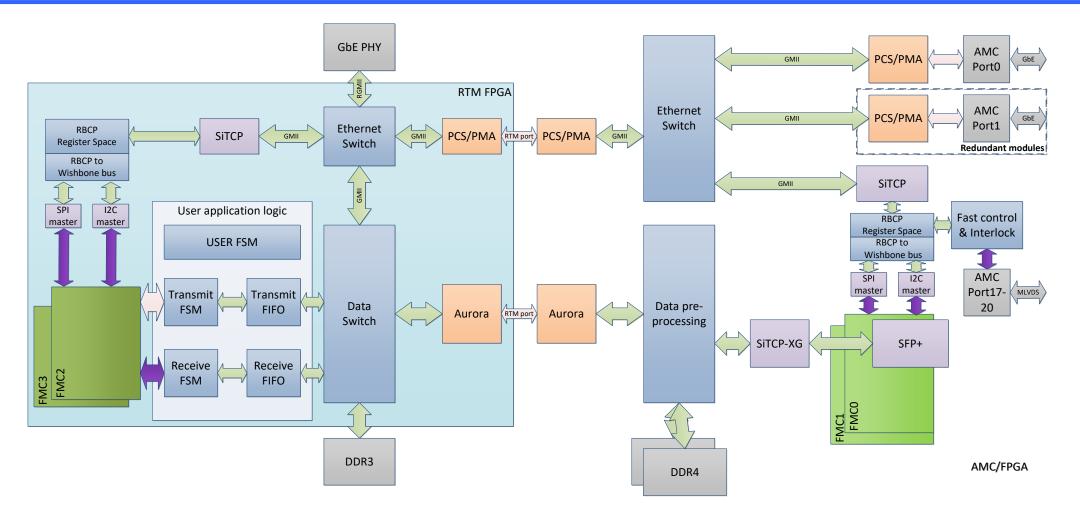

## FPGA BOARD (AMC+RTM)

• u4FCP-v1

• uRTM-v2

#### u4FCP & uRTM:

FPGA-based MicroTCA compatible AMC board

- For generic system control and data acquisition in HEP/HEPS experiments

- Conceived to serve a mid-sized system residing either

- inside a MicroTCA crate or

- **stand-alone** on desktop with high-speed optical links or Ethernet to PC

- HPC FMC sockets

- Provide additional clock signals, user-specific I/O and high-speed transceivers that can be used to extend the connectivity as well as the I/O bandwidth

- The red lines are high-speed serial links connected to the <u>gigabyte transceivers</u> (<u>GTY/GTH/GTX</u>) of the FPGA. The blue lines are the general input/ outputs connected to the High Performance (HP), High Range (HR) or High Density (HD) banks of the FPGA.

- More details:

- https://github.com/palzhj/u4FCPv2

### FMC CONNECTION

Although the FMC standard defines LA, HA, HB and DP differential ports, only parts of them are connected to FPGA due to limited IO resources. The table below summarizes the connections of FMC

|   |      | HPC                    |                        |          |         |                        |                        |                                         |           |  |

|---|------|------------------------|------------------------|----------|---------|------------------------|------------------------|-----------------------------------------|-----------|--|

|   | FMC  | LPC                    |                        |          |         |                        |                        |                                         |           |  |

|   |      | LA[16:0]               | LA[33:17]              | DP[0]    | DP[9:1] | HA[16:0]               | HA[23:17]              | HB[16:0]                                | HB[21:17] |  |

|   | FMC0 | HP bank<br>(1.0V~1.8V) | -                      | 1<br>GTY | 7 GTY   | -                      | -                      | HD bank<br>(3.3V), 8<br>ADC<br>Channels | -         |  |

|   | FMC1 | HP bank<br>(1.0V~1.8V) | -                      | 1<br>GTY | 7 GTY   | -                      | -                      | HD bank<br>(3.3V), 8<br>ADC<br>Channels | -         |  |

|   | FMC2 | HR bank<br>(1.2V~3.3V) | HR bank<br>(1.2V~3.3V) | 1<br>GTH | 7 GTH   | -                      | -                      | HR bank<br>(2.5V), 5<br>ADC<br>Channels | -         |  |

| P | FMC3 | HR bank<br>(1.2V~3.3V) | HR bank<br>(1.2V~3.3V) | 1<br>GTH | 7 GTH   | HR bank<br>(1.2V~3.3V) | HR bank<br>(1.2V~3.3V) | HR bank<br>(2.5V), 5<br>ADC<br>Channels | -         |  |

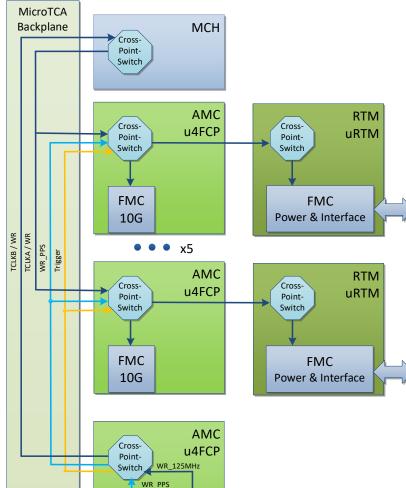

### **ELECTRONICS SYSTEM ARCHITECTURE**

To be upgrade with internal switch

NAT, NAT-HUB-E (wait to deliver)

Vadatech, UTC056-500-212-110 (under test)

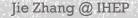

WR(White Rabbit)

## **CLOCK REDUNDANCY CONSIDERATION**

- Due to the life limit of fiber optic transceivers, we plan to use a redundant WR clock

- Each uTCA crate has two WR slave nodes

- Clock source selection

- WR node report the loss of lock

- DCS get the report, and configure the hardware to switch to the redundant node

Ref clock master

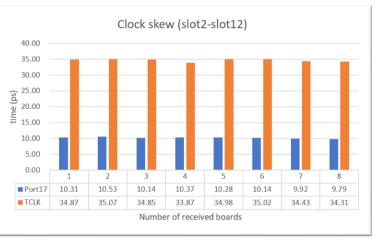

## CLOCK DISTRIBUTION IN MICROTCA

Two clock allocation schemes inside the crate

• Port 17 ?

TCLK?

- Native R9 crate with WR Support

- MLVDS multi-drop connection

• TCLKB (slot12)-> MCH (NAT-MCH-PHYS80) -> TCLKA (slot1-11)

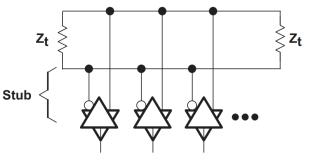

# BIAS VOLTAGE

Multi-channel, each channel independent adjustable

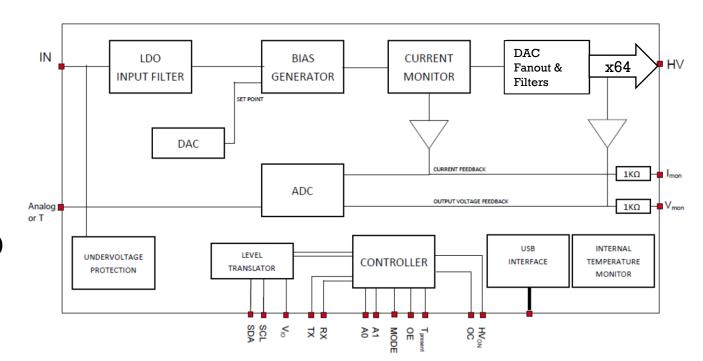

### ADJUSTABLE MULTI-CHANNEL BIAS VOLTAGE (PLAN)

- MicroTCA card mechanics

- 64 ch outs

- 2 x 64 pin IDC connectors

- up to 200V/ch

- up to 550uA/ch

- 2 x 14bit DAC chips

- Output voltage monitor (24bit ADC)

### HARDWARE STATUS

|                 | Name                                           | Status                               |

|-----------------|------------------------------------------------|--------------------------------------|

| ASIC scheme     | FEB (Front-end board) with 8 MPT ASIC (256 ch) | Not started                          |

|                 | Powerboard v2                                  | Ready                                |

|                 | FEB with pre-amplifier                         | Prototype                            |

| Discrete device | ADC card low-density (16 or 32 ch)             | Ready                                |

| scheme          | ADC card high-density (128 ch)                 | Under mass-production by<br>Roma-Tre |

|                 | FPGA board (uFCP v1 and uRTM v2)               | Ready                                |

|                 | FPGA board (uFCP v2 and uRTM v2.2)             | Under mass-production                |

| Back-end        | FPGA board (uFCT and uRTM v2.2)                | Not started                          |

|                 | WR node                                        | Ready or on-shelf product            |

|                 | External trigger node                          | Ready                                |

| Bias voltage    | 64 ch bias voltage(<200V)                      | Not started                          |

### SUMMARY

- MicroTCA architecture

- Suitable for small and medium-sized experiments

- uFC series boards

- FPGA-based MicroTCA compatible AMC board for generic system control and data acquisition in physics experiments

- HPC FMC sockets

- Provide additional clock signals, user-specific I/O and high-speed transceivers that can be used to extend the connectivity as well as the I/O bandwidth

- Support discrete device scheme and ASIC scheme for SiPM readout in one system

### CLOCK DISTRIBUTION IN MICROTCA AMC with mini-WR fixed in slot 12, move AMC receiver

FMC

WR Redundant

Single-Mode optical fiber to WR-Switch

Jie Zhang @ IHEP

Clock skew (slotN-slot12) 8.00

7.50

7.00

7.00

9

6.50

9

(y = 0.223x + 4.22)

9

25.00

9

(y = 2.203x + 4.22)

9

(y = 2.200)

9

(y = 0.223x + 4.22)

9

(y = 0.22

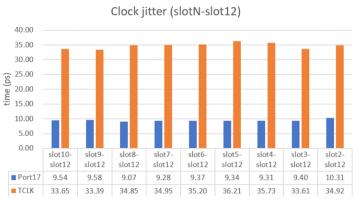

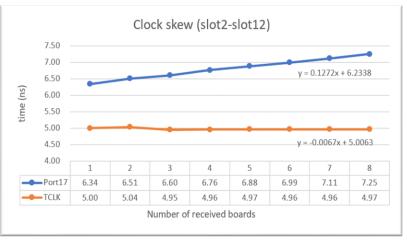

#### Receiver is fixed at slot 2, add more adjacent AMC boards

- TCLK scheme has deterministic skew, but more jitter

- Port17 scheme has smaller jitter, but the skew is related to the location and receiver quantity <sup>25</sup>

### **FPGA Firmware**

- Config & monitor via UDP/IP

- Readout via TCP/IP

### FEASIBILITY

- AMC+RTM boards

- With various FMC cards

FPGA node

Mini-WR FMC

SFP+x4

QSFP28 x2

QSFP28 x2

#### QSFP28 x2

#### ADC FMC board

- 16 single-end channels

- 125 MHz analog bandwidth

- DC coupled analog input

- 12/16-bit  $\Sigma$ - $\Delta$  ADC

- Raw sample rate up to 2 GSps