# The Readout for the Silicon Tracker

Xiongbo Yan

On behalf of the CEPC Silicon Tracker Group

& Electronics Group

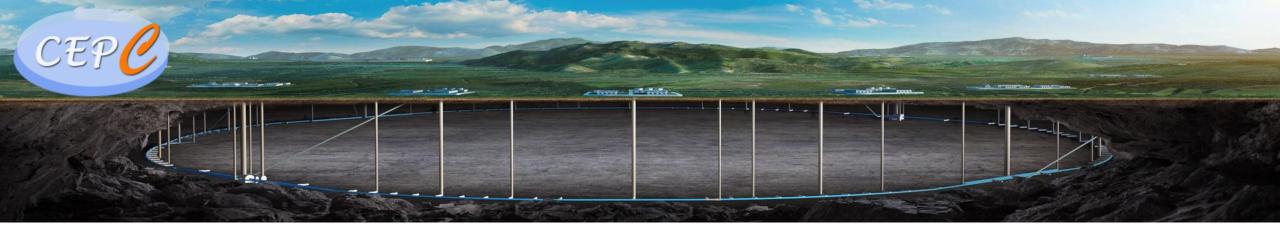

## Introduction

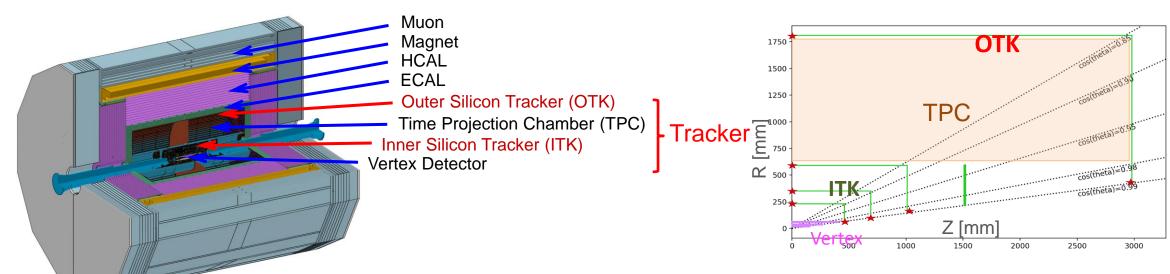

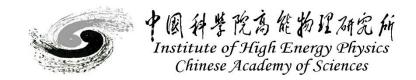

- The CEPC tracker system includes several detectors: the Vertex Detector, Inner Silicon Tracker, Time Projection Chamber (TPC), and Outer Silicon Tracker.

- The ITK employs advanced CMOS sensor technology to achieve precise position measurements for accurate particle trajectory determination.

- The OTK integrates the AC-LGAD for precision time measurement of charged particles, significantly enhancing particle identification capabilities.

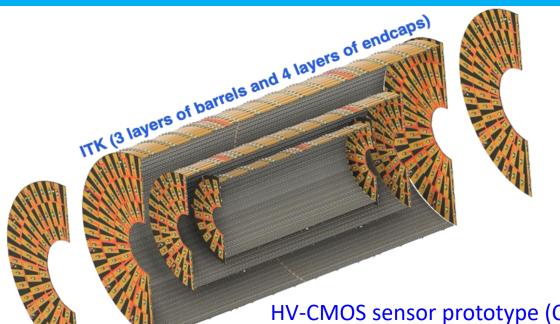

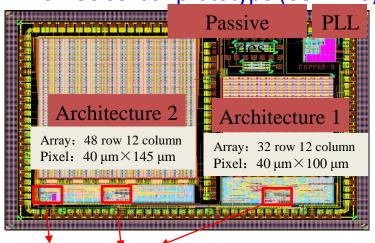

## ITK Design Based on HV-CMOS Pixel Sensor

- $\Box$  Three barrel and four endcap layers (~20 m<sup>2</sup>).

- ☐ Monolithic HV-CMOS pixel sensor is applied.

- ☐ Three rounds prototype tape-outs, including sensor, CSA, comparator, TDC, serializer.

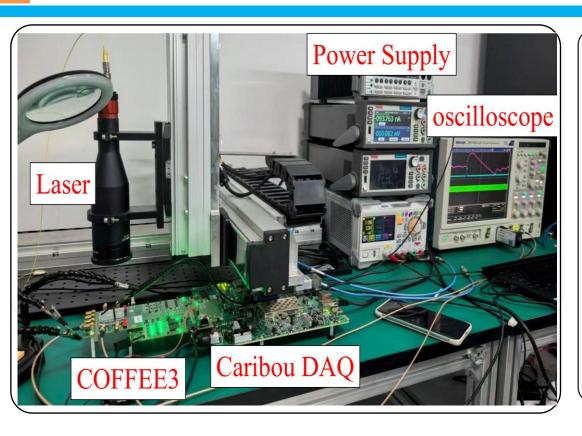

HV-CMOS sensor prototype (COFFEE3)

|                    | - <b>F</b>                         |  |  |  |

|--------------------|------------------------------------|--|--|--|

| Sensor size        | $2 \text{ cm} \times 2 \text{ cm}$ |  |  |  |

| Sensor thickness   | 150 $\mu$ m                        |  |  |  |

| Array size         | 512 × 128                          |  |  |  |

| Pixel size         | 34 $\mu$ m $	imes$ 150 $\mu$ m     |  |  |  |

| Spatial resolution | 8 μm × 40 μm                       |  |  |  |

| Timing resolution  | 3-5 ns                             |  |  |  |

| Power              | 200 mW/cm <sup>2</sup>             |  |  |  |

|                    |                                    |  |  |  |

**HV-CMOS** sensor specification for ITK

## **R&D Progress on HV-CMOS Pixel Sensor**

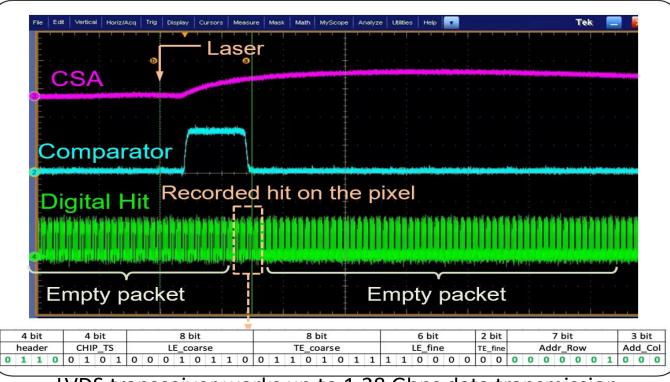

LVDS transceiver works up to 1.28 Gbps data transmission

- The latest COFFEE3 sensor was submitted for tape-out and received in May 2025, is currently undergoing testing.

- Several aspects have already been validated, including preamp, comparator, and serializer and the remaining tests are currently in progress. [more details in Yang Zhou's talk]

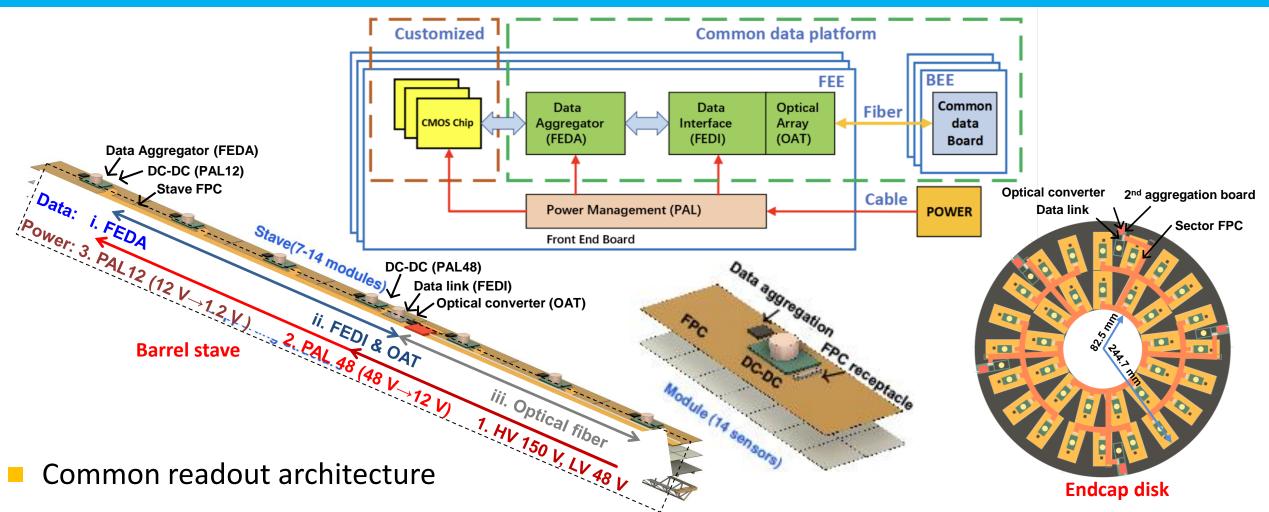

## **Design Including Power and Readout Electronics**

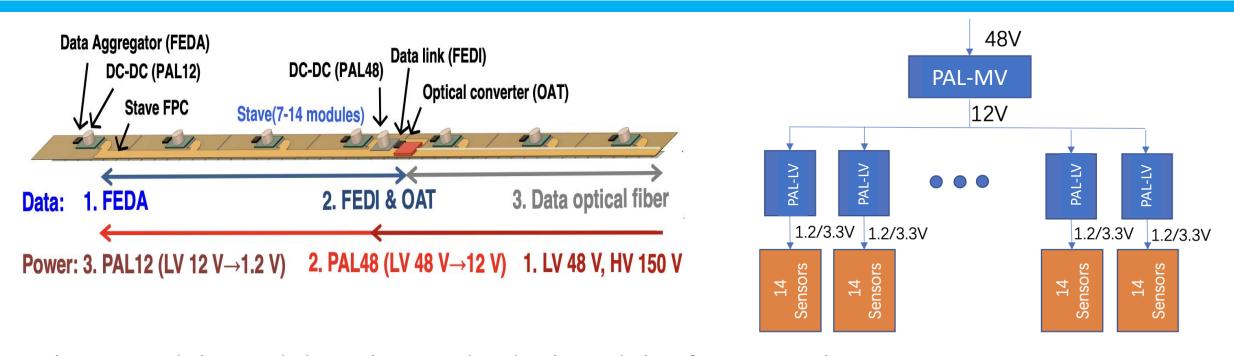

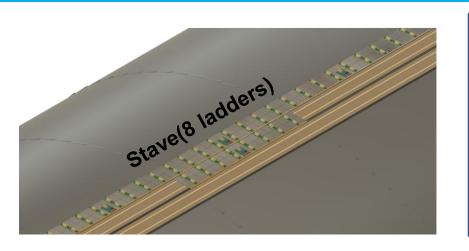

- Stave FPC and optical fiber are used to transmit HV, LV, data, clock signals, and chip commands.

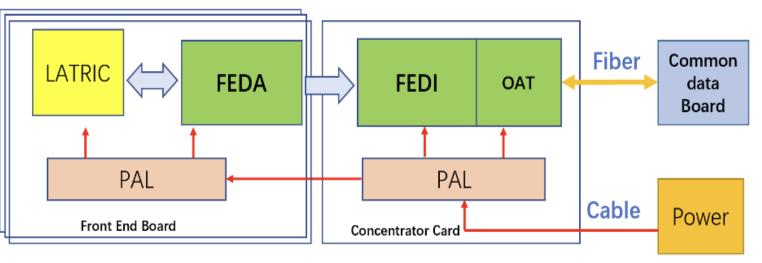

- The FEDA, FEDI, OAT, and PAL chips are under development by the CEPC team.

# **Power Management for ITK**

- The HV is delivered directly to individual modules for sensor biasing. HV switch is considered in case of HV short of individual module.

- The power is delivered by Flex PCB from the both sides for barrel.

- 1.2V for front end, FEDI, FEDA, 3.3V for VCSEL driver in optical convertor.

- Both of DC-DCs is supposed to be with output capability ~10A.

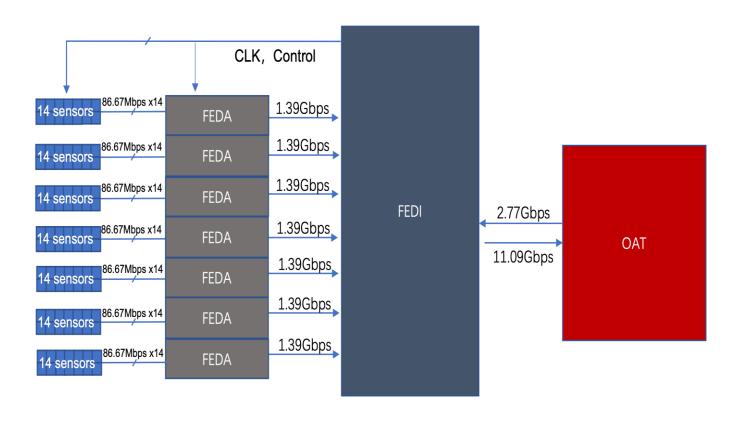

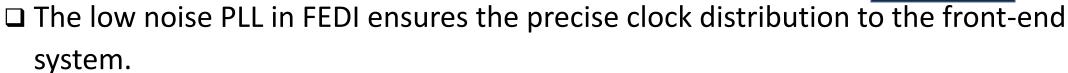

### **Data Readout Flow for ITK**

- Each FEDA concentrates data from 14 sensors, 7 FEDAs to 1 FEDI

- FEDI provides clocks, uplinks from FEDA, downlinks to FEDA and Sensor such as configuration, reset and synchronization.

- Data frame from sensor includes TOA, TOT, adress, bunch ID, polarity.

In the readout design, each sensor can tolerate up to 86.67 Mbps

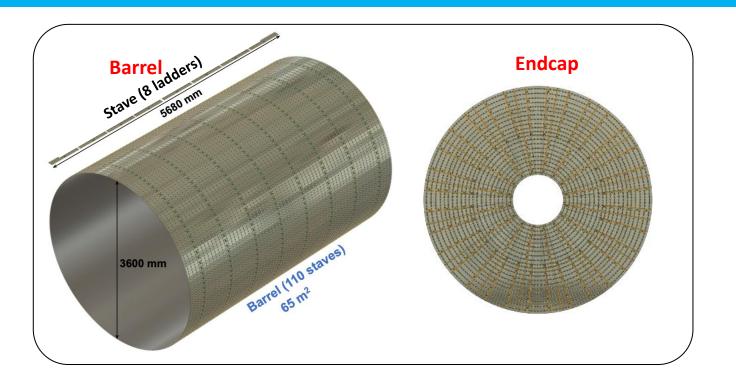

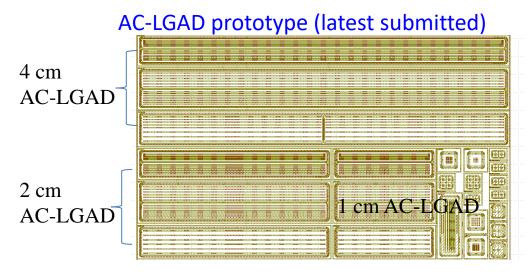

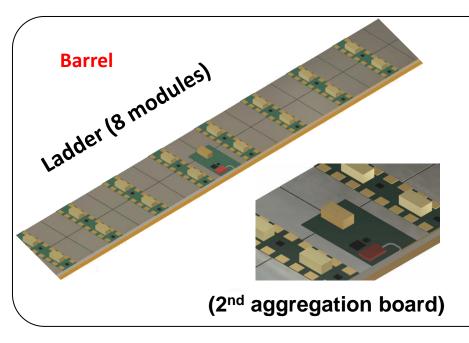

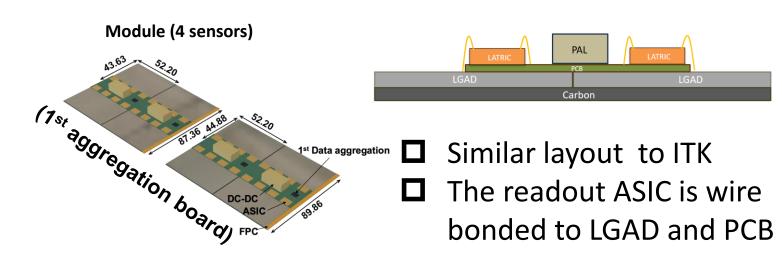

## **OTK Design Based on LGAD Strip Sensor**

- $\square$  One barrel layer and one endcap layer (~85 m<sup>2</sup>).

- ☐ The latest LGAD sensor with different length and pitch was submitted for tape-out in March and waiting for the return.

| LGAD sensor specification for OTK |                                              |  |  |  |

|-----------------------------------|----------------------------------------------|--|--|--|

| Sensor size                       | $(3-4.5) \text{ cm} \times (3-5) \text{ cm}$ |  |  |  |

| Strip pitch                       | ~100 μm                                      |  |  |  |

| Spatial resolution                | 10 μm                                        |  |  |  |

| Timing resolution                 | 50 ps                                        |  |  |  |

| Power                             | 300 mW/cm <sup>2</sup>                       |  |  |  |

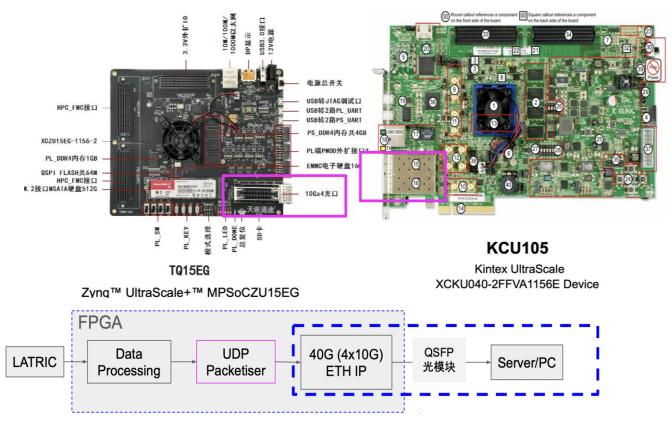

## **OTK Readout Electronics**

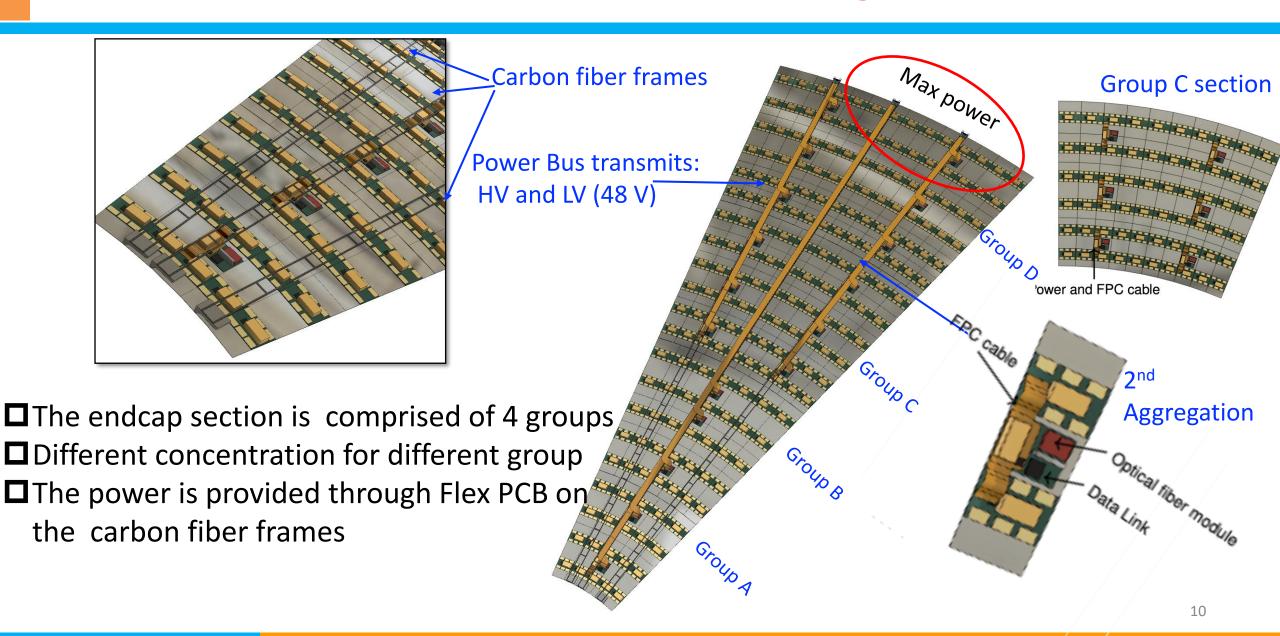

# **OTK Readout Endcap layout**

## **Power and Data readout flow for OTK**

☐ The power management is similar to ITK

□ Data frame from sensor includes TOA,TOT, adress, bunch ID, polarity.

☐ Each FEDA concentrates data from 16 FEs.

□ 43.3Mbps per LATRIC for barrel and 86.7 Mbps per LATRIC for endcap

□ Low-frequency clock jitter and potential phase instability, particularly caused by temperature variations, will require special attention.

## **R&D Progress on LGAD ASIC**

[more details in Chuanye's talk]

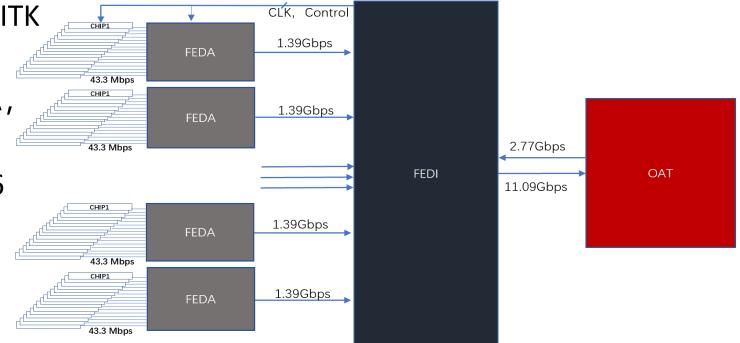

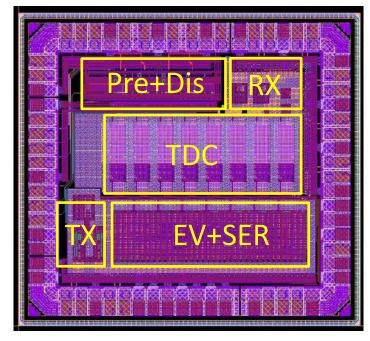

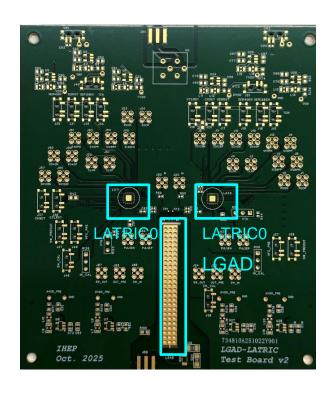

#### The first LATRIC prototype, LATRICO, submitted for tape-out in April, was wire bonded and delivered to IHEP in Aug

- o The ASIC integrates a pre-amplifer, a discriminator, a TDC, and a serializer for data output.

- Tests find that the LSB is 29.8 ps, meeting the 30 ps design goal. The measured TDC power consumption is 0.1 mA (1.2 V)

0.5 MTPS (Mega-Trigger Per Second), 0.3 mA @ 1 MTPS, and 0.5 mA @ 2 MTPS, agreeing with the design.

More in-depth tests are on-going...

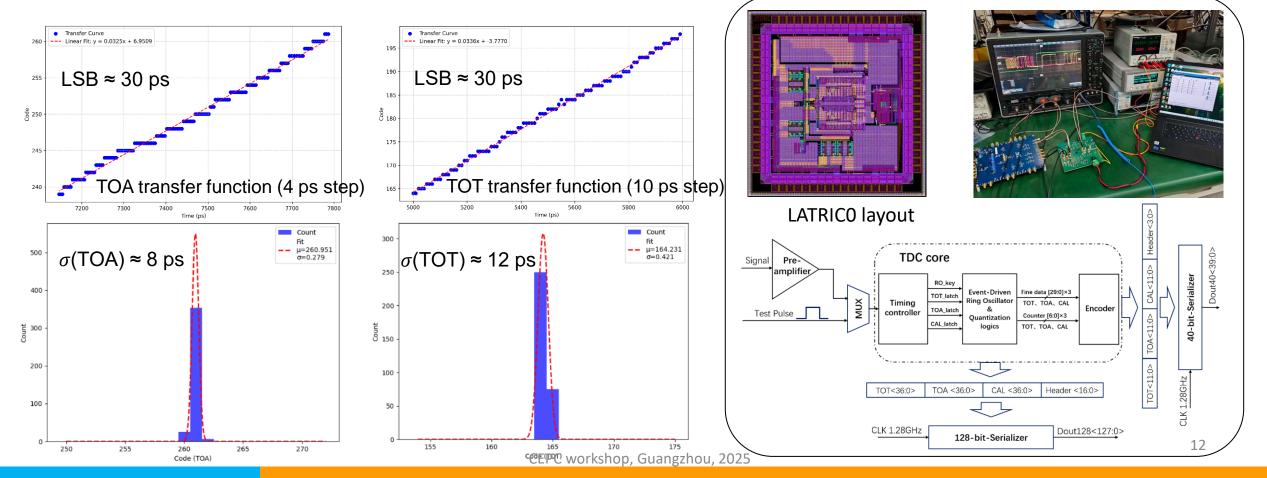

# **LATRIC1 Progress**

- Submitted for tape-out in October

- 8 channels TDC

- 4 channels with front end

- Increase the gain of preamp

- Improve the encoder logic

- Add event builder and scramble logic

- 100 um channel pitch match the LGAD

- Test PCB design is ongoing

LATRIC1 layout

## **LATRIC test with LGAD**

- 2 LATRICOs on PCB are connected to LGAD.

- The PCB already came back and waiting for soldering and bonding.

- DAQ debug is ongoing.

- Laser for measurement is ready.

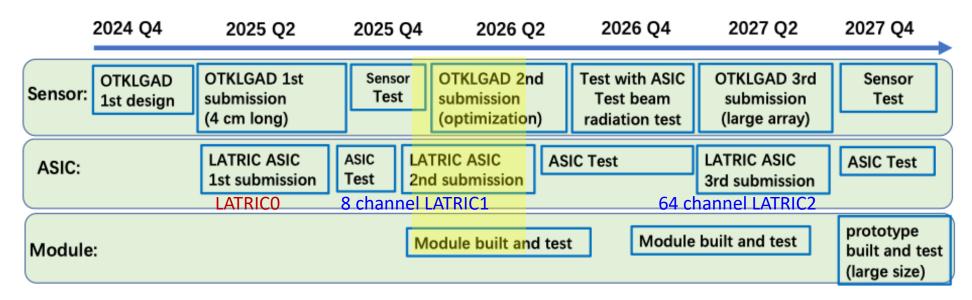

# **R&D Plan Following the Ref-TDR**

#### HV-CMOS pixels:

2024 Q4 COFFEE2 full characterization 2025 Q2 MPW submission for key module verification COFFEE3 2025 Q4 Test & spec finalization 2026 Q3 Quarter chip submission to validate fullcolumn readout 2027 Q2 2027 Q4 Module Full-size fullprototype function chip

#### AC-LGAD strips+ASIC:

## Summary

- The design of readout electronics scheme for the Silicon Tracker and the latest R&D progress have been presented.

- Next focus will be on R&D, aiming front end ASIC (multiple channels integtation for LATRIC), sensor (seek process optimization for LGAD and COFFEE) and readout electronics prototype development.

- A multi-channel design with full component integration, is carefully planned to verify the sensor bonding and realistic performance characterization.

### **Our Research Team**

Currently active: 29 institutes, 50 staff, and 50+ postdocs & students

We we

We welcome collaboration with partners worldwide.

# Thank you for your attention!

# **BACKUP**

**Figure 5.1:** Layout of the Silicon Tracker (ITK and OTK). The ITK consists of three barrel layers and four endcap layers, together with two extended connection rings, forming the complete ITK assembly that is inserted into the inner barrel of the TPC. The OTK, as the outermost component of the tracker system, includes one barrel layer and one endcap layer, mounted outside of the TPC. It provides both high-precision spatial and timing measurements.

**Table 5.1:** Parameters and layout of the Silicon Tracker. The column labelled  $\pm z$  shows the half-length of the barrel layers, and the z position of the end-cap disks. The column labelled  $\sigma_{\phi}$  and  $\sigma_{t}$  represent the spatial resolution in the bending direction and time resolution, respectively.

| Detector   |                 |              | ius <i>R</i><br>m] | ±z<br>[mm] | Material budget $[\% X_0]$ | σ <sub>φ</sub><br>[μ <b>m</b> ] | $\sigma_t$ [ns] |

|------------|-----------------|--------------|--------------------|------------|----------------------------|---------------------------------|-----------------|

| ITK Barrel | Layer 1 (ITKB1) | 235.0        |                    | 493.3      | 0.68                       | 8                               | 3-5             |

| IIK Darrei | Layer 2 (ITKB2) | 345.0        |                    | 704.8      | 0.68                       | 8                               | 3-5             |

|            | Layer 3 (ITKB3) | 55.          | 5.6                | 986.6      | 0.68                       | 8                               | 3-5             |

| OTK Barrel | Layer 4 (OTKB)  | 1,800        |                    | 2,840 1.6  |                            | 10                              | 0.05            |

|            |                 | $R_{\rm in}$ | $R_{\rm out}$      |            |                            |                                 |                 |

|            | Disk 1 (ITKE1)  | 82.5         | 244.7              | 505.0      | 0.76                       | 8                               | 3-5             |

|            | Disk 2 (ITKE2)  | 110.5        | 353.7              | 718.5      | 0.76                       | 8                               | 3-5             |

| ITK Endcap | Disk 3 (ITKE3)  | 160.5        | 564.0              | 1,000      | 0.76                       | 8                               | 3-5             |

|            | Disk 4 (ITKE4)  | 220.3        | 564.0              | 1,489      | 0.76                       | 8                               | 3-5             |

| OTK Endcap | Disk 5 (OTKE)   | 406.0        | 1,816              | 2,910      | 1.4                        | 10                              | 0.05            |

**Table 5.2:** Estimated average and maximum hit rates of the Silicon Tracker [10<sup>3</sup> Hz/cm<sup>2</sup>] for all layers across three operation modes.

| $\mathcal{L} (10^{34}  \mathrm{cm}^{-2} \mathrm{s}^{-1})$ | Low Lumi Z<br>26 |       | Higgs<br>8.3 |       | High Lumi Z<br>192 |       |

|-----------------------------------------------------------|------------------|-------|--------------|-------|--------------------|-------|

|                                                           | Average          | Max   | Average      | Max   | Average            | Max   |

| ITKB1                                                     | 1.04             | 1.95  | 0.63         | 1.01  | 3.10               | 5.84  |

| ITKB2                                                     | 0.98             | 3.30  | 0.55         | 1.33  | 2.93               | 9.89  |

| ITKB3                                                     | 0.76             | 1.69  | 0.39         | 0.77  | 2.26               | 5.07  |

| OTKB                                                      | 0.66             | 1.11  | 0.37         | 0.58  | 1.96               | 3.32  |

| ITKE1                                                     | 3.46             | 15.78 | 2.35         | 11.70 | 10.37              | 47.28 |

| ITKE2                                                     | 3.99             | 24.50 | 2.06         | 9.82  | 11.95              | 73.38 |

| ITKE3                                                     | 2.29             | 17.26 | 1.14         | 7.46  | 6.86               | 51.71 |

| ITKE4                                                     | 2.54             | 8.55  | 1.26         | 3.71  | 7.59               | 25.61 |

| OTKE                                                      | 1.54             | 6.35  | 0.94         | 4.12  | 4.61               | 19.01 |