# The development of FEDA

**Guoxiang Zhang**

**Central China Normal University**

November 8, 2025

- Background

- ☐ FEDA Chip: Requirements & Overall Block Diagram

- FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

- Background

- FEDA Chip: Requirements & Overall Block Diagram

- FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

### **Background**

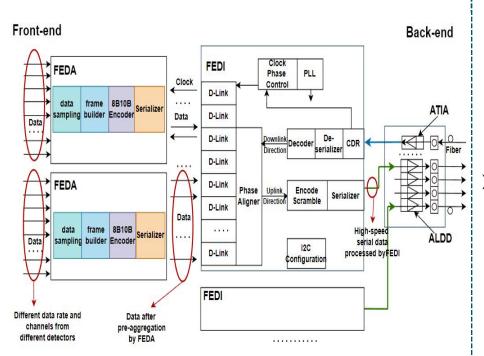

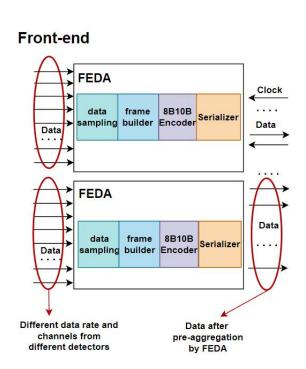

- This project focuses on the requirements of CEPC (Circular Electron-Positron Collider) in high-energy physics, developing a general-purpose bidirectional high-speed data transmission system to solve the problem of efficient acquisition and transmission of multisource data in the CEPC detection system.

- Within the system's overall framework, frontend data—with varying rates from different channels—is sent to the backend through this data link system; this is what we call **uplink transmission**. At the same time, clock signals, trigger signals, and configuration signals are also sent to the frontend through this system, which we refer to as **downlink transmission**.

- Background

- ☐ FEDA Chip: Requirements & Overall Block Diagram

- FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

### FEDA Chip: Requirements & Overall Block Diagram

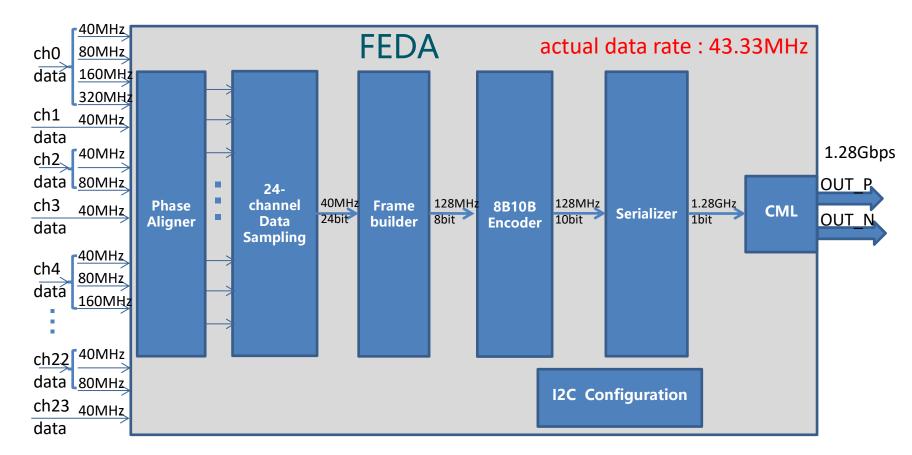

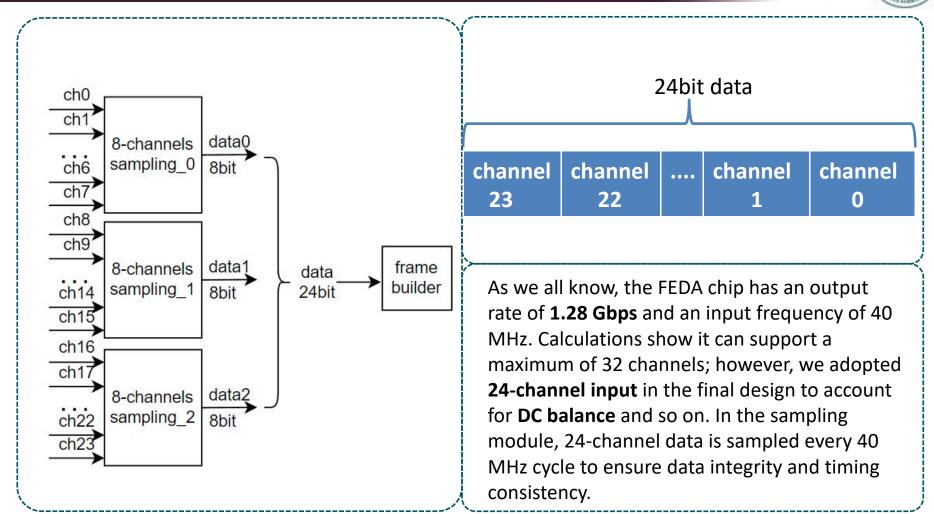

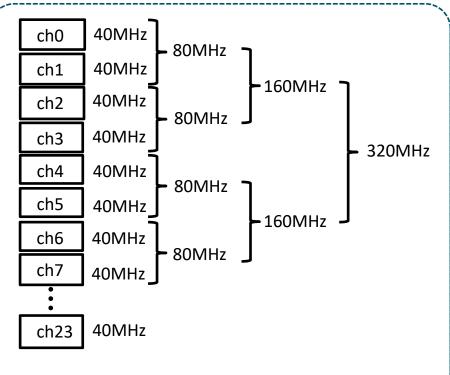

To meet this core need, the Front-End Data Aggregator(FEDA) chip we designed plays an important role in data processing: it collects data of different rates (40 MHz, 80 MHz, 160 MHz, 320 MHz) from various frontend detectors. After gathering this data, it finally outputs data at a rate of 1.28 Gbps—providing a stable data stream for the backend's high-speed data transmission link.

### FEDA Chip: Requirements & Overall Block Diagram

The FEDA Chip design is mainly composed of seven core modules: Phase aligner,24-channel Data Sampling, Frame Builder, 8B10B Encoder, Serializer,CML Driver and I2C Configuration.

- Background

- ☐ FEDA Chip: Requirements & Overall Block Diagram

- ☐ FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

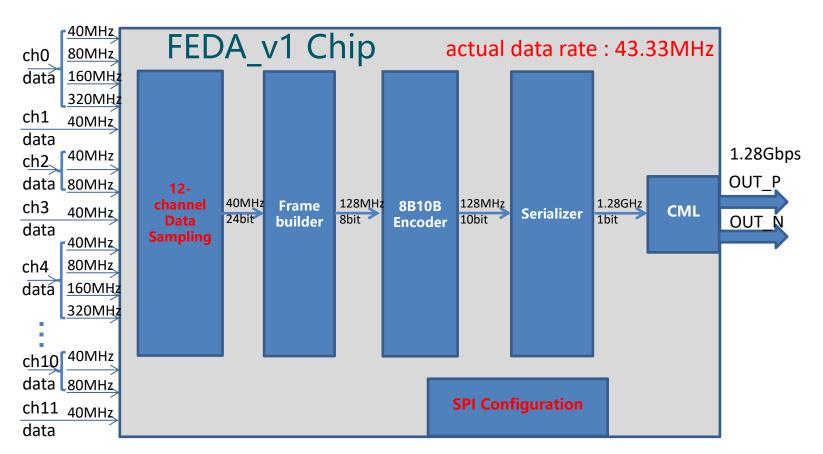

# FEDA\_v1 Chip: Overall Block Diagram

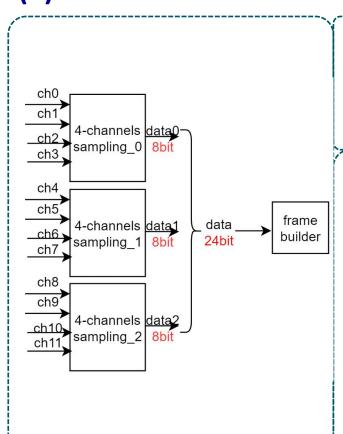

The FEDA\_v1 Chip design is mainly composed of **six** core modules: **12-channel Data Sampling**, Frame Builder, 8B10B Encoder, Serializer, CML Driver and **SPI Configuration**.

# FEDA\_v1 Chip: Overall Block Diagram

#### Differences Between the FEDA\_v1 Chip and the Final FEDA Chip:

- ➤ Data Input Channels: In the first version uses 12 data input channels, while the final version will have 24 data input channels.

- Configuration Interface: The first version uses SPI configuration, while the final version will use I2C configuration.

- ➤ Phase Alignment Function: The FEDA\_v1 Chip didn't employ phase alignment; while the final FEDA chip will add phase alignment before data sampling.

# **FEDA Chip: 24-channel Data Sampling**

# **FEDA Chip: 24-channel Data Sampling**

The 24 input channels can be divided into 3 independent 8-channel units (i.e., Channels 0-7, 8-15, 16-23). The input rate analysis of Channels 0-7 can be directly reused for the other two 8-channel units.

the 24-channel input of the FEDA supports multiple channel rate configurations—it works with both single-rate and mixed-rate configurations.

| Configuration<br>Type        | Specific Configurations                                                                              |

|------------------------------|------------------------------------------------------------------------------------------------------|

| Single-rate<br>Configuration | - 40 MHz x 24 channels                                                                               |

|                              | - 80 MHz x 12 channels                                                                               |

|                              | - 160 MHz x 6 channels                                                                               |

|                              | - 320 MHz x 3 channels                                                                               |

| Mixed-rate<br>Configuration  | e.g.,320 MHz × 1 channel +<br>160 MHz × 2 channels + 80<br>MHz × 2 channels + 40<br>MHz × 4 channels |

- Background

- ☐ FEDA Chip: Requirements & Overall Block Diagram

- FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

#### (1) 12-channel Data Sampling:

4'b10

ch

ch

ch

ch

...

4'b10

ch

ch

ch

ch

10

11

10

9

8

10

3

2

1

0

24bit.data

- The output bit width of both the 12-channel data sampling in the first version (V1) and the 24-channel data sampling is 24 bits, which ensures a consistent frame format. for each 8-bit group, the upper 4 bits use a fixed input of 4'b1010, and the lower 4 bits are channel sampling values;

- Advantages: fewer channels mean fewer PADs, a smaller chip area, and lower costs;

- ➤ Compatibility: No modification to the frame format is required for the V2 version, enabling direct expansion to 24 channels and reserving good compatibility for project iteration.

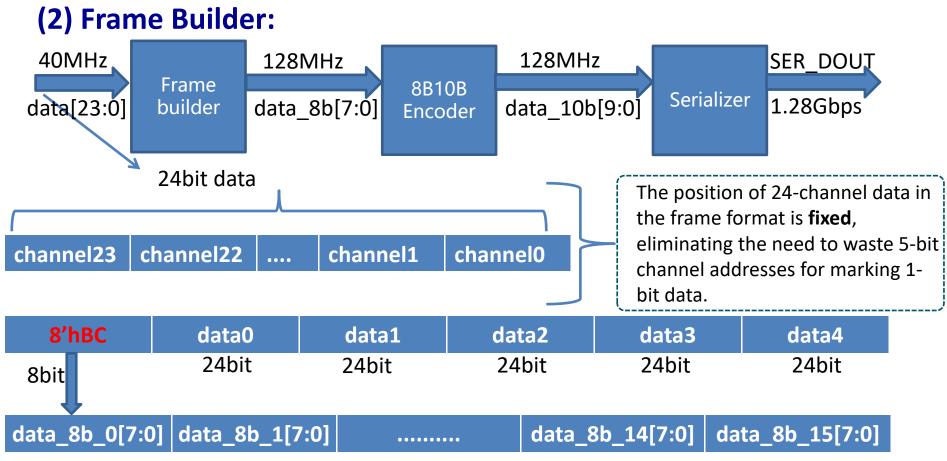

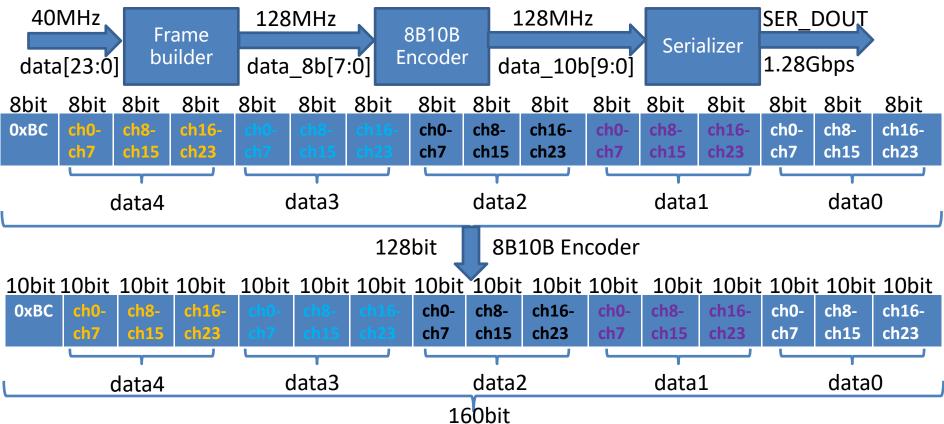

**Composition of One Frame**: 8-bit frame header  $+ 5 \times 24$ -bit input data (din) = 128 bits = 8 bits  $\times$  16.

#### (3) 8B10B Encoder:

**Purpose**: We use 8B10B encoding mainly to ensure **DC balance**—this keeps the number of "0"s and "1"s in the signal balanced over the long run, which is key for stable transmission.

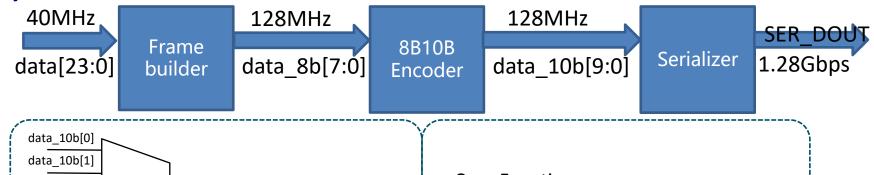

#### (4) Serializer:

#### **Core Functions:**

- ①it serializes the frontend 10-bit parallel data, achieving a final output rate of 1.28 Gbps with **LSB first**;

- ②it performs frequency division on the 640 MHz clock to generate **128 MHz** and **320 MHz** clocks for the frontend modules, ensuring that all clocks in the system are in-phase.

- Background

- ☐ FEDA Chip: Requirements & Overall Block Diagram

- FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

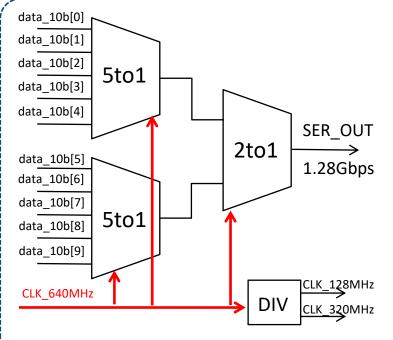

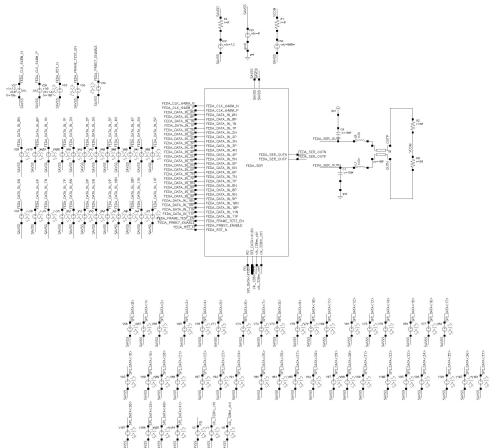

**Key Chip Specifications:**

➤ Process: SMIC55nm

$\triangleright$  Chip Area: 1288um $\times$ 1405um

➤ Voltage: 1.2V

1405um

1288um

19

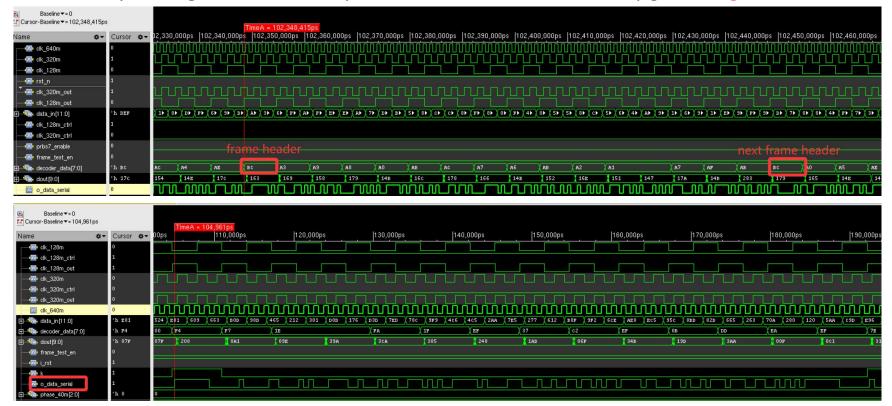

simulation 1: Post-Layout Digital Post-Simulation

- Tool: Nclaunch

- Process: By feeding the encoded output into a decoder, we successfully got the right frame format.

We also checked the serial data output under PRBS7 pseudo-random numbers—and it matched the XOR relationship of pseudo-random numbers.

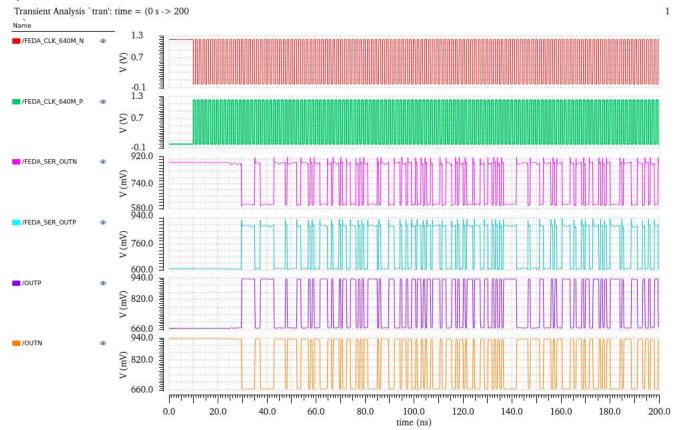

simulation(2):Post-Simulation with Transmission Line Model

- Tool: Virtuoso

- Process: added a transmission line model to the Test Bench for the simulation.

simulation2:Post-Simulation with Transmission Line Model

Output Signals: Under PRBS7 pseudo-random number mode, The output waveforms of the chip and the transmission line model are as follows.

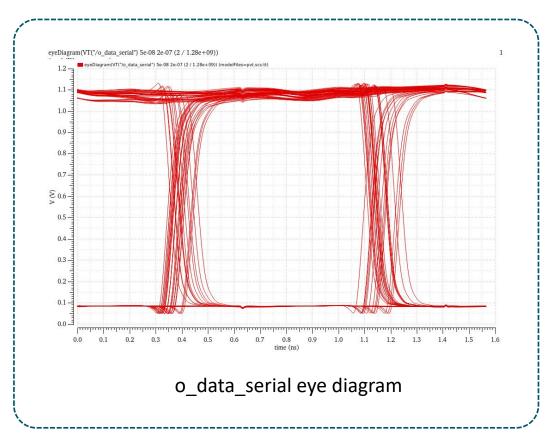

simulation②:Post-Simulation with Transmission Line Model Eye Diagrams: Eye diagrams of the "o\_data\_serial" signal output by the Serializer in the design:

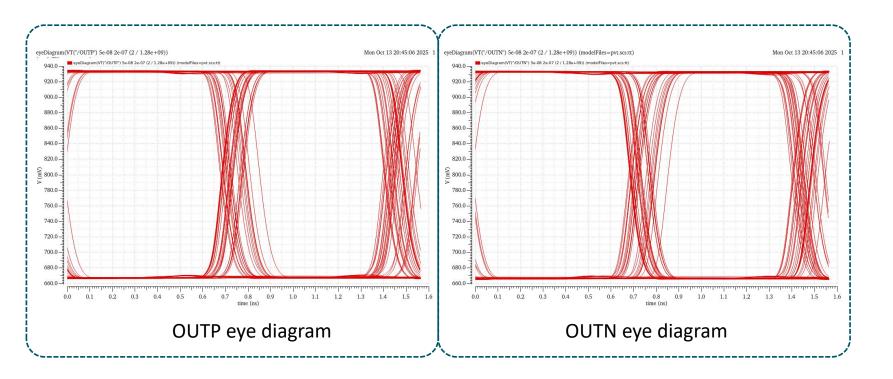

simulation②:Post-Simulation with Transmission Line Model Eye Diagrams: Eye diagrams of the "OUTP" and "OUTN" signal output by the Transmission Line Model:

- Background

- FEDA Chip: Requirements & Overall Block Diagram

- FEDA\_v1 Chip : Overall Block Diagram

- ☐ FEDA\_v1 Chip : Core Module Design

- FEDA\_v1 Chip: Layout and Simulation

- Summary and Plan

#### **Summary and Plan**

#### **Summary**

The first version (V1) of the FEDA chip has completed design and been submitted to the foundry for tape-out.

#### **Future Plans**

- **Before chip return**: Complete the design of the test PCB board and firmware configuration of the test system.

- After chip return: Immediately initiate chip testing to verify key performance indicators (e.g., data rate, transmission stability).

- Looking ahead: The current first version uses 12 data input channels. The second version will focus on expanding the channel count to 24, improving the stability of the data sampling module, and making targeted improvements based on V1 test results.

# **Ending**

# Thanks for your attention!