# A low-power 55 nm HV-CMOS pixel sensor readout architecture for the CEPC Inner Tracker

Yang Zhou<sup>1</sup>, WeiGuo Lu<sup>1</sup>, Pengxu Li<sup>3</sup>, Xiaoxu Zhang<sup>1,4</sup>, Xiaomin Wei<sup>2</sup>, Leyi Li<sup>1,6</sup>, <u>Bingchen Yan<sup>1</sup></u>, Jianpeng Deng<sup>3</sup>, Mei Zhao<sup>1</sup>, Yu Zhao<sup>2</sup>, Zheng Wei<sup>2</sup>, Yang Chen<sup>5</sup>, Yujie Wang<sup>5</sup>, Zhan Shi<sup>5</sup>, Hongbo Zhu<sup>3</sup>, Meng Wang<sup>6</sup>, Jianchun Wang<sup>1</sup>, Yiming Li<sup>1</sup>

<sup>1</sup>Insitute of High Energy Physics, CAS, Beijing, China <sup>2</sup>Northwestern Polytechnical University, Xi'an, China <sup>3</sup>Zhejiang University <sup>4</sup>Nanjing University, Nanjing, China <sup>5</sup>Dalian Minzu University, Dalian, China <sup>6</sup>Shandong University, Qingdao, China

# Introduction

The HV-CMOS pixel sensor has been confirmed as the baseline technical solution for the inner tracking (ITK) detector of the CEPC. It needs to provide ~ns time resolution and <10  $\mu$ m position under the condition of <200 mW/cm² power consumption.

On the basis of meeting the requirements of CEPC, two different readout architectures are proposed. The first one aims to further increase the upper limit of hit density (>100 MHz/cm²) that HV-CMOS technology can handle (refer to Leyi Li's Poster). The other one target to further reduce the average power consumption of the HV-CMOS pixel sensor to simplify the requirements of the cooling system; this readout concept could also be used to further reduce the position resolution and improve data accuracy. (This Poster)

# The power consumption theory

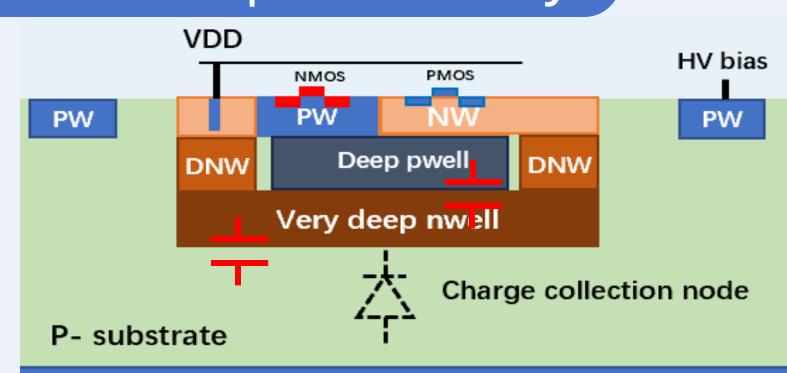

Fig 1. The pixel cross section view of a typical HV-CMOS sensor. The very deep N-well (VDNW) and P-type substrate formed the charge collection electrode. Charge-sensitive amplifiers (CSA) and readout electronics can be integrated nearby within the pixel

### Working principle:

- The power consumption of a HV-CMOS pixel sensor (typically contains ~100000 pixel unit) mainly from the in-pixel electronics.

- The response time of a CSA proportional to the capacitance of the sensor diode ( $C_d$ ) and inversely proportional to the transconductances of the transistor used for the amplifier ( $g_m$ ), as given by:

$$au_{CSA} \propto \frac{1}{g_{

m m}} \frac{c_{

m d}}{c_{

m f}}$$

•  $g_m$  is normally proportional to the consumed current. The relationship is:

$$g_m = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_{DS}}$$

• Time walk is the main contributing source to time resolution. It is proportional to the time response of the CSA and the threshold  $(V_{TH})$  of the comparator, and inversely proportional to the minimum signal quantity, which can be expressed as:

TW  $\propto \tau_{CSA} \frac{V_{TH}}{V_{sig,min}}$

### **Conclusion:**

For a determined temporal response, a smaller  $C_d$  and large signal are crucial to reduce the power consumption of the pixel sensor.

# The C<sub>d</sub> theory

The main contributions of C<sub>d</sub>:

- The capacitance between Deep pwell (DPW) and VDNW;

- The capacitance between the signal collection electrode VDNW and P-sub;

# 1e-11 Capacitance\_with\_HV C<sub>HV</sub> = 24.12fF Capacitance\_with\_PWELL/DPW C<sub>PWELL</sub> = 185.9fF 1e-12 1e-13 1e-14 1e-15 0 HV Voltage (V)

### Conclusion:

- Capacitance between DPW and VDNW is the main source of Cd, and does not change with bias voltage.

- ➤ A simple in-pixel electronic structure(small DPW size) is very beneficial for low power consumption.

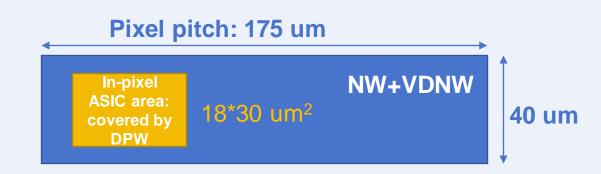

Fig. TCAD simulation results of the relationship between the Cd value and bias voltage of a typical HV-CMOS pixel. The pixel size is set at 40\*175um<sup>2</sup>, in-pixel electronics layout size is 18\*30 um<sup>2</sup> (covered by DPW). The doping conditions are derived from speculation. Test results confirmation is required.

# The low-power readout architecture

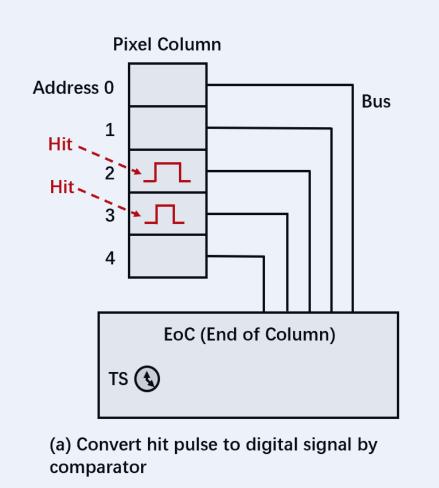

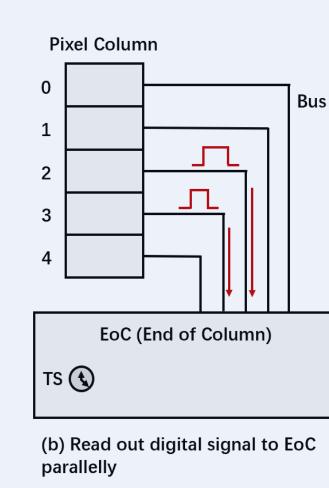

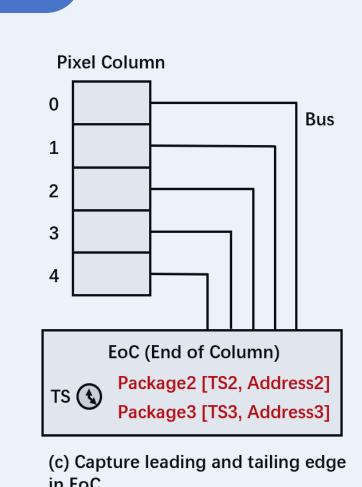

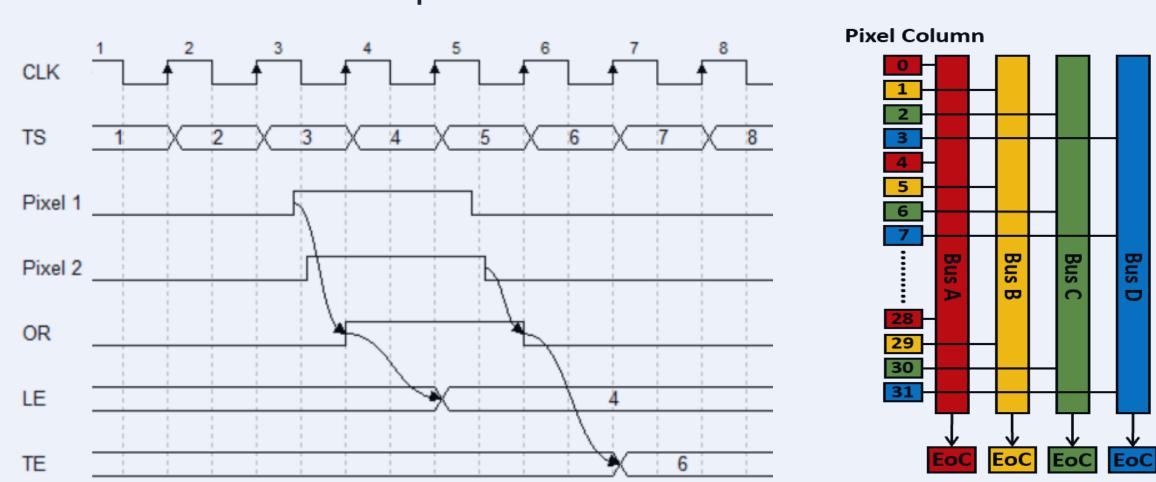

Read out concept of the pixel matrix: The signal output of each pixel is transmitted in parallel to the bottom of the column for further processing. It is characterized by the fact that the pixel can only contain an amplifier and a comparator, occupying very little area to achieve a smaller Cd value.

Multiple pixels simultaneously fired in a column, may lead to inaccuracies in time stamps.

To overcome such issues. Each column of pixels can be divided into 4 groups, input to 4 distinct EoC modules. Each EoC module contains two separate state machines and time-stamp counters, ensuring accurate time information even when particles hit adjacent pixels (charge sharing effect) or multiple pixels in the same column fired simultaneously.

# Implementation of the readout architecture

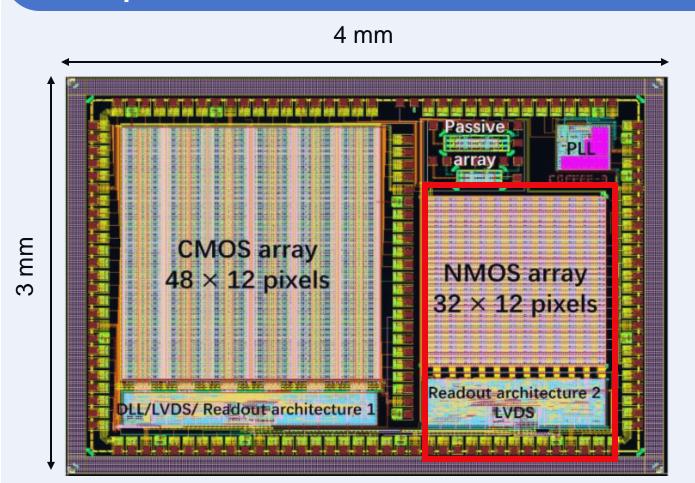

Fig. Layout of the COFFEE3, submitted Jan. 2025. The proposed architecture have implemented in the area circled in red in the above figure. The current process substrate resistivity is  $10 \ \Omega \cdot \text{cm}$ , breakdown voltage is ~70V, depletion depth is ~10 µm.

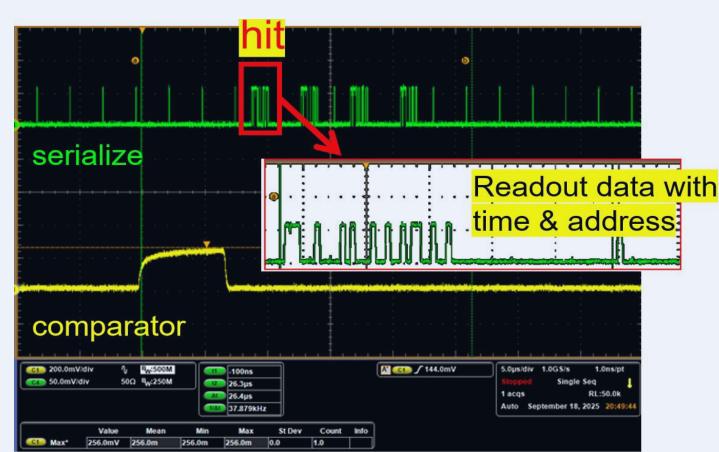

Fig. Response of full readout chain with laser test:

Sensing diode → in-pixel (CSA\comparator\TDC) →

EOC (digital peripheral) -> data link-> DAQ (refer to Boxin Wang's Poster)

## Summary & outlook

On the basis of meeting the requirements of CEPC, we have proposed and preliminarily verified an 55nm HV-CMOS pixel sensor readout architecture on that has the potential to further reduce power consumption or improve position resolution accuracy.

The next step will focus on optimizing the process, increasing the breakdown voltage, and reducing the contribution of VDNW and P-substrate capacitance to  $C_d$ . High-resistivity wafers will be adopted to increase the total signal (from the current ~1000e- to ~16000e-), thereby simplifying the design and power consumption of the in-pixel CSA and further reducing the overall chip power consumption.

A simplified in-pixel design could also be used to further reduce the pixel size to improve position resolution, while this requires more discussions starting from the physical requirements to determine.