# Common R&D efforts on CMOS pixel detector system for the experiment of electron-positron colliders

16th FCPPN/L Workshop, 21 – 25 July 2025, Qingdao

## Yunpeng Lu

on behalf of the FCPPN/L collaboration teams

French Groups: IPHC/IN2P3, Jérôme BAUDOT, Christine Hu-Guo, ...

CPPM/IN2P3, Marlon Barbero, ...

**Chinese Groups:** IHEP/CAS, *Qun OUYANG, Yunpeng Lu, ...*

USTC, Lailin Xu, ...

Jilin University, Weimin Song, ...

## **Outline**

- > Introduction

- Overview of collaboration

- ➤ BELLE II VTX upgrade proposal

- Backend electronics and TDAQ system

- > R&D for CEPC vertex detector

- Large area sensor design JadePix-5

- Summary

<sup>\*</sup>Monolithic Active Pixel Sensor, or CMOS Pixel Sensor are used interchangeably in this talk without distinction

## Overview of collaboration

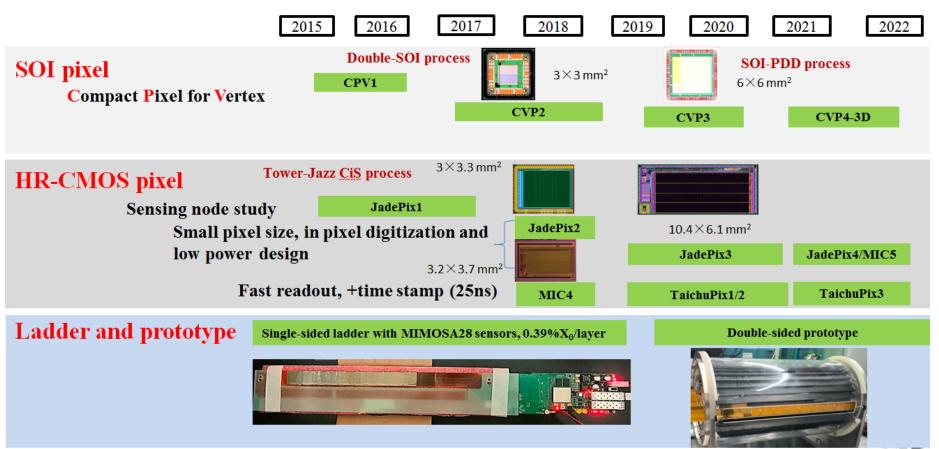

- Starting from 2010, common R&D efforts of MAPS for the e<sup>+</sup>e<sup>-</sup> collider experiments: **BES III** upgrade, ILC/CEPC, BELLE II upgrade

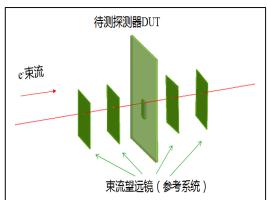

- 1. The prototype of CMOS pixel detector for the upgrade of BESIII-inner tracker

- ✓ Development of pixel detector ladder based on the MIMOSA28 sensors from IPHC

- ✓ common participation of beam test at DESY, to validate the ladder performance, space resolution, material budget, ...

Ref.: NIMA924(2019)287-292, NIMA986(2021)164810

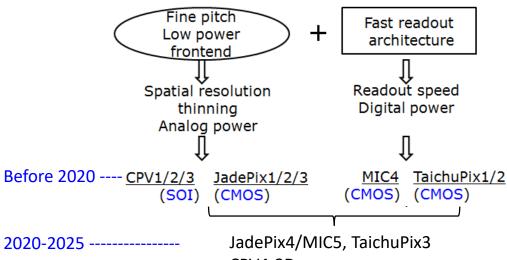

2. CMOS Pixel Sensors R&D for future e<sup>+</sup>e<sup>-</sup> colliders: *pixel sensor and double-sided ladder development* Since 2015, **four engineering runs** have been shared with TJ 180 nm CIS process

2015: JadePix-1

2017: JadePix-2/MIC4

2020: JadePix-3

2022: JadePix-4/MIC5

# **Development of CMOS Pixel Sensor JadePix-3**

- ➤ JadePix-3 is a fully functional prototype chip with

- Very compact in-pixel circuit, layout area 16 μm×23 μm

- Low power consumption targeted on 50 mW/cm<sup>2</sup>

- > Designed by IHEP and collaborators in China

- IHEP, CCNU, SDU, DLNU

- Extensive lab characterization and beam test

- Electrical

- Infrared Laser beam

- Radiative source

- High energy charged particle beam

#### Reference:

- Design and characterisation of the JadePix-3 CMOS pixel sensor, NIMA, 1048 (2023) 167967

- Performance study of the JadePix-3 telescope from a beam test, NIMA, 1065 (2024) 169551

# **Extended collaboration among Chinese groups**

- Active participation in the JadePix-3 test study

- ✓ Common development of MAPS test system, used in several chip tests

- ✓ Characterization of reverse-biased JadePix-3 sensor, research article submitted to NIMA

- ✓ Analysis of beam test data, co-author of NIMA paper

✓ 1 student graduated with master degree, "Performance Study of the JadePix-3 CMOS Pixel

Detector Chip" • Input Capacitance,  $\mathcal{C}_{\text{input}}$  accessed by calculating analog response Amp - Smaller  $\mathcal{C}_{\mathrm{input}}$  increase voltage excursion and improves the SNR C<sub>input</sub> reduced nearly 65% as Bias Voltage increasing! nwell electrode  $Amp = \frac{Q_{inject}}{C_{innut}} \cdot f_{gain} \cdot f_{sf}$ deep pwell  $V_{

m sub}^{\perp}$ P- epitaxial layer P<sup>+</sup> substrate sensing diode of JadePix-3 Bias Voltage/V 胡珈豪 (中国科学技术大学) 2025/4/19

## **Outline**

- > Introduction

- Overview of collaboration

- ➤ BELLE II VTX upgrade proposal

- Backend electronics and TDAQ system

- ➤ R&D for CEPC vertex detector

- Large area sensor design JadePix-5

- > Summary

<sup>\*</sup>Monolithic Active Pixel Sensor, or CMOS Pixel Sensor are used interchangeably in this talk without distinction

#### Physics program @ SuperKEKB with Belle II

- Thorough test of Std Model

- Direct/indirect search for New Physics

- Hadronic Physics

with billions of  $B\bar{B}$ ,  $c\bar{c}$ ,  $\tau\bar{\tau}$  pairs In "clean" environment of B-factory

⇒ The Belle II physics book <u>PTEP 12 (2019) 123C01</u>

- Based on accumulation of 50 ab<sup>-1</sup> of e<sup>+</sup>+e<sup>-</sup> at  $\sqrt{s} = M_{Y(4S)}$

- requires instantaneous luminosity close to 6x10<sup>35</sup> cm<sup>-2</sup>.s<sup>-1</sup>

SuperKEKB collider implementing the nano-beam scheme @ high currents

High collision rate

High beam-induced bkg

#### The Belle II experiment

"classical" B-factory detector + enhanced features

The vertex detector (VXD)

- Better vertexing ← lower boost

Smarter tracking ← higher hit rate

- + Harsher radiation environment

- + Belle II trigger rate ~ 30 KHz

J. Baudot - CMOS Pixel Chip for the planned Belle 2 upgrade - Terascale detector workshop 2022

→ Proposal for replacement of VXD = PXD (DEPFET sensors) + SVD(Double Sided Strip Detector) by VTX detector.

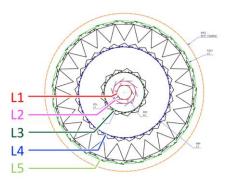

# VTX proposal

#### Proposed BELLE II VXT upgrade scheme

- 5 straight layers with Depleted Monolithic

Active Pixel Sensors

- Identical chips on all layers: Optimized BELle II pIXel (OBELIX) sensor

- ~1m² silicon surface

| From simulations                            | Belle II VIX                                                                 |  |  |

|---------------------------------------------|------------------------------------------------------------------------------|--|--|

| Spatial res.                                | <10-15μm                                                                     |  |  |

| Total material budget<br>Inner-outer layers | 0.1 – 0.8 %Xo                                                                |  |  |

| Max hit rate                                | 120MHz/cm²                                                                   |  |  |

| Time precision                              | <100ns                                                                       |  |  |

| Trigger (freq.)<br>(delay)                  | 30 kHz<br>5-10μs                                                             |  |  |

| Rad. hard. (TID)<br>(fluence)               | <100 kGy/year<br><50x10 <sup>12</sup> n <sub>eq</sub> cm <sup>-2</sup> /year |  |  |

| Power                                       | <200mW/cm²                                                                   |  |  |

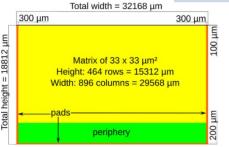

| 300 um                                      |                                                                              |  |  |

#### **OBELIX**

- Tower 180 nm process

- Extension of TJ-Monopix2

- → OBELIX sensor

- <40 µm pitch, 100 ns integration

#### **Key sensor specifications:**

• Pixel pitch: *30-40 μm*

• Integration time: ≤100 ns

• Power dissipation:  $\leq 200 \text{ mW/cm}^2$

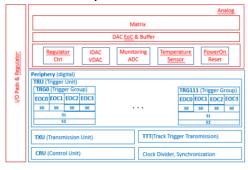

# **OBELIX (Optimized for BELIe II pIXell)**

- Developed from **TJ-Monopix2 sensor** (*Developed for ATLAS-ITK: doi: 10.1016/j.nima.2020.164460*)

- ☐ Increase active area from 17x17 mm² to 15x29,6 mm²

- ☐ LDO implementation on lateral sides for **power drop compensation** on ladder

- Re-design digital periphery for handling **VTX trigger requirements** with additional features: TTT (Track Trigger Transmission) & PTD (Peripheral Time to Digital)

- Additional analog functionalities for improved monitoring and safety: Monitoring ADC, Temperature sensor, Power On Reset

- **Design collaboration:** IPHC, CPPM, HEPHY, KEK, INFN, University of Bergamo, University of Pavia, University of Pisa, University of Applied Sciences and Arts Dormund, University of Bonn, University of Valencia

- ✓ With their expertise in MAPS, Chinese laboratories are **candidate** for Belle II VTX contributing in different development aspects, such as chip characterization or system design. ← Width = 30168 μm → Width = 30168 μm

8812µm

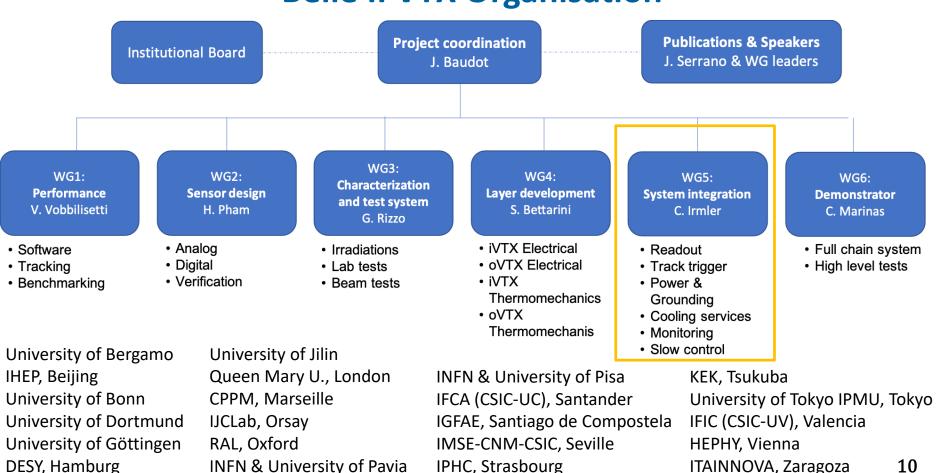

# **Belle II VTX Organisation**

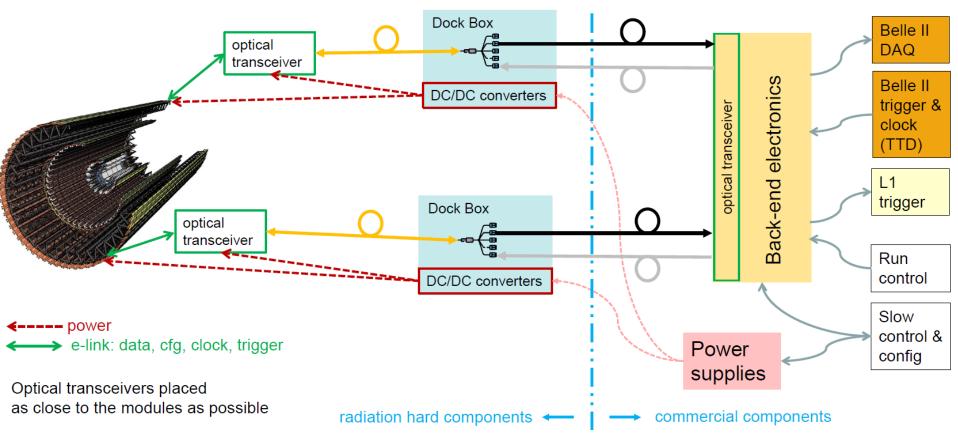

# **VTX Readout Concept**

# WG5: System Integration

#### Readout electronics

- Data readout

- Chips configuration

- Fast optical links

- Interfaces to Belle II

- DAQ

- Trigger Timing Distribution (TTD)

- · Run / slow control

- Track trigger

- Transmit TTT data to Belle II trigger system

## Powering, GND

- Power supplies for LV and HV, power cables

- Grounding and shielding scheme

#### Monitoring

- Temperatures, voltages, currents, humidity, air and water flow, water leak, radiation, etc.

- Hard-, firm- and software

## Cooling services

- Chiller(s) and control unit for water cooling

- Cold and dry air / N<sub>2</sub> supply

- Piping (water and air)

- Water leak detection

#### Run / slow control

- Entire software for control, monitoring, data acquisition and data quality monitoring

- Server infrastructure for VTX operation

# WG5 interest overview

- Dedicated WG5 meeting in May 2025

- 9 institutes interested to contribute to WG5

- USTC, Jilin University and IHEP presented activities and interests

|                  |         |           | Interface board                                   |                                                       | Back-end electronics          |                                   |           |                            |            |                     |

|------------------|---------|-----------|---------------------------------------------------|-------------------------------------------------------|-------------------------------|-----------------------------------|-----------|----------------------------|------------|---------------------|

| Group            | Country | City      | optical<br>tranceivers<br>for hit data<br>readout | optical<br>tranceivers for<br>trigger data<br>readout | hit data<br>readout<br>(DAQ)  | trigger data<br>readout<br>(TDAQ) | Online su | Power supplies & grounding | Monitoring | Cooling<br>services |

| HEPHY            | Austria | Vienna    | x                                                 |                                                       | partially                     | partially                         | probably  |                            | partially  |                     |

| СРРМ             | France  | Marseille | ×                                                 |                                                       | as as one one one one one one |                                   |           |                            |            |                     |

| USTC             | China   | Hefei     | ×                                                 | ×                                                     | ?                             | х                                 |           | x                          | x          |                     |

| IHEP             | China   | Beijing   |                                                   | ×                                                     |                               | х                                 |           |                            |            |                     |

| Jilin University | China   | Changchun |                                                   |                                                       |                               |                                   | ×         |                            |            |                     |

| IFIC             | Spain   | Valencia  |                                                   |                                                       | x                             |                                   | x         |                            |            |                     |

| IFCA             | Spain   | Santander |                                                   |                                                       |                               |                                   |           |                            | X          | ×                   |

| IGFAE            | Spain   | Santiago  | X                                                 |                                                       | x                             |                                   |           |                            |            |                     |

| ITA              | Spain   | Zaragoza  |                                                   |                                                       |                               |                                   |           | ×                          |            |                     |

## **Outline**

- > Introduction

- Overview of collaboration

- ➤ BELLE II VTX upgrade proposal

- Backend electronics and TDAQ system

- > R&D for CEPC vertex detector

- Large area sensor design JadePix-5

- > Summary

<sup>\*</sup>Monolithic Active Pixel Sensor, or CMOS Pixel Sensor are used interchangeably in this talk without distinction

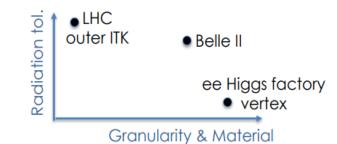

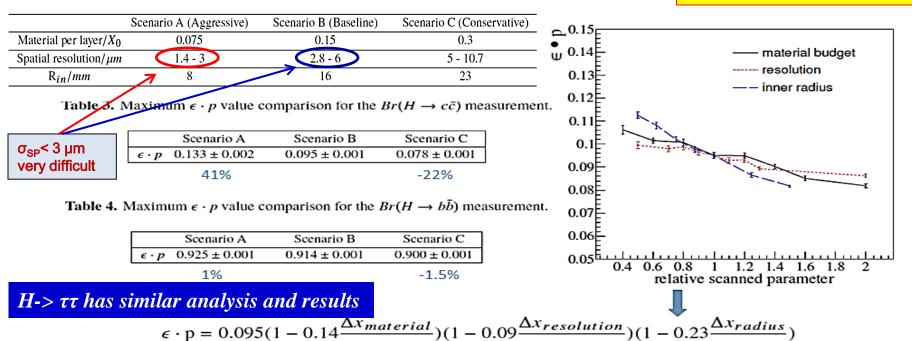

## Physics requirements on the CEPC vertex detector

- Br (H -> cc) is extremely sensitive to the vertex design

- Br (H -> bb) is not really sensitive to the vertex design

Ref: ZG Wu, Optimization on silicon detectors at CEPC, CEPC workshop 2019

Ref.: ZG Wu et al., Study of vertex optimization at the CEPC, 2018 JINST 13 T09002

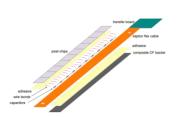

## R&D for CEPC Vertex detector

#### HR-CMOS pixel sensor

- TowerJazz CIS 180 nm process

- *Quadruple* well process

- Thick (~20 μm) epitaxial layer with high resistivity  $(\geq 1 \ k\Omega \bullet cm)$

- Thinning to 50 µm proved

#### SOI-CMOS pixel sensor

- LAPIS 200 nm process

- *High resistive substrate* ( $\geq 1 \ k\Omega \cdot cm$ )

- Double-SOI / PDD-SOI layers available

- Thinning and backside process

- 3D connection technology available

#### Towards Baseline Requirements: CMOS and SOI R&D in Synergy

|             | Pixel size    | Readout Scheme  |

|-------------|---------------|-----------------|

| JadePix-3   | 16 X 23.1 μm² | Rolling shutter |

| CPV-4       | 17 X 21 μm²   | AERD            |

| JadePix-4   | 20 X 29 μm²   | AERD            |

| TaichuPix-3 | 25 X 25 μm²   | Column drain    |

2020-2025 CPV4-3D

## R&D for CEPC Vertex detector

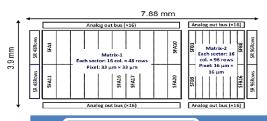

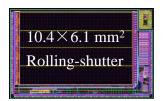

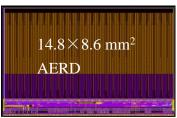

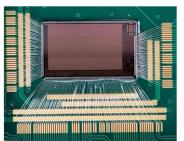

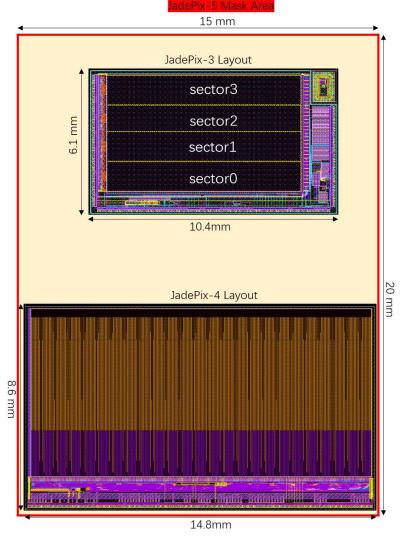

## JadePix-5

- The largest design of JadePix series

- Pixel array 896 rows  $\times$  480 col.

- Sensitive area 17.9 mm  $\times$  14.4 mm (86%)

- Functional blocks verified in JadePix-3/4

- Sensing diode

- Analog frontend

- Pixel logic

- AERD and DAC

- Optimizations on power distribution and signal driving

- Voltage drop across the matrix

- Signal transition on long metal lines

- Optimizations on peripheral readout

- SRAM size and clock frequency

# Shared submission and Technology discussion

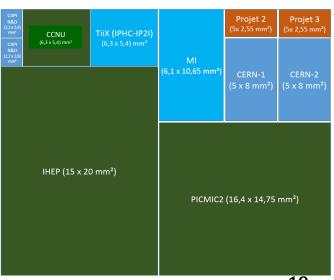

- ➤ Shared submission to Tower 180 nm process (Engineering Run)

- 3/8 mask area for IHEP team (2 cm x 1.5 cm)

- **JadePix-5 design** for CEPC R&D

- Submitted in Apr. 2025

- Paperwork for export license still ongoing with IPHC as coordinator

- ➤ Discussion sessions have been launched on demand and Visit in person during workshops

- Pixel 2024 workshop, Strasbourg, 18-22 Nov. 2024

- VTX workshop, Pisa, 15-17 December (to be announced)

# **Summary**

- ➤ Common R&D efforts of monolithic CMOS Pixel Sensor for the e<sup>+</sup>e<sup>-</sup> collider experiments since 2010

- BES III upgrade, ILC/CEPC, BELLE II upgrade

- > 2 French groups and 3 Chinese groups involved in the BELLE II VTX upgrade

- Chinese groups participated WG5 workshop and expressed interest on various tasks

- Large area MAPS chip JadePix-5 submitted to a shared engineering run coordinated by IPHC

- JadePix-5 is one of two major chips on the same mask

Thank you for your time!