## DESY MicroTCA Solutions: FPGA- and SoC-Based Platforms for Science Community and Next-Generation Research Facilities

2025 MicroTCA/ATCA International Workshop for Large Scientific Facility Control

Michael Fenner, <u>Behzad Boghrati</u>, Stanislav Chystiakov, Holger Schlarb, Robert Wedel, Johannes Zink MSK Accelerator Beam Controls - Digital Hardware Team

Chongqing, China on Sep.15-Sep.17, 2025

# Agenda

- 1. MicroTCA Eco System and Licensing Strategy

- 2. History and Highlight: New Developments

- 3. What we can offer: Community Tools

### **Background**

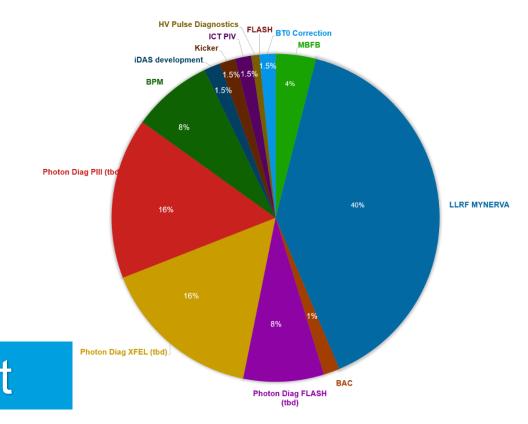

- DESY MSK = Accelerator Beam Controls

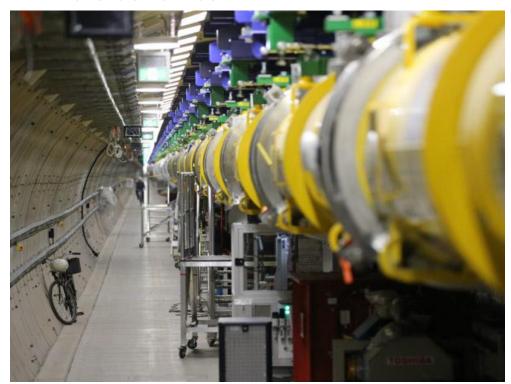

- Responsible for LLRF electronics of large FLASH and XFEL (and other) accelerators:

- As part of large DESY team: concept, design, installation, operation and maintenance

• 100% end-to-end development in-house: hardware (schematics, board, test), firmware and software10 years+ of electronics life time (hostile environment), 24/7 operation, limited access

to electronics

### Main responsibility We develop and maintain digital electronic boards

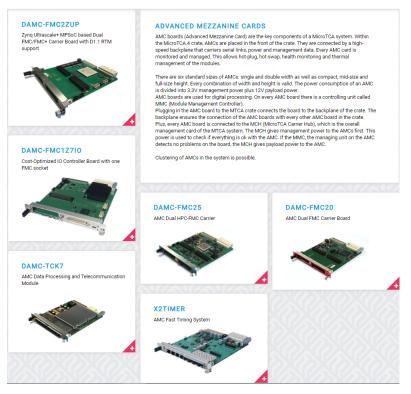

#### **AMC**

DAMC-FMC20 DAMC-FMC25 DAMC-FMC2ZUP DAMC-FMC1Z7IO DAMC-TCK7 DAMC-MOTCTRL

DAMC-DS812ZUP

DAMC-MMCBREAKOUT

DAMC-Template

DAMC-AMCTest

DAMC MACNEED ETEST

DAMC-MMCNEEDLETEST

**DAMC-UNIZUP**

DAMC-X3TIMER DAMC-DS5014

FMC

DFMC-AD16

DFMC-DS800

DFMC-MD22

DFMC-SFP4

DFMC-SIO

DFMC-TC4

DFMC-TestAdp

DFMC-UNI-IO

LISA

~ 5 Boards

RTM

DRTM-PZT4

DRTM-MXC

DRTM-AD84

DRTM-PZT4

DRTM-DS812FT

DRTM-CLKFT

DRTM-Template

DRTM-VM2

**eRTM**

DRTM-HVPM

19-inch boxes

X2 Converter Box LDD (Mezzanine, Carriers)

19-inch components

FRED, FredFan, FredFanPWM (MO) H-Bridge Driver Redundancy Controller 4P Redundancy Controller 3P+1N ZMX Connection Module

TMCB2 GPIOTest PowerSeqPatch REFMOPT patch Patchpanel (Uni-IO) **Eval Boards**

DS8XX DC/DC Eval. Loop Eval.

Motion Controller DCDC Eval.

Coaxipack2 Eval

**Development Support**

RTM Standalone Driver

AMC Bringup Adapter

DFMC-Extender

FMC Test Carrier

SE2DIFF Adapter

Breakout MD22

Breakout AD16

Stand-Alone

DMMC-STAMP RadCon ZMX Test Board NoiseEater

**Company Support**

Struck (MMC)

CAENels

Piezotechnics, E

Piezotechnics, Eicsys (PZT4)

Techlab

Embeck, Hitachi, 7Solutions, D-TACQ, CEA

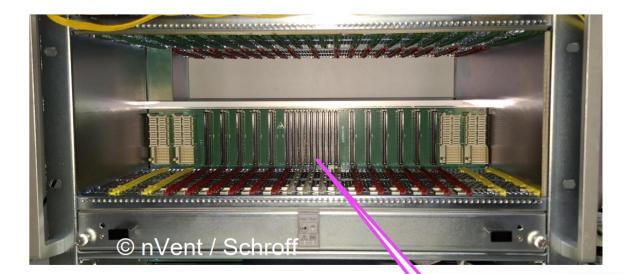

Photo is 6 years old: Underlined Boards are not shown on picture *Italic* Boards are not developed by us, but maintained by us

### **Licensing Strategy**

- We promote an ecosystem

- DESY has licensed almost all developments: components are available for us and for third parties

- Strategy: Concentrate on the application; purchase all "unexciting" infrastructure

### All SoC developments of the last few years

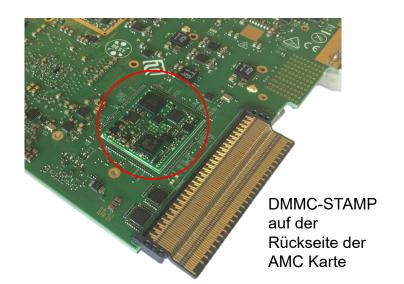

Similarity 1: Boards are all based on DMMC-STAMP

DAMC-FMC2ZUP (Supercarrier) **MPSoC** DAMC-DS5014DR DAMC-X3Timer DAMC-UNIZUP DAMC-FMC1Z7IO DAMC-MOTCTRL (DMMC-STAMP) DAMC-DS812ZUP (RFSoC-based) INSTRUMENTATIO JItrascale+ Zynq-7000 **Ultrascale** MPSoC **RFSoC** 2024 2023 2025 2022 2021 2020 2019

- DMMC-Stamp handles MicroTCA Management

- Complete software framework

- 95% re-use

- Compatibility with all MCHs we know of

- In-system update (from MMC and FPGA)

- Serial-over-IPMI (remote access to the FPGA and MMC UART)

- 2024: over 1000 pieces produced

- used by 30 partners

- 100% test in the needle test adapter

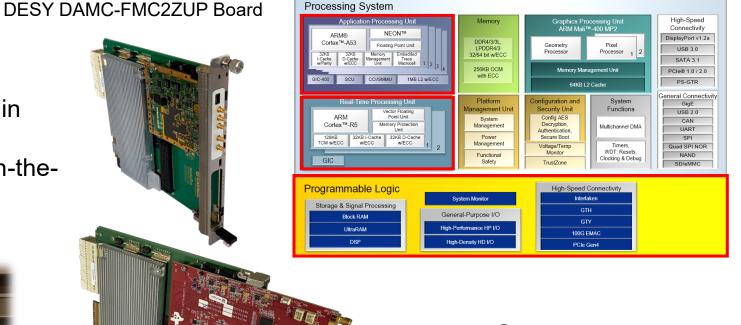

### Why MPSoC?

#### **Similarity 2: Processor inside FPGA**

Everything is SoC-based

Processor-centric approach ("Raspberry Pi in FPGA")

• Changed development method towards: "on-the-fly", "re-use", "modular" and "low-code"

Keywords: IP modules, Linux, Python

DAMC-FMC2ZUP board runs graphical Linux desktop (Displayport)

• Additionally: Web server with Jupyter

DAMC-FMC2ZUP collects data from FMC-DS500; Output via

Python Mathplotlib

Courtesy of J. Marjanovic and S. Farina

### High performance processing MPSoC-based FMC carrier

DFMC-DS800

**DFMC-MD22**FMC 2 channel stepper motor driver

DFMC-AD16

FMC 16-channel A-D Converter

"Working horse", very powerful, very flexible FMC carrier - is part of a family of boards.

#### **Main Features:**

- High-performance FPGA: Zynq Ultrascale+

ZU11EG or ZU19EG

- Full Backplane and RTM D1.1 connectivity

- FMC/FMC+ mezzanine support (28 Gbps)

- Quad-Core ARM Cortex-A53 @1.5 GHz, Dual-Core ARM-R5 RT @600 MHz and Mali-400 MP2 graphics

- PCIe x4 (x8 option on supported systems); Gen.3 supported

- USB type-C Alternate Mode Display Port for standalone operation (no need for additional AMC CPU Module)

- Flexible clocking scheme and front panel connector for external clock input and White Rabbit support

- Supported by all Xilinx development tools (e.g. Vivado HLx)

DESY.

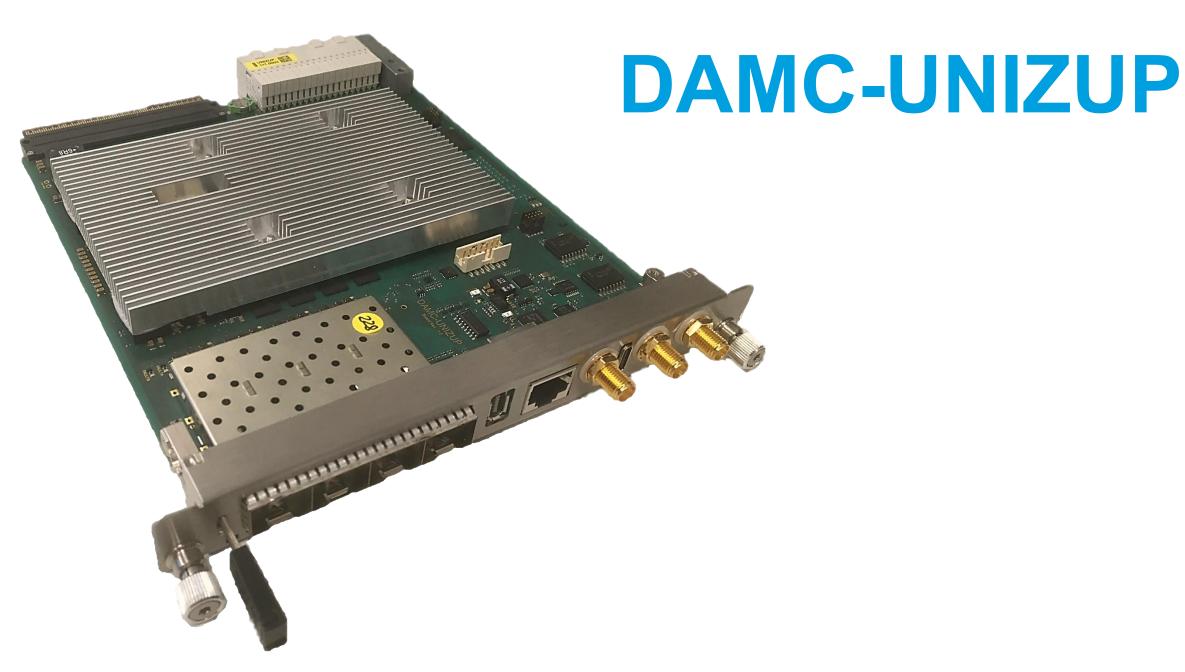

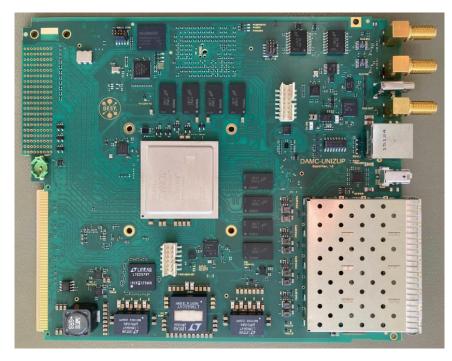

#### **DAMC-UNIZUP**

### INSTRUMENTATION TECHNOLOGIES

#### Inherited features:

- Quad-Core ARM Cortex-A53 @1.5 GHz, Dual-Core ARM-R5 RT @600 MHz and Mali-400 MP2 graphics

- PCIe x4 (x8 option on supported systems); Gen.3 supported

- USB type-C Alternate Mode Display Port for standalone operation (no need for additional AMC CPU Module)

- Flexible clocking scheme and front panel connector for external clock input and White Rabbit support

- Supported by all Xilinx development tools (e.g. Vivado HLx)

#### "Little Sister" of DAMC-FMC2ZUP

- Lower-cost-board with smaller FPGA: hundreds of units will be needed at Petra IV

- 14 instead of 16 layers, 0402 components, (only 0201 capacitors)

#### **Facts**

- Board inherits the technology of DAMC-FMC2ZUP

- Universal MPSoC board with high-performance RTM connectivity

- Large FPGA (in smaller package):

Zynq Ultrascale+ ZU7CG...ZU11EG

#### New:

- 2 x 64bit wide DDR4 interfaces (in total 8GiB RAM)

- 4 integrated SFP+ slots with 16.375 Gbps (not 28 Gbps GTY)

- Connectors for "slow trigger" (RS485 for machine protection) and "fast trigger" on Front Panel

- 2 Front panel clock inputs via SMA, 1 Output

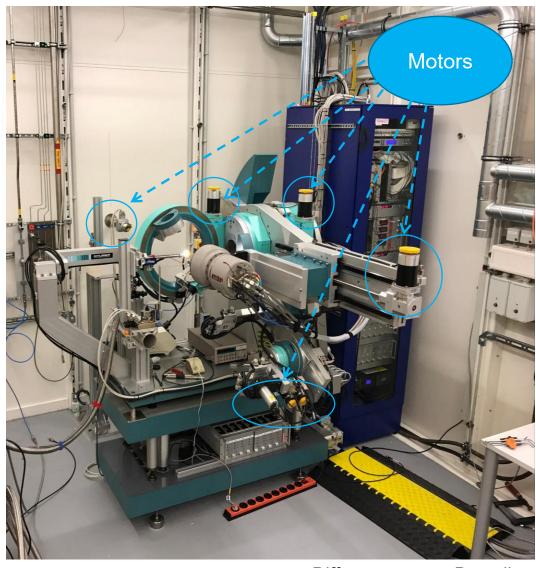

### **Motion Controller**

DESY needs to move motors in experiments

- Popular motion control at DESY:

- Beckhoff EtherCAT (DIN rail)

- OMS MAXv (VME)

#### Already discussed by Michael Randall

- MicroTCA infrastructure is planned for upcoming Petra IV

- A replacement for VME systems is required

- to overcome limitation of 8 motors per card,

- to provide (long-desired) card-to-card communication

- DAMC-MOTCTRL:

- Controls (min.) 48 motors/axis per card (FW depended)

- Scalable interconnection of several cards in the crate and campus-wide

- Position-triggered data acquisition with other MicroTCA cards

- Focus on competitive cost factor (licensing planned)

Diffractometer at Beamline (Martin Tolkiehn)

### **Hardware Plattform**

#### **Hardware Plattform**

- Board is fully running in Rev. A

- No single patch wire.

#### Heterogeneous Approach

- MPSoC (2GB DDR4) and FPGA (4GB DDR3)

- Kintex-7: real-time control

#### MPSoC:

- "Raspberry Pi" inside the FPGA (runs Yocto Linux)

- responsible for non-realtime tasks

- communication to other cards

- 5 SFP+ ports (1Gbps to 10Gbps)

- e.g. 3x Motor interfaces, 2x Ring topology

- HW Support: CAN EtherCAT, SERCOS

- Backplane Ethernet

- 26-pin connector: 3.3V /5V IO

- Monitor/Keyboard interface via USB-C

#### **DAMC-DS812ZUP**

#### 8-Channel Giga-sample Digitizer

#### **Modes of operation:**

8-Channel 800 MSPS digitizer or 4-channel 1600 MSPS

#### New:

- Coaxial Zone-3 connection "RF1.0"

- Front panel/ RTM swapping concept using semi-rigid coaxial RF cables

- Front Panel: oscilloscope-like application and board bring-up

- RTM: space for signal conditioning, filters, etc.

#### **Main Features:**

- 2.7GHz input BW, 12bits, 8-channels (Amplifier Bandwidth: 4.8 GHz)

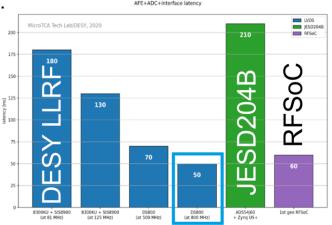

- 50ns end-to-end latency

- Coaxial analog Zone 3 RF1.0 Class

- RF input from front panel or RTM: 800 MSPS / 1600 MSPS

- On-board PLL: 14fs jitter

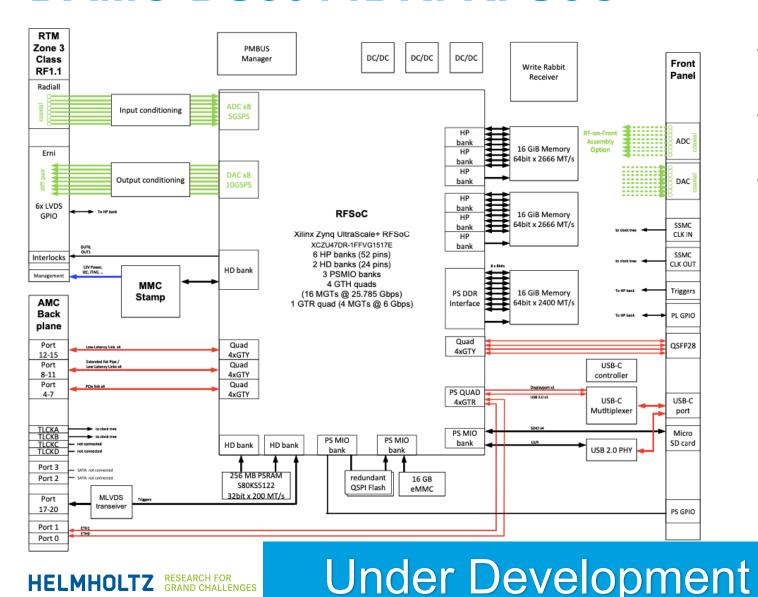

### DAMC-DS5014DR: RFSoC

#### **Features**

- 8x 14 bits ADC, 5 GSPS, 6GHz analog bandwidth

- 8x 14 bits DAC, 10 GSPS, 4GHz analog bandwidth

- DC- and AC operation (assembly option)

# We invite everybody to be part of the MicroTCA ecosystem

What we can offer...

**Creative Commons License**

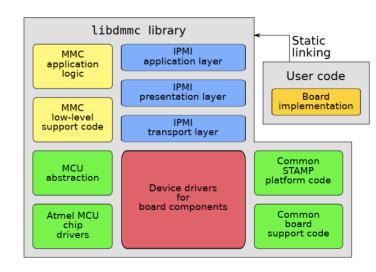

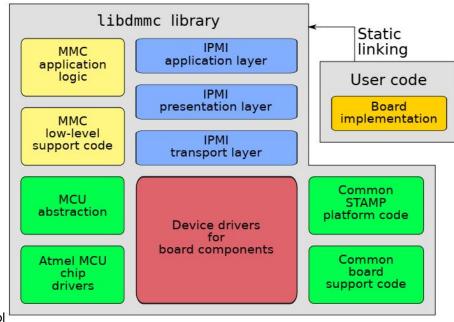

# **DMMC-STAMP: A complete Management solution for MicroTCA**

- System on Module (SoM)

- 25.5 x 29.5 x 2.3 mm

- Pre-programmed firmware

- Evaluation board available (BoB)

- Software Development Kit (SDK)

- MMC firmware customization

- DESY MMC Software Library (libdmmc)

- Example implementations (BoB, DAMC-FMC2ZUP)

- Open Source Tools and Templates

- AMC and RTM Altium Designer Templates

- mmcterm: serial over IPMB

- bin2hpm: create HPM files for IPMI upgrade

- frugy: read and write FRUs

- cpld-img-tools: bitstream conversion for Lattice CPLDs

**Next talk by Patrick Huesmann**

Post-Production test of DMMC-STAMP

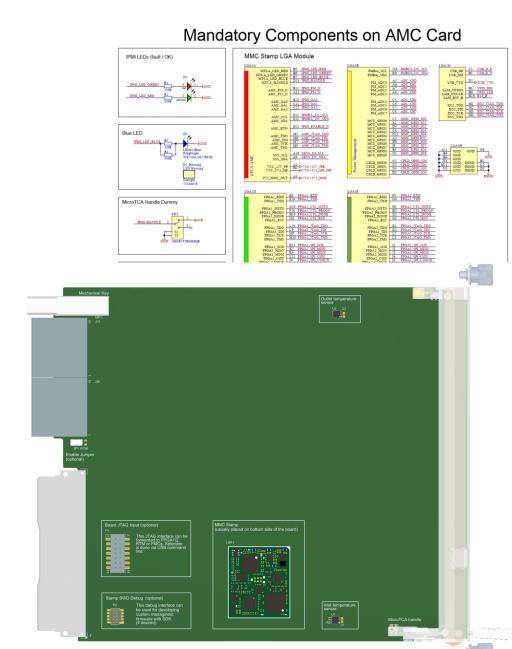

### **MicroTCA.4 Template**

#### **Community Support**

Idea: Jump-Start with MicroTCA as you would with any other board

#### Fully MicroTCA compliant "empty" board

- Already "fully functional"

- Start with correct mechanical shape

- AMC and RTM "only" get power

- All the management is done on DMMC-STAMP

#### Purpose: facilitate development

- Allows design migration (e.g. from VME)

- Source design files (Altium Designer) are provided

- Schematics

- PCB

#### Components:

- MMC SoM, LEDs, Connectors, Temperature Sensors

- USB Interface for management and status

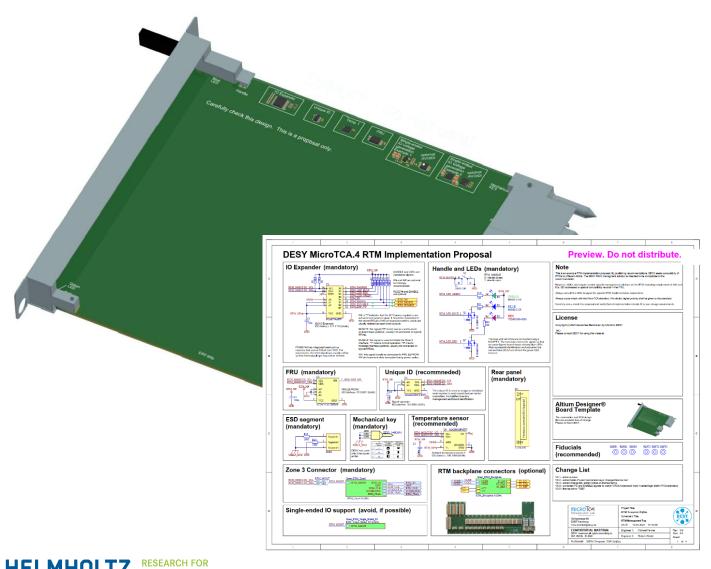

### **RTM Template**

**Community Support**

- We also provide a RTM Template

- Complete guide and "empty board" for own MTCA RTM designs □ Altium Designer Template

- MTCA Standard leaves freedom for RTM interface implementation (vendor-specific) □ risk of noninterchangeable AMC-RTM pairs

- DESY has a "class concept" □

Interchangeable boards

- DESY collected and documented best design practices beyond the standard

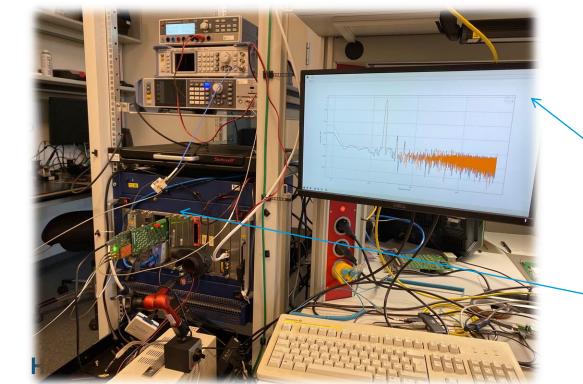

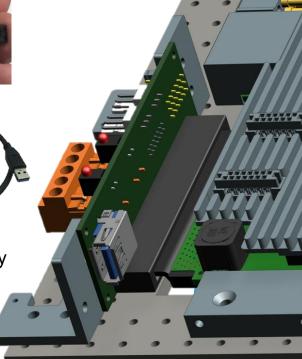

### **Benchtop Setup - Typical Bring-Up environment**

With RTM Support...

- We have flexible lab development tools

- DESY provides them on request:

- Aluminum frame production files

- Bring-up PCB production files

Adatper brings out PCIe x1 Gen. 3 (8Gbps) connectivity "on the lab desk"

### **Typical Lab bring-up Setup**

- Flexible and handy development tools

- DESY provides them (Creative Commons)

- bring-up PCB production files

- Aluminium frame production files

Write an email to me if you are interested in these designs.

# FWK: The Swiss Army Knife of FPGA development

- MSK Firmware group maintains a large open-source repository for FPGA development. It contains:

- BSPs, IPs,

- FWK, Scripts, Tools, Example Designs in Vivado

- Documentation

- Is actively used in DESY's accelerators

- FWK: FPGA development toolkit written in Tcl for large FPGA projects

- Create and implement FPGA project using various vendor tools (including Vivado)

- Handle versioning

- Combine multiple IPs and create address mapping for each register

- Create documentation of the IPs

- Package an IP

- Create an IP using Higher-Level-Synthesis (eg. Xilinx HLS)

- Embedded Linux Creation with Yocto Flow

Visit now! gitlab.desy.de/fpgafw

Documentation: fpgafw.pages.desy.de/docs-pub/doc/

Courtesy of Çağıl Gümüş

### **Summary**

- Overview: DESY's MSK Digital Team develops and maintains FPGA- and SoC-based MicroTCA platforms for accelerator beam control, focusing on reliability, modularity, and full in-house hardware/firmware/software development.

- Ecosystem & Licensing: DESY has licensed nearly all of its developments, making the components accessible both internally and to external partners. The strategy is to focus on application-specific solutions while sourcing standard infrastructure from external suppliers.

- Key Hardware: The DMMC-STAMP ecosystem standardizes MicroTCA management, allowing for significant hardware/firmware reuse (95%), supporting in-system updates, and has been adopted by over 30 partners due to its open licensing strategy. Boards like DAMC-FMC2ZUP (high-performance MPSoC carrier), DAMC-UNIZUP (cost-optimized version), and DAMC-MOTCTRL (motor controller) enable scalable, processor-centric, "Raspberry Pi inside FPGA" solutions for data acquisition and control. High-speed digitizers: Includes 8-channel gigasample digitizers (DAMC-DS812ZUP), RFSoC-based converters (DAMC-DS5014DR).

- Development Support: DESY provides open-source FPGA tools (FWK), Altium design templates for AMC/RTM boards, and lab bring-up setups under Creative Commons to encourage community collaboration and rapid prototyping.

- Future Outlook: Next-generation MTCA efforts focus on PCIe Gen 5, 100 GbE, higher power per AMC (up to 220 W), and lower latency to meet the demands of future large research facilities.

### Thank you!

#### **Contact**

**DESY.** Deutsches Elektronen-Synchrotron

www.desy.de

**Michael Fenner**

MSK michael.fenner@desy.de +49 (0) 40-8998-1885 **Behzad Boghrati**

MSK Behzad.boghrati@desy.de +49 (0) 40-8998-4766

# Thank you!

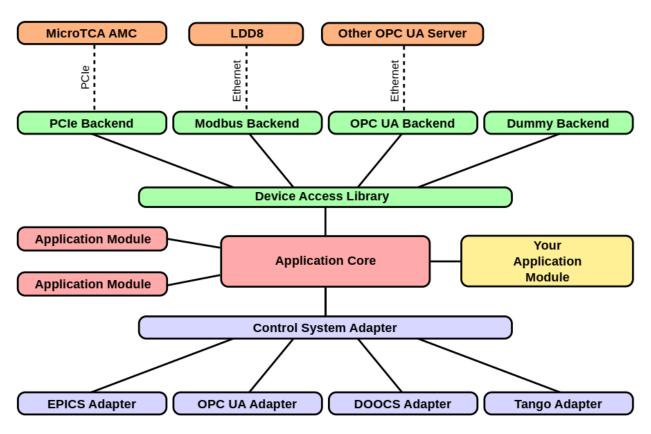

# ChimeraTK – A software tool kit to facilitate control application development

#### **DeviceAccess**

- Common API for different backends

- Seamless integration with FWK

- Improved device abstraction

- Named registers → process variables

- C++ (native)

- Python bindings

- Matlab bindings

- Command line interface

- Graphical user interface

#### **ApplicationCore**

- Model data flow with process variables

- Small self-contained modules

- Modern multi-threading

#### ControlSystemAdapter

- Native integration into control systems

- Publish process variables

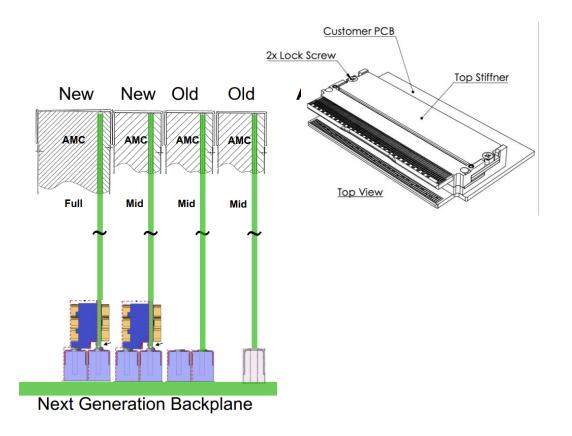

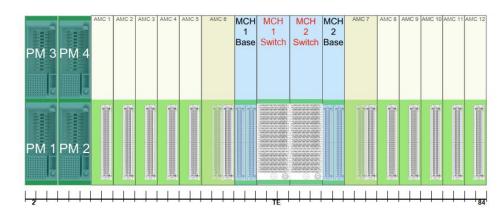

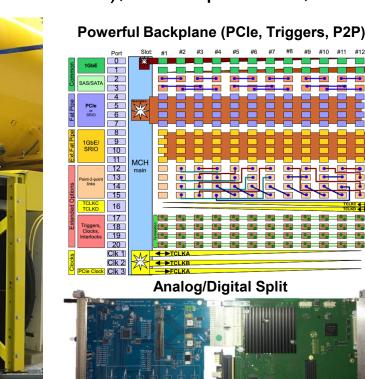

### **Next Generation MTCA**

#### **Community Support**

- PCIe Gen. 5 and 100 GbE → 32 Gbps → lower latency

- Power: up to 220 W per AMC, more power on RTM

- Crate power ≥ 2 kW

- Split MCH

Redundant MCH in center of crate to achieve 32 Gbps in all slots

**Courtesy of Kay Rehlich**