## 2025年4月考核报告

报告人: 李灿明

导师: 赵京周

专业: 核技术及应用

时间: 2025.4.29

## 报告主要内容

#### ■ iRPC 触发数据传输的固件开发

- 数据合并算法实现

- 分时复用链路设计

### ■ iRPC 后端电子学原型系统搭建

- 探测器数据模拟

- 慢控链路搭建

- DAQ链路搭建

#### ■ iRPC数据读出系统相关研究

- Slink ip例程

- DTH/BEB背板连接映射

### ■ iRPC探测器四路取数实验设计

- PETIROC 刻度

- TDC 通道一致性调整

- 四路数据分析

#### ■ 研究目的

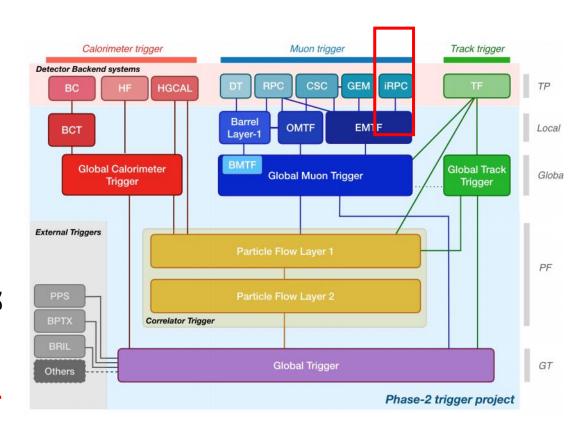

- iRPC 探测器的击中信息由前端电子学采集,后端电子学在完成簇查找以及角度转换之后,将其作为iRPC的触发条件 (TP) 输出给端盖缪子寻迹器 (Endcap Muon Track Finder, EMTF) ,和其他探测器的信息一起用来进行端盖区的Muon 径迹查找。

- 在run3取数阶段,需要在原型机上开发iRPC连接EMTF这部分固件,与EMTF联调进行功能验证。

- 固件主要功能模块:数据合并算法实现、分时复用链路设计

CMS 二期升级Muon探测器的触发系统结构

#### ■ 数据合并算法实现

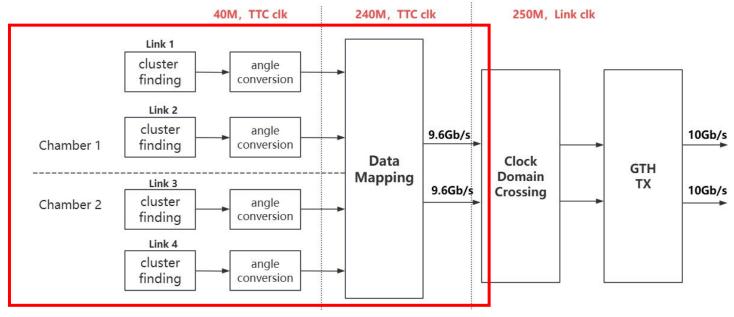

- 输入:在目前的固件设计中,每块后端板连接两个iRPC chamber,共4条输入链路,在经过簇查找算法处理后,每路每BX (40M)输出64bits (包含两个cluster)信息。

- **输出**:数据合并算法需要将一块chamber对应的两条链路的簇团信息进行**聚合**,从64bits数据中提取出两个 簇团数据,分别打包好链路信息以及簇团信息,在**240M**时钟下对数据进行**对齐和排序。**

#### 分时复用链路设计

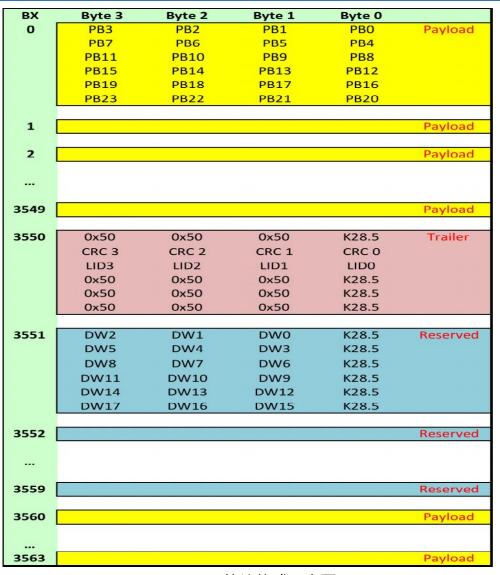

- 按束流周期 (3564BX) 对链路数据进行封装

- 根据束团计数进行区分,基于"分时复用"的思想,实现触发数据和控制信息的链路共享

- Payload:

包含240M时钟下的触发数据。在送入高速串行收发器 GTH前涉及到时钟域的转换,设计了环形缓冲区填充数据

Trailer:

包含了CRC校验码,用于数据校准;以及Link ID信息,用于判断哪一条链路在发送数据

Reserved: 预留位

#### ■ 测试结果

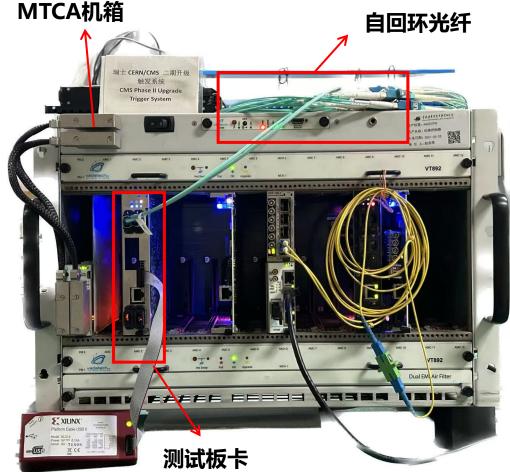

- 在后端电子学板(CPPF)上利用ILA(逻辑分析仪)工具,进行了单板自回环测试,数据初步验证正确。

- 测试结果已在RPC电子学合作组会议上汇报,后续将前往CERN计划进行探测器联调测试。

#### 发送端

接收端

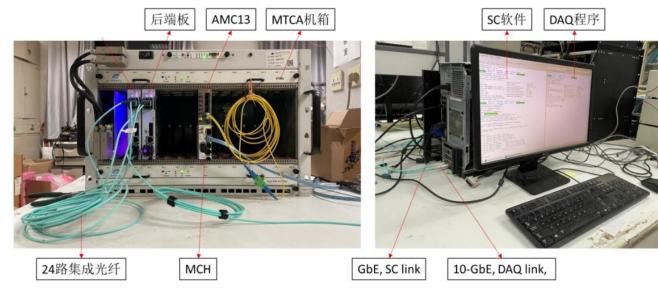

MTCA机箱测试平台

### iRPC探测器四路取数实验设计

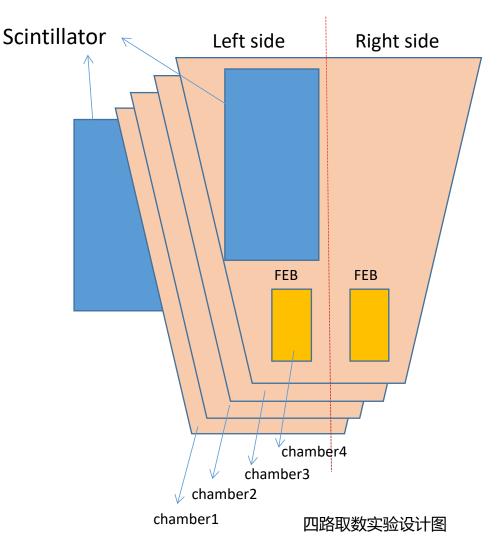

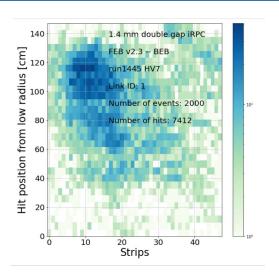

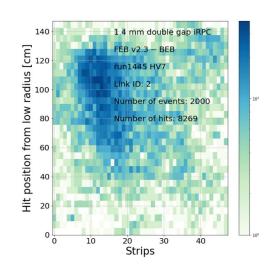

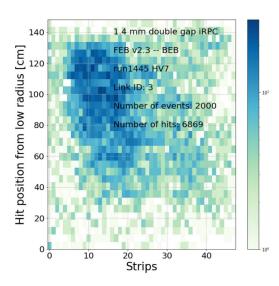

#### ■ 实验设计

- 为了进一步验证目前BEE四路固件的功能,与合作组成员沟通后设计了实验方案,在CERN 904 Lab搭建了测试系统。

- 包括四块iRPC RE3/1 Chamber, 每块Chamber对应 两块前端板,取左侧前端板分别命名Link1/2/3/4

- 通过上下两块闪烁体探测器进行**宇宙线符合**,作为 Trigger信号送入系统并进行取数。

- 在取数前,对前端板 PETIROC 进行刻度,并调整前端板 TDC 通道一致性。

## iRPC探测器四路取数实验设计

#### ■ 前端板的刻度与对齐:

• 将目前的慢控脚本由两路扩展至四路,刻度和对齐后的参数通过Sitcp链路经由后端对前端进行配置

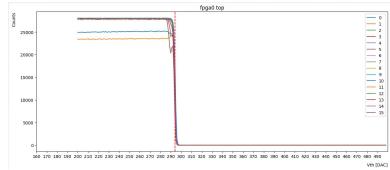

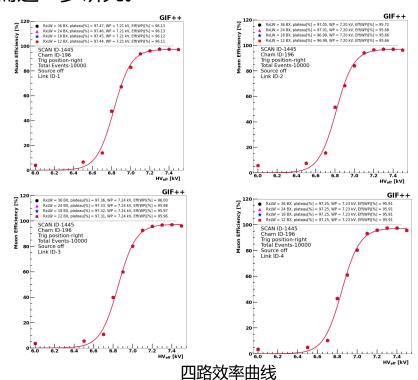

PETIROC 对齐后的阈值扫描曲线

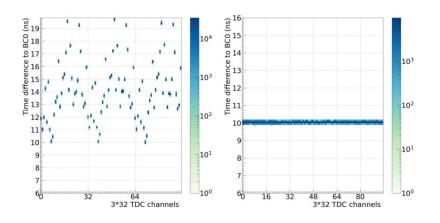

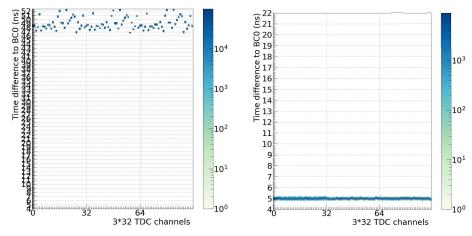

TDC 通道一致性调整之前 (左) 和之后 (右) 的结果对比

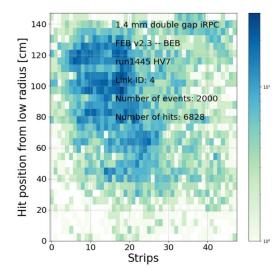

#### ■ 数据分析:

- 在每个高压点下(6300V~7300V)取2000个事例数据, 进行了效率曲线分析。

- 各链路效率接近,初步验证了四路固件可以工作,但效率 偏低,需进一步研究。

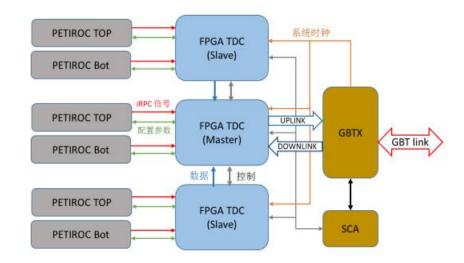

## iRPC 后端电子学原型系统搭建

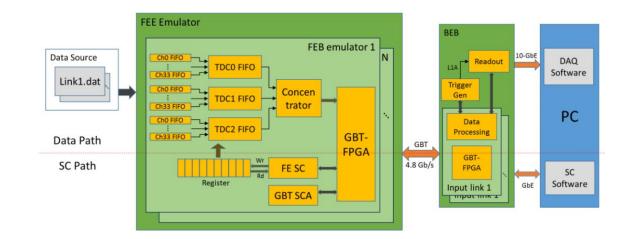

#### ■ 探测器击中数据模拟:

- 根据预设的事例率,用python程序随机模拟粒子在 探测器上的击中位置,包含48根条共96个TDC通道

- 按照上行链路的数据要求对击中数据进行组装,包括TDC数据、有效标志位等,传输给后端电子学

#### ■ 慢控链路搭建:

- 基于ipbus的干兆慢控链路,对上位机环境进行配置

- 通过慢控链路配置BEE的初始化及算法使能等

#### ■ DAQ链路搭建:

- 基于商用IP核实现DAQ万兆读出

- 通过后端自触发进行取数,将得到的DAQ数据与模拟数据进行比对,验证后端固件算法的正确性

FEE数据模拟

CMS二期触发升级原型机系统

## iRPC数据读出系统相关研究

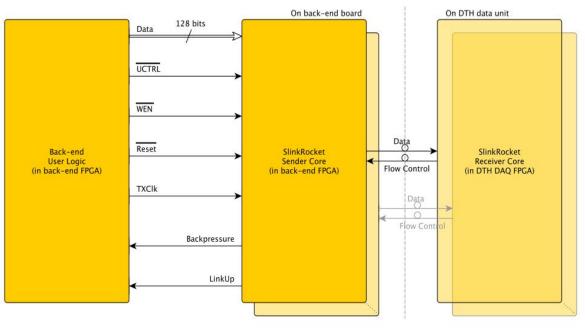

#### ■ SlinkRocket IP例程:

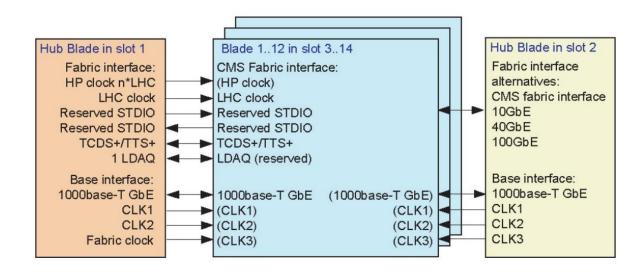

在CMS二期升级计划中,后端电子学板将通过光纤与ATCA 机箱中的DTH板(DAQ, Trigger and Timing Hub)连接, 进行DAQ数据读出。传输协议为CERN自定义的SlinkRocket

Slink IP example

#### ■ DTH/BEE背板连接映射:

确定了后端电子学板与DTH板的背板连接信号,目前 实验室已有DTH板但没有二期升级的后端电子学板 (Serenity),计划设计一块连接板将实验室的 ATCA原型板与DTH板进行供电和背板连接。

# 请各位老师批评指正!

# Backup

## iRPC探测器四路取数实验设计

#### WebDCS QC3

Standby

HV after scan:

Chamber side:

| Monitoring        |                 | HVscan |   | Stability                               | Hardware         | Settings                                |   |    |  |

|-------------------|-----------------|--------|---|-----------------------------------------|------------------|-----------------------------------------|---|----|--|

| lish Valtage Coop |                 |        |   | 0.00-9000000000000000000000000000000000 | 9660 96614960011 | 0.0000000000000000000000000000000000000 |   |    |  |

| ligh Voltage Scan |                 |        |   |                                         |                  |                                         |   |    |  |

| ype scan:         | Efficiency scan |        | v |                                         | Comments:        |                                         |   |    |  |

| Vaiting time:     | 1               | (min)  |   |                                         |                  |                                         |   | M. |  |

|                   |                 |        |   |                                         | Labels:          | efficiency                              | ~ |    |  |

| leasure time:     | 0.2             | (min)  |   |                                         |                  |                                         |   |    |  |

| Chamber C             | MS-RE3-1-Ghent-208 | CMS-RE3-1-Ghent-220 | CMS-RE3-1-Ghent-261 | CMS-RE3-1-Mexico-282 | Max triggers |

|-----------------------|--------------------|---------------------|---------------------|----------------------|--------------|

| HV <sub>eff</sub> 1   | 6300               | 6300                | 6300                | 6300                 | 2000         |

| HV <sub>eff</sub> 2   | 6400               | 6400                | 6400                | 6400                 | 2000         |

| -IV <sub>eff</sub> 3  | 6500               | 6500                | 6500                | 6500                 | 2000         |

| IV <sub>eff</sub> 4   | 6600               | 6600                | 6600                | 6600                 | 2000         |

| -West 5               | 6700               | 6700                | 6700                | 6700                 | 2000         |

| IV <sub>eff</sub> 6   | 6800               | 6800                | 6800                | 6800                 | 2000         |

| IV <sub>eff</sub> 7   | 6900               | 6900                | 6900                | 6900                 | 2000         |

| IV <sub>eff</sub> 8   | 7000               | 7000                | 7000                | 7000                 | 2000         |

| IV <sub>eff</sub> 9   | 7100               | 7100                | 7100                | 7100                 | 2000         |

| IV <sub>eff</sub> 10  | 7200               | 7200                | 7200                | 7200                 | 2000         |

| -IV <sub>ett</sub> 11 | 7300               | 7300                | 7300                | 7300                 | 2000         |

#### Start HV scan

## PETIROC 对齐和TDC 通道一致性调整

前端板板载 6 个 PETIROC,每个 PETIROC 有 32 个独立的甄别器,输入信号过域即可产生输出,目前每个 PETIROC 只使用了其中 16 个通道。甄别器的阈值决定了 PETIROC 的灵敏度,也间接反映了 iRPC 对粒子击中的响应能力。为了保证 PETIROC 对每个 iRPC 读出条传入信号的响应能力一致,必须进行通道对齐。PETIROC 通道对齐的直观判断方法为其各通道的阈值扫描曲线是否重合。PETIROC 芯片为了均衡 32 个通道的响应,提供了两个调整模块。一是整个PRTIROC 通用的 10b DAC(可设置的数值范围为 0~1023),可确保在动态范围内调节阈值。二是为每个通道提供一个单独的 6b DAC(可设置的数值范围为 0~63),以实现 PETIROC 所有通道响应一致。

通过阈值扫描测试来评估前端板 PETIROC 的各个通道是否对齐,其具体操作为:对 PETIROC 进行 10b DAC 扫描,并在每个 10b DAC 的数值下读取一定时间内各通道产生输出的次数。在没有任何外部信号注入的测试条件下,当阈值设置的非常低时,噪声能够过域,随着阈值逐渐提高,过域的噪声会逐渐减少直至为 0。如果 PETIROC 各通道的响应能力一样,那么每个通道在相同阈值(10b DAC)下的相同时间内得到的输出信号的个数应该非常接近。

要保证前端板 TDC 对每个 iRPC 读出条信号到达时间的测量标尺一致,除前端板所有通道共用的时间参考信号需一致外,所有与 PETIROC 相连接的通道对同一信号给出的时间戳数值也应当一致。通过慢控制对前端板进行设置,使得前端板 3 个 FPGA 的所有与 PETIROC 相连接的 TDC 通道同时获得输入并给出时间戳,进而来分析前端板 TDC 通道的一致性。

基于后端固件以指定通道的"TDC data"产生触发信号的功能,设定只要接收到来自前端板 FPGA1 的 BC0 通道的 TDC data 便产生触发信号,进而读出前端板 3 个 TDC 所有通道的"TDC data"。那么在一个事例中就包括了 96 个PETIROC 通道的时间戳和 3 个 BC0 通道的时间戳。将每个事例所包括的 96 个TDC 通道的时间戳与 FPGA1 BC0 通道的时间戳的差值进行统计,得到图4.25(左),可以看出 3 个 FPGA 都存在各 TDC 通道时间测量不一致的现象。