# LHCb Real Time Analysis

Shanzhen Chen, on behalf of Peilian Li

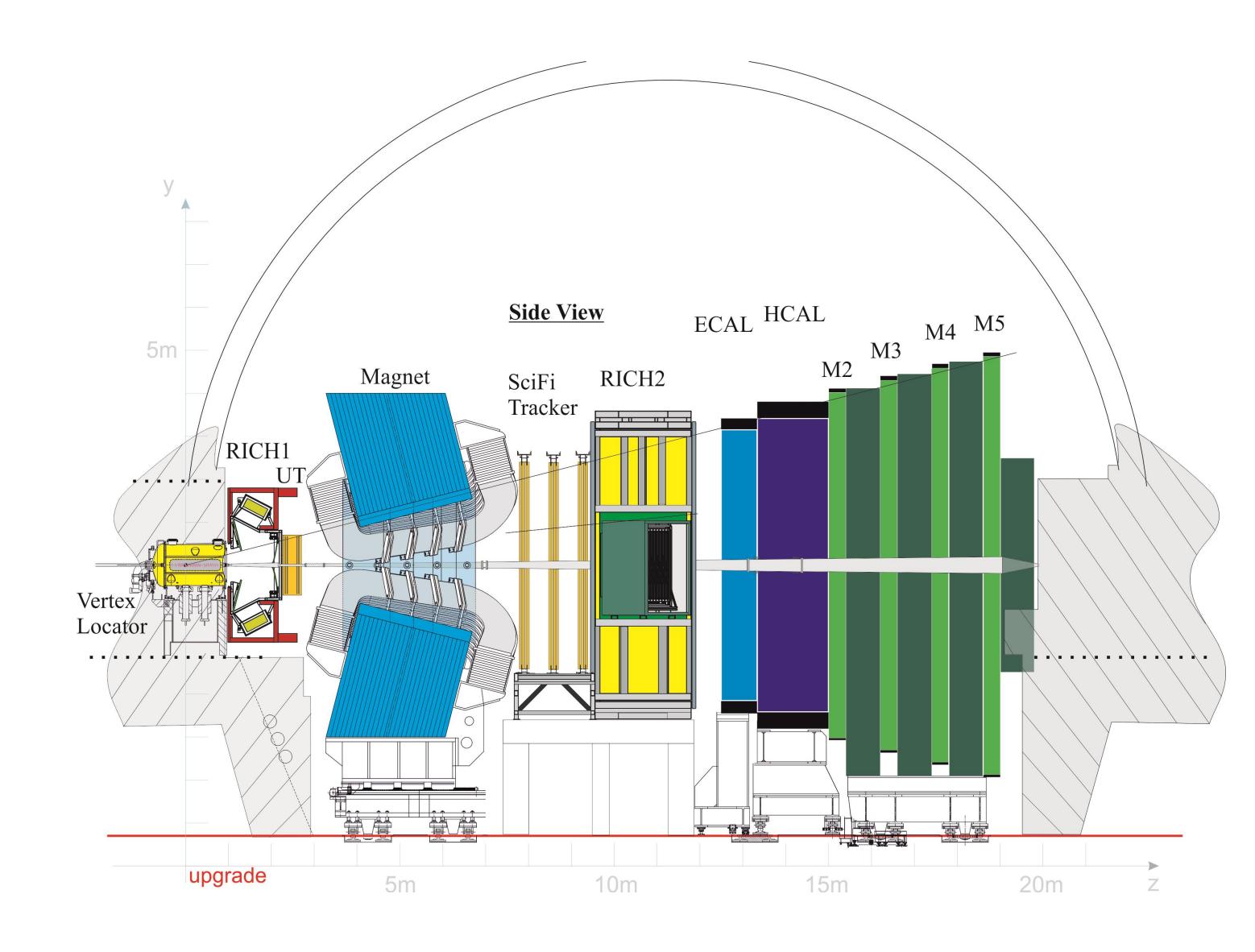

## The LHCb Upgrade I detector

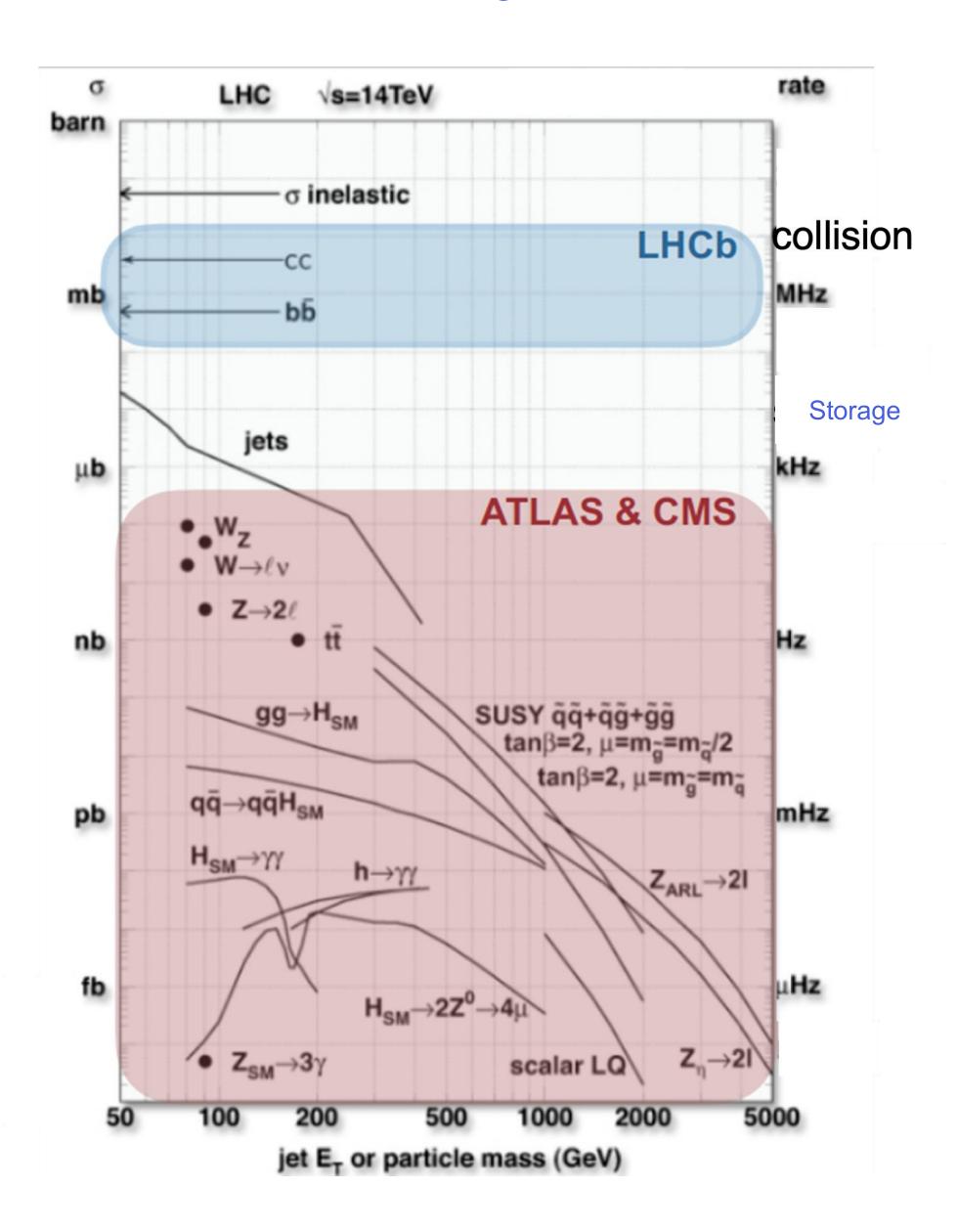

- Dedicated for flavor physics studies, but also serve as a forward general-purpose detector

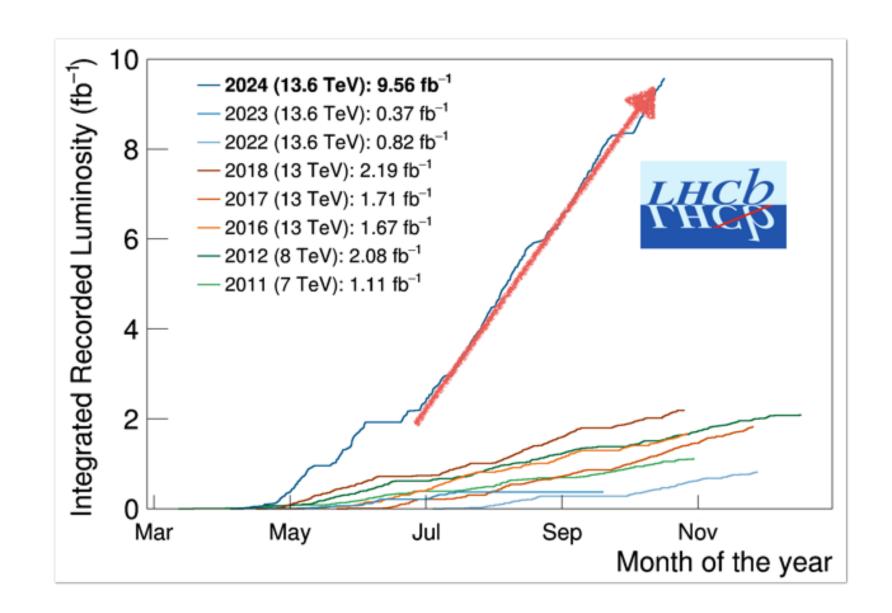

- Increased instantaneous luminosity 5× from Run 2 to 2×10<sup>33</sup>cm<sup>-2</sup>s<sup>-1</sup>

- New tracking detectors

- Improved readout electronics to meet rate requirements

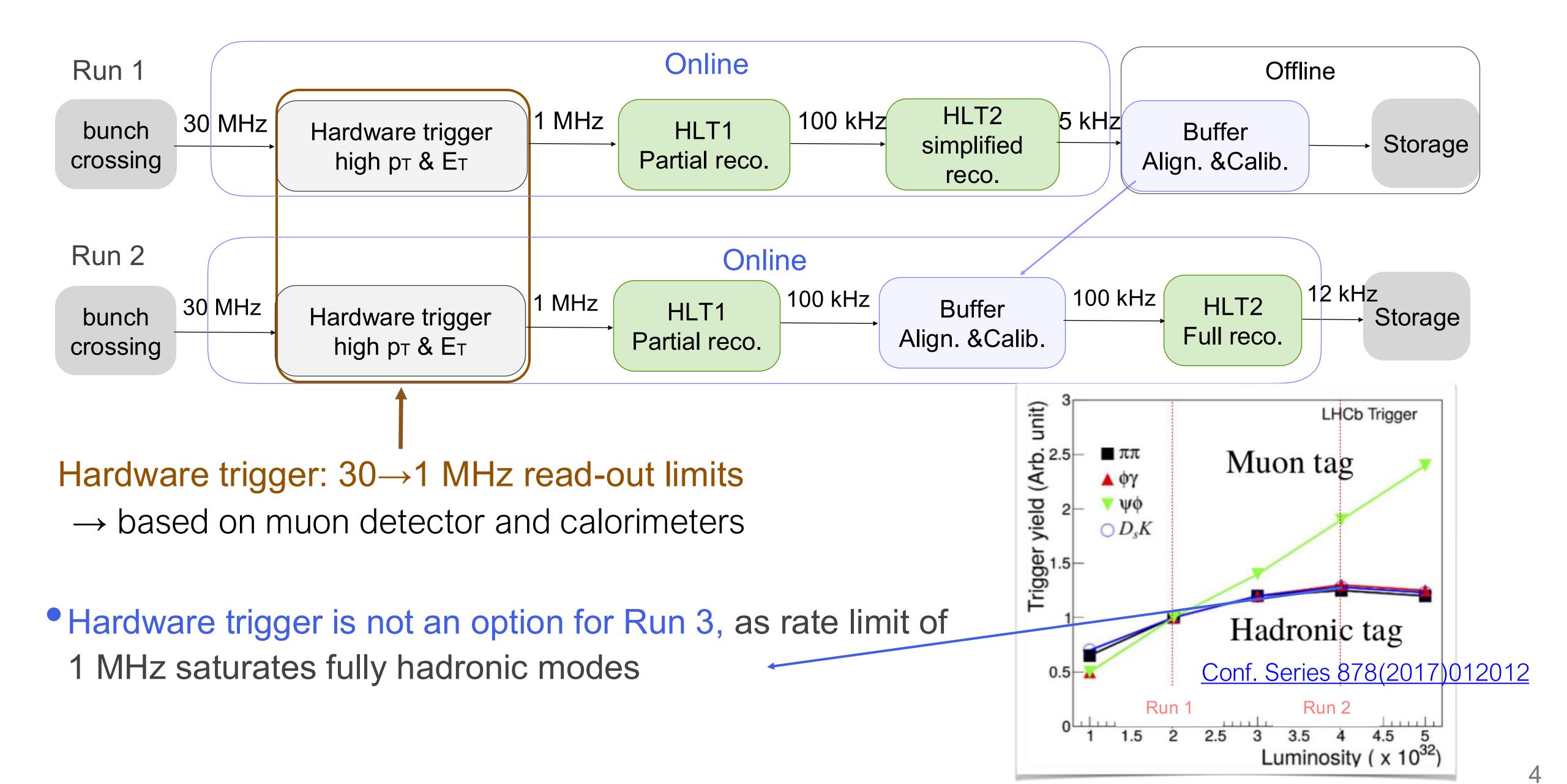

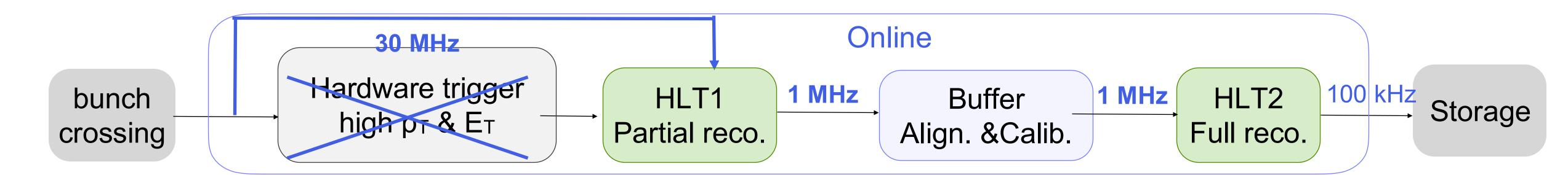

- No hardware trigger

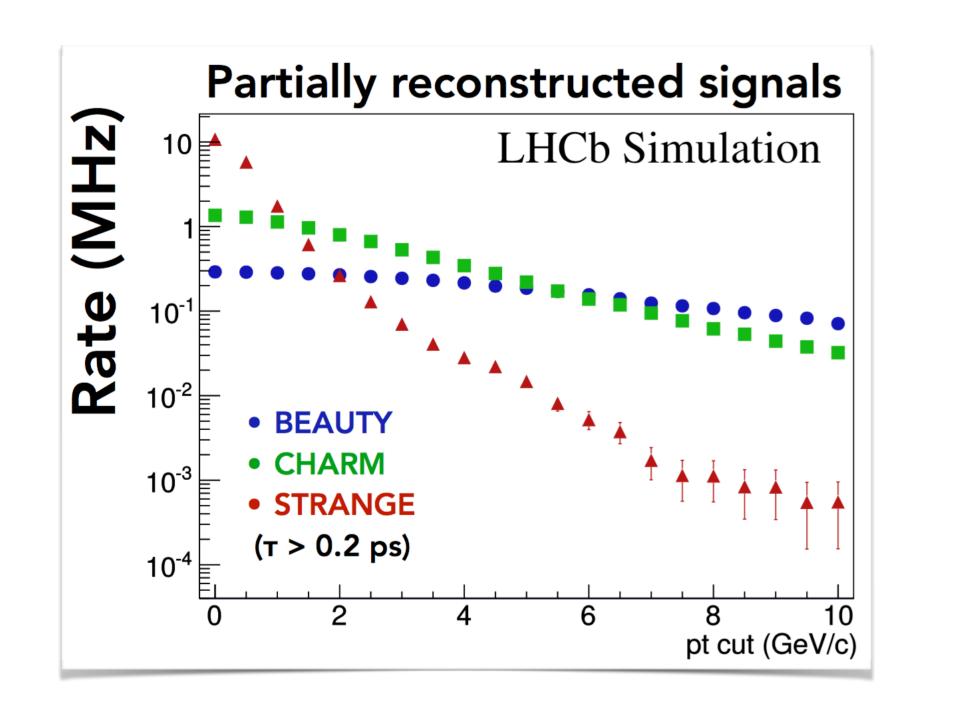

## LHCb: a heavy flavour factory

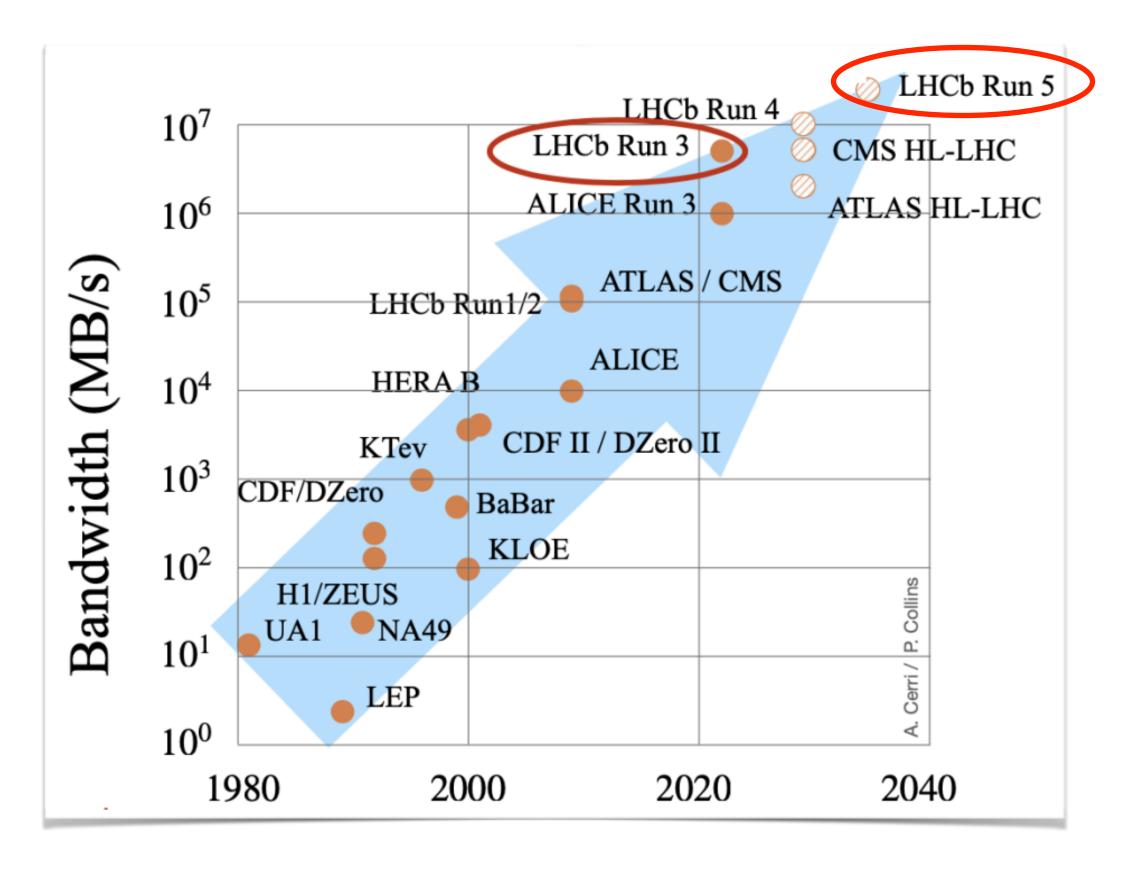

#### Pioneering in novel trigger strategies!

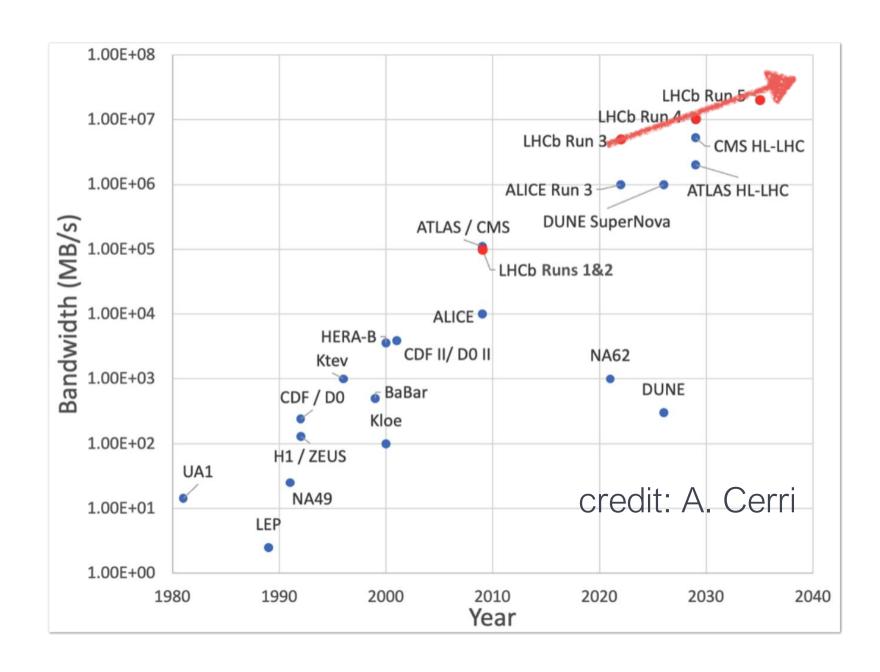

Signal rate at MHz level

Highest data processing rate of any HEP experiment!

## A bit of trigger history

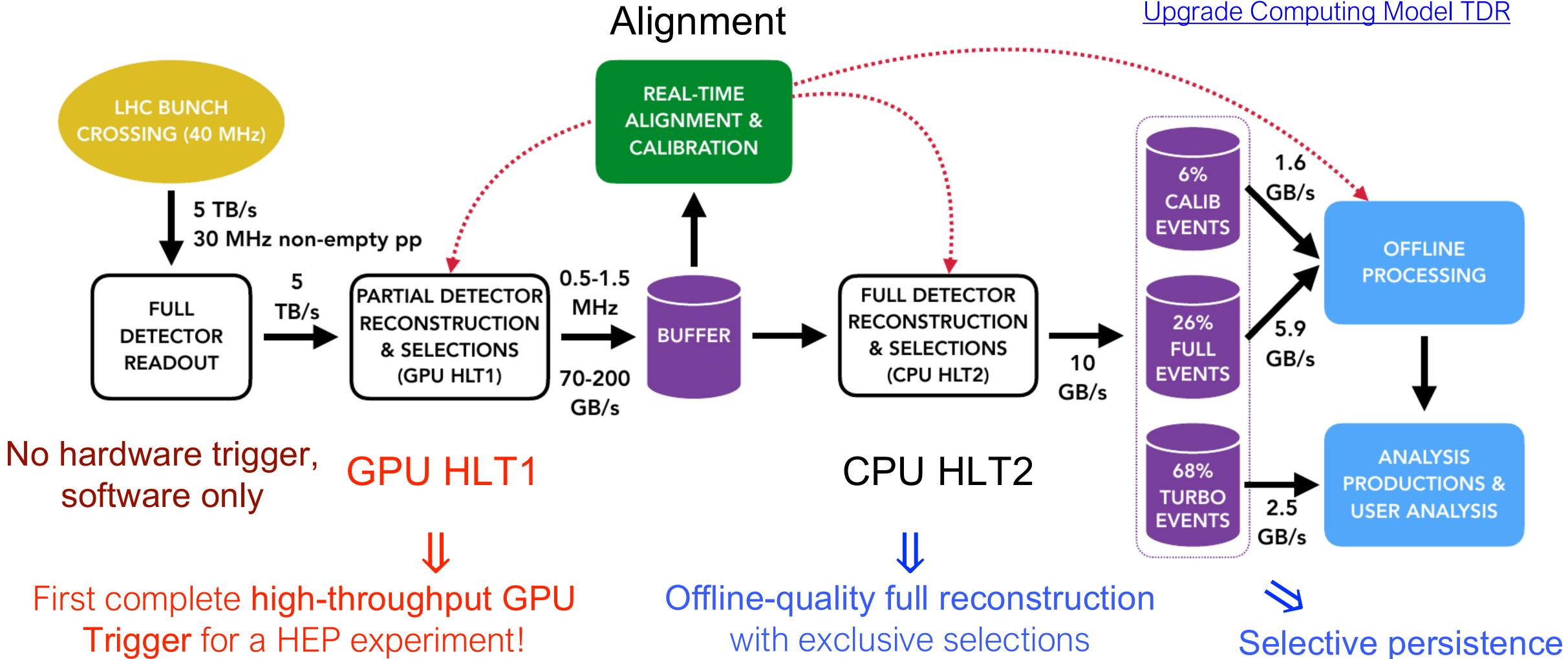

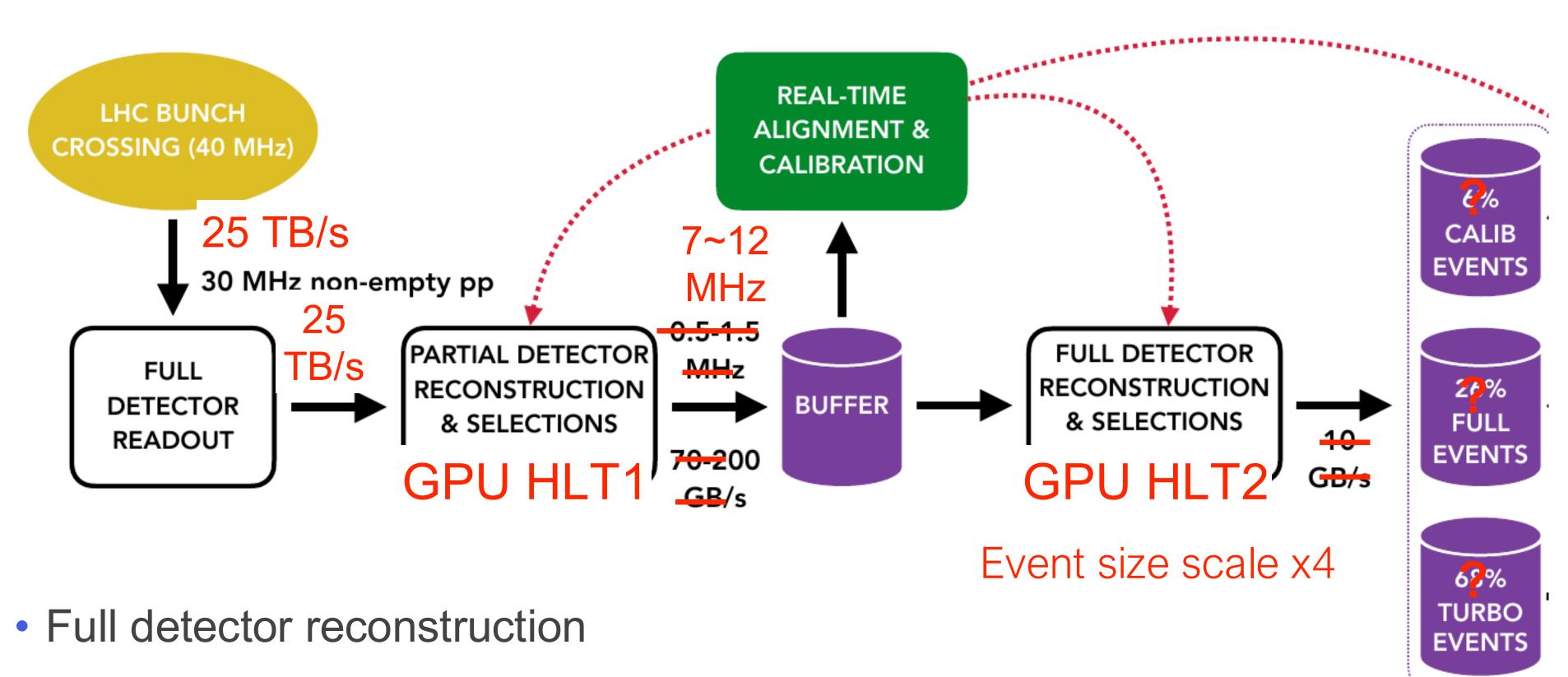

## LHCb Run 3 Trigger

#### Online - Real Time Analysis

### LHCb Run 3 Data Flow

All numbers related to the dataflow are taken from the LHCb

Upgrade Trigger and Online TDR

Upgrade Computing Model TDR

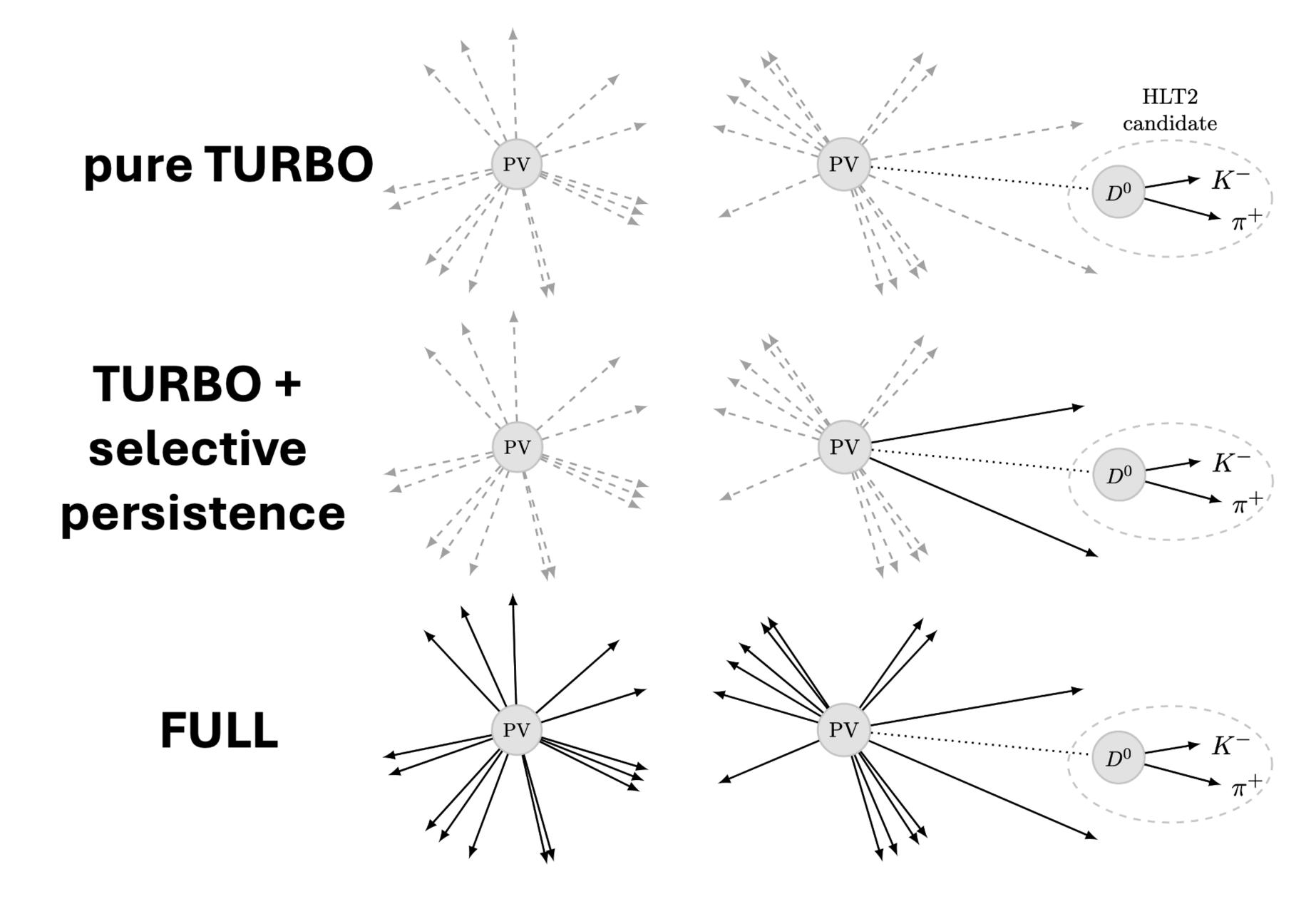

# Types of data

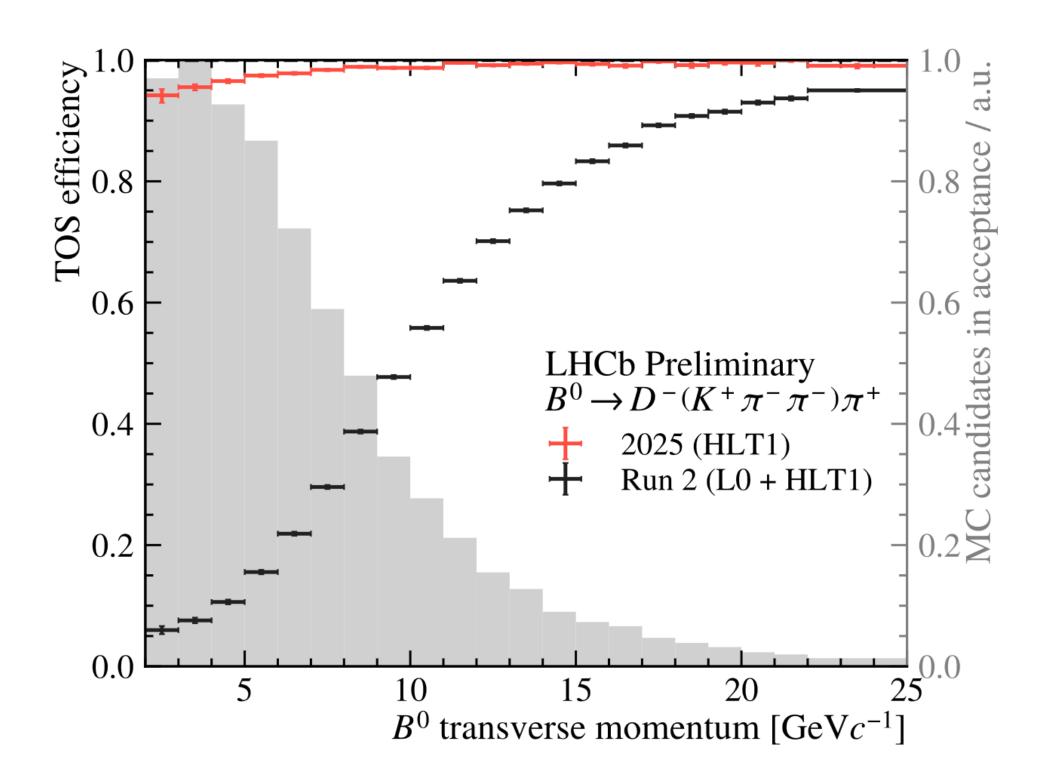

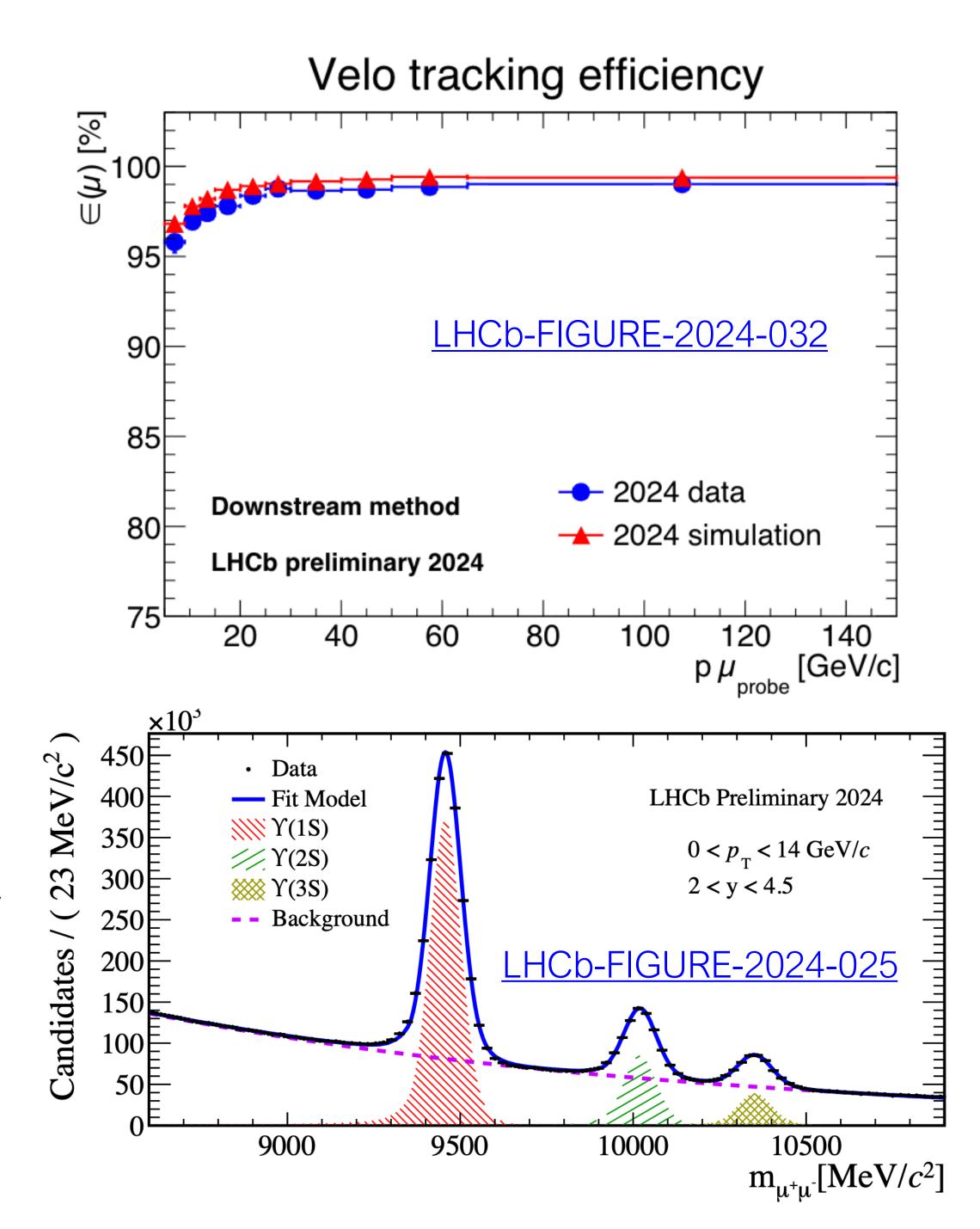

### LHCb Run 3 Performance

Significant improvement in HLT1 efficiency (2-4x for hadronic modes)

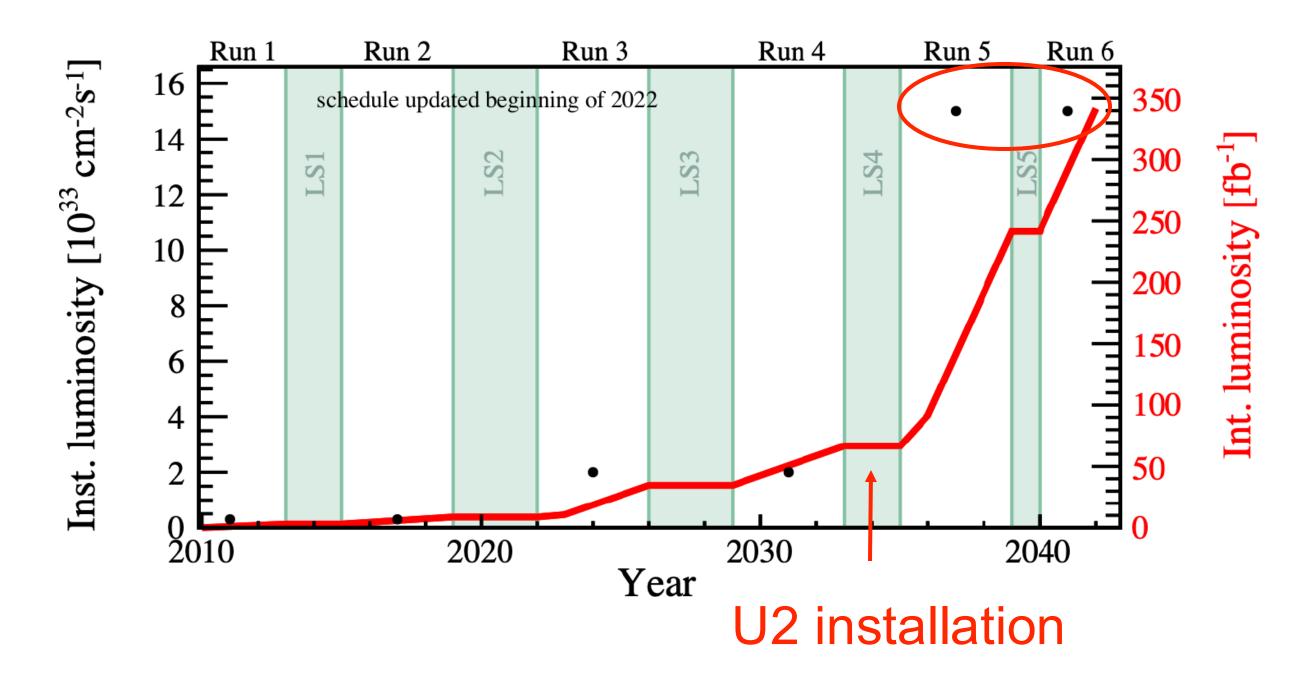

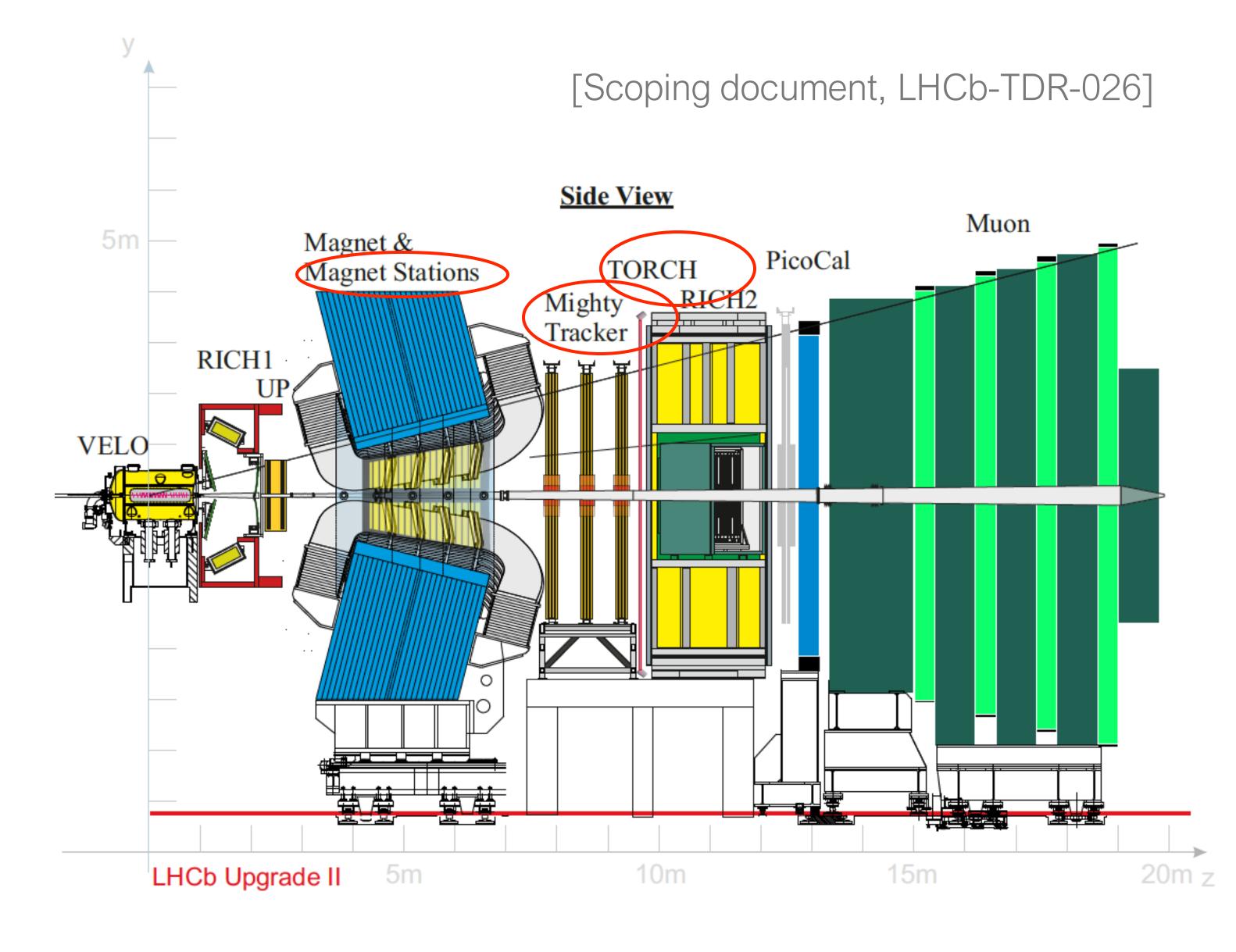

## LHCb Upgrade II

- $5x \sim 7.5x$  higher luminosity, up to  $10^{-34}$  cm<sup>-2</sup>s<sup>-1</sup>

- Data rate: from 5 TB/s  $\Rightarrow$  25 TB/s

- "triggerable" decay in every event

- Larger event size (more PVs + timing info)

- Computing and storage of HLT2 needs scale

quadratically [Scoping document, LHCb-TDR-026]

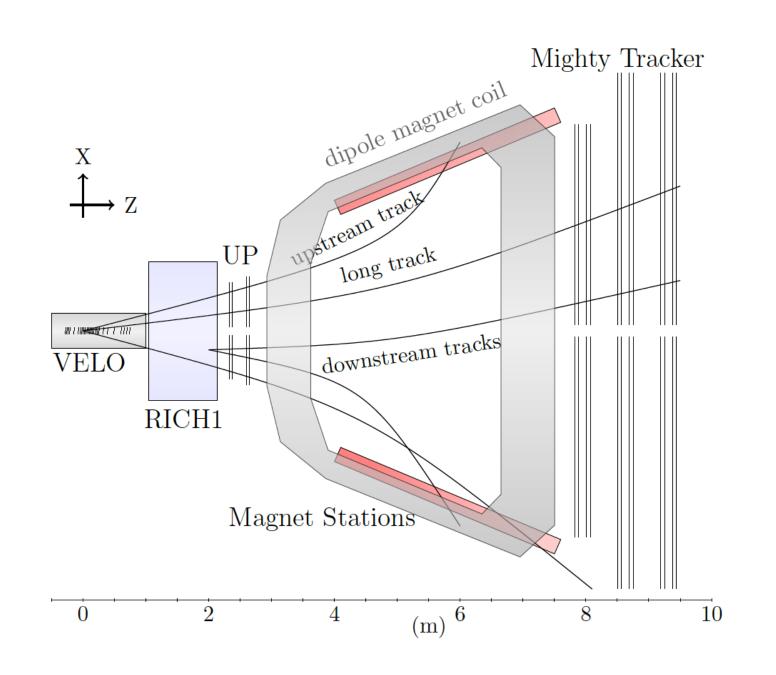

## LHCb Upgrade II

Same layout as Run 3, but with

- Pixels for VELO + UP + Mighty

- TORCH + Magnet Station

- Timing information from VELO,

TORCH/RICH and PicoCal

Find more in Fiona's talk and Elena's talk on Thursday

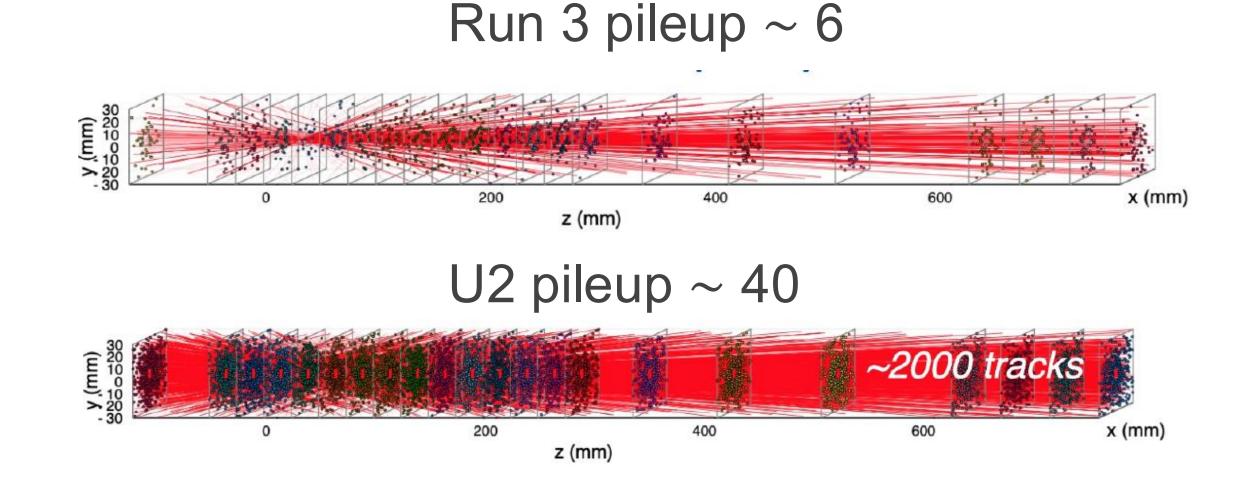

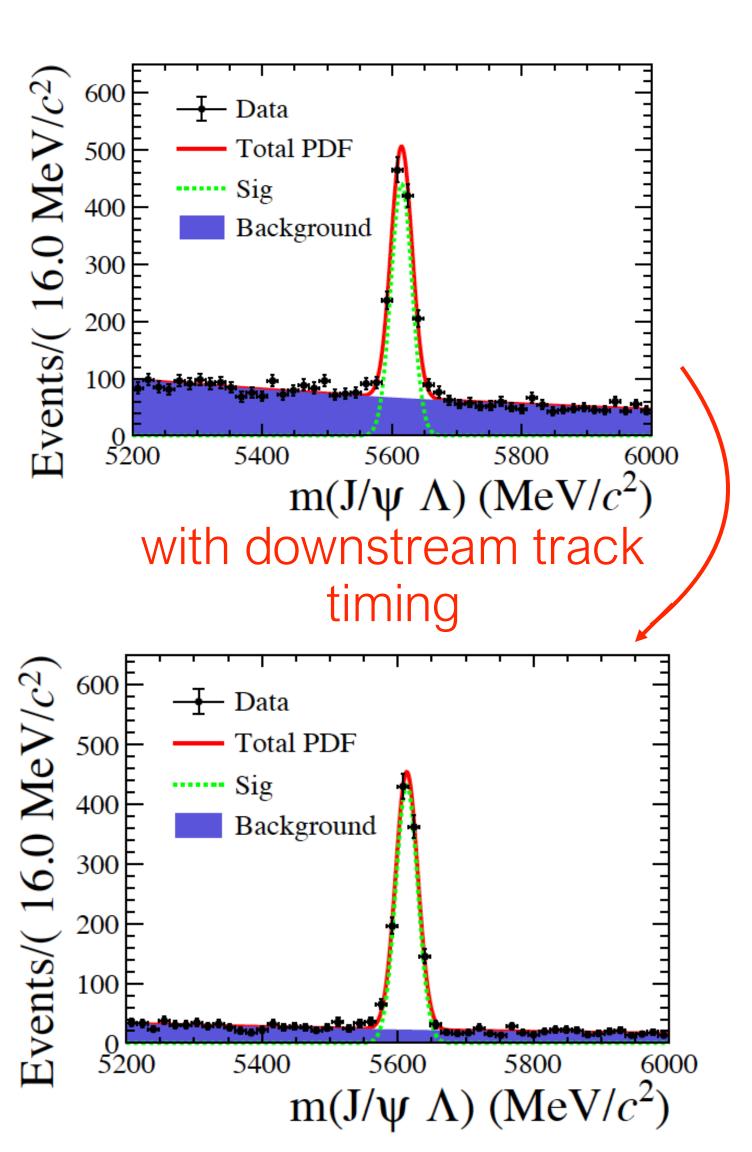

## Pile up mitigation with timing

- Timing is necessary for HL-LHC to mitigate the pile-ups

- 4D Tracking and Vertexing, and timing in PID

Efficiency 30 ps timing window O COORTOO COORTOON O 0.8z [mm] VELO UI (3D) @ UI Luminosity 0.4x [mm] VELO UI (3D) @ UII Luminosity VELO UII (4D) @ UII Luminosity 0.2 $n_{\text{tracks}}$  (has b hadron) 200 50 100 150  $n_{

m tracks}$ 50 z [mm]

[Scoping document, LHCb-TDR-026]

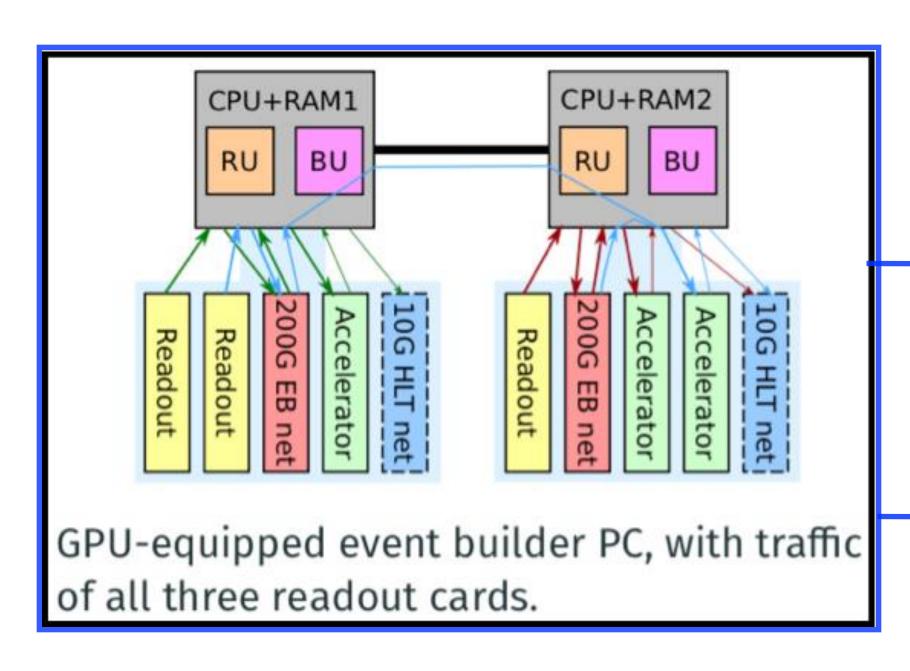

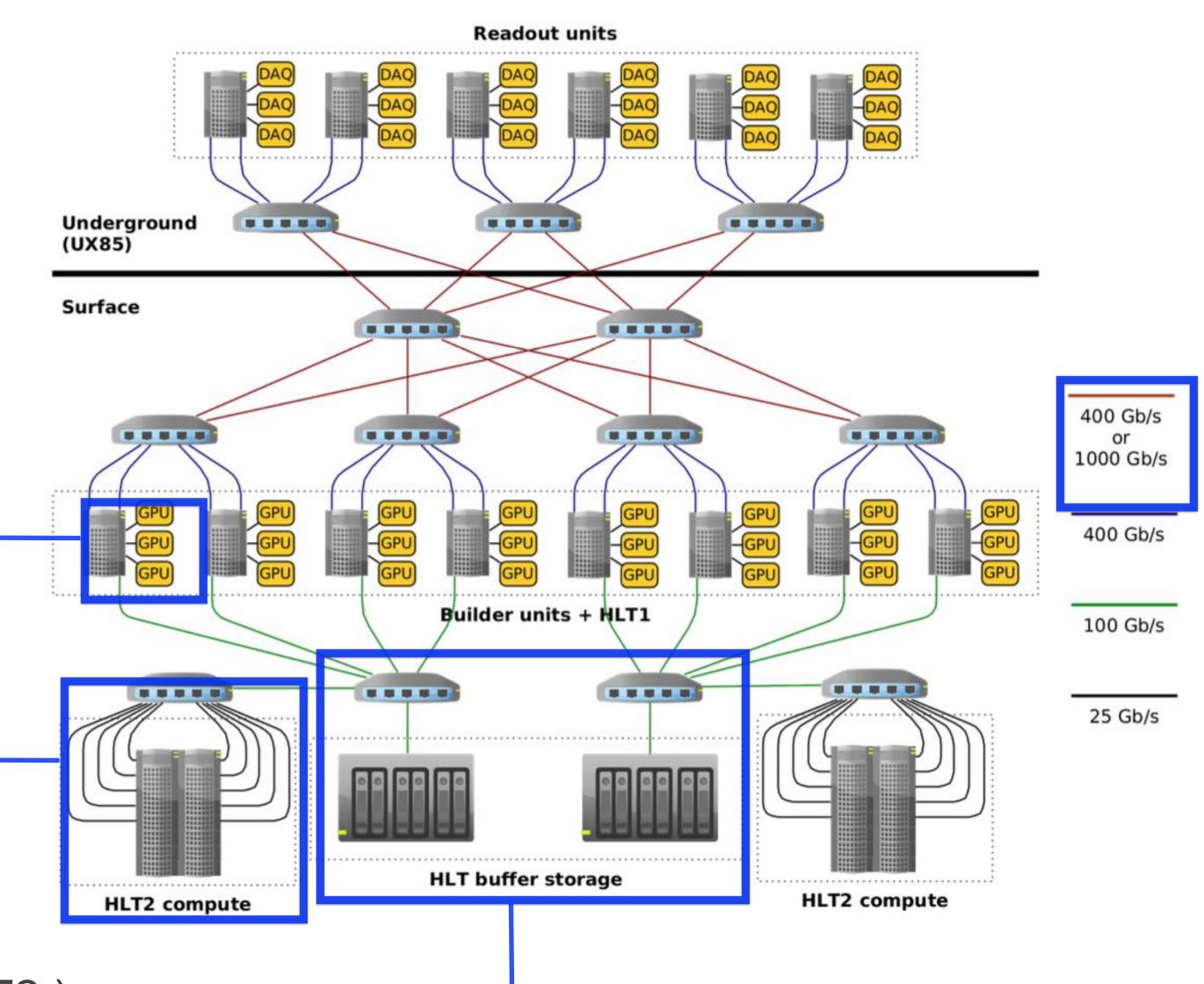

### Event-builder architecture

- 5 times capacity of the Run 3 DAQ

- Assume 480 readout-boards at full speed

Full detector reconstruction

Two reconstruction stages (HLT1 + HLT2 ) on GPUs (Baseline)

Disk buffer for alignment & calibration

## U2 trigger strategy

All numbers related to the dataflow are taken from the LHCb

Upgrade Trigger and Online TDR

Upgrade Computing Model TDR

#### Alignment

- Two reconstruction stages (HLT1 + HLT2) on GPUs (Baseline)

- Clustering & track primitives on FPGAs

- Selective persistency

## Summary

- LHCb successfully realised the pure software trigger paradigm in Run 3

- √ Hybrid architecture (GPU+ FPGA +CPU)

- √ Great performance achieved in 2024 data

- Baseline strategy with both HLT1 and HLT2 on GPU for U2

- Various ML / FPGA / IPU developments in progress