# Sensor Development for LHCb Upstream Pixel Tracker

Cheng Zeng 曾程 (Institute of High Energy Physics, CAS)

On behalf of COFFEE team

CMOS SENSUR IN

FIFTY-FIVE NM PROCESS

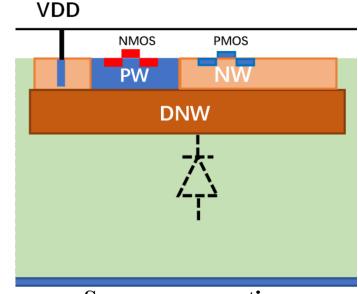

## **HVCMOS** for LHCb UP Tracker

• LHCb Upgrade II requires tracker with better radiation hardness and spatial resolution.

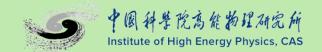

#### **Upstream Pixel Tracker for LHCb Upgrade II**

Area:  $\sim 8 \text{ m}^2$

Radiation hardness:  $\sim 3 \times 10^{15} \, n_{eq}/cm^2$

Time resolution: 3 - 5 ns, capability to tag 25 ns

bunch crossing

Power consumption:  $\sim 200 \text{ mW/cm}^2$

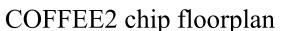

- HVCMOS advantages:

- MAPS, Excellent spatial resolution, no need to bump bond the sensor and ASIC

- Large deep n-well as charge collection node, high voltage bias; Fast charge collection, less trap effect

- Enclose readout circuit inside deep nwell. Intrinsically radiation hardness

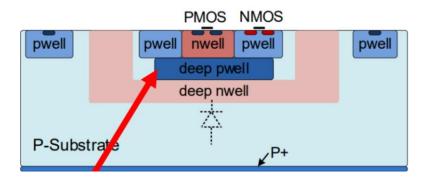

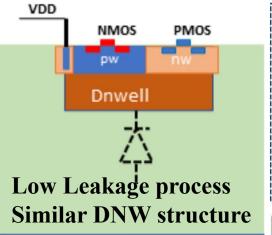

**Sensor cross section**

## COFFEE Chips

## CMOS sensOr in Fifty-FivE nanometer procEss chips

• Targeting to achieve full-size, full function chips meeting the LHCb UP

Tracker requirements in a few year.

- COFFEE1: Validate the 55 nm low leakage process

- COFFEE2: Explore and validate the 55 nm HV-CMOS process

- COFFEE3: Validate the readout circuit structures and core performances

CMOS SENSOR IN

FIFTY-FIVE NM PROCESS

COFFEE1 2023.4

COFFEE2 2024.1

COFFEE3 2025.6

Process modification 2025.11

Quarter chip 2026

Full matrix 2027

Fully functional design

## **COFFEE2** Introduction

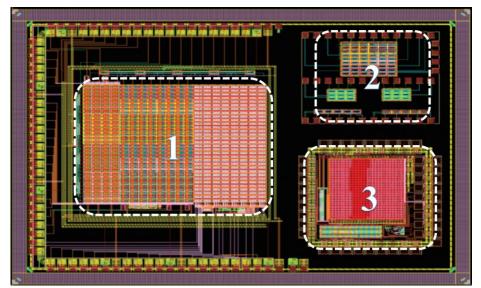

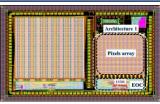

COFFE2 chip,  $3 \times 4 \text{ mm}^2$ , the first HVCMOS chip in 55 nm process, triple-well structure

Sensor cross section

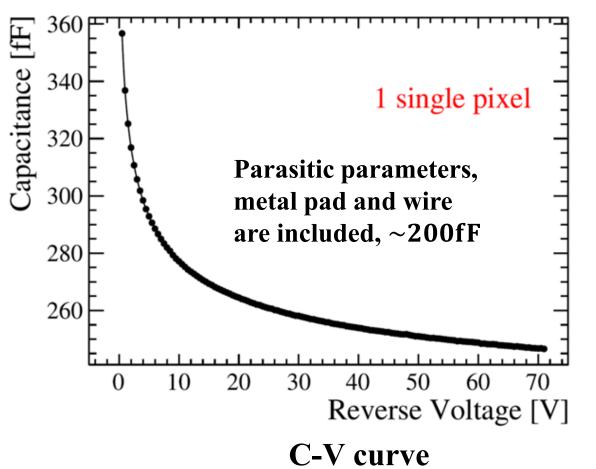

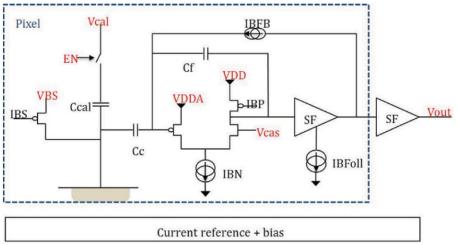

- Section 1: 32 rows × 20 columns pixels matrix, with sensor and in-pixel circuit. Studying for in-pixel charge sensitive amplifier (CSA), CMOS and NMOS comparator design for process validation. JINST 20 (2025) C10011

- Section 2: Passive diode, real validation of sensor.

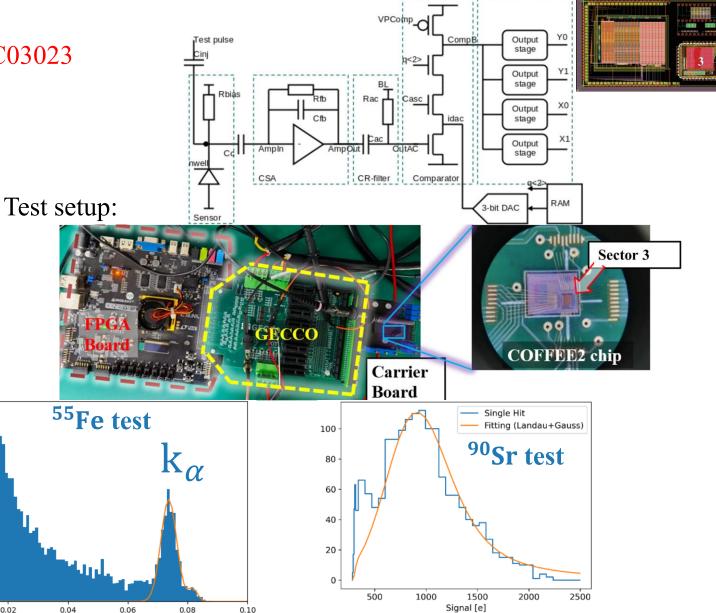

- Section 3: 26 rows × 26 columns pixels matrix, with sensor, in-pixel circuit and digital readout periphery for novel electronics structure study. JINST 20 (2025) C03023

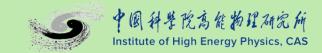

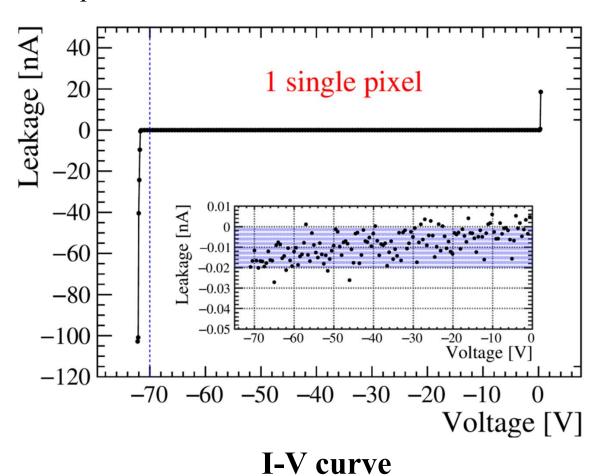

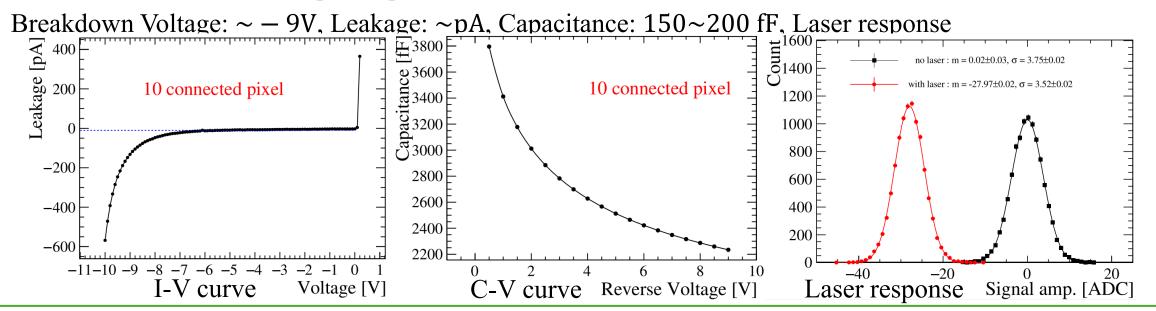

#### Section 2, Passive diode

- Breakdown Voltage:  $\sim -70 \text{ V}$

- Leakage: ~10 pA

- Capacitance:  $30\sim40$  fF at -70 V

#### **Section 1**

Injection

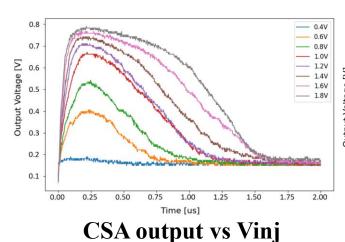

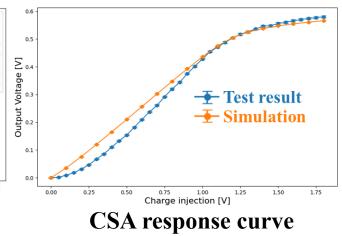

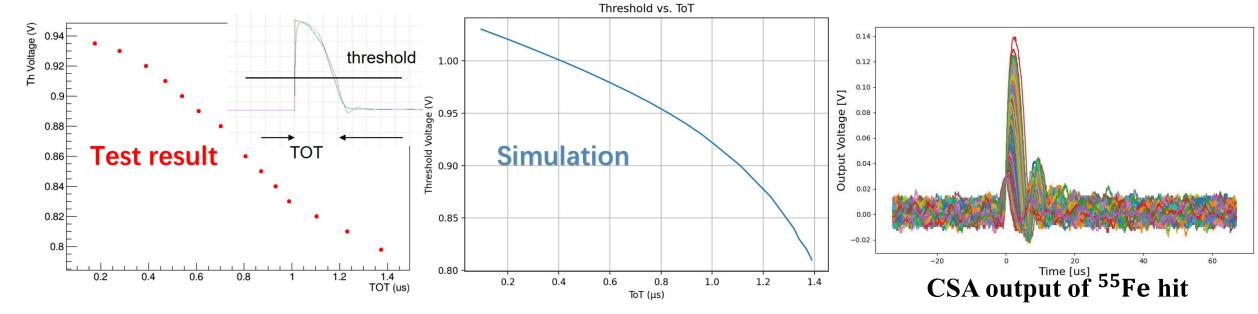

- Charge injection test: JINST 20 (2025) C10011

- CSA waveform in expected

- CSA response curve consistent with simulation

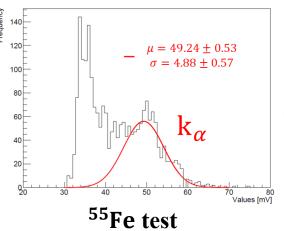

- Radioactive sources test:

- <sup>55</sup>Fe (5.9 keV X-ray), Gaussian fit

- μ~49 mV~1640 e<sup>-</sup>

- $\sigma \sim 4.9 \text{ mV} \sim 160 \text{ e}^-$

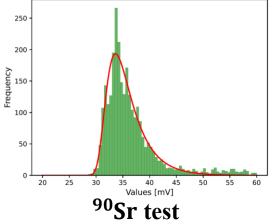

- <sup>90</sup>Sr (β-source), Landau fit

- MPV: ~34 mV~1120 e<sup>-</sup>

- Depletion depth: ~10 μm

#### **Section 1**

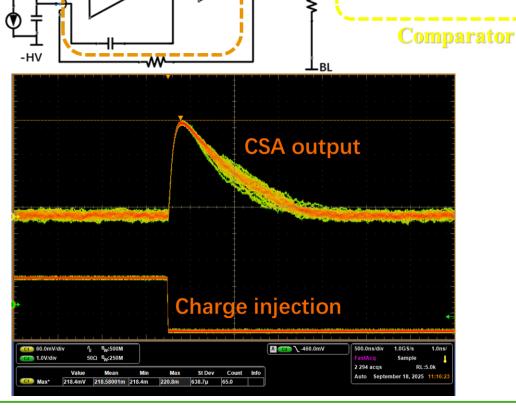

- Laser test: JINST 20 (2025) C10011

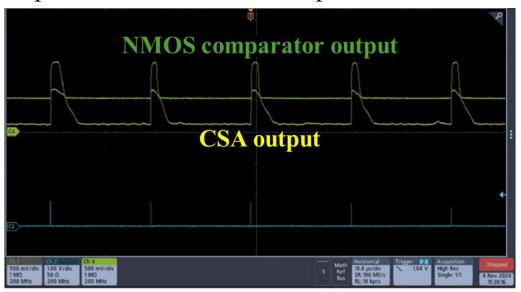

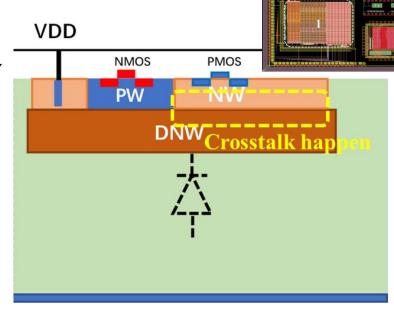

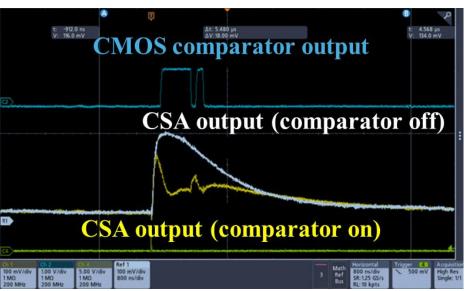

- Two different in-pixel comparator design: CMOS and NMOS-only

- Pixel with NMOS-only designed work well

- Crosstalk issue seen in CSA output waveform when CMOS comparator is on

- Potential flip in digital circuitry cause the disturbance between N-well of PMOS bulk terminal and deep N-well

- The crosstalk can be mitigated by adding a p-layer for isolation, process modification is required.

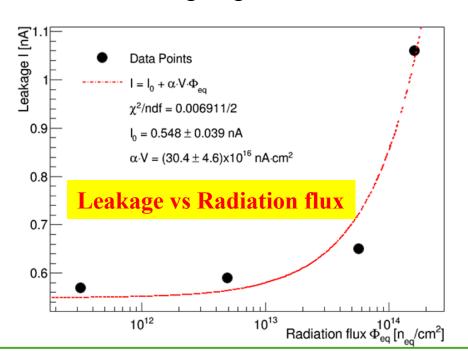

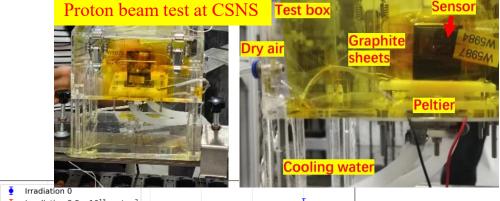

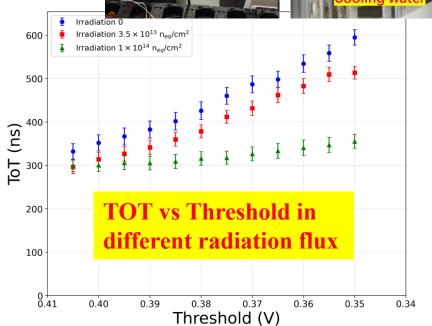

#### Radiation hardness test

- In LHCb UP Tracker, Radiation hardness target to  $\sim 3 \times 10^{15} \text{ n}_{eq}/\text{cm}^2$

- Proton irradiation at CSNS (China Spallation Neutron Source), up to  $1.3 \times 10^{15} \, n_{eq}/cm^2$

- After  $\sim 10^{14} \text{ n}_{eq}/\text{cm}^2$  radiation:

- Leakage 10 pA  $\rightarrow$  1 nA

- Capacitance and breakdown voltage remain unchanged

- In-pixel circuit still work

- More studies are still ongoing

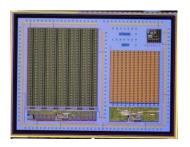

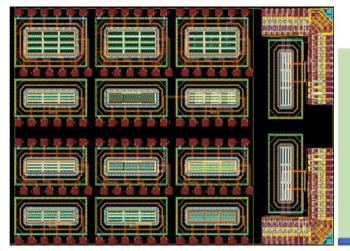

## COFFEE3 Introduction

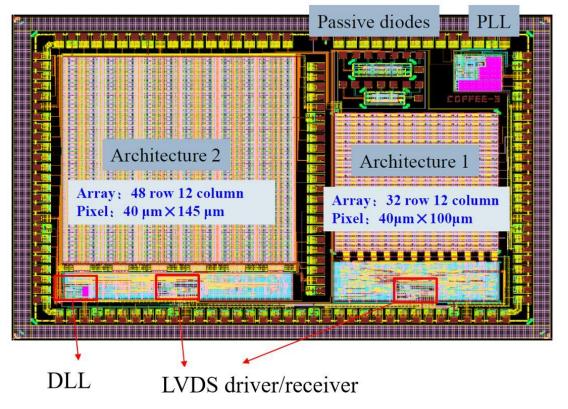

#### COFFEE3 chip, $3 \times 4 \text{ mm}^2$

- Passive diodes: same design as COFFEE2 chip, for further study of sensor and process

- Peripheral function modules: PLL, LVDS, DLL for IP accumulation and power consumption assessment

- Two pixel matrix readout architectures:

- 1. CSA + NMOS design in-pixel, less crosstalk between analog and digital circuits

- 2. CSA + CMOS design in-pixel, for future quadruple-well process. Advanced readout design, more suitable for high hit density situation

- Future quadruple-well process, add a deep p-well under n-well, reduce cross-talk between n-well and deep n-well

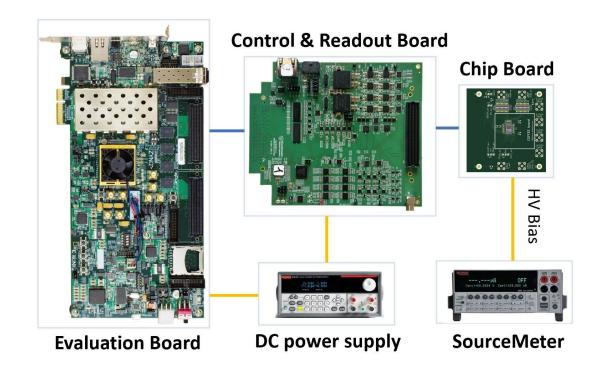

#### Pixels matrix array test system

- Test platform based on Caribou system: power, clock, DAQ, slow-ctrl, fast-readout, ...

- PC + ZC706/ZCU102 + Caribou board + chip carrier board

- FE chip specific carrier board, firmware IP, software by ourself

|                                   |                                              | DRD3 |

|-----------------------------------|----------------------------------------------|------|

| Feature                           | Description                                  | DIO  |

| Adjustable Power Supplies         | 8 units, 0.8 – 3.6 V, 3 A                    |      |

| Adjustable Voltage References     | 32 units, 0 – 4 V                            |      |

| Adjustable Current References     | 8 units, 0 – 1 mA                            |      |

| Voltage Inputs to Slow ADC        | 8 channels, 50 kSPS, 12-bit, 0 – 4 V         |      |

| Analog Inputs to Fast ADC         | 16 channels, 65 MSPS, 14-bit, 0 – 1 V        |      |

| Programmable Injection Pulsers    | 4 units                                      |      |

| Full-Duplex High-Speed GTx Links  | 8 links, <12 Gbps                            |      |

| LVDS Links                        | 17 bidirectional links                       |      |

| Input/Output Links                | 10 output links, 14 input links, 0.8 – 3.6 V |      |

| Programmable Clock Generator      | Included                                     |      |

| External TLU Clock Reference      | Included                                     |      |

| External High-Voltage (HV) Input  | Included                                     |      |

| FEAST Module Compatibility        | Supported                                    |      |

| FMC Interface to FPGA             | Included                                     |      |

| SEARAY Interface to Detector Chip | 320-pin connector                            |      |

Resources for various target applications

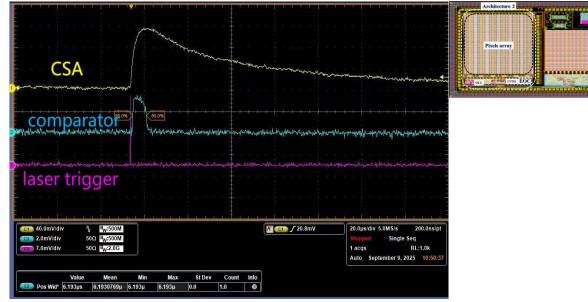

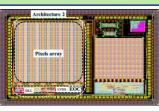

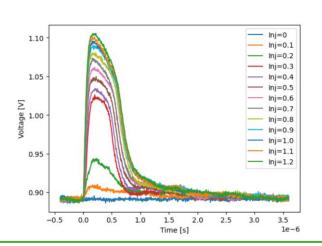

#### **Architecture 1 test**

Amp

In-pixel circuit working well with charge injection and laser

• Digital readout function validated

Radioactive source study ongoing

**CSA**

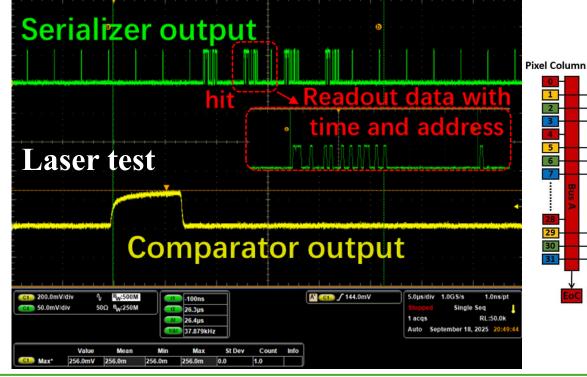

#### **Architecture 2 test**

- In-pixel CSA and comparator output for laser signal

- Typical time over threshold (TOT) of laser signal is consistent with simulation

- CSA response of <sup>55</sup>Fe signal can be seen, more study in near future

#### **Architecture 2 test**

- Full readout chain works well with laser test

- Only unmask pixel column 0, row 1

Sensor diode  $\rightarrow$  in-pixel (CSA, comparator, TDC)  $\rightarrow$  End of column readout circuit  $\rightarrow$  DAQ

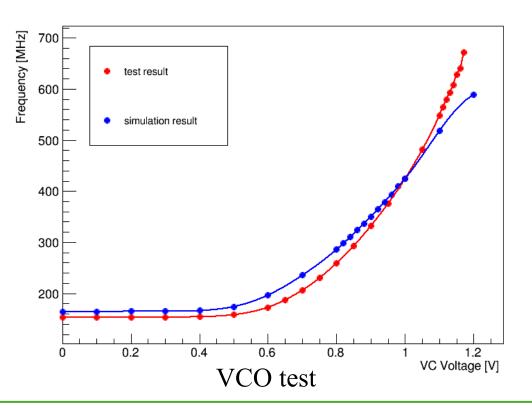

#### Phase locked loop (PLL) module

- Design for synchronizing the clock among chips and back-end DAQ

- Input CLK to generate internal clock to support TDC, high speed data transmission

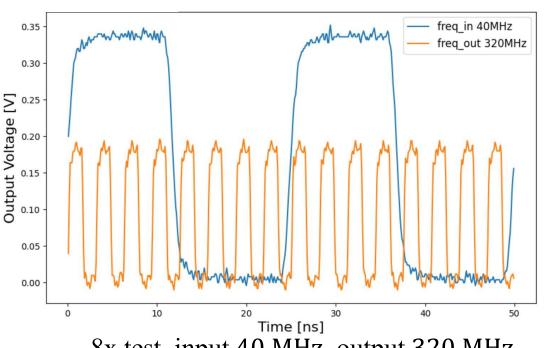

- Voltage-Controlled Oscillator (VCO) and frequency multiply functions (x4, 8, 16) work well within the range up to 640 MHz

- Working fine from the room temperature to -50 °C

8x test, input 40 MHz, output 320 MHz

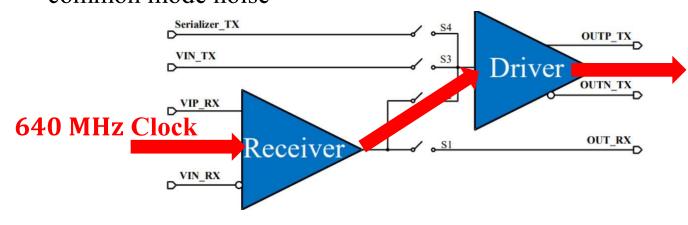

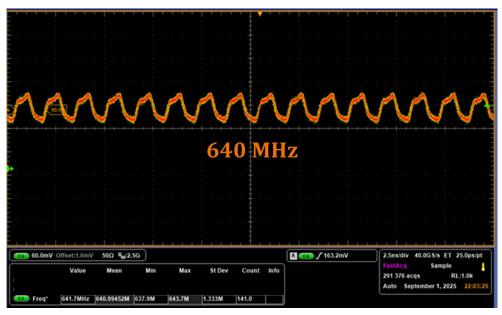

#### Peripheral circuit

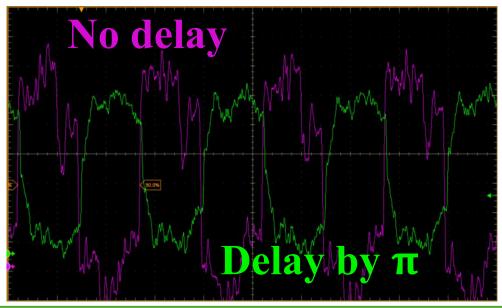

Data LVDS transceiver works up to 640 MHz supporting to 1.28 Gbps data transmission, to reduce common mode noise

- Delay Locked Loop (DLL) delivers clock phase delay as expected, to eliminate timing errors generated during the transmission of clock signals within the chip

- Following successful validation, these modules (PLL, LVDS, DLL) can be used in future large chips

- HVCMOS prototyping chip in 55 nm process for UP at LHCb Upgrade II

- Many encouraging results from COFFEE chip:

- Breakdown Voltage > 70 V, leakage ~10 pA

- Two full readout pixel matrixes work well

- Future plan:

- Full characterization of COFFEE3 chip:

- Spatial and timing resolution, power consumption, radiation hardness

- Seek process optimization for future chip design

# Thanks for your attention!

# Back up

## COFFEE1 Brief Result

COFFEE1 chip,  $3 \times 2 \text{ mm}^2$ , verify the feasibility of 55 nm process. NIMA 1069 (2024) 169905

Pixel area P-stop DNW gap

COFFEE1 chip floorplan

Sensor cross section Schematic design of COFFEE1 in-pixel circuit

#### **Section 3**

- Charge injection test: JINST 20 (2025) C03023

- CSA waveform in expected

- Radioactive sources test:

- <sup>55</sup>Fe (5.9 keV X-ray), Gaussian fit

- $\mu \sim 73 \text{ mV} \sim 1640 \text{ e}^-$

- $\sigma \sim 2.6 \text{ mV} \sim 58 \text{ e}^-$

- $^{90}$ Sr ( $\beta$ -source), Landau fit

- MPV: ~50 mV~1100 e<sup>-</sup>

- Depletion depth:  $\sim 10 \, \mu \text{m}$

350

300

250 200 150

100