## Draft v0.4.1 CEPC Reference Detector Technical Design Report

Version: v0.4.1 build: 2025-06-14 14:07:25+08:00

## Draft v0.4.1

### **Chapter 4** Vertex Detector

The CEPC vertex detector is a crucial component of the tracking system, designed to provide excellent spatial resolution and ultra-low material budget for precision vertexing and flavor tagging.

A high-granularity low-mass design based on Monolithic Active Pixel Sensor (MAPS) has been proposed and selected as the CEPC vertex detector baseline, in order to achieve an excellent impact parameter resolution while maintaining low power consumption and air cooling compatibility. The MAPS technology allows for sub-5  $\mu$ m spatial resolution and minimal dead zones, with a target material budget of less than 0.15% radiation length (*X*<sub>0</sub>) per layer, ensuring high tracking performance without compromising the calorimeter and timing detector coverage.

The CEPC vertex detector consists of several concentric cylindrical layers surrounding the interaction point and is finely segmented in both the longitudinal and transverse directions. This layout is optimized to provide full solid angle coverage and to ensure efficient reconstruction of secondary and tertiary vertices.

This chapter is organised in the following structure: the overall design considerations 2451 are outlined in Sec. 4.1, followed by the design on detector layout along with estimates 2452 of the background rate and radiation dose in this layout. Detailed sensor and readout 2453 technologies are presented in Sec. 4.2, Mechanics and cooling design as well as service 2454 design are presented in Sec. 4.3. R&D of key technology are presented in Sec. 4.5 to 2455 support the baseline design of the CEPC vertex detector. The detailed simulation of 2456 expected detector performance and detector alignment strategy are presented in Sec. 4.6. 2457 Finally, The summary and future plan are presented in Sec. 4.7. 2458

### 2459 4.1 Detector overall design

#### **4.1.1 Vertex detector design specification**

The CEPC is designed to operate at higher collision frequencies, accommodating 2461 multiple collision modes. In its initial 10 years, the plan includes running at 240 GeV in 2462 the Higgs boson factory mode and at 90 GeV in the Z boson factory mode. Specifically, 2463 the collision frequency for the Higgs factory is approximately 1.7 MHz, while the Zboson 2464 factory mode operates at about 14.5 MHz during the initial low-luminosity phase and 2465 increases to 43 MHz in the later high-luminosity phase. These frequencies significantly 2466 exceed the 100 kHz collision frequency of the A Large Ion Collider Experiment (ALICE) 2467 experiment, posing challenges in maintaining low power consumption at higher operational 2468 frequencies - a critical aspect of the vertex detector chip development for this project. To 2469

2436

### Draft v041 4.1 Detector overall design

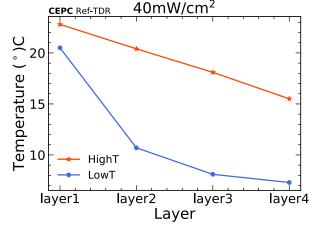

balance power efficiency and timing performance, the CEPC vertex detector is designed with a power consumption limit of below 40 mW  $\cdot$  cm<sup>-2</sup> while maintaining a time stamp precision within 100 ns for recorded hits.

Additionally, the CEPC requires the vertex detector to achieve higher spatial resolution, targeting levels between 3 to 5  $\mu$ m, and to maintain a low material budget of less than 0.15%  $X_0$  per layer. This capability is essential for studying the properties of the Higgs particle, particularly its decay channels involving bottom and charm quarks, and for exploring potential new physics phenomena. The performance of the vertex detector directly impacts the physics objectives of the CEPC.

To meet the requirements mentioned above, the vertex detector has selected 65 nm 2479 technology as the baseline for chip development. Preliminary simulations and tests based 2480 on the first CEPC vertex detector prototype indicate that the power consumption at low-2481 luminosity Zmode operation for the 180 nm technology is larger than 60 mW/cm<sup>2</sup>. This 2482 level of power dissipation exceeds the air cooling capacity of the vertex detector, resulting 2483 in sensor temperatures surpassing the operational upper limit of 30 °C. To address this 2484 critical issue, the vertex detector has adopted 65 nm technology as the baseline technology. 2485 This choice significantly reduces power consumption and also offers the potential for 2486 smaller pixel sizes, thereby enhancing spatial resolution. 2487

During extended runs at the Z-pole, the vertex detector will be subjected to significant radiation exposure and intense beam-related backgrounds, requiring sensor technologies with high radiation tolerance, low noise, fast timing, and reliable long-term stability. Additionally, the readout electronics must handle high occupancy and deliver data at rates sufficient to cope with the demanding trigger and data acquisition requirements, all while operating under stringent power and cooling constraints to maintain mechanical stability and minimize distortions. In summary, the key requirements are listed in Table 4.1:

| Parameter                    | <b>Baseline Requirement / Design</b>                             |

|------------------------------|------------------------------------------------------------------|

| <b>Operation Period</b>      | First 10 years (Higgs factory + low-luminosity Zrun)             |

| Number of Barrel Layers      | 6 layers                                                         |

| Layer Radii                  | ~11–40 mm                                                        |

| Material Budget per Layer    | $\leq 0.15\% X_0$                                                |

| Fluence                      | $\sim 2 \times 10^{14}$ Neq/cm <sup>2</sup> (for first 10 years) |

| <b>Operation Temperature</b> | $\sim 5^{\circ}$ C to $30^{\circ}$ C                             |

| Readout Electronics          | Fast, low-noise, low-power                                       |

| Mechanical Support           | Ultralight structures to minimize mass                           |

| Replacement Strategy         | Replacement/upgrade after ~10 years                              |

| Spatial Resolution           | ~3–5 µm                                                          |

| Power Consumption            | $< 40 \text{mW/cm}^2$ (air cooling requirement)                  |

| Time stamp precision         | ± 100 ns                                                         |

| Table 4.1: Baseline Requirements and Ove | erall Vertex Detector Design Parameters |

|------------------------------------------|-----------------------------------------|

|------------------------------------------|-----------------------------------------|

4.1 Detector overall design

#### 2495 **4.1.2 Detector layout**

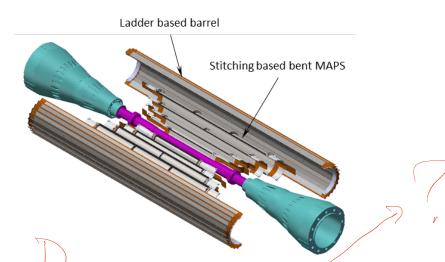

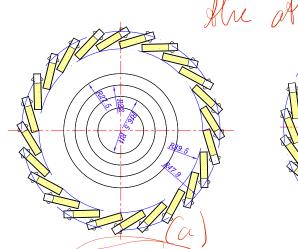

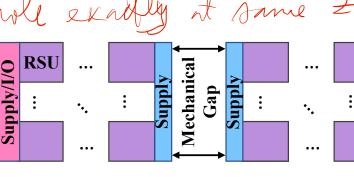

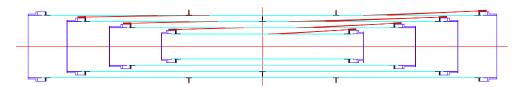

In the baseline layout, shown as Figure 4.1, the first four layers utilize stitching 2496 technology, with each layer composed of two semicircular structures spliced together. 2497 This technology employs wafer stitching techniques to fabricate large-area sensors that 2498 can be integrated directly into a curved geometry. By reducing or eliminating the need for 2499 multiple planar tiles and mechanical support frames, curved sensors significantly lower the 2500 overall material budget. There is a mechanical gap between the two semicircular structures 2501 ranging from 0.2 to 0.5 mm, as shown in Table 4.2. The semicircular structure achieved 2502 through stitching technology requires the entire chip to be bent along the phi direction as 2503 a half arc corresponding to each radius. The position of different layers determines the arc 2504 length of the semicircle, which defines the width of the whole chip. Additionally, to satisfy 2505 the covering pole angle of 8.1°, the length of the whole chip is also determined. Due to 2506 wafer size limitations, stitching technology cannot be effectively applied to the large-area 2507 outer layers. Therefore, we employ conventional double-layer planar CMOS sensors with 250 a ladder design for the 5th and 6th layers as Figure 4.2a shows. With the outter radius 2509 of the beam pipe in the CEPC-TDR set at 10.7 mm, the radius of the innermost layer in 2510 the vertex detector baseline is designed to be 1.06 mm based on the chip design of the 2511 stitching scheme. 2512

A backup detector layout using 3 layers of double-sided ladders with planar CMOS sensors are also considered as Figure 4.2b shows. The backup layout represents a well established, more conventional option. It serves as alternative tallback solution if the baseline layout with curved technology encounters unforeseen challenges. However, it introduces additional material and complexity due to the need for mechanical support, overlaps between ladders, and potentially thicker support elements.

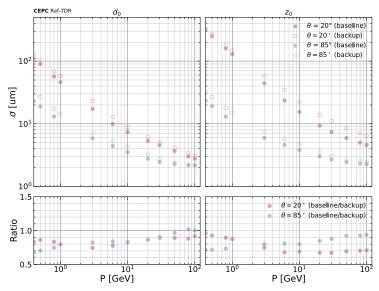

Detailed parameters for baseline vertex detector layout and backup detector layout are provided in Table 4.2. The intrinsic single-point resolution of the chip is derived from the TaichuPix-3 beam current experiments, with a conservative resolution/of 5 µm.

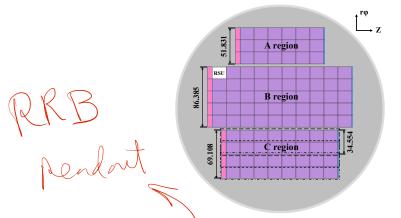

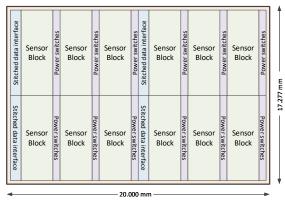

**Stitching plan in baseline layout** On a 300 mm wafer, the stitching plan is designed 2522 to meet the layout requirements of the four stitching layers in the baseline scheme. To 533 enhance the design reticle utilization and streamline the process flow, the same chip is used 2524 to fulfill the baseline scheme requirements, and the same mask plate is employed. Due to 2525 the required arc length and the integer number of instances needed per layer, an instance 2526 with a dimensions of  $17.277 \times 20.000 \text{ mm}^2$  is used as the Repeated Sensor Unit (RSU)s 2527 (see Section 4.2.2). Three layouts are designed on a wafer, with the A/B/C regions of 2528 different lengths designed based on the required z-axis length. The preliminary stitching 2529 plan of the silicon wafer and the dimensions of each half layer are depicted in Figure 4.3. 2530 Each region is composed of repeated sensor units with different rows and columns, and 2531

10 4.2 -77 detail

### Draft v0 4 1 4.1 Detector overall design

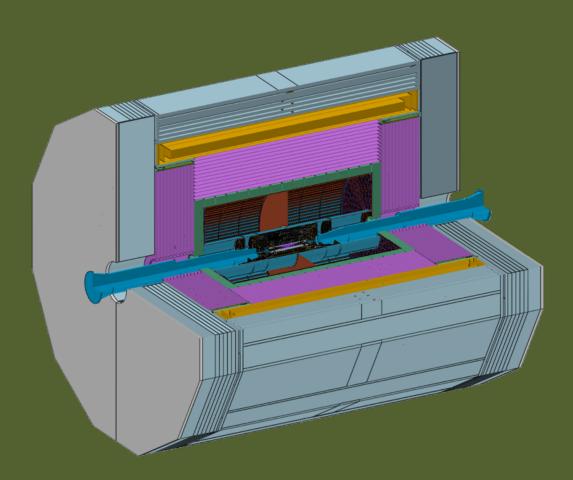

**Figure 4.1:** Baseline design diagram of the vertex detector. The first four layers are *cms* designed as single-layer structures (full-model cylindrical structure) using 65 nm Cmos Image Sensor (CIS) stitched sensors, while the last two layers are designed as double-layer structures (ladder structure) utilizing full size 65 nm CIS sensors.

IN.D

(a) Sectional view of the VTX baseline layout.

(b) Sectional view of the VTX backup (ayout.

l

**Figure 4.2:** Sectional view of baseline and backup layout. (a) The inner four layers are bent MAPS with semicircular structure and for the 5th and 6th layers are double-layer planar CMOS sensors with ladder desgin. (b) All the 6 layers (3 layers of double sided ladders) are composed of planar CMOS sensors.

chip peripheral circuits and I/O pads at the left and right edges.

BVTX 1 and BVTX 3 share the C region, with BVTX 1 containing the two C region  $\mathcal{M}$ of the two modules. BVTX 2 utilizes the A region chip, consisting of two A region  $\mathcal{J}$ modules arranged along the *z*-direction and two A region 3 modules arranged along  $\phi$ -direction. BVTX 3 employs the C region chip, consisting of two C region 4 modules arranged along the *z*-direction and two C region 4 modules arranged along the  $\phi$ -direction. BVTX 4 adopts the B region chip, consisting of two B region 5 modules arranged along

is needs some bot of dickam the modules connected to each

4.1 Detector overall design

Palind

a

**Table 4.2:** Geometric configuration parameters. Bent Vertex Layer (BVTX) is used to denote the layer of VTX employing a curved stitching CMOS sensor, while Planar Vertex Layer (PVTX) is used to denote the layer of VTX employing a planar CMOS sensor. The effective thickness of the support structure in each layer in baseline layout and backup layout are also listed.

IN

| Layout   | BVTX/<br>PVTX X | radius<br>mm | length<br>mm | arc length<br>mm | height<br>mm | <b>support thickness</b><br>μm |

|----------|-----------------|--------------|--------------|------------------|--------------|--------------------------------|

|          | BVTX 1          | 11.1         | 161.4        | 69.1             | -            | 45                             |

|          | BVTX 2          | 16.6         | 242.2        | 103.7            | -            | 32                             |

| Baseline | BVTX 3          | 22.1         | 323.0        | 138.2            | -            | 31                             |

|          | BVTX 4          | 27.6         | 403.8        | 172.8            | -            | 29                             |

|          | <b>PVTX 5-6</b> | 39.5         | 682.0        | -                | 3.3          | 300                            |

|          | PVTX 1-2        | 12.5         | 260.0        |                  | 1.7          | 300                            |

| Backup   | <b>PVTX 3-4</b> | 27.9         | 494.0        |                  | 2.6          | 300                            |

| ~        | PVTX 5-6        | 43.8         | 749.0        | -                | 3.3          | 300                            |

**Figure 4.3:** The arrangement of stitching frames on a 300 mm wafer. The purple part represents the RSUs, the pink represents the Left-End Block (LEB) (Left-End Block), and the blue represents the Right-End Block (REB) (Right-end Block). To meet the requirements of each layer of the vertex detector, the A/B/C regions are designed with different lengths and widths. The A and B regions are used to make one of the sensors for BVTX 2 and BVTX 4, respectively. The full C region can be used for one of the sensors for BVTX 3. The C region can be divided into four modules along the vertical direction. Using two modules of the C region can make a sensor for BVTX 1. The three possible groupings of two modules are indicated by long-dashed lines, short-dashed lines, and dash-dot lines, respectively.

the trestons don't make nenstras)

L KB Deadout

# Draft v0.4.1 Detector overall design

~ An

the *z*-direction and two B region 5 modules arranged along the  $\phi$ -direction. BVTXs 2, 3, and 4 are spliced in the *z*-direction, resulting in a 0.5 mm splicing seam at z = 0, also referred to as a mechanical gap, as shown in Figure 4.4.

Figure 4.4: Schematic diagram of layer 2/3/4 assembly (not to scale).

<sup>2542</sup> Considering the mechanical dead zones in the  $\phi$  direction and the dead zones in the <sup>2543</sup> width of the whole chip, the BVTX 1, BVTX 2, BVTX 3, and BVTX 4 of the vertex detector are rotated by an angle when mounted. This angular adjustment minimizes the <sup>2545</sup> occurrence of multiple dead zones at the same angle in the  $r\phi$  plane. Each semicircular structure is supported by a Carbon Fiber Reinforced Polymer (CFRP) (Carbon Fibre-M2547 Reinforced Polymer) material with a specific thickness (see Section 4.3.1.3). The amount <sup>2548</sup> of the vertex detector material per layer is detailed in Table 4.3.

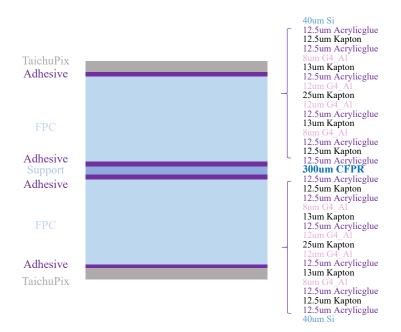

Double-sided Ladders in baseline layout The fifth and sixth layers are constructed 2549 using Taichu chips, each sized  $15.9 \times 25.7 \text{ mm}^2$  with a thickness of 40  $\mu$ m. The back of 2550 the chip is affixed to the flex that transmits the signal using glue. The chip is treated as 2551 a unit, and the dead zones of the adhesive are arranged from the -z/2 region to the z/22552 region at intervals of 0.1 mm. The flex is glued to both sides of the support structure CFRP 2553 to create a complete ladder cell as shown in Figure 4.6, where the effective thickness of 2554 the support structure CFRP hollow pipe is 300  $\mu$ m, as described in the Section 4.3.1. The 2555 geometric center of the ladder unit rotates around the origin at a specific radius position 2556 from the  $\phi = 0$  position, while maintaining the height of the wire, forming a barrel structure 2557 known as PVTX 5-6 to ensure that no particles leak out in the  $\phi$  direction. A total of 24 2558 ladder structures are utilized in the fifth and sixth layers. 2559

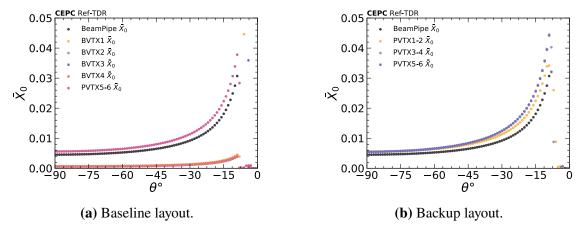

Material budget for baseline and backup layout The backup layout replaces the first four layers of the stitching chip in the baseline layout with a structure similar to the PVTX 5-6. To optimize the material budget and accommodate the readout electronics, each ladder of PVTX 1-2, PVTX 3-4 and PVTX 5-6 consists of eight layers of aluminum, forming a symmetric ladder structure as shown in Figure 4.6. Additionally, the innermost layer of PVTX 1-2 has a radius of 12 mm, which differs from BVTX 1. Figure 4.5 shows

the variation of the average material budget  $X_0$  with  $\theta$  in the  $\phi$  direction. Table 4.3 lists the material budget of each layer for the two configurations.

**Figure 4.5:** The average value  $\bar{X}_0$  within the range of  $\phi \in (0, 360)^\circ$  of two configurations, the baseline layout 4.5a and the backup layout 4.5b, varies with  $\theta$ .

**Figure 4.6:** Longitudinal cross-section of a ladder in the backup layout, composed of two layers of chips and other materials, such as glue, carbon fiber, and aluminum. Each ladder of PVTX 1-2, PVTX 3-4 and PVTX 5-6 in the backup layout, as well as PVTX 5-6 in the baseline layout, utilizes this structure.

**Table 4.3:** The material budget parameters of the baseline layout and backup layout.

| Layout   | Beampipe | layer 1 | layer 2 | layer 3 | layer 4 | layer 5 | layer 6 |

|----------|----------|---------|---------|---------|---------|---------|---------|

| Baseline | 0.454%   | 0.067%  | 0.059%  | 0.058%  | 0.061%  | 0.280%  | 0.280%  |

| Backup   | 0.454%   | 0.276%  | 0.276%  | 0.276%  | 0.276%  | 0.287%  | 0.287%  |

### Draft v0 4 1 4.1 Detector overall design

### **4.1.3 Background estimation**

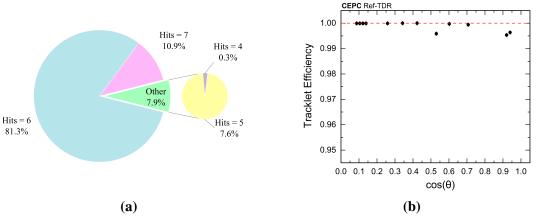

As a kind of important information, the hit rate significantly affects the design specifications of the sensor. The details of each component's contribution to the VTX will be discussed in the Chapter 3 . In this subsection, we will only present the total hit rate, data rate, occupancy, and other relevant information for each mode.

Before we talk about these information, the definition of them should be declared. 2573 When a particle passes through a chip, several pixels on that chip may generate signals due 2574 to a series of physical effects. The collection of signals produced by the same particle on 2575 the same chip is referred to as a hit, and the number of pixels contained in this collection 2576 is known as the cluster size. The number of hits per unit time is termed the hit rate. For 2577 a given time window, the ratio of the number of active subunits within a cell to the total 2578 number of subunits in that cell is referred to as the occupancy of the cell during that time 2579 window. For example, when the cell is defined as a specific chip, the numerator is the total 2580 number of active pixels within that chip. When the cell is defined as a specific layer, the 2581 numerator is the total number of active chips within that layer. 2582

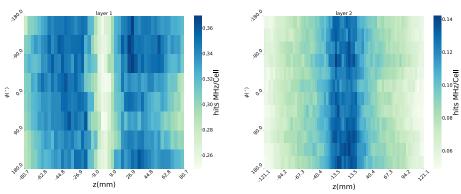

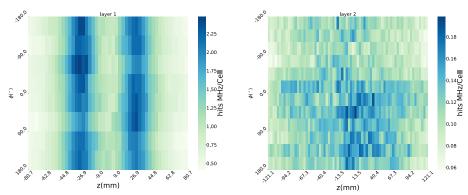

In order to calculate the data rate, information about the cluster size is essential. To compute the data rate more accurately, we did not set the cluster size as a fixed value; instead, we referenced the results from the TaichuPix-3 beam test and calculated the cluster size based on the particle's incidence angle. The background hit rate and data rate are shown as Table 4.4, and the hit rate distributions of Higgs as well as Zmode are shown as Figure 4.7 and Figure 4.8.

**Figure 4.7:** Hit rate distribution of Higgs mode. The shape of VTX is approximately cylindrical, where the x-axis can be equivalently regarded as the z-axis of the global coordinate, and the y-axis can be equivalently regarded as the polar angle  $\phi$  of the global coordinate. Synchrotron radiation is not included.

For the VTX, the primary sources of beam background are synchrotron radiation and pair production. However, due to the excessive computational resources required for simulating and analyzing synchrotron radiation, we did not perform simulations and analyses with the same event statistics and granularity as those for other beam backgrounds.

# Draft v0.4.1 Detector overall design

**Figure 4.8:** Hit rate distribution of Z mode. For we could not completely handle highlumi Z mode now, as well as the major difference between high-lumi Z with Z mode is luminosity which means their hit rate distribution is similar, the hit rate distribution of high-lumi Z would not be shown here. Synchrotron radiation is not included.

**Table 4.4:** Summary of background estimation. Current detector scheme cannot completely handle high-lumi Z mode, so the result of high-lumi Z will not be shown here. For the results of high-lumi Z, based on accelerator parameters, a rough estimation can be made by simply multiplying the existing Z mode results by a factor of 3. Synchrotron radiation is included.

| Layer  | Ave.<br>Hit Rate<br>MHz/cm <sup>2</sup> | Max.<br>Hit Rate<br>MHz/cm <sup>2</sup> | Ave.<br>Hit Rate×C<br>MHz/cm <sup>2</sup> | Max.<br>Hit Rate×C<br>MHz/cm <sup>2</sup> | Ave.<br>Data Rate<br>Mbps/cm <sup>2</sup> | Max.<br>Data Rate<br>Mbps/cm <sup>2</sup> |

|--------|-----------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| Higgs: | DataRate = Hitk                         | Rate ×32 bit / pixe                     | l × ClusterSize @(                        | Bunch Spacing:                            | 346ns, 53 %Gap, 2                         | $25 \times 25 \ \mu m^2 / \text{ pixel})$ |

| 1      | 2.45                                    | 2.79                                    | 8.17                                      | 10.48                                     | 261.29                                    | 335.36                                    |

| 2      | 0.67                                    | 1.07                                    | 2.18                                      | 3.48                                      | 69.59                                     | 111.41                                    |

| 3      | 0.17                                    | 0.35                                    | 0.62                                      | 1.19                                      | 19.68                                     | 38.21                                     |

| 4      | 0.08                                    | 0.18                                    | 0.32                                      | 0.98                                      | 10.25                                     | 31.39                                     |

| 5      | 0.03                                    | 0.15                                    | 0.11                                      | 0.74                                      | 3.41                                      | 23.73                                     |

| 6      | 0.02                                    | 0.09                                    | 0.07                                      | 0.41                                      | 2.37                                      | 13.24                                     |

| Zmod   | e: DataRate = Hi                        | tRate ×32 bit / pi                      | el × ClusterSize (                        | @(Bunch Spacing                           | : 69ns, 9 %Gap, 2                         | $5 \times 25 \ \mu m^2 / \text{ pixel}$   |

| 1      | 9.35                                    | 18.68                                   | 42.45                                     | 88.23                                     | 1358.33                                   | 2823.36                                   |

| 2      | 0.89                                    | 1.47                                    | 3.73                                      | 7.54                                      | 119.24                                    | 241.36                                    |

| 3      | 0.31                                    | 0.75                                    | 1.45                                      | 5.99                                      | 46.49                                     | 191.75                                    |

| 4      | 0.19                                    | 0.47                                    | 0.95                                      | 4.86                                      | 30.50                                     | 155.50                                    |

| 5      | 0.05                                    | 0.10                                    | 0.20                                      | 0.45                                      | 6.40                                      | 14.38                                     |

| 6      | 0.04                                    | 0.07                                    | 0.15                                      | 0.38                                      | 4.80                                      | 12.17                                     |

Based on simulation results of approximately  $1 \times 10^9$  synchrotron photons, we estimate that the beam background contribution from synchrotron radiation is comparable to that from pair production. Therefore, when presenting Table 4.4, to incorporate the synchrotron radiation results, we multiplied the pair production contribution by a factor of 2. However, it should be noted that the actual maximum value will be lower than simply doubling the pair production results.

We used a bunch crossing as a time window to calculate the occupancy of different modes at various levels, and the results are as Table 4.5.

### Draft v04 4.2 Sensors and electronics design

**Table 4.5:** Occupancy estimation. †: Considering that the only difference between the two modes in the current simulation lies in the bunch settings, the occupancy in both modes should be similar. Therefore, they are combined and presented as Zmode. Synchrotron radiation is not included.

| Layer | Mode   | Ave. Occupancy@Pixel<br>(×10 <sup>-5</sup> / BX) | Max. Occupancy@Pixel<br>(×10 <sup>-5</sup> / BX) |

|-------|--------|--------------------------------------------------|--------------------------------------------------|

| 1     |        | 1.818                                            | 2.331                                            |

| 2     |        | 0.484                                            | 0.778                                            |

| 3     |        | 0.137                                            | 0.265                                            |

| 4     | Higgs  | 0.071                                            | 0.219                                            |

| 5     |        | 0.024                                            | 0.170                                            |

| 6     |        | 0.017                                            | 0.095                                            |

| 1     |        | 0.972                                            | 2.026                                            |

| 2     |        | 0.085                                            | 0.168                                            |

| 3     | 7 Mada | 0.033                                            | 0.124                                            |

| 4     | Z Mode | 0.022                                            | 0.108                                            |

| 5     |        | 0.005                                            | 0.011                                            |

| 6     |        | 0.004                                            | 0.009                                            |

Considering all beam background effects, the maximum achievable data rates are 335 Mbps/cm<sup>2</sup> in Higgs mode and 2823 Mbps/cm<sup>2</sup> in Zmode, with corresponding average rates of 261 Mbps/cm<sup>2</sup> and 1358 Mbps/cm<sup>2</sup> respectively. The system demonstrates excellent compatibility with the current vertex detector design, particularly given the low occupancy of  $2.331 \times 10^{-5}$ /BX in Higgs mode and  $2.026 \times 10^{-5}$ /BX in Zmode. These favorable occupancy levels ensure efficient data handling within the existing scheme.

### **4.2** Sensors and electronics design

#### **4.2.1 Sensor technology overview**

The current design and development of the CEPC vertex detector are centered on utilizing state-of-the-art MAPS technology for chip design and manufacturing. This technology integrates the sensor and readout electronics onto a single chip, significantly reducing both pixel size and power consumption while delivering high-performance detection capabilities. Such features meet the stringent requirements for high resolution, low material budget, and rapid readout speeds.

The Solenoidal Tracker at RHIC (STAR) experiment at Relativistic Heavy Ion Collider (RHIC) (Relativistic Heavy Ion Collider) successfully employs MAPS technology in its vertex detector [1], and the STAR MAPS vertex detector features excellent spatial resolution [1, 2]. The Inner Tracker System (ITS)2 of CERN's ALICE experiment is the largest scale MAPS system among high energy physics experiments [3]. ITS2 is a full-pixel silicon detector based on TowerJazz 180 nm technology. It boasts exceptional technical parameters, including approximately 5 μm high resolution, an extremely low

### Draft VQ4 4.2 Sensors and electronics design

material budget of less than 0.3 %  $X_0$  per layer, stable readout support for collision fre-2622 quencies up to 100 kHz, and power consumption as low as 40 mW·cm<sup>-2</sup> [3, 4]. The 2623 upcoming ITS3 upgrade for the ALICE experiment introduces the concept of "curved 2624 wafer-level chips", aiming to achieve a self-supporting wafer structure [5, 6]. This de-2625 velopment is based on TowerJazz Tower Partners Semiconductor Co. (TPSCo) 65 nm 2626 technology. This innovation could potentially reduce the material budget of the vertex 2627 detector by a factor of 3 to 5. The ITS3 project is currently in the research and development 2628 phase. The comparison of key parameters between different vertex detectors mentioned 2629 above is shown as Teble 4.6. 2630

**Table 4.6:** Comparison of sensor technology in vertex detectors of different experiments: ALICE ITS2, ALICE ITS3, the first CEPC vertex detector prototype, and final CEPC vertex detector.

| Detector                        | Technology Node | Power Consumption               | <b>Readout Speed</b> | Spatial Resolution |

|---------------------------------|-----------------|---------------------------------|----------------------|--------------------|

| ALICE ITS2 [3, 4]               | 180 nm          | $40 \text{mW}/\text{cm}^2$      | Up to 100 kHz        | 5 µm               |

| ALICE ITS3 [5]                  | 65 nm           | $40 \text{mW}/\text{cm}^2$      | 164 kHz              | 5 µm               |

| 1st CEPC Vertex prototype [7–9] | 180 nm          | $80 \sim 100 \text{mW/cm}^2$    | 40 MHz               | 5 µm               |

| Final CEPC Vertex Detector      | 65 nm           | $\leq 40 \text{mW}/\text{cm}^2$ | Up to 43 MHz         | 3-5 µm             |

#### **4.2.2 Stitched sensor prototype design**

The stitching technology enables the production of chips significantly larger than the 2632 dimensions of the design reticle. The design reticle is divided into sub-frames that align 2633 with the sub-frames of the photomasks. By selectively exposing these reticle sub-frames 2634 onto adjacent locations following the designed pattern, manufacturers can create large 2635 chips with dimensions nearing the wafer's diameter. This innovative approach expands 2636 the possibilities for chip design and production, allowing for more efficient utilization 2637 of wafer space. This technology is particularly advantageous for pixel sensor chips that 2638 feature a high number of repeated units (pixel matrices) and demand a large active area. 2639 Taking into account the difficulty and yield of stitching technology, the baseline design 2640 of the stitched sensor prototype involves using 1D stitching to achieve stitched-chip along 2641 the beam pipe direction. The feasibility of 2D stitching will also be continuously explored 2642 during research and development. 2643

#### **4.2.2.1** Sensor architecture and functional blocks

The idea of using a stitched sensor chip to construct half of the detector layer is inspired by the design of the ALICE ITS3[5][6] sensor. Thanks to the promising results obtained in the MOnolithic Stitched Sensor (MOSS) and MOnolithic Stitched sensor with Timing (MOST) prototypes for the ALICE ITS3 project, this consideration benefits from the scheme of the MOSS and MOST prototype. Detailed R&D on the stitching floor

### Draft v04 4.2 Sensors and electronics design

plan for the vertex detector is under assessment at the time of writing. The preliminary

stitching plan of the silicon wafer and the dimensions of each half layer are introduced in

Figure 4.3.

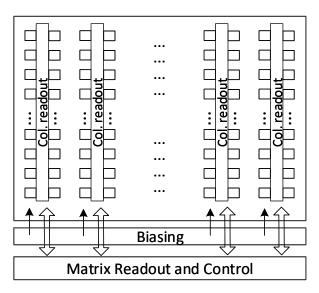

Figure 4.9 illustrates the floor-plan of one RSU. One RSU is divided into several 2653 identical Sensor Block. Each sensor block is fully independent from the others with its 2654 own biasing generator, slow control and periphery readout circuit, shown in Figure 4.10. 2655 The sensor block has local power switches located at the right side of the sensor block 2656 that can be selectively switched on by the user control. This powering granularity reduces 2657 the sensitivity of the stitched sensor to possible manufacturing faults. In the case of a 2658 supply short in one of the sensor blocks, it allows to switch off the faulty sensor block 2659 and maintain the others functioning normally. Considering the sensitive area of a sensor 2660 block will introduce an extra dead area in the event of switching off, the dimension of the 2661 pixel matrix in a sensor block should be choose carefully. The scale of a sensor block will 2662 be optimized in the future design for a trade-off between the power granularity and the 2663 data transmission performance. In the preliminary design at the time of writing, one RSU 2664 contains 12 identical sensor blocks and 4 stitched interface blocks arranged in two rows. 2665 Each sensor block has a single output for data readout at 86.66 Mbps. Data of each sensor 2666 block has to be transmitted to the LEB through the one-to-one direct connection between 2667 the sensor block and the LEB. As the longest transmission distance reaches more than 20 2668 cm for the rightmost sensor block of the module, the regeneration of the signal periodically 2669 over the link is necessary. This function is proposed to be implemented in the stitched 2670 data interface blocks. The stitched data interface block transmits control signals and data 2671 from/to the LEB. Table 4.7 provides plan of the dimensions of the LEB, REB and the main 2672 functional blocks that make up the Repeated Sensor Unit. Some values are derived from 2673 the experience gained from the design of TaichuPix prototypes. Table 4.7 provides the 2674 dimensions of individual functional blocks. As the RSU is divided into multiple sections 2675 internally, different functional blocks are repeated multiple times. An RSU contains 12 2676 Pixel Matrices, Biasing Blocks, Power Switches Blocks, and Matrix Readout Blocks, and 2677 4 Stitched Data interface Blocks. 2678

### Draft v041 4.2 Sensors and electronics design

**Figure 4.9:** Proposed floor-plan for a RSU (not to scale). It contains several identical sensor blocks. Each of them has a pixel matrix with its own biasing generator, slow control and periphery readout circuit. Each sensor block can be selectively switched on/off. The stitched data interface blocks are used to transmit control signals and data to the edge of the stitching sensor.

**Figure 4.10:** Architecture of the sensor block. It consists of a pixel matrix, a biasing generator block and a periphery readout and control.

**Table 4.7:** Plan of dimensions of the LEB, the REB, and the main functional blocks of one RSU.

|             | Pixel<br>Matrix | Biasing<br>Block | Power<br>Switches | Matrix<br>readout | Stitched interface | RSU    | LEB    | REB    |

|-------------|-----------------|------------------|-------------------|-------------------|--------------------|--------|--------|--------|

| Height [mm] | 8.409           | 0.053            | 8.409             | 0.177             | 8.409              | 17.277 | 17.277 | 17.277 |

| Width [mm]  | 3.296           | 3.333            | 0.019             | 3.333             | 0.055              | 20.000 | 4.154  | 1.385  |

### Draft v041 4.2 Sensors and electronics design

#### **4.2.2.2 Design of the repeated sensor unit**

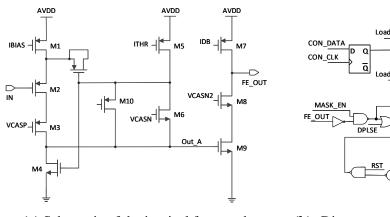

Each pixel cell integrates a sensing diode, a front-end amplifier, a discriminator and a digital pixel readout. The in-pixel digital readout benefited from the TaichuPix prototype. Each pixel contains a hit storage register and logic for pixel mask and test pulse configuration. A common threshold level is applied to all the discriminators of the pixels. Every pixel can be tested and calibrated individually, combining charge injection scans and threshold scans.

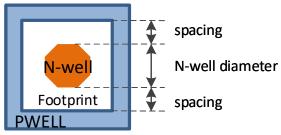

**I. Sensing diode** As depicted in Figure 4.11, the collection N-well electrode has an oc-2686 tagonal shape fabricated on a P-type epitaxial layer. The collection electrode is surrounded 2687 by the P-guard ring. The space between the collecting N-well and the surrounding P-well 2688 is introduced to increase the depletion region and thus enhance the charge collection effi-2689 ciency. Footprint represents the total area defined by the surrounding P-well. The design of 2690 the sensing diode geometry is a compromise among the charge collection performance (i.e. 2691 charge collection efficiency and time, radiation tolerance), area, and sensor capacitance. 2692 As mentioned in Section 4.5.1, the optimization of sensor performance was previously ad-2693 dressed in the 180 nm TowerJazz CMOS technology. These studies offer valuable insights 2694 for enhancing sensor performance in the 65 nm TowerJazz CMOS technology. To further 2695 optimize the sensor geometry to align with the 65 nm CMOS process, pixel test structures 2696 are proposed to be designed in the initial phase of the stitched sensor R&D. Various sensor 2697 variants in the test structures encompass different electrode diameters, spacing between 2698 electrode and surrounding PWELL, PWELL shapes, and the method of applying reverse 2699 bias to the sensor diode. 2700

**Figure 4.11:** Geometry of the sensing diode. It consists of the collecting N-well and the surrounding P-well.

**II. Pixel Front-end** The simplified schematic of the analogue front-end is shown in Figure 4.12a, which had been verified in the TaichuPix prototype (see Section 4.5.2). The topology of the circuit was derived from the ALICE Pixel Detector (ALPIDE) sensor chip used in the ALICE ITS2 [4]. The analog front-end and the discriminator are continuously active. The current consumption is mainly determined by the bias current (IBIAS) of the first branch , adjustable by one of the local Digital-to-Analog Converter (DAC)s in the

### Draft v04 4.2 Sensors and electronics design

<sup>2707</sup> periphery of the pixel array. Targeting the power requirement of 40 mW/cm<sup>2</sup>, the value of <sup>2708</sup> IBIAS is reduced compared to the one in the TaichuPix design. The choice of the IBIAS <sup>2709</sup> value is a trade-off between the power consumption and the speed. By design, the nominal <sup>2710</sup> power consumption values of the new front-end in TPSCo 65 nm process are 68.4 nW. <sup>2711</sup> The nominal value corresponds to analogue power densities of 26.7 mW/cm<sup>2</sup> for the pixel <sup>2712</sup> pitch of 16  $\mu$ m and 10.9 mW/cm<sup>2</sup> for the pixel pitch of 25  $\mu$ m.

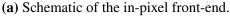

**III. In-pixel digital logic** The in-pixel digital electronics inherit the TaichuPix design. 2713 Figure 4.12b presents the diagram of the in-pixel logic. It features a hit latch set by a 2714 negative pulse from the output of the front-end. The pixel readout follows a double-2715 column drain arrangement. The region for in-pixel digital readout logic is shared by two 2716 columns to minimize the crosstalk between analog signals and digital buses. Additionally, 2717 it saves space for the routing of the address encoder. The priority logic arbitrates the 2718 pixel readout, with the topmost pixel having the highest readout priority. The in-pixel 2719 logic also integrates configuration registers for calibrating the pixel front-end, for testing 2720 in-pixel readout logic, and for masking the faulty pixel. The configuration function is 2721 programmable through the setting of control bits, including MASK\_EN, PULSE\_EN, 2722 DPULSE and APULSE (as shown in Figure 4.12b). 2723

(**b**) Diagram of the in-pixel digital logic.

Figure 4.12: Schematic and block diagram of the in-pixel circuits.

**IV. Peripheral readout circuits on sensor** The main function of the on-chip peripheral readout circuits includes: sending the control signals required by the pixel array and receiving the data from the pixel array; buffering the data to smooth the output data rate; providing a slow control interface for chip configurations and tests.

The data from the pixel array are organized in Double Columns (Dcols). In order to achieve a detection efficiency above 99 %, all double columns of pixel array are read out in parallel. A timestamp is recorded at the end of the double column for the future data

### Draft v04 4.2 Sensors and electronics design

processing. Without a trigger signal, all the readout data are buffered and output. A data

compression mode is optional, which, in our estimation, will reduce the output data rate

by half.

The peripheral readout circuit's core function is to send control signals to the pixel array and receive data from it. A data-driven schema is preferred. The read signal is only sent when the pixel is triggered. To read the signals sequentially, a priority mechanism must be implemented. The most popular method is address priority. A hit signal is generated when the collected signal exceeds a threshold and is reset after the pixel address is read out.

Based on this approach, the pixel array's clock is inactive in the absence of a hit. This approach effectively minimizes power consumption. To optimize control timing, a hierarchical priority control chain can be implemented.

To accommodate higher data rates, a real-time data compression strategy can be implemented before sending data to First In First Out (FIFO)s.

The address of the first pixel in a package is recorded, while the next three pixels are encoded using a three-bit code, where '0' represents no hit and '1' represents a hit. Operating at a system clock of 40 MHz, the data compression circuits incur no additional timing overhead. By enabling the data compression function, the data volume is reduced, and the readout speed is increased.

The fast chip-level readout is closely related to FIFO accesses. We propose a shareable architecture [10]. The shared FIFO features flexible capacities to handle random hit bursts. As a result, higher hit flux can be accommodated even with a reduced total memory volume.

The power consumption is evaluated based on TaichuPix, which is implemented 2753 using a 180 nm process for average hit rates of 1 MPixels/s·cm<sup>2</sup>, 15 MPixels/s·cm<sup>2</sup>, and 2754 40 MPixels/s·cm<sup>2</sup>. The future design of the RSU will use a 65 nm process. The power 2755 supply will be reduced from 1.8 V to 1.2 V. The area of the peripheral readout circuits is 2756 estimated to be reduced by 50 %. The dynamic power consumption due to clock and data 2757 upsets is estimated with a reduction of 4.5 times. However, the static leakage currents will 2758 increase significantly. To meet the power density of 40 mW/cm<sup>2</sup>, the power consumption 2759 of peripheral circuits in RSU is estimated to be 40 mW, the leakage current should be 2760 controlled in 5 times of TaichuPix. Power switches will be implemented to meet these 2761 requirements. Finally, the power consumption of the future design is estimated as 29 2762 mW and 37.5 mW for 8 MPixels/s·cm<sup>2</sup> (Higgs mode) and 44 MPixels/s·cm<sup>2</sup> (Z mode), 2763 respectively. 2764

<sup>2765</sup> Considering the application and tests, the sensor chip will provide proper register <sup>2766</sup> control and on-chip test mode.

The sensor chip includes control and status registers, which can be categorized into several types:

a. Read-only registers store internal status and can be read via the Inter-Integrated

### Draft v041 4.2 Sensors and electronics design

<sup>2770</sup> Circuit (I2C) interface or output from IO through a multiplexer.

- b. Internal control and configuration registers enable the selection of work modes,

clock frequencies, DAC settings, and more.

- c. Special configuration registers manage the pixel array, including mask and calibra tion registers.

d. Additional registers are dedicated to on-chip test configuration.

The On-Chip Test (OCT) module is planned to generate input signals for peripheral readout circuits, enabling chip debug and data alignment. Waveforms can be customized based on register settings. In chip debug mode, a test output port supports data transmission via the I<sup>2</sup>C interface.

<sup>2780</sup> The OCT and test output port operate independently.

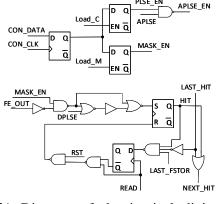

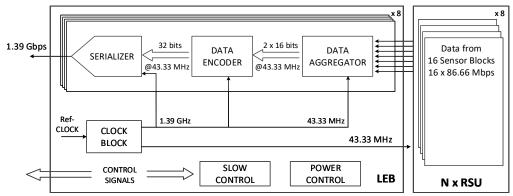

#### **4.2.2.3 Design of the left-end block**

All data from the RSUs per module (see Figure 4.14) are collected and processed by 2782 the LEB on the left side of a module. The block diagram in Figure 4.13 illustrates the 2783 main functions of the LEB. The data of the RSUs are transmitted to the LEB through a 2784 large array of differential point-to-point on-chip serial data links operating at 86.66 Mbps. 2785 As mentioned in Section 4.1.2, the individual module of different layers in the detector 2786 contains a varying number of RSUs. Among them, the single module in Layer 4 has the 2787 highest number of RSUs, which is 10. Since each RSU has 12 data links, the LEB needs 2788 to receive a maximum of 120 data links. A group of 128 receivers primarily compensates 2789 for phase differences in the incoming data streams from the RSUs and resamples them 2790 using the local fast clock. The data encoding blocks gather and encode the data with 2791 redundancy to correct errors during off-chip transmission. After encoding, the data is 2792 serialized at a speed of 1.39 Gbps and transmitted off-chip using 8 serializers. The Clock 2793 Block provides the required clocks for the LEB and RSUs. The functionalities of LEB 2794 also include providing slow control and power switches control signals for RSUs. 2795

**Figure 4.13:** Proposed diagram of the LEB. All data from RSUs of one module has to be transmitted to the LEB. 'N  $\times$  RSU' labeled in the right part of the diagram represents that different layers in the detector contain a varying number of RSUs.

### Draft VQ4 4.2 Sensors and electronics design

| _        | Module |     |     |                  |     |     |     |         |                  | _   |   |

|----------|--------|-----|-----|------------------|-----|-----|-----|---------|------------------|-----|---|

| SUPPLIES | LEB    | RSU | RSU | RSU              | RSU | RSU | RSU | RSU     | RSU              | REB |   |

| SUPPLIES | LEB    |     | RSU | - — — — —<br>RSU |     |     |     | <br>RSU | - — — — —<br>RSU | REB | - |

**Figure 4.14:** Top level floor-plan for a sensor of layer1 (not to scale). It contains two identical modules, with one of them indicated by the dotted red rectangle.

#### 2796 **4.2.2.4 Power consumption estimates**

As illustrated in Figure 4.9 and 4.10, each RSU consists of pixel matrix, biasing 2797 blocks, matrix readouts, and data interface blocks. Table 4.8 provides the expected power 2798 consumption of the main functional blocks of the RSU and the total power consumption 2799 of a single RSU. In Table 4.8, the entries for the pixel matrix include the power of the pixel 2800 analogue circuit and the pixel digital logic. In the current calculations, it is assumed that 2801 the pixel size is  $25 \times 25 \ \mu m^2$ , which is consistent with the intrinsic position resolution 2802 value used in Section 4.1.2. The power of the pixel analogue is calculated by the power 2803 density of the pixel front-end (shown in Section 4.2.2.2) and the total area of 12 pixel 2804 matrices (dimension of the pixel matrix is shown in Table 4.7). The power consumption 2805 of the pixel digital in the table includes the dynamic power of the in-pixel digital logic 2806 and the double-column address encoding logic (described in Section 4.2.2.2), as well as 2807 power consumption due to the leakage current. The dynamic power consumption of the 2808 pixel digital circuit mainly depends on the pixel hit rate. Based on estimations of the 2809 hit rate in the vertex detector and testing experience with the TaichuPix prototype, the 2810 dynamic power consumption of the pixel digital circuit is relatively small. In contrast, 2811 considering the planned use of 65 nm CMOS process, the contribution of leakage current 2812 from transistor gate leakage to power consumption is much greater than the dynamic 2813 power of the digital circuit. The contribution of the Biasing Blocks is estimated based on 2814 the experience of the design in the TaichuPix. The entry for the Matrix readout blocks 2815 is described in Section 4.2.2.2. The value for the data interface blocks is obtained from 2816 the very preliminary considerations on the transmitting power of the control signals and 2817 the readout data of RSUs. Table 4.9 lists the power consumption estimates for the main 2818 functional blocks of the LEB (see Figure 4.13). 2819

**Table 4.8:** Estimates of power consumption of one repeated sensor unit (RSU). All values are for 27 °C temperature and 1.2 V power supply voltage.

| Components | Pixelanalogue | Pixeldigital | Biasingblock | Matrixreadout | Datainterface | RSUTotal |

|------------|---------------|--------------|--------------|---------------|---------------|----------|

| Power [mW] | 36            | 30           | 8            | 40            | 17            | 131      |

### Draft V041 4.3 Mechanics, cooling and services

**Table 4.9:** Estimates of power consumption of the LEB. All values are for 27 °C temperature and 1.2 V power supply voltage.

| Components | ClockBlock | DataAggregator | DataEncoder | Serializer | Slow & Powercontrol | LEBTotal |

|------------|------------|----------------|-------------|------------|---------------------|----------|

| Power [mW] | 36         | 120            | 80          | 32         | 80                  | 348      |

Combining the power estimates of Table 4.8 and 4.9 with the surface areas of the major blocks found in Table 4.7, one obtains the estimates for the power dissipation densities. The results are given in Table 4.10.

**Table 4.10:** Estimates of average power dissipation per unit area over the main blocks composing the stitched chip

| Components           | Power density [mW/cm <sup>2</sup> ] |

|----------------------|-------------------------------------|

| Repeated Sensor Unit | 38                                  |

| Left-End Block       | 485                                 |

### **4.2.3** Backend electronics and cables

In the vertex detector design, flexible printed circuit boards (flex Printed Circuit Board (PCB)s) are integral to the backend electronics system. These flex PCBs serve as conduits for transmitting signals, clocks, control commands, power, and ground connections between the control boards and the detector modules. By providing a lightweight and adaptable interconnection, flex PCBs facilitate efficient data communication and power distribution while minimizing material usage, which is crucial for maintaining the detector's performance and reducing multiple scattering effects.

### **4.3** Mechanics, cooling and services

This section describes the mechanical design of the VTX, including the support structure and related finite element analysis, detector air cooling and the general scheme of services.

### **4.3.1 Mechanics**

### **4.3.1.1 General support structure**

The baseline design of the vertex detector consists of, from outer radius to inner radius, a single-layer double-sided ladder-based barrel followed by four concentric cylinders constructed with stitching technology-based bent MAPS (Monolithic Active Pixel Sensor).

### Draft V041 4.3 Mechanics, cooling and services

The innermost cylinder has a radius of 11 mm, and maintains a 0.3 mm gap from the beam pipe. As shown in Figure 4.1, the side view along the beam direction, this figure demonstrates the general structure of the detector and its integrated mechanical support. To be consistent with the physics requirements and goals, the general mechanical support design for the Vertex detector aims to use ultra-light materials to create a rigid enough structure, realizing a low material budget without weakening the spatial resolution.

#### **4.3.1.2 Ladder and support**

The double-sided ladder is the structural unit of the layer 5 and 6. It features pixel 2847 sensors on both sides of the ladder support, while sensors are glued onto the FPC, which 2848 is also glued onto the ladder support. The CFRP is used to make the ladder support due 2849 to its low density and high specific modulus and strength. The main body of the ladder 2850 support [11] is a hollow shell structure [11] with an overall size of  $682 \times 3.2 \times 17.5$ 2851 mm<sup>3</sup>. With the assistance of the finite element static analysis, the laminated shell of the 2852 ladder support is made of ultra-thin CFRP plies, using the high modulus CFRP at a level 2853 equivalent to M40, the CFRP laminate of the shell is made with a thickness of 0.15 mm, 2854 to get a conservative estimation by just putting the mass of the sensors and FPC to the 2855 bare ladder support (without taking into account their contribution to the rigidity of the 2856 complete ladder), it is anticipated that the ladder support deforms very slightly and at a 2857 negligible level. According to previous evaluations, about 20 % smaller deformation will 2858 be induced for the complete ladder [11]. 2859

#### **4.3.1.3** Ladder-based barrel and fixation to the beam pipe (assembly)

The vertex detector is the first detector outside the beam pipe, and structurally it will be integrated into the beam pipe assembly. The outer most layer of the vertex detector, the ladder-based barrel, does not directly mount on the beam pipe; it rests and is secured to the intermediate conical parts that are mounted to the beam pipe, providing support for the vertex structure. The four layers of bent MAPS cylinders are mainly fixed to the extended section of the beam pipe.

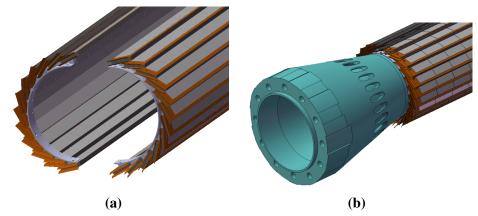

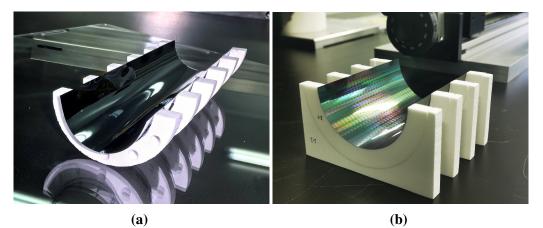

The barrel-shaped outer layer detector formed by the double-sided ladders which 2867 overlap with each other in the circumferential direction to form a continuous sensitive 2868 layer. To facilitate barrel assembling and its installation on the beam pipe integration, the 2869 barrel structure is designed as Figure 4.15 shows, it is assembled by two half-barrels, 2870 each half-barrel consisting of two half side-rings located at both ends along with several 2871 ladders. The ladders are positioned and secured to the side-rings by the surfaces of the 2872 tooth-shaped structure of the side-rings. After the two independent half-barrels are pre-2873 assembled on dedicated tooling, they are installed and fixed onto the intermediate conical 2874 part of the beam pipe assembly, as illustrated by Figure 4.15. 2875

### Draft VQ4 4.3 Mechanics, cooling and services

**Figure 4.15:** (a) The barrel assembly. (b) The barrel on beam pipe assembly (the outer tube of the beam pipe assembly is not shown)

Structurally, the ladder-based barrel design is consistent with our previous prototyped vertex design. Furthermore, much R&D work involving structural validation tests were conducted during the previous prototype development phase, these experiences can be helpful to optimize the TDR design.

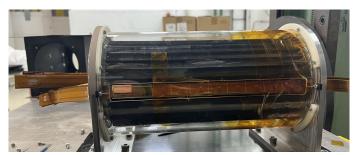

#### **4.3.1.4 Bent MAPS cylinders and fixation to beam pipe**

There are four layers of bent MAPS cylinders with different radii and lengths consis-2881 tent with the physical layout of the vertex detector. Each of the four bent MAPS cylinders 2882 is a single detector layer that consists of two half cylinders, as shown in Figure 4.16. To 2883 maintain the bent MAPS in the shape of the cylinders, ultra-light local supports made of 288 CFRP have been designed for each layer. Integrated with the electronic readout, the FPC 2885 is connected to the curved edge of the bent MAPS on its lateral side by wire bonding . 2886 To keep the connecting joint safe and also for protecting the wire bonds, extended support 2887 has been designed for each cylinder, as shown in Figure 4.16, it prevents the FPC from 2888 deforming very close to the joint area, thereby avoiding damage to the connection. The 2889 bent MAPSs, the local support and the extended support form the cylinder assembly. Each 2890 cylinder assembly is independent and has no contact with the adjacent layers of cylinder 2891 assemblies, also will be mounted onto the beam pipe assembly separately. This kind of 2892 design focuses primarily on realizing and facilitating a feasible process for both assembly 2893 and wire bonding, as well as installation onto the beam pipe. The results of the finite 2894 element simulation analysis indicate that, under constrained conditions at both ends, this 2895 structure has very minimal deformation, and the stress on the bent chips is also very low, 2896 both of which are negligible, taking the innermost layer bent MAPS cylinder assembly as 289 an example. In addition, some R&D studies of making the bent MAPS have been done; 2898 so far, the dummy wafer with a thickness of 40 µm and a radius of 12 mm has been tested 2899 and proven to be feasible, refer to Section 4.5.2.3. 2900

### Draft v041 4.3 Mechanics, cooling and services

**Figure 4.16:** The half cylinder assembly (bent MAPS with FPC and the extended support) of the innermost layer. (a) An overview of the half cylinder of bent MAPS detector layer, and the yellow part is FPC. (b) An extended support to prevent the FPC from deforming too close to the joint area.

### 2901 4.3.2 Cooling

The heat generation of the Vertex detector for both the ladder-based barrel and the bent MAPS cylinders is estimated to be at the same level of 40 mW/cm<sup>2</sup>. The operational temperature for the detector is required to be no higher than 30 °C. Thus, cooling is essential for maintaining optimal sensor performance. Generally, electronic equipment with heat generation up to  $0.3 \text{ W/cm}^2$  can be cooled using forced air convection. Given the stringent material budget requirements for the vertex detector, compressed air cooling has been selected as the cooling method.

To evaluate the cooling performance of the current structural design of the vertex 2909 detector, air cooling simulation analysis was conducted. The simulation results indicated 2910 that at an average flow rate of 3.5 m/s, the maximum temperature of the outer ladder is 2911 within the required range, as shown in Table 4.11. For the bent MAPS cylinders, the 2912 innermost layer is very close to the beam pipe and has no airflow, making it the most 2913 challenging layer to cool within the entire detector. The simulation results indicate that 2914 at an airflow rate of 3.5 m/s (which satisfies the ladder cooling), with the central beam 2915 pipe surface temperature considered, the innermost layer of the bent MAPS cylinder can 2916 be cooled to a sufficiently low temperature, as shown in Figure 4.17, thereby meeting 2917 the experimental requirements. Additionally, simulations were performed to compare the 2918 maximum temperature of the innermost layer at different wind speeds. Based on these 2919 simulation results, it can be anticipated that air cooling will meet the current cooling needs 2920 of the detector. 2921

### Draft V041 4.3 Mechanics, cooling and services

**Table 4.11:** Simulation results of the barrel-maximum temperature on the ladder. Inlet air temperature of 5  $^{\circ}$ C; air speed of 3.5 m/s.

| Power dissipation    | Total heat generation of the barrel | Max temperature on ladder |  |

|----------------------|-------------------------------------|---------------------------|--|

| $40 \text{ mW/cm}^2$ | 190 W                               | 29.4 °C                   |  |

|                      |                                     |                           |  |

**Figure 4.17:** Simulation results for the cooling of bent MAPS cylinders, with an airflow rate of 3.5 m/s. The beam pipe surface temperature, as shown in Chapter 3, is taken into account.

#### 2922 **4.3.3 Services**

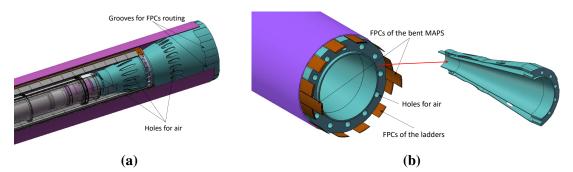

This section introduces the needs and considerations of the general services for the Vertex detector. The vertex uses air cooling; the main service requirement is to ensure proper airflow and good ventilation for the entire detector zone. The vertex detector will be mounted onto and integrated into the beam pipe assembly; the other service requirement is to route all the cables of the VTX out of the very space-limited beam pipe assembly.

Since the VTX consists of a single barrel layer and four concentric cylinder layers, 2928 ventilation for each gap between the adjacent layers must be ensured for effective cooling. 2929 The mechanical design for the vertex detector fully considered this requirement and also 2930 tried to minimize the effect caused by FPCs blocking, which is obviously reflected in 2931 the hollow support structures designed for the detector, especially the support of the bent 2932 MAPS cylinders. The conical part that is integrated into the beam pipe assembly to support 2933 the barrel layer mentioned before also works as the general air distributor for the entire 2934 vertex detector. It is a hollow structure; air will be blown into the inside hollow space 2935 from the side of the part then distributed to the detector zone through those ventilation 2936 holes facing different zones of the detector on the outer surface, as shown in Figure 4.18. 2937 The space for the entire VTX outside the beam pipe is very compact. Together with 2938 the beam pipe assembly, for the vertex detector, on both ends of the barrel and the bent 2939

### Draft v04 4.4 Alignment and calibration

MAPS cylinders, the FPCs of the ladders and the bent MAPS are the only cables that need 2940 to be routed out. The FPCs of the bent MAPS cylinders will be routed along their extended 294 support and converged after the end of the outermost layer, and then they are stacked and 2942 go through the intermediate conical part via the grooves. The FPCs of the ladders of layer 5 2943 and 6 will be streamlined by converging the FPCs of two adjacent ladders into one conduit, 2944 similar to the FPCs of the bent MAPS, then go through the conical part via their specified 2945 grooves, as illustrated in Figure 4.18, which effectively halves the spatial occupancy and 2946 preventing the circumferential accumulation of FPCs from fully cover the outer surface of 2947 the conical part. After all the FPCs are routed outside the beam pipe assembly, they will 2948 be transferred to optical fibers via connectors, as described in Section 4.2. Additionally, 2949 a half-dummy model of the vertex structure, incorporating the bent MAPS cylinders and 2950 two short ladders, was constructed to test the FPC routing. The trial results demonstrated 2951 that the routing scheme is fundamentally feasible. 2952

**Figure 4.18:** Air ventilation and cable routing of the VTX. (a)Air channel design with holes on global support structure for air distribution. Grooves on support structure is designed for FPCs routing. (b) the FPCs of the vertex detector routed out of the side of the beam pipe assembly, along with a cut view of the conical part.

### **4.4 Alignment and calibration**

The vertex detector is designed to precisely measure the trajectory parameters of charged particles close to the interaction point, enabling accurate reconstruction of decay vertices from short-lived particles. Effective alignment is crucial for achieving optimal resolution in the vertex detector.

The alignment strategy for the vertex detector faces significant challenges due to the implementation of bent wafer-scale monolithic pixel sensors. The primary goals of this strategy include achieving high spatial resolution, reducing uncertainties in impact parameters, and ensuring stable alignment through efficient and automated processes.

### Draft v04 4.4 Alignment and calibration

#### **4.4.1** Initial mechanical alignment and reference alignment system

Initial mechanical alignment will be conducted during detector assembly, utilizing precision optical survey instruments. Sensors will be aligned within a few micrometers of design specifications, and optical method will confirm sensor curvature and cylindrical positioning. Fiducial markers placed strategically on sensor modules and supporting structures will facilitate optical tracking and ensure precise referencing. A stable external alignment system, regularly monitored through X-ray or laser-based and optical survey methods [12], will serve as the reference for continuous alignment.

### 2970 4.4.2 Track-based alignment

Mechanical alignment procedures during installation provide an initial level of preci-2971 sion in the vertex detector position. This precision is typically significantly worse than the 2972 desired design hit resolution. Additional alignment (tracker-based alignment) is needed 2973 to account for the position, orientation, and surface deformations of the MAPS sensors. 2974 Charged particle tracks obtained from collision data will facilitate iterative alignment 2975 corrections during both the commissioning and operational phases. Global and local  $\chi^2$ 2976 minimization algorithms will refine sensor positioning, enhancing accuracy and ensuring 2977 optimal detector performance. 2978

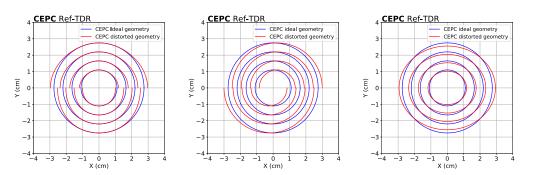

In the current detector design, simulations have demonstrated the ideal performance of the detector; however, in practical applications, it is necessary to consider the typical deformation mode as shown in Figure 4.19. The deformation includes elliptical deformation; irregular, wavy distortion; circular distortion with uniform radial expansion.

These deformation modes can affect the detector's ability to determine the relative 2983 positions of collision products as they pass through the vertex detector, ultimately im-2984 pacting the accuracy of the reconstructed collision parameters  $d_0$  and  $z_0$ . The effect of 2985 each of these deformations was studied in the simulation by modifying the position of 2986 the hits according to the three types of deformation. In particular, for each simulated 2987 charged-particle trajectory, the intersection with the deformed geometry was computed 2988 to determine the corresponding position of the hit in the local detector coordinates. The 2989 track-reconstruction algorithm was then executed assuming an ideal geometry to quantify 2990 the effect of the detector deformations in the absence of a detector alignment procedure. 2991

#### 2992 4.4.3 Real-time monitoring

A laser-based online alignment monitoring system will perform real-time checks, verifying alignment accuracy continuously.

Due to the air cooling design in the vertex detector, it is important to monitor the movement of the MAPS sensors. Inspired by the laser alignment system of CMS

### Draft v041 4.4 Alignment and calibration

**Figure 4.19:** Illustration of the hit positions in the transverse plane with ideal vertex geometry and three deformed geometry. The amount of deformation is amplified with respect to the expected one for visualisation. Left Figure: elliptical deformation. The red distorted geometry is elongated horizontally, demonstrating a deformation primarily along the x-axis. Middle Figure: Illustration of the hit positions in the transverse plane for vertex geometry exhibiting irregular, wavy distortion. The distorted geometry has noticeable undulations, indicating non-uniform deformation affecting both the x and y directions unevenly. Right Figure: Illustration of the hit positions in the transverse plane for vertex geometry showing a circular distortion with uniform radial expansion. The distorted geometry presents a uniformly increased radius, representing an isotropic deformation compared to the ideal geometry.

experiment [12], it is proposed to install laser alignment system to keep track of these 2997 movement. In Figure 4.20, a laser source placed on the right side of the 4th layer of chips 2998 is used to monitor the movement of the first layer of MAPS; laser sources are placed on 2999 the service portions on both sides to monitor the movement of the 3rd, 2nd and 1st layer 3000 of MAPS. This system utilizes near-infrared laser beams (1050 nm) directed through the 3001 vertex detector to detect potential movements or deformations of the mechanical structure. 3002 Laser sources located in service areas are triggered to send pulsed infrared light to MAPS 3003 sensors of the vertex detector. By detecting their interaction with the silicon sensors, the 3004 system can infer movements of the MAPS sensors, ensuring that any deformations due to 3005 environmental factors like temperature, air flow, or magnetic fields are promptly identified. 3006

**Figure 4.20:** A laser-based online alignment monitoring system. Red lines diagonally connect with the aqua blue line (MAPS chip) are the lasers, and the laser sources are placed at both sides of the inner three layers and right side of the 4th layer to monitor the movement of each layer.

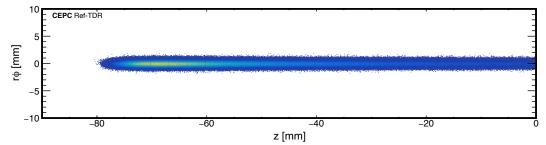

To validate the laser calibration system, signals generated by the laser were simulated using Geant4 [13] within the CEPCSW framework. The laser was emitted as a point

source from the position (13 mm, 0, -85 mm), directed at an angle of  $\theta = 10^{\circ}$  and  $\phi = 0$ . In the absence of a focusing system, a divergence of tan  $\alpha = 0.1$  was established.

The resulting laser beam spot on the second layer of the vertex detector is presented in Figure 4.21.

**Figure 4.21:** The laser beam spot on the second layer from (13 mm, 0, -85 mm) in cylindrical coordinate system, where the horizontal axis is the *z*-coordinate, and the vertical axis is the  $r\phi$  coordinate. And each region is divided by a blank or lower rate than its neighbor means one sensor.

<sup>3013</sup> When simulating deformation by radially displacing the second layer outward by d =<sup>3014</sup> 10µm, the resulting distribution of signal IDs, The observed difference of 2 corresponds to <sup>3015</sup> a distance of 50µm, which is consistent with relationship  $d/\tan\theta \approx 57$ µm. If an accurate <sup>3016</sup> fitting function can be employed to characterize this distribution and precisely determine <sup>3017</sup> the most probable position, it would enable more accurate detection of displacement. <sup>3018</sup> These findings indicate that the laser calibration system can infer positional changes <sup>3019</sup> through the distribution of pixel IDs.

#### **4.5 R&D efforts and results**

To meet the stringent requirements of high spatial resolution, low material budget, 3021 rapid readout speeds, and low power consumption, significant efforts have been directed to-3022 ward advancing MAPS technologies, notably through the TaichuPix and JadePix projects. 3023 The JadePix project focuses on investigating CMOS pixel sensors for the CEPC 3024 vertex detector, exploring low-power readout schemes. Concurrently, the TaichuPix series 3025 is dedicated to developing MAPS featuring advanced in-pixel electronics optimized for 3026 rapid readout. These sensors utilize a data-driven, column-drain architecture specifically 3027 designed to meet the fast response requirements imposed by the high collision rates at 3028 CEPC. 3029

#### **4.5.1 CMOS pixel sensor JadePix series**

The CEPC vertex detector imposes stringent requirements on spatial resolution. To achieve a spatial resolution of 3  $\mu$ m, the pixel size needs to be reduced to less than 20

$\mu$ m, which is limited by the feature size of integrated circuit technology. JadePix utilizes a specialized 180 nm CMOS integrated circuit process optimized for ionizing radiation detection, which is a modification and development based on the commercial CMOS Imaging Sensor process. The pixel pitch in this process typically ranges from 25 to 30  $\mu$ m. Therefore, the key focus of JadePix's development is on how to reduce the pixel size while also meeting the requirements for low power consumption and fast time stamping.

#### **3039 4.5.1.1 Overview of JadePix development**

The JadePix series of chips are primarily designed and optimized for high spatial resolution, low power consumption, and fast time stamping. Since 2015, a total of 5 chips have undergone continuous improvements which are shown as Table 4.12.

| Chip<br>Name | Pixel<br>Array     | Pixel Pitch(µm <sup>2</sup> ) | Analog Front-end       | Matrix Readout  | Design Team              |

|--------------|--------------------|-------------------------------|------------------------|-----------------|--------------------------|

| JadePix-1    | 128×192,<br>160×96 | 16×16, 33×33                  | Source follower        | Rolling Shutter | IHEP                     |

| JadePix-2    | 96×112             | 22×22                         | Diff. Amp.,<br>CS Amp. | Rolling Shutter | IHEP                     |

| JadePix-3    | 512×192            | 16×23, 16×26                  | ALPIDE                 | Rolling Shutter | IHEP, CCNU,<br>SDU, DLNU |

| JadePix-4    | 356×489            | 20×29                         | ALPIDE                 | AERD            | CCNU, IHEP               |

| JadePix-5    | 896×480            | 20×30                         | ALPIDE                 | AERD            | IHEP, CCNU               |

Table 4.12: Overview of JadePix development

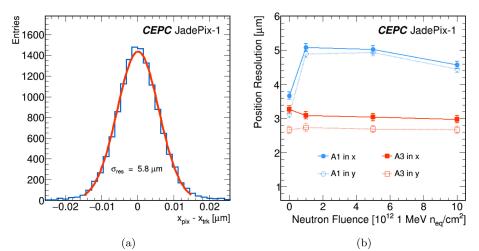

JadePix-1[14] primarily focused on sensor optimization, comparing different geometric dimensions [15] and providing experimental evidence for the design of small charge collection electrodes [16]. As Figure 4.22 shows, the optimal spatial resolution obtained through beam tests on a  $33 \times 33 \mu m^2$  pixel array was 2.7 $\mu m$  [17].

**Figure 4.22:** (a) Residual distribution of JadePix-1 sensor in the x direction; (b) position resolution for sensors with a small electrode (A1) and a large electrode (A3) before and after the neutron irradiation.

JadePix-2 investigated AC coupling and different analog front-end amplifiers [18], attempting to optimize resolution, power consumption, and time stamping design using a 180 nm process based on the Minimum Ionising MOS Active pixel sensor (MIMOSA) architecture.

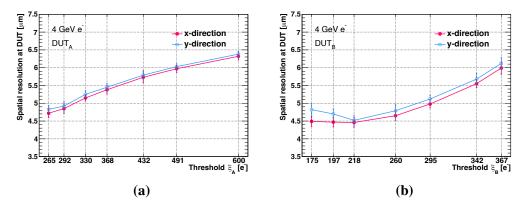

JadePix-3 utilized the low-power front-end amplifier of ALPIDE[4], combined with 3051 a Rolling Shutter readout architecture, achieving the smallest pixel design among similar 3052 chips at  $16 \times 23 \mu m^2$ . Infrared laser tests showed spatial resolutions of 3.4  $\mu m$  (X-direction) 3053 and 2.7 µm (Y-direction) [19]. A 5-layer beam telescope system was constructed based on 3054 this chip, measuring spatial resolutions on a 5.8 GeV electron beam of 5.2 µm (X-direction) 3055 and 4.6  $\mu$ m (Y-direction) [20]. The cluster size from beam tests was significantly larger 3056 than that from laser tests, adversely affecting the spatial resolution. The highest efficiency 305 reached 99 % at the optimum threshold of 160  $e^{-}$ . 3058

JadePix-4 and JadePix-5 employed ALPIDE analog front-ends and AERD readout architectures. The latter is an efficient sparse readout logic that can quickly read out the addresses of hit pixels at very low power consumption and apply time stamps around the periphery of the pixel array. The AERD readout architecture has been adopted not only by various CMOS pixel chips on the 180 nm process but also by the next-generation 65 nm Stitching process.

### **3065** 4.5.2 MAPS TaichuPix series

To meet the CEPC requirements for operating at the Higgs, *Z*, and *W* modes with bunch-crossing intervals of 554 ns, 23 ns, and 185 ns, a maximum hit rate of  $36 \times 10^6$  cm<sup>-2</sup> ·  $s^{-1}$  is required.

3069

In order to address the high hit density of the CEPC, a MAPS, named TaichuPix, has

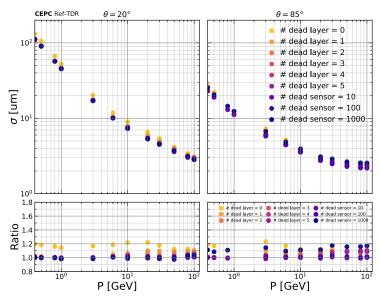

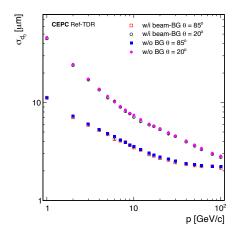

<sup>3070</sup> been developed with the goal of high readout speed and high spatial resolution. TaichuPix-<sup>3071</sup> 1[7] and TaichuPix-2[8], are multi-project wafers, and TaichuPix-3 is a full-scale prototype <sup>3072</sup> with an engineering run. The pixel matrix of TaichuPix-3 is  $1024 \times 512$  with a pixel pitch <sup>3073</sup> of 25 µm, and a thickness of 150 µm. The proposed baseline vertex detector consists of <sup>3074</sup> three layers of ladders, with double-sided mounted TaichuPix-3 sensors.