# 2025年9月考核报告

报告人：李灿明

导师：赵京周

专业：核技术及应用

时间：2025.9.5

# 报告主要内容

## ■ iRPC探测器四路取数实验设计

- PETIROC 刻度

- TDC 通道一致性调整

- 四路数据分析

## ■ iRPC 后端电子学四路固件功能验证

- 探测器数据模拟

- DAQ链路/慢控链路搭建

- 数据打包机制研究

- 数据包分析脚本开发

## ■ 其他工作及后续计划

- AMC13功能验证固件开发

- CMS中国组年会报告

- Serenity远程加载调试平台搭建

- 后续计划

# iRPC探测器四路取数实验设计

## ■ 实验设计

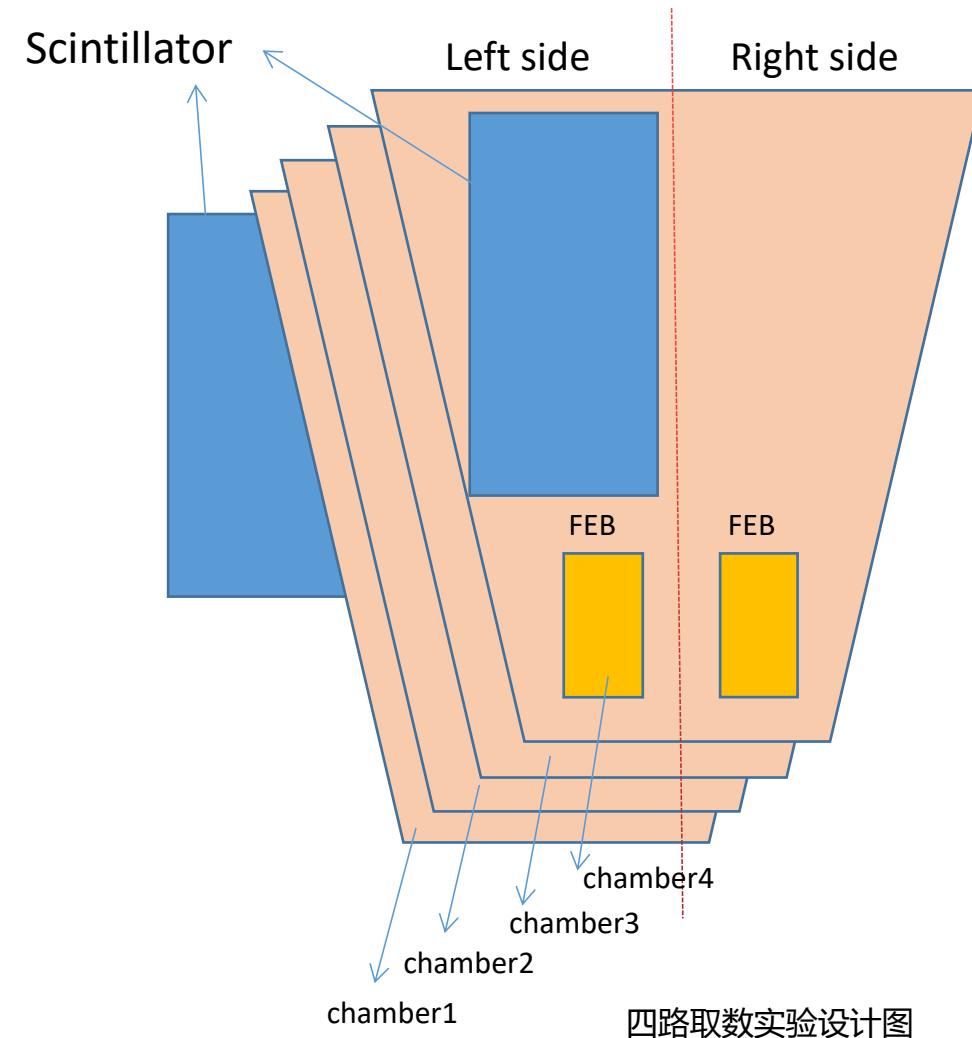

- 为了进一步验证目前BEE四路固件的功能，与合作组成员沟通后设计了实验方案，在**CERN 904 Lab**搭建了测试系统。

- 包括四块iRPC RE3/1 Chamber, 每块Chamber对应两块前端板，取左侧前端板分别命名Link1/2/3/4

- 通过上下两块闪烁体探测器进行**宇宙线符合**，作为Trigger信号送入系统并进行取数。

- 在取数前，对前端板 PETIROC 进行刻度，并调整前端板 TDC 通道一致性。

# iRPC探测器四路取数实验设计

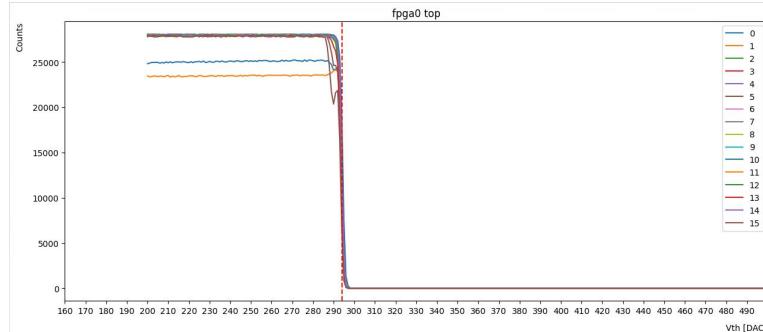

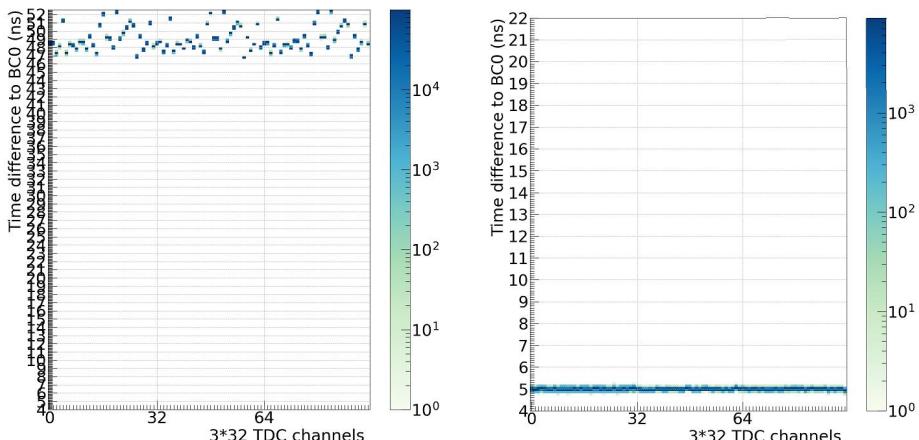

## ■ 前端板的刻度与对齐:

- 将目前的慢控脚本由两路扩展至四路，刻度和对齐后的参数通过Sitcp链路经由后端对前端进行配置

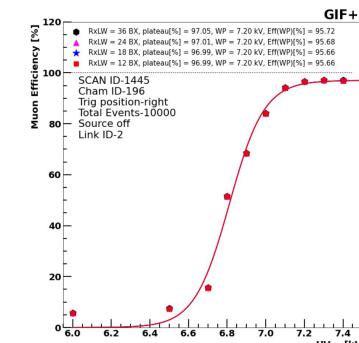

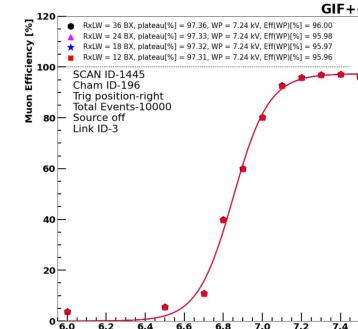

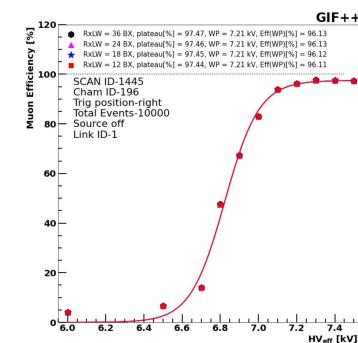

PETIROC 对齐后的阈值扫描曲线

TDC 通道一致性调整之前（左）和之后（右）的结果对比

## ■ 数据分析:

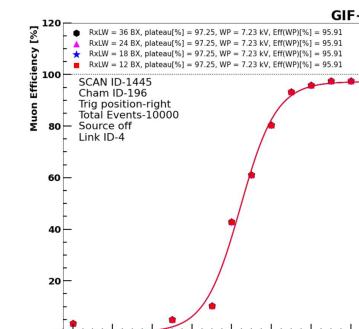

- 在每个高压点下 (6300V~7300V) 取2000个事例数据，进行了效率曲线分析。

- 各链路效率接近，初步验证了四路固件可以工作，但效率偏低，需进一步研究。

四路效率曲线

# iRPC 后端电子学固件功能验证

## ■ 研究目的:

针对目前开发的四路固件进行功能验证，最终给出确定版本的mTCA系统固件，主要内容包括：

- 高事例率下系统功能验证

- 簇查找算法正确性

- DAQ打包机制是否合理，高触发率下数据打包是否完整

- 当前系统的Busy反馈机制是否有效

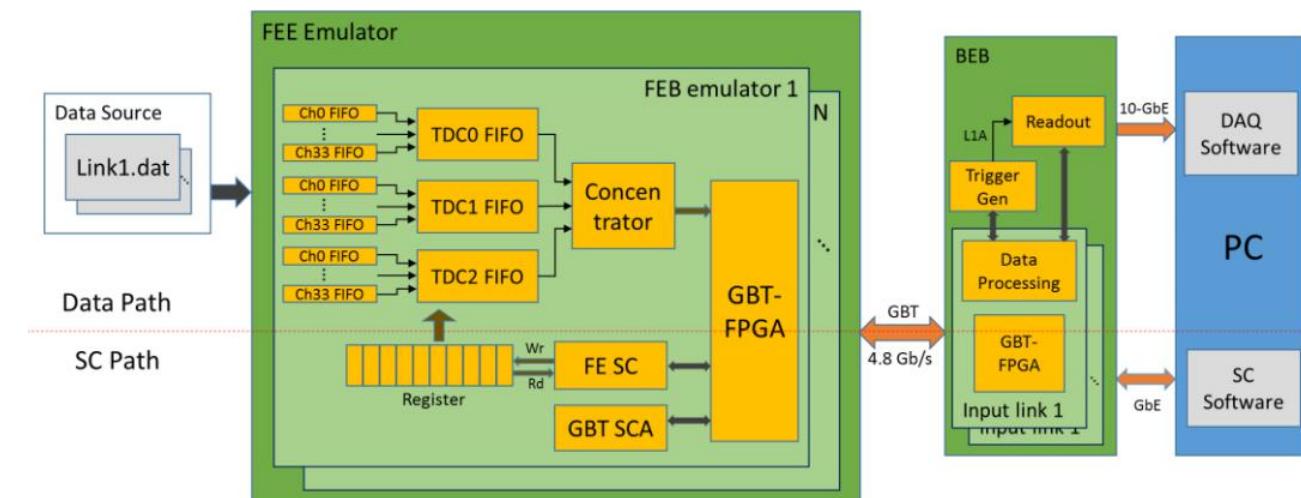

## ■ 探测器击中数据模拟:

- python开发模拟脚本，随机模拟粒子在探测器上的击中位置，包含48根条共96个TDC通道的时间信息，并实现触发率可调，以匹配phase2阶段750kHz事例率

## ■ 慢控链路搭建:

- 搭建了基于ipbus的千兆慢控链路，对上位机环境进行配置

- 通过慢控链路配置BEE的初始化及算法使能等

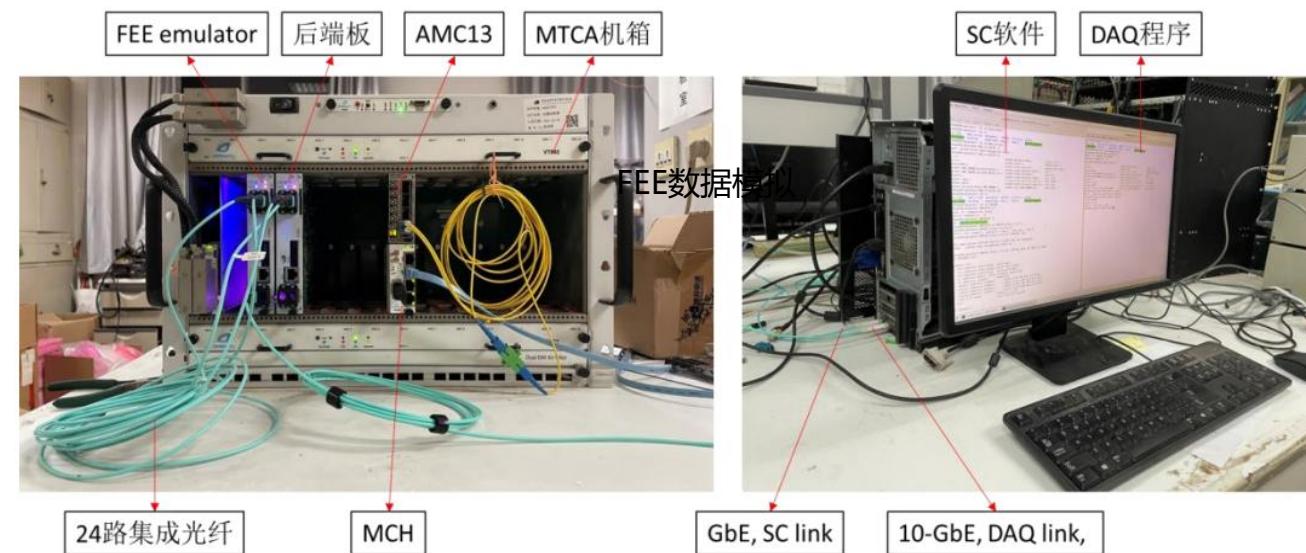

FEE数据模拟

# iRPC 后端电子学四路固件功能验证

## ■ DAQ链路搭建及验证

- 重新开发了基于千兆sitcp的数据读出链路

- 对当前DAQ的数据打包机制的合理性以及所需延迟进行了全面验证，发现目前的打包延迟无法满足phase-2阶段高触发率下的延迟要求，计划开发新的打包/读出机制

## ■ 数据包分析脚本开发：

- 对数据的事例长度、触发号、包头包尾格式进行检查，验证数据打包功能正确性

- 将DAQ得到的簇团信息与模拟数据原始信息比对，验证后端固件算法正确性

## ■ 版本管理：

- 使用TCL脚本进行工程的导出与重建，解决之前工程嵌套的问题，使用git进行工程管理

- 验证了数据打包/后端算法的正确性，给出正式版本

CMS二期触发升级原型机系统

# 其他工作及后续计划

## ■ AMC13功能验证固件开发:

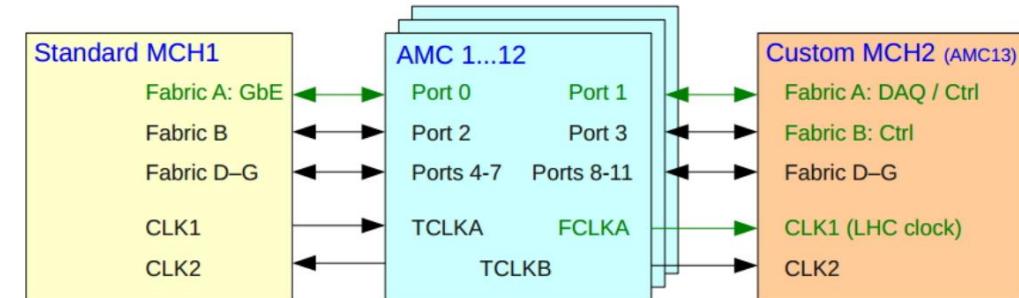

- AMC13为mTCA系统中定制的MCH插件，接收CMS全局分发的TTC光纤信号，恢复出LHC时钟和TTC信号

- 与RPC合作组协调，开发验证固件，验证后端板是否接收到来自分发来的时钟和L1A等信号，帮助进行AMC13调试

## ■ CMS中国组2025年会报告:

- 作题为“CMS iRPC Trigger Latency optimization Research”工作报告

- 报告内容主要包括CSP(Check- sort- Push) 相关研究以及FEB Sending Delay Register参数研究

CMS

### FEB Sending Delay Register

Trigger Lab IHEP

- Background and purpose:

- The transmission delay of the front-end electronics has been greatly reduced by CSP, but is still higher than expected and exceeds simulation results.

- Next Steps: Optimizing the FEB Sending Delay Register to further reduce transmission delays.

- TDC Sending Delay

- Definiton:** The difference of TDC data sending time and generation time(BX)

- 2 stage of hard limit** of delay transmission:

- TDC Level: the creation time to transmission time to CONCENTRATOR , in 120 Mhz

- Concentrator Level: Pending time at concentrator buffer, in 40Mhz

CMS China 2025

Structure of the FEB

9

7

# 其他工作及后续计划

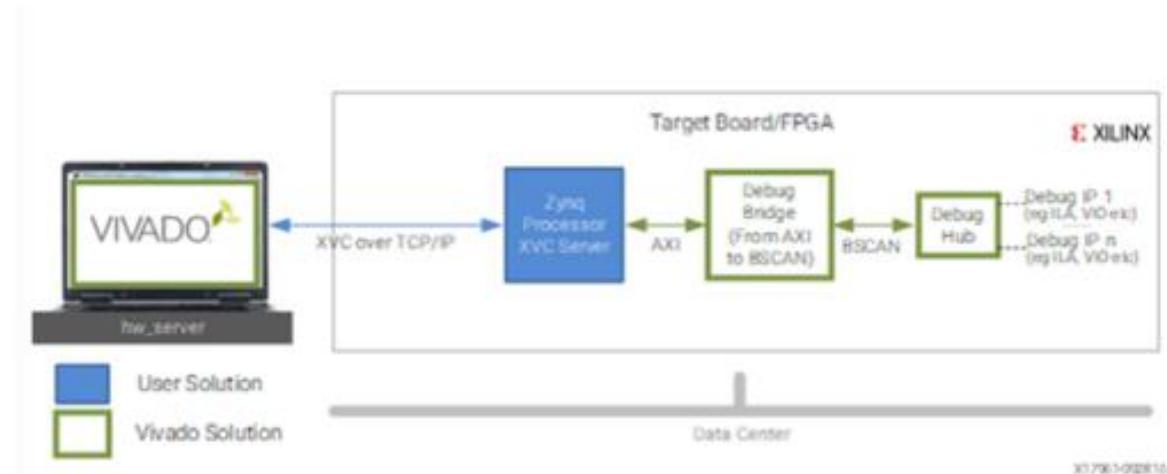

## ■ Serenity远程加载调试平台搭建：

- Serenity是phase2阶段ATCA系统后端原型板卡，其固件加载比特流有多种方式

- 计划使用vivado提供的xvc (Xilinx Virtual Cable) server功能，搭建测试平台，远程使用图形化界面进行加载与调试

## ■ 后续计划：

- 前往CERN进行四路固件的平台搭建与取数验证，并在P5搭建多块后端板的系统

- 与EMTF部分进行系统联调，验证固件功能正确性

- 针对ATCA系统进行固件移植与开发

请各位老师批评指正！