# Silicon Tracker Weekly Meeting

11 October 2025

张嘉健

● 主要工作: DAQ 与 碳纤维桁架制作

### ● DAQ 用途:

- AC-LGAD laser test, beta source & beam test

- AC-LGAD + LATRIC test

#### DAQ

- Baseline: Oscilloscope

5~10Gsps sampling rate,

- >1.5GHz bandwidth

- Option: FPGA + ADC

- ADC12DJ3200 6.4Gsps FMC AD子卡 (1-ch 6.4 / 2-ch 3.2)

- AD9695 1.25Gsps FMC AD子卡 (4-ch 1.25)

- AD6688 / AD9208 3.0Gsps FMC AD子卡 (2-ch 3.0)

- DC couple up to 900MHz bandwidth

- AC couple 50M ~ 1GHz to 6GHz (Balun transformer)

- Further study is also performed for bandwidth & sampling rate requirement

- Option: FPGA + customized TDC

27

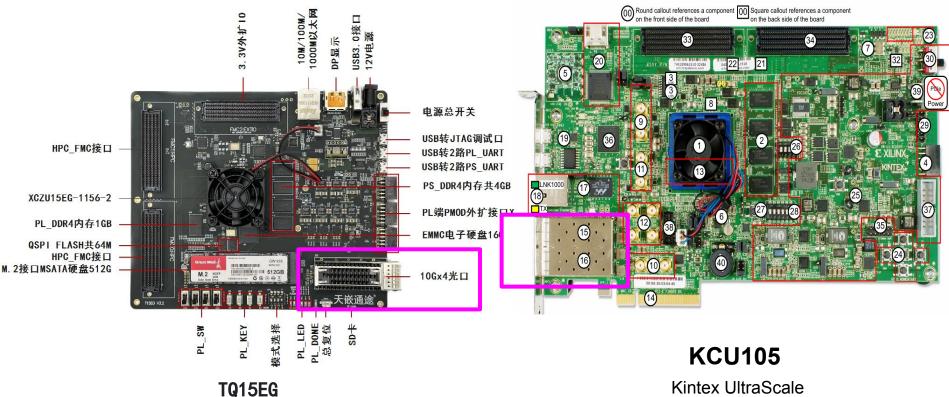

## 开发板

Zynq™ UltraScale+™ MPSoCZU15EG

Kintex UltraScale XCKU040-2FFVA1156E Device

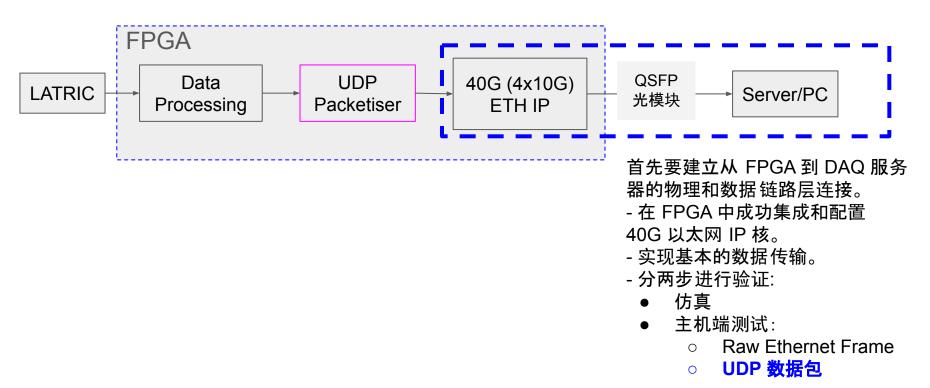

#### 从ASIC到DAQ服务器的简化数据流:

## QSFP 40G→ 4x10G IP Core

在硬件部署前, 通过仿真验证 40G 以太网 IP 核的功能。

- 创建一个测试平台 (Testbench)。

- 生成 AXI-Stream 流量作为 IP 核的输入 (Tx)。

- 监视 IP 核的输出 (Rx)。

#### 从ASIC到DAQ服务器的简化数据流:

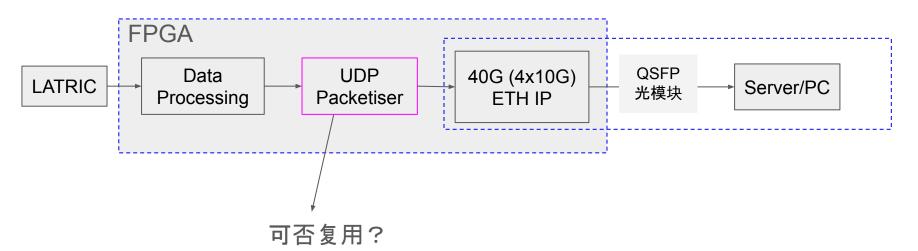

## UDP 模块用于 QSFP+ 4x10G?

RGMII 接口的 10G 以太网 编写的 UDP 模块直接用于 Vivado 中的 QSFP+ 4x10G 以太网 接口并不直接可行,除了UDP 数据包生成/解析逻辑协议层(如校验和、头部处理等)可以复用, 其他部分需要自行编译/修改.

| 特性            | GMII 1G Ethernet                                       | QSFP+ 40G->4x10G                               |

|---------------|--------------------------------------------------------|------------------------------------------------|

| 物理接口          | 通常通过 PHY 芯片使用 RGMII(10G 下罕见;10G 通常使用<br>SGMII 或 XGMII) | 使用4 条 10G 串行链路(例如通过Aurora、XAUI或<br>10GBASE-KR) |

| MAC 层接口       | 使用 <b>GMII</b> /XGMII或AXI4-Stream                      | 通常通过AXI4-Stream与40G/50G 以太网子系统或CMAC连接          |

| 时钟方案          | 源同步时钟(例如 1G 时为 125 MHz)                                | 使用高速收发器(GTY/GTP/GTM)和恢复时钟                      |

| 所用 FPGA IP    | 通常为三速以太网 MAC + RGMII 接口                                | 10G/25G or 40G/50G 以太网子系统(用于 UltraScale+)      |

| 数据位宽 / 速<br>率 | 并行(例如 8/16/32 位 @ 高频时钟)                                | 串行(64b/66b 编码, 每通道 64 位 @ <b>156.25 MHz</b> )  |

正在编写适用于 QSFP+ 4x10G 以太网UDP 模块

## 后续安排:

● 编译适用于 QSFP+ 4x10G 以太网UDP 模块

- 主机端测试:

- Raw Ethernet Frame

- FPGA 发送不带高层协议(如IP/UDP)的原始以太网帧。

- 使用MAC地址在单个本地网络网段内进行点对点通信,无法在不同网络之间路由。

- 在 DAQ 服务器上,使用 `tcpdump` 或类似的抓包工具捕获数据帧,验证其内容和格式的正确性。

- 需要 SFP+ NICs

- UDP 数据包

- 在 FPGA 中实现一个 UDP 封装器 (Packetizer), 将数据封装成 UDP 包。

- 在服务器上编写一个简单的接收程序,监听指定端口,接收并验证 UDP 数据包的负载和完整性。