## 基于USB的多通道准高斯型脉冲信号发生器设计

祁宾祥 刘树彬 等

核探测与核电子学国家重点实验室 中国科学技术大学近代物理系

## 主要内容

## 设计介绍

性能测试

总结

## 设计背景与需求

▶大型粒子物理实验的规模越来越大,其电子学系统的通道数也越来越多;

如CERN的LHC读出电子学通道数达10<sup>8</sup>量级; BEPCII配套的大型通用探测器BESIII的电子学通道数超过10000路; 即将建造的LHAASO-WCDA探测器电子学需求通道为3600路

- ➤前端电子学在研制过程中都需用精密信号源校准测试每个通道的时间、幅度测量精度等参数;

- ▶常用于测试的商业信号发生器如Tektronix公司的AFG3252只有两个通道,且价格不菲;

- ▶校准测试如此大量的电子学通道是一项非常耗时繁 琐的工作。

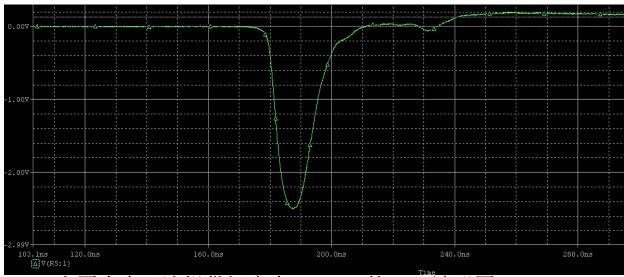

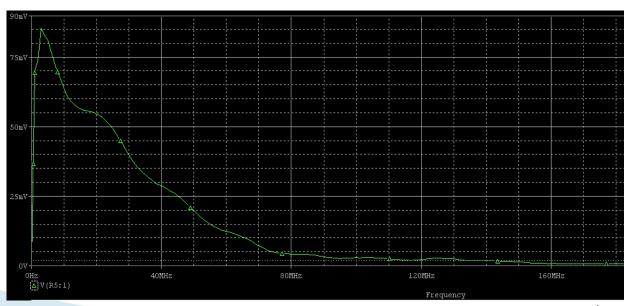

## PMT信号

● 诸多大型粒子物理 实验都使用光电倍 增管 (PMT) 探测 记录光子,光电倍 增管的冲击响应信 号可用准高斯型信 号近似。

所以很有必要设计 多通道多通道准高 斯型脉冲信号发生 器,便于快速完成 电子学测试与校准

上图为大亚湾提供幅度为2500mv的PMT波形图

#### 下图为其频域图形

## 设计指标

- 产生类PMT信号,要求前沿3ns左右,后沿10ns左右。

- 输出信号幅度要求可调。

- > 可独立控制16个信号产生通道。

- ▶ PC机通过USB接口控制信号产生电路。

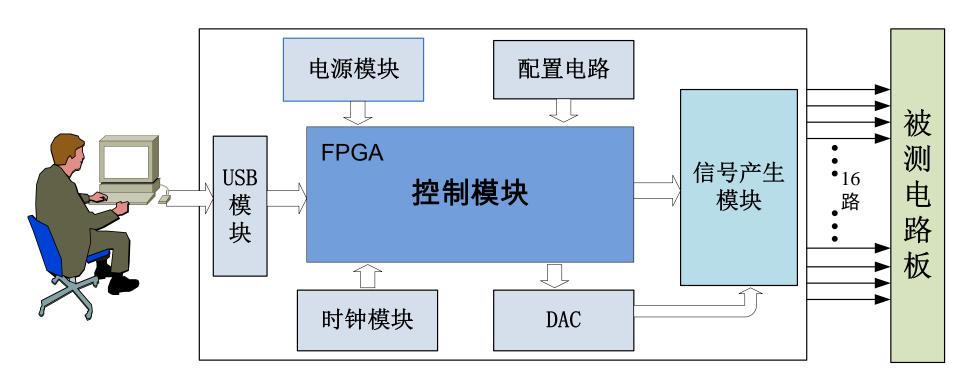

## 电路设计结构

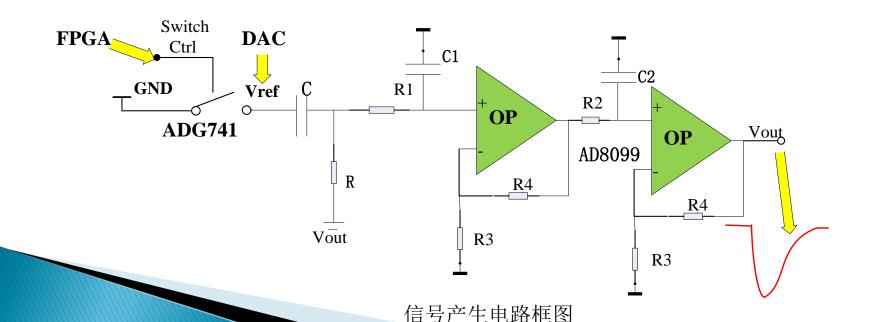

利用高速模拟开关电路来产生模拟脉冲信号,DAC用于调节脉冲信号的幅度,通过FPGA来控制高速模拟开关的触发电平以及DAC输出,信号产生电路中RC网络以及运算放大器组成的成形电路来决定脉冲信号的前后沿变时间,最终输出16通道的准高斯信号

## 信号产生模块

#### 产生幅度可调的准高斯型脉冲信号

- ▶ 低电压单刀单掷的高速模拟开关可产生沿边为1ns左右的阶跃信号;

- ➤ 由FPGA控制触发模拟开关的通断,通过RC网络和运算放大器组成的成形电路输出符合需求的多通道准高斯信号;

- ▶ 成形电路采用AD8099组成的两级低通滤波电路

- ▶ 通过DAC来调节输出信号的幅度大小;

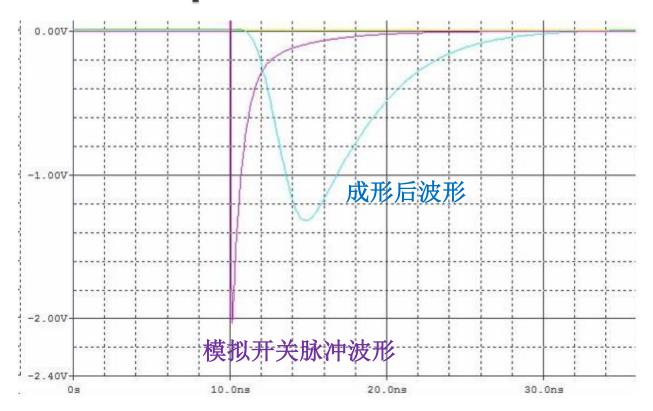

## 信号产生Pspice仿真

- ightharpoonup 经过多次仿真,RC值选取了R=50Ω,C=20p,R<sub>1</sub>,R<sub>2</sub>取100Ω,C<sub>1</sub>,C<sub>2</sub>取20p,可得到如所示的仿真输出波形。

- ➤ 可见,经过两级成形电路之后,输出信号呈准高斯形状,前沿约3ns,后沿约10ns。

## 控制模块

- FPGA和DAC作为整个设计中控制模拟开关触发和调节 脉冲信号幅度的控制模块。

- ▶ FPGA作为主控制器,实现USB控制、DAC控制、模拟 开关触发控制等功能。电路比较简单,估算需要68个 管脚,约1000LEs。

- ▶ 综合考虑FPGA选用了cycloneII系列EP2C5Q208C8, DAC芯片选用了AD5628

## 控制模块-FPGA

#### EP2C5Q208C8

#### 其资源特性如下:

- > 4,608 Les

- > 119,808 total RAM bits

- ➤ 13 Embedded multipliers (18×18 硬件乘法器)

- ➤ 2PLLs (锁相环)

- ➤ 142 User I/O pins (用户可用I/O)

- ➤ Fineline PGFP208-pin package (封装)

| • | 配置芯片EPCS1和EPCS4都可用 |

|---|--------------------|

|   | 选用EPCS1            |

| Table 1–1. Cyclone II FPGA Family Features (Part 1 of 2) |                   |           |            |            |         |         |               |  |  |  |

|----------------------------------------------------------|-------------------|-----------|------------|------------|---------|---------|---------------|--|--|--|

| Feature                                                  | EP2C5 <i>(2</i> ) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35  | EP2C50  | EP2C70        |  |  |  |

| LEs                                                      | 4,608             | 8,256     | 14,448     | 18,752     | 33,216  | 50,528  | 68,416        |  |  |  |

| M4K RAM blocks (4<br>Kbits plus<br>512 parity bits       | 26                | 36        | 52         | 52         | 105     | 129     | 250           |  |  |  |

| Total RAM bits                                           | 119,808           | 165,888   | 239,616    | 239,616    | 483,840 | 594,432 | 1,152,00<br>0 |  |  |  |

| Embedded multipliers (3)                                 | 13                | 18        | 26         | 26         | 35      | 86      | 150           |  |  |  |

| PLLs                                                     | 2                 | 2         | 4          | 4          | 4       | 4       | 4             |  |  |  |

| Table 1. Serial Configuration Devices (3.3-V Operation) |                    |  |  |  |  |

|---------------------------------------------------------|--------------------|--|--|--|--|

| Device                                                  | Memory Size (Bits) |  |  |  |  |

| EPCS1                                                   | 1,048,576          |  |  |  |  |

| EPCS4                                                   | 4,194,304          |  |  |  |  |

▶ 配置模式采用JTAG和AS两种

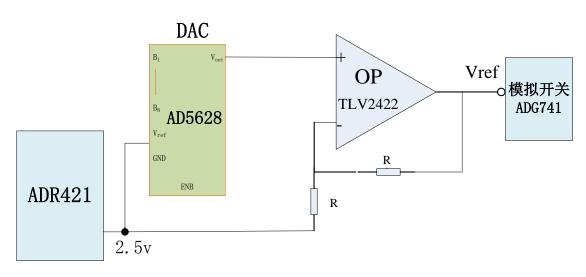

## 控制模块-DAC

- ▶2片AD5628可满足16通道 的设计需求

- ►ADR421为DAC和OPA提供2.5V的参考电平

- ▶运放TLV2422作为DAC输出信号的驱动,并可增大输出电平的调节范围,使V<sub>ref</sub>=2V<sub>DAC</sub>-2.5V

DAC控制电路图

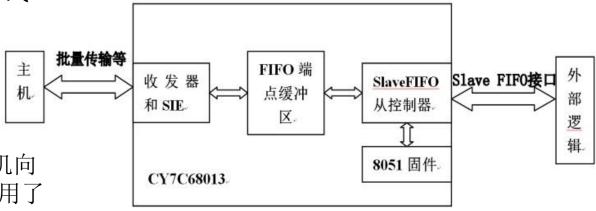

## USB模块

#### 与PC相连的USB接口使用了Cypress公司的CY7C68013

- ▶ CY7C68013可提供全面集成的 USB解决方案;

- ➤ 我们采用Slave FIFO传输方式

- ➤ 使用外部24MHz晶振

- ➤ 使用EPROM 装载程序

- ➤ 由于本设计只需要通过PC机向 FPGA写数据,因此直接使用了 Cypress公司提供的Cyconsole EZ-USB Interface软件来实现了 指令下发和测试

Slave FIFO传输示意图

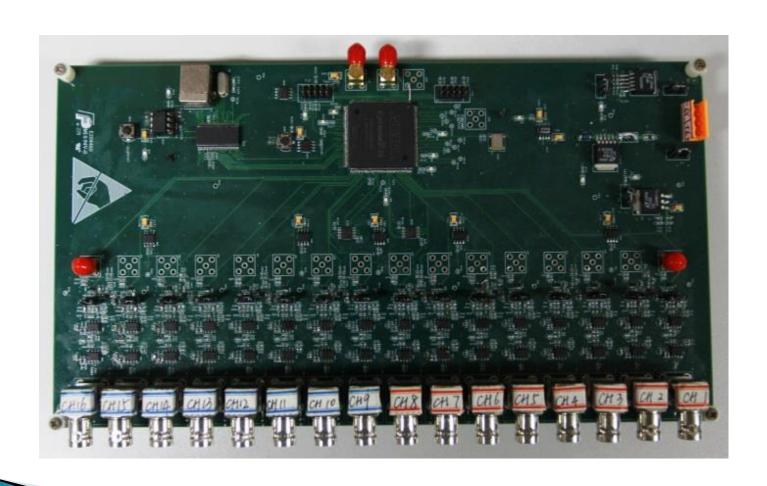

## 信号发生器电路实物图

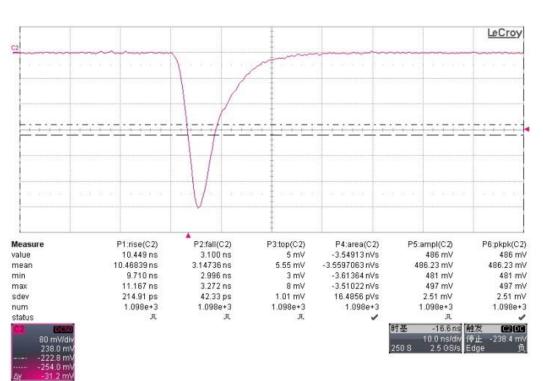

## 性能测试-信号输出

可见输出信号前沿为3.15ns, 后沿为10.47ns,均达到要求; 信号输出幅度为486mv。

通道1输出的准高斯信号 (控制电平V<sub>ref</sub>为1875mv)

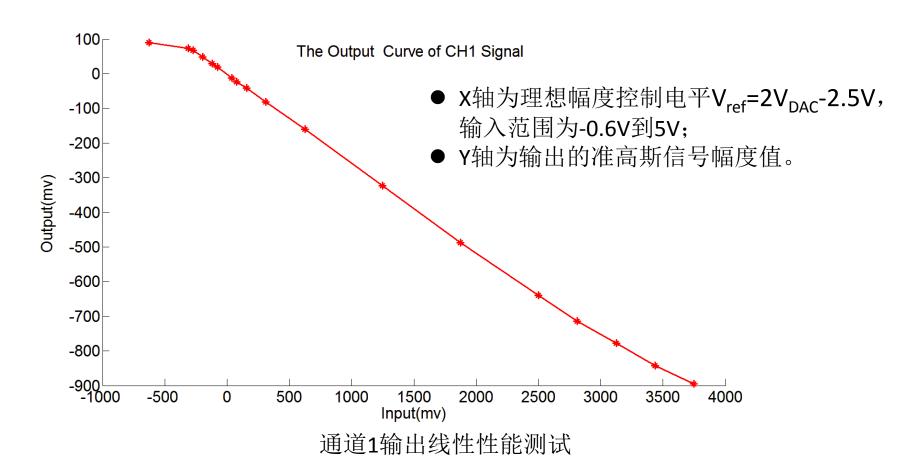

## 性能测试-信号输出特性曲线

可见,在输入为-300mv到2500mv时积分非线性小于0.7%,具有很好的线性,其对应的输出为67mv到-640mv,这与探测器中PMT直接输出的信号幅度范围近似,可作为有效的输出信号使用。

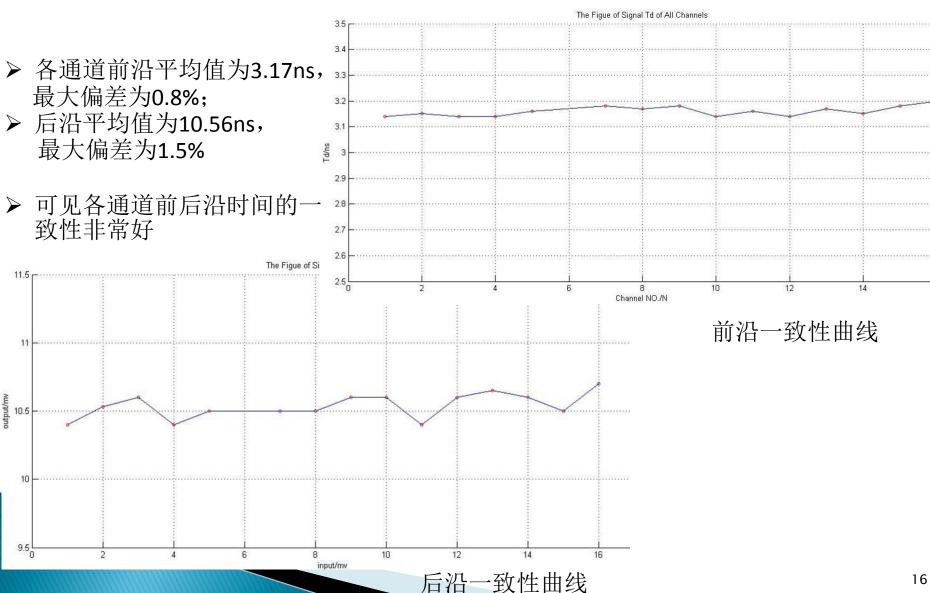

## 各通道输出前后沿一致性测试

## 各通道输出信号一致性测试

- ➤ 右表为16个通道DAC控制电平V<sub>ref</sub>与输出信号幅度线性比例常数(斜率)、偏置(截距)以及积分非线性;

- ➤ 可见各通道的积分非线 性都保持在0.7%以下

| \ <b>Z</b> \ <b>¥</b> □ | 기구 14 다 · 시 시 시 시 시 시 시 시 시 시 시 시 시 시 시 시 시 시 |         |        |  |  |  |  |  |  |

|-------------------------|-----------------------------------------------|---------|--------|--|--|--|--|--|--|

| 通道号                     | 线性常数                                          | /偏直(MV) | 积分非线性  |  |  |  |  |  |  |

| 1                       | -0.2565                                       | -2.02   | 0.0072 |  |  |  |  |  |  |

| 2                       | -0.2548                                       | -1.78   | 0.0071 |  |  |  |  |  |  |

| 3                       | -0.2538                                       | -0.91   | 0.005  |  |  |  |  |  |  |

| 4                       | -0.2539                                       | -5.72   | 0.0067 |  |  |  |  |  |  |

| 5                       | -0.2572                                       | -3.46   | 0.0077 |  |  |  |  |  |  |

| 6                       | -0.2542                                       | -2.49   | 0.0067 |  |  |  |  |  |  |

| 7                       | -0.2572                                       | -2.45   | 0.0052 |  |  |  |  |  |  |

| 8                       | -0.2527                                       | -4.64   | 0.0053 |  |  |  |  |  |  |

| 9                       | -0.2542                                       | -3.07   | 0.006  |  |  |  |  |  |  |

| 10                      | -0.2525                                       | -2.52   | 0.0048 |  |  |  |  |  |  |

| 11                      | -0.2548                                       | -1.06   | 0.0058 |  |  |  |  |  |  |

| 12                      | -0.2535                                       | -2.71   | 0.0062 |  |  |  |  |  |  |

| 13                      | -0.2507                                       | -5.44   | 0.0063 |  |  |  |  |  |  |

| 14                      | -0.253                                        | -2.79   | 0.0071 |  |  |  |  |  |  |

| 15                      | -0.252                                        | -3.20   | 0.0062 |  |  |  |  |  |  |

| 16                      | -0.2499                                       | -4.48   | 0.0058 |  |  |  |  |  |  |

| 平均值                     | -0.2538                                       | -3.08   | 0.0062 |  |  |  |  |  |  |

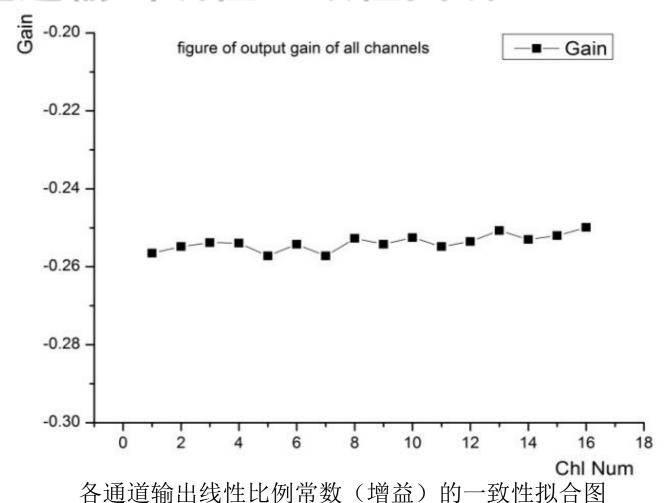

## 各通道输出线性一致性曲线

可见各通道输入输出线性比例一致性很好, 均值为-0.2538,最大一致性偏差为1.5%

## 测试小结

- 结果表明16路信号产生通道均可独立输出准高斯信号,且各通道一致性良好;

- ▶ 其前沿平均值约3.17ns, 后沿平均值约10.56ns;

- ▶ 输出信号在67mv到-640mv范围内可调,其积分 非线性均小于0.7%。

## 总结

- ▶ 设计并实现了一种基于USB接口可编程的16通道准 高斯型脉冲信号发生器

- 电路性能测试表明各通道工作正常,且各通道一致 性良好

- 产生的准高斯脉冲信号特性与粒子物理探测器中 PMT输出信号类似,可模拟探测器输出信号

- 用于大型粒子物理实验前端电子学的性能测试、校准检测等工作。

# 谢谢