#### **ATLAS Silicon Detector Activities**

Hongbo Zhu (IHEP)

# Outline

- Introduction to Phase-II silicon tracker upgrade

- Early involvement in the IBL project

- Intended involvement in ATLAS ITk-Strip project

- Summary and outlook

### Introduction

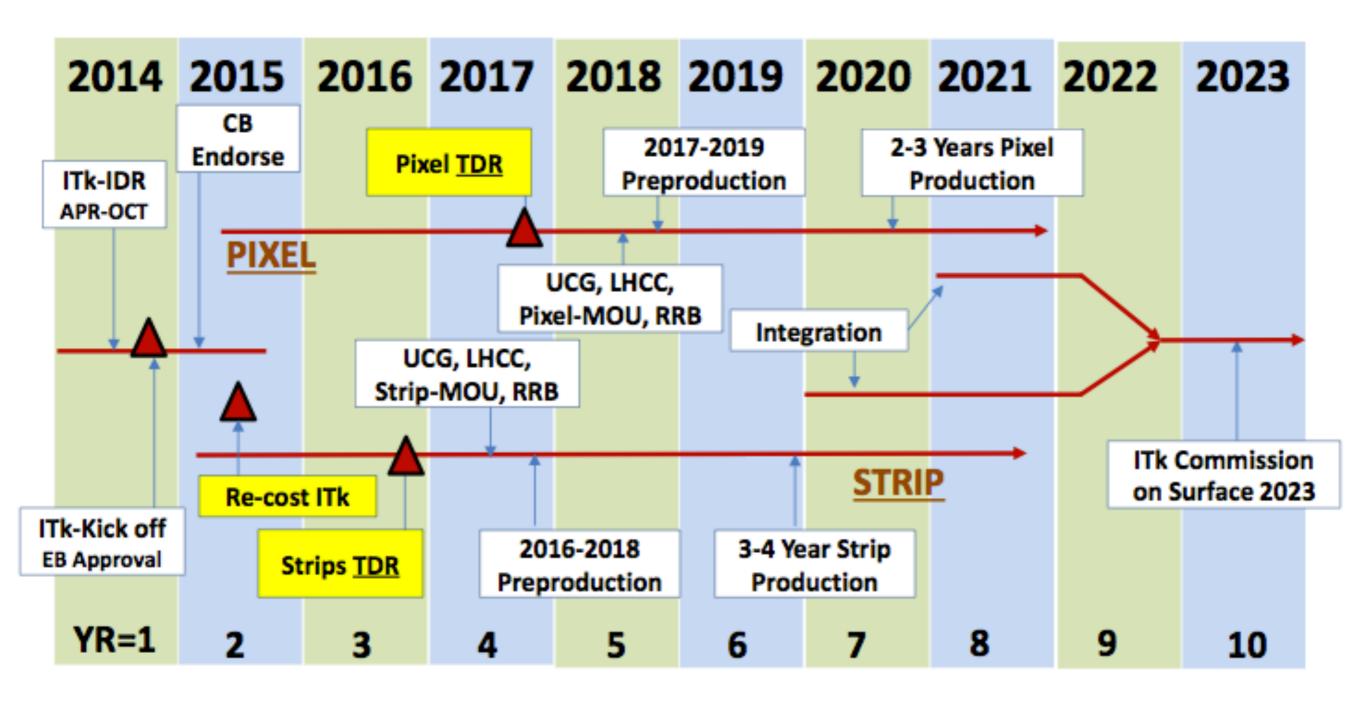

- New full silicon tracker expected around 2022, to maintain or improve the tracking performance under the HL-LHC conditions

- Radiation damage, detector occupancy

- Exploring the state-of-the-art silicon detector and electronics

- Pixel: planar/3D/CMOS sensor + readout ( →TSMC 65nm)

- Strip: microstrip/cmos sensor + readout (130 nm)

on-going R&D activities great opportunity to get involved

#### Initial Interestes in Pixel

- IHEP has long been interested in pixel detector development, in particular the design of advanced front-end electronics.

- Collaborated with CPPM and LBL on the design and test of FE-I4 (readout chip for the ATLAS IBL pixel layer recently installed)

- Have ASIC designers trained, but unfortunately most of the work never recognised in the ATLAS community

- Collaboration suspended due to several reasons, including the most critical one: export control, which forbids the possibility to test the chip in local lab.

- Additional contributions to the IBL project, e.g. chip design for the off-detector signal receiver and FPGA firmware development for the readout system.

# Drift to Strip

- ITK management visited IHEP in June and we had dedicated meetings to exchange ideas regarding IHEP's tentative involvement in the ITk project.

- Steve McMahon (ITk PL) had stressed several times that the institute participation in the Pixel and Strip detector project was highly imbalanced: less institutes on Strips but much larger detector area (10 m<sup>2</sup> vs 200 m<sup>2</sup>) to construct.

- He suggested "again" that IHEP should consider contributing to the Strip detector project.

- After several local group meetings called for discussion as well as continuous interactions with the ITk management, we started to believe it would be more feasible to participate in the Strip.

## ITk Kick-off Meeting

• During the ITk kick-off meeting, we expressed formally our interests.

#### **Expression of Interest**

- Institute of High Energy Physics (IHEP) will be leading the ITk related work within the Chinese Cluster.

- Intended contributions: Strips (primary) + Pixel (optional)

- <u>CONSTRUCTION</u>: Strips detector module production and related studies, including powering, radiation tolerance and thermal effects (just started and in close collaboration with DESY)→ production site

- <u>DESIGN</u>: 1. HV-CMOS sensor design & evaluation; 2. front-end electronics for strips/pixel (manpower available)

- <u>COMMON</u>: tracking software and performance (interested)

- We have not yet given up the intention to get involved in the Pixel development, but the chance will be rather slim.

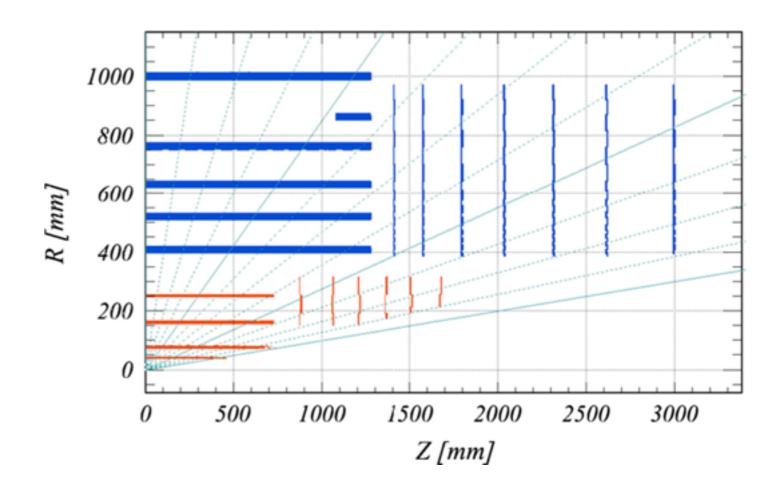

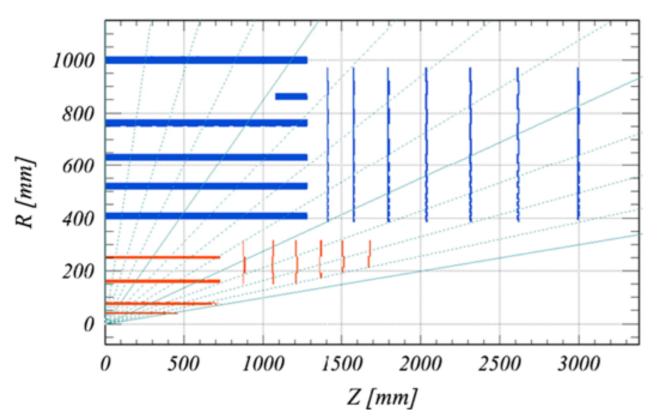

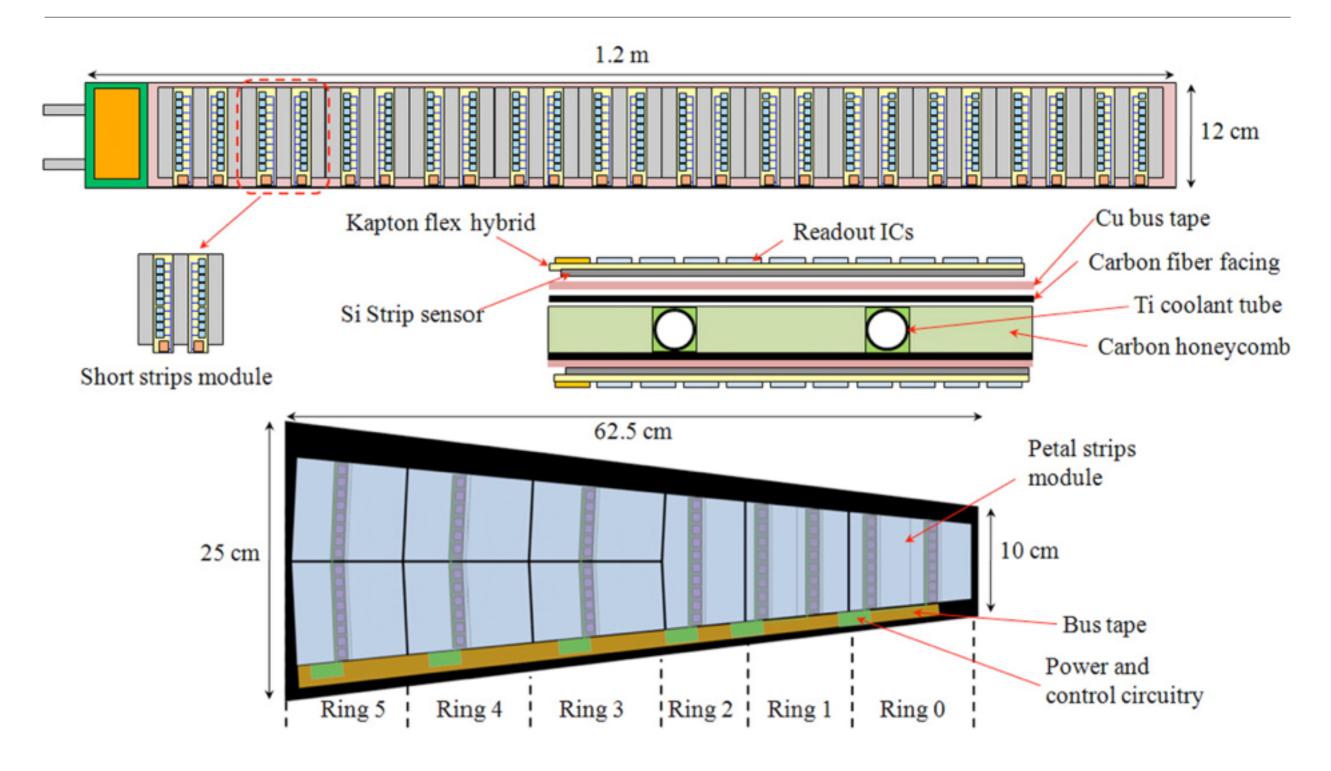

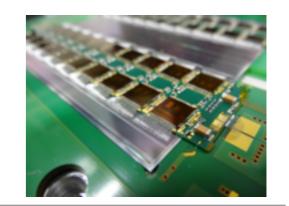

#### Stave/Petal

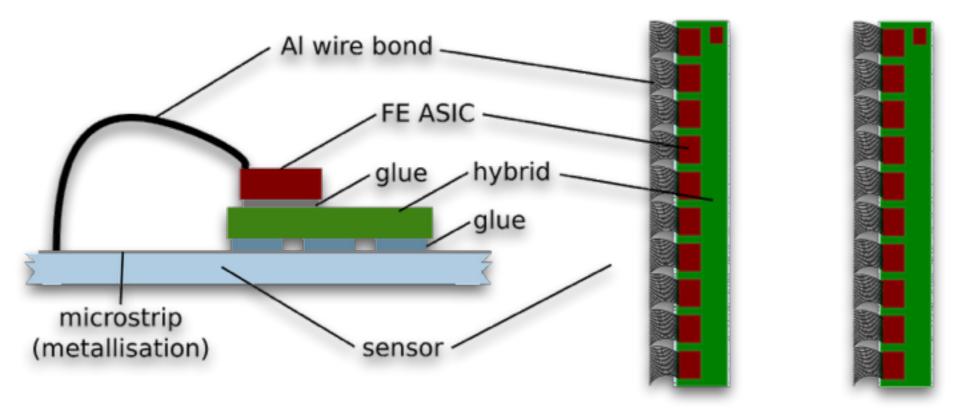

### Strips Detector Module

According to the expected contribution of 1% to the ATLAS Phase-II project, we shall construct ~500 strips detector modules.

We will collaborate with DESY (a leading player in the Strip detector project), under the framework of "CAS-Helmholtz Joint Research Group"; important for knowledge transfer and support

## Future Mass Production

- ATLAS has decided to stay with the IBM process (line secured to some extend) → export control issue remains ...no easy solution

- It is possible that we could apply for exception on the readout chip, but will be very uncertain.

- We have been also discussing with DESY and RAL to see if they could provide us some lab space so that we can have our team embedded and produce detector module.

- RAL has given green light and similarly for DESY

- But can we convince our funding agency to allow us place overseas our instrument (e..g expensive high speed wire boning machine)? → nontrivial

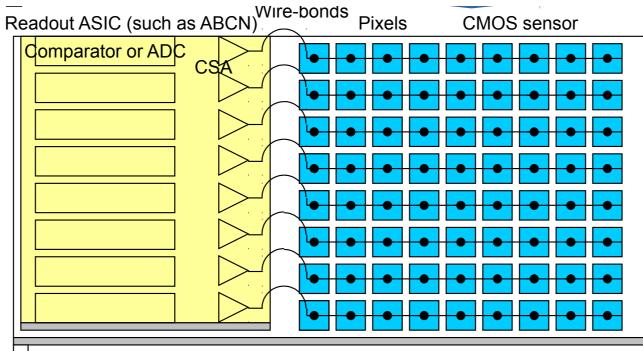

## **CMOS Sensor for Strips**

- Attractive and promising alternative to the conventional silicon microstrip sensor utilising standard HV/HR-CMOS process→ significant reduction in cost and production time

- Extra z-position via voltage encoding  $\rightarrow$  improvement in resolution

• We will contribute to the sensor design and test. Design contribution being discussed; prototype sensors for test on the way.

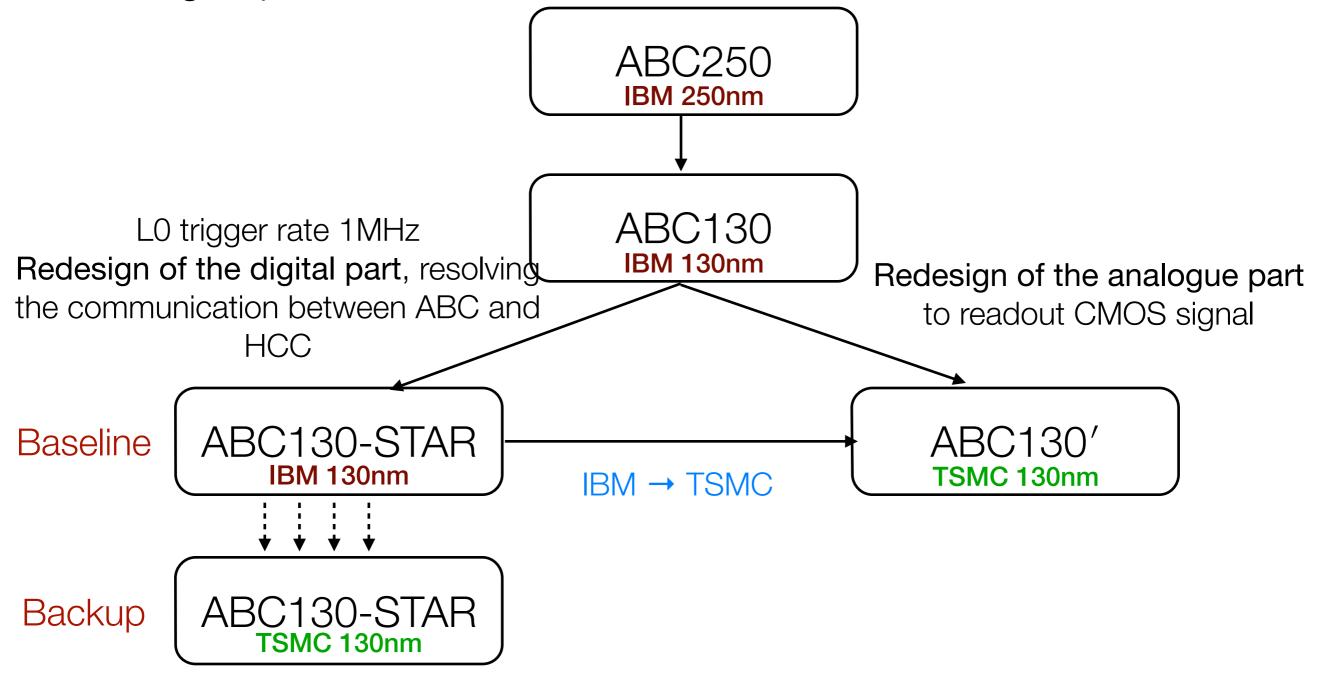

## Front-end Electronics Design

• Opportunity to contribute the re-design of the readout chip for Strip, the digital part for ABC130-STAR.

## Front-end Electronics Design

- Expected contributions (experienced staff member and PhD student to be rotated to CERN for efficient communication):

- Task 1: to develop RTL (functional) code in Verilog language

- Taks 2: to develop functional verification environment with the SystemVerilog language

- We have also expressed interests to contribute to the analog part design for the CMOS sensor readout chip, which will be critical for the CMOS Task Force.

- Contributing to both analog and digital design (and in TSMC) might enable the possibility to migrate the technology for CEPC silicon tracker.

## **Project Timeline**

## Summary and Outlook

- We have almost identified the topics for the Phase-II Inner Tracker upgrade. → significant progress after long time of struggling

- We have started to work on a concrete plan for our involvement in the project for the coming years, including rotating group members to collaborating institutes to get trained and make contributions.

- We have requested for funding, but the situation is not clear yet.

wikiHow