# 首批谱仪共用波形数字化 电子学研制进展

曹平

核探测与核电子学国家重点实验室中国科学技术大学核科学技术学院

2016年6月27日

# 主要内容

- 一. 研究计划要点

- 二. 研究工作的主要进展

- 三. 总结

# 一、研究计划要点

- 课题简介

- 研究内容

- 技术路线

### 1.1、课题简介

- 白光中子源是国际上开展核数据测量实验研究的最重要实验装置

- 国防核应用、先进核能技术、核天体物理和基础核物理

- 经过论证,确定了主要物理目标和探测器设计方案,将建设6套探测器系统:

- 1. 源中子注量率、能谱及束流剖面监测

- 2. 俘获截面测量 ( $C_6D_6$ 探测器及 $BaF_2$ 球)

- 3. 裂变截面测量

- 4. 全截面测量

- 5. (n,x)反应

- 6. 探测器标定

为保证首批物理实验的顺利进行,减小研发周期及成本,将探测器系统通用部分进行统一设计,形成公用电子学

### 1.2、研究内容

- 首批物理实验公用电子学研制

- 5类探测器信号的波形数字化模块

- ➤ C<sub>6</sub>D<sub>6</sub>探测器:俘获截面测量(阮锡超)

- ➤ Si-Mon探测器:中子注量探测(鲍杰)

- ➢ GIC、ΔE-E探测器:带电粒子测量(孙志嘉)

- ▶ 多层裂变电离室:中子全截面测量(刘荣)

- ▶ 快裂变电离室:中子能谱、束流监测(鲍杰)

### 1.3、技术路线

#### (1)依托BaF<sub>2</sub>谱仪读出电子学系统

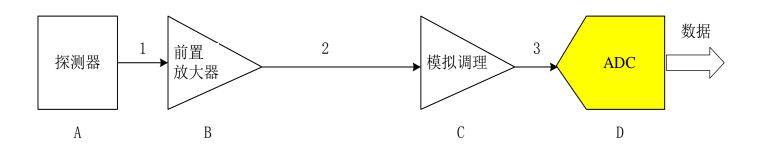

在BaF<sub>2</sub>谱仪电子学基础上,设计共用电子学架构,并统一高精度波形数字化模块、时钟触发模块、PXIe平台接口的设计。

#### (2) 共性、专用电子学分离设计

波形数字化及读出平台采用共性设计、探测器前置放大器采用 专用设计,二者通过模拟调理插件适配。

# 二、研制进展

- 需求及方案制定

- C<sub>6</sub>D<sub>6</sub>系统

# 2.1、总体需求

|                     | C <sub>6</sub> D <sub>6</sub> 系统 | Si-Mon探测器           | 带电粒子测量    | 多层裂变电离室             | 快裂变室                 |

|---------------------|----------------------------------|---------------------|-----------|---------------------|----------------------|

| 模拟调理输入信号 前沿         | 5ns                              | 800ns               | 50-1000ns | 100ns               | 10ns~30ns            |

| 模拟调理输入信号<br>后沿      | 50ns                             | 70us                | (未确定具体参数) | 100us               | 50~100us             |

| 信号动态范围              | 0~-3V<br>( 200keV~8MeV )         | 5mV~500mV           | (未确定具体参数) | 0~500mV             | 5mV~500mV<br>(经过快主放) |

| 事例率                 | 200~300Hz                        | 200~300Hz           | 200~300Hz | ~500Hz              | 1~200Hz              |

| 信号类型(电流型<br>or 电压型) | 电压型                              | 电压型                 | 电压型       | 电流型                 | 电流型                  |

| 通道数                 | 4                                | 1                   | 12        | 8                   | 2                    |

| 所用电缆类型<br>(电缆2)     | 差分电缆                             | 差分电缆                | 同轴电缆      | 差分电缆                | 差分电缆                 |

| 传输距离(电缆2)           | 10~20m                           | 10~20m              | 10~20m    | ~10m                | 10~20m               |

| 接插件型号               | LEMO(具体型号依<br>据电缆定)              | LEMO(具体型号依<br>据电缆定) | BNC或SMA   | LEMO(具体型号<br>依据电缆定) | LEMO(具体型号<br>依据电缆定)  |

| 采样长度                | 300ns(可调节)                       | 3us                 | 3us       | 1us                 | 3us                  |

| 中子飞行时间<br>测量精度      | ≤1ns                             | ≤1us                | ≤1ns      | ≤1ns                | ≤10ns                |

# 需求(共性部分)

| 量化精度            | 12bit                                     |  |  |  |

|-----------------|-------------------------------------------|--|--|--|

| 采样率             | 1GSPS                                     |  |  |  |

| 数据缓存长度          | 10ms                                      |  |  |  |

| 触发方式            | 内触发、外触发                                   |  |  |  |

| 触发甄别阈           | 可调,精度:8bit、范围:10~200mV                    |  |  |  |

| 质子打靶间隔          | 40ms                                      |  |  |  |

| 波形数字化插件输入<br>信号 | 差模:-400~400mV,共模:1.25V                    |  |  |  |

| 数据上传方式          | FDM到零槽通过PCIe总线采用DMA方式传输<br>零槽到服务器通过干兆网线上传 |  |  |  |

| 软件接口            | 干兆以太网(TCP/IP协议)                           |  |  |  |

| 其它              | 无                                         |  |  |  |

| 备注              | 如后期确定增加主放,则参数可能调整(Si-Mon)                 |  |  |  |

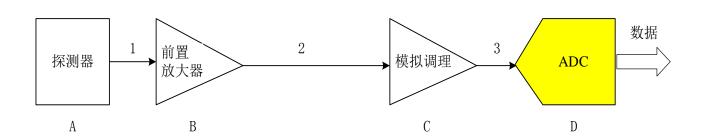

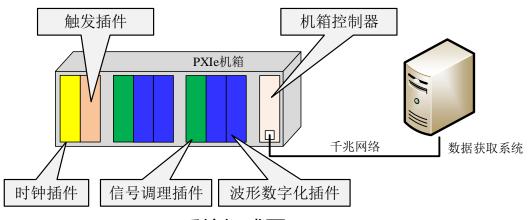

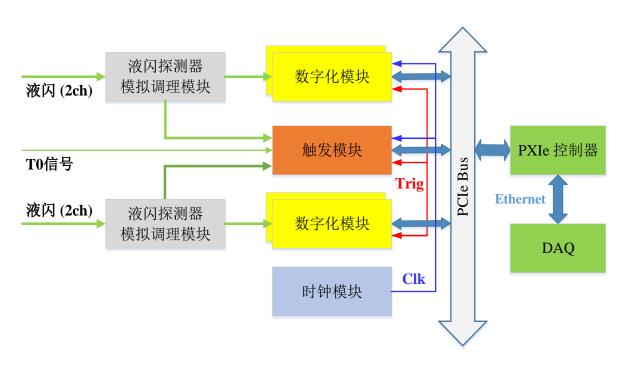

### 2.2、系统架构

- ▶基于PXIe平台、波形数字化的技术路线

- >电子学系统主要包括:

- ✓模拟调理插件(专用电子学)

- ✓触发插件(专用电子学)

- ✓时钟插件(公用电子学)

- ✓数字化插件(公用电子学)

## 研究现状

- 完成初步的需求统计

- 设计符合首批物理实验的数据读出通用型系统架构

- PXIe平台读出

- 波形数字化、时钟插件统一设计

- 信号调理、触发插件专用设计

- 探测器通道规模通过信号调理插件进行适配

- 开展C<sub>6</sub>D<sub>6</sub>探测器数据读出的研制

●模拟调理模块 ( 4in , 4out ) :

●C6D6探测器:1块

●半导体探测器:1块

●快裂变室:1块

●多层裂变电离室:3块

●带电粒子探测器:2块

系统组成图

# 2.3、C<sub>6</sub>D<sub>6</sub>俘获截面测量系统

#### 测量目标:

- ●测量中子飞行时间谱,精度小于1ns

- ●测量γ-ray能谱

- ●监测中子注量率

#### 关键电路设计:

- ●模拟调理插件模块

- ●触发模块

- ●时钟模块

- ●波形数字化模块

C<sub>6</sub>D<sub>6</sub>测量俘获截面读出电子学系统框图

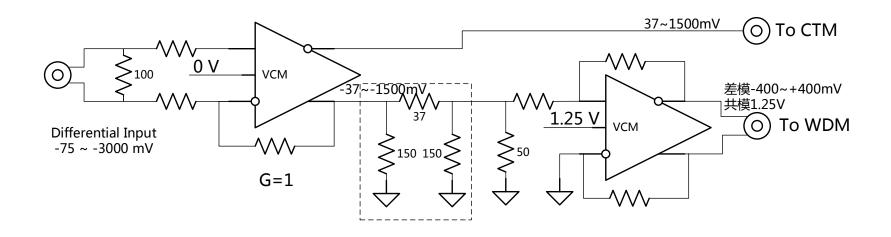

# 2.4、 C<sub>6</sub>D<sub>6</sub>探测器模拟调理插件

| 输入信号时间特性            | 前沿:5ns , 后沿:50ns    |  |  |

|---------------------|---------------------|--|--|

| 输入信 <del>号</del> 范围 | -75~-3000 mV        |  |  |

| 输出信 <del>号</del>    | 差分600mVpp , 1.25V共模 |  |  |

| 输入通道数(IN)           | 4                   |  |  |

| 输出通道数(OUT)          | 4                   |  |  |

- ●完成前放电路与波形数字化插件之间的信号适配

- ●通过长距离模拟电缆(10~20m)与前放连接

- ●差分信号(短距离,<1m)至波形数字化模块

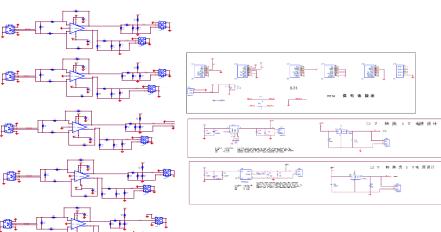

### 信号调理电路

◆每个通道信号扇出为两路

FDM,波形数字化

CTM,时间测量与触发判选

◆FDM要求范围:

$-400^{\sim}400 \text{ mV}_{\text{diff}}$  ;  $1.25 \text{V}_{\text{com}}$

◆CTM要求范围

输出电压幅度:0~3.3V

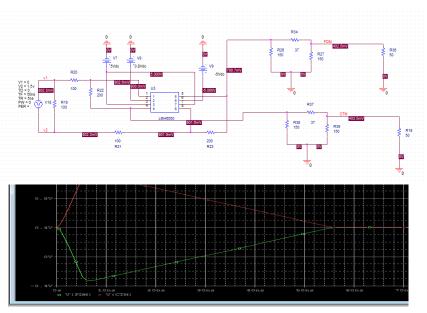

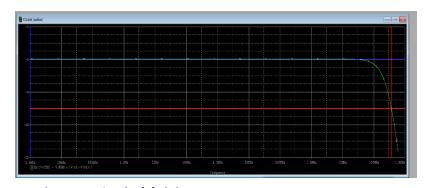

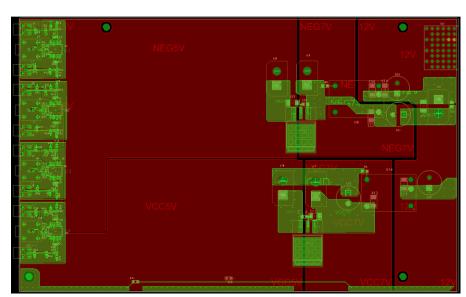

# 原理图及PCB设计

瞬态响应仿真

幅频响应特性:-3dB@364MHZ <sub>CSNS白光中子源中期检查会议,东莞</sub>, 2016.6.27~28

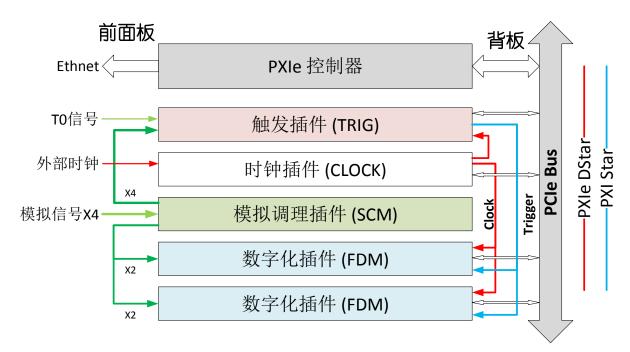

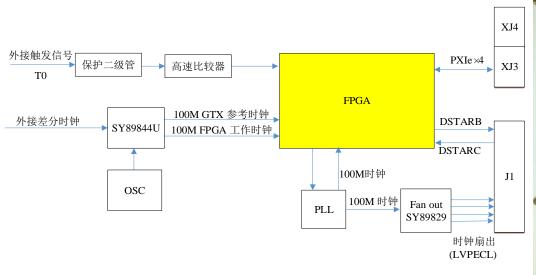

### 2.3、触发时钟插件

- ●为系统提供统一的时钟和触发信号,定时槽

- ●复用BaF,系统的本地触发时钟模块(LTCM)

- ●1路外触发(面板输入)

- ●1路外时钟(100MHz,面板输入)

- ●16路触发扇出(PXIe背板)

- ●16路时钟扇出(PXIe背板)

- 时钟(三种选择)

- 本地高性能晶振提供的100 MHz时钟

- 外部参考时钟经过PLL得到100 MHz时钟

- 直接使用PXIe机箱提供的100 MHz时钟

LTCM实物图

触发时钟插件结构图

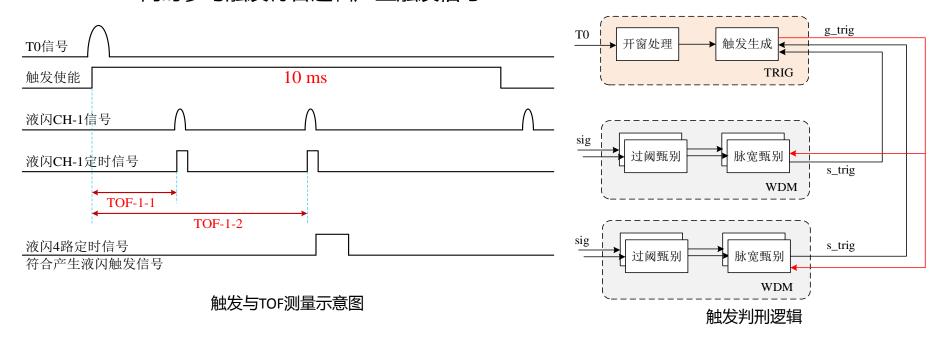

## 2.4、触发方案

- 提供触发信号

- 参与TOF测量

- 开启10ms触发使能窗,每次探测器信号过阈作为一次时间测量的停止时刻,同时参与触发符合逻辑产生触发信号

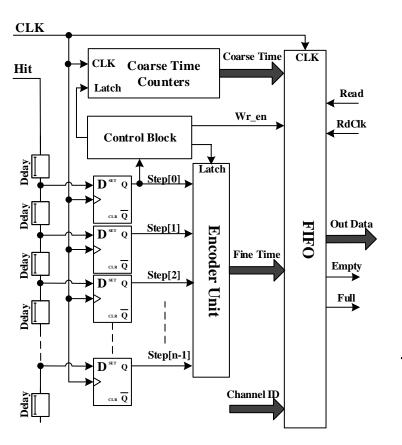

### TDC@FPGA实现原理

实现原理: "粗"+"细"的时间测量(计数器+进位链内插)

粗计数:

- ➤ 24bit计数器

- ➤ 时钟: 200MHz (5ns)

- 实现大动态范围,大于前端延迟线单元需求

细计数:

- ➤ 利用进位链测量小于1个周期的时间

- ➤ 每个CARRY4单元输出CO0 和CO3

译码单元: ➤ 温度计码

▶ 折半查找

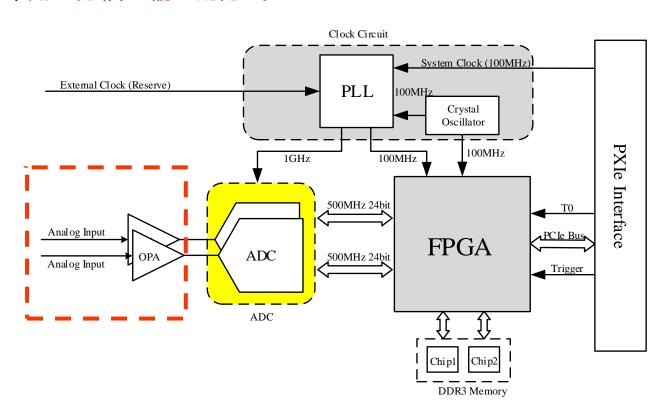

### 2.5、波形数字化插件

- ▶波形数字化模块沿用白光中子源BaF₂探测器波形数字化模块

- ▶采用1Gsps@12bits ADC

- ▶每两个通道对应于一个波形数字化板

- ▶板载大容量DDR3内存(乒乓,4Gb×2),可缓存数据采集长度:150ms

- ▶统一采用差分信号输入的方式

# 三、下一步计划

- ·完成C<sub>6</sub>D<sub>6</sub>及公用电子学插件设计

- 进度安排:

- 2017年4月前完成全部共用电子学研制、加工、调试和测试

|               | 2017.9 | 2017.10 | 2017.11 | 2017.12 | 2018.1 | 2018.2 | 2018.3 |

|---------------|--------|---------|---------|---------|--------|--------|--------|

| 束流测量          |        |         |         |         |        |        |        |

| 裂变截面          |        |         |         |         |        |        |        |

| 俘获截面          |        |         |         |         |        |        |        |

| 刻度实验          |        |         |         |         |        |        |        |

| 全截面           |        |         |         |         |        |        |        |

| (n, x) 实<br>验 |        |         |         |         |        |        |        |

|               |        |         |         |         |        |        |        |

### 总结

- 初步完成共用电子学需求及方案设计

- •完成C<sub>6</sub>D<sub>6</sub>模拟调理电路设计

- 下一步, 开展电路加工、焊接、调试及联合测试

# 谢谢!!